Изобретение относится к вычислительной технике, автоматике и телемеханике, к устройствам кодирования и декодирования информации и может быть использовано в цифровых системах обработки и., передачи дискретной информации.

Целью изобретения является повыдостоверности д екодирования за счет устранения начальной неоднозначности и скачков фазы произвольного порядка.

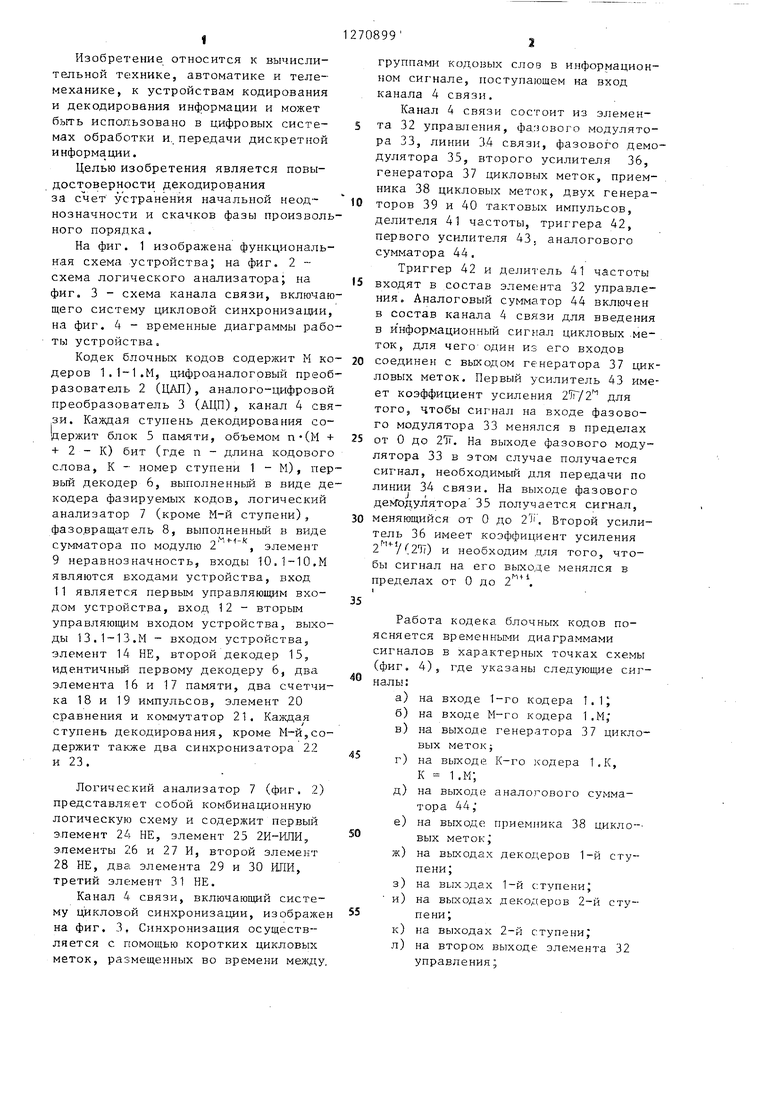

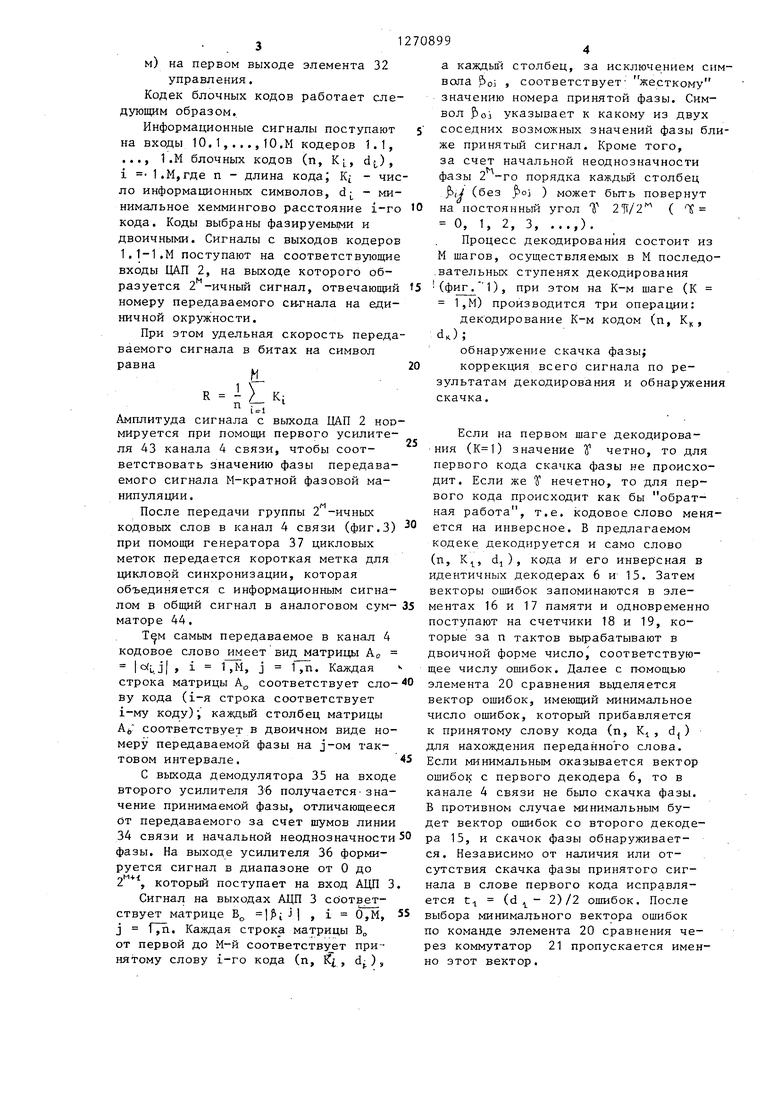

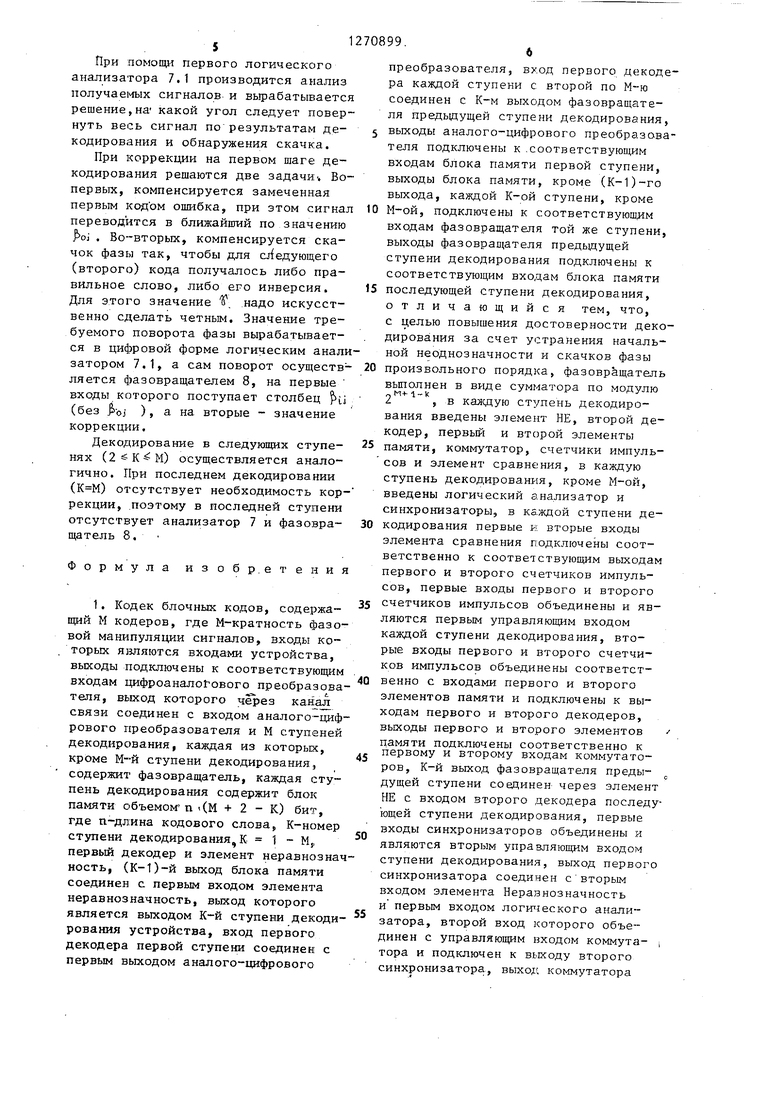

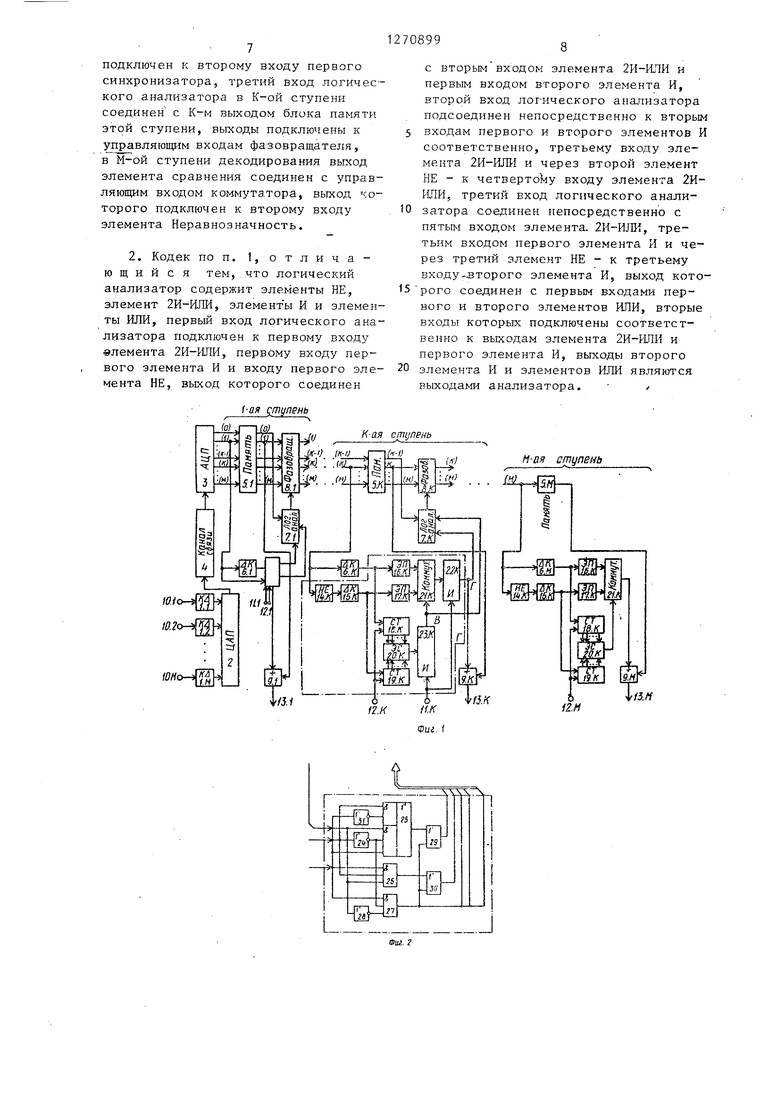

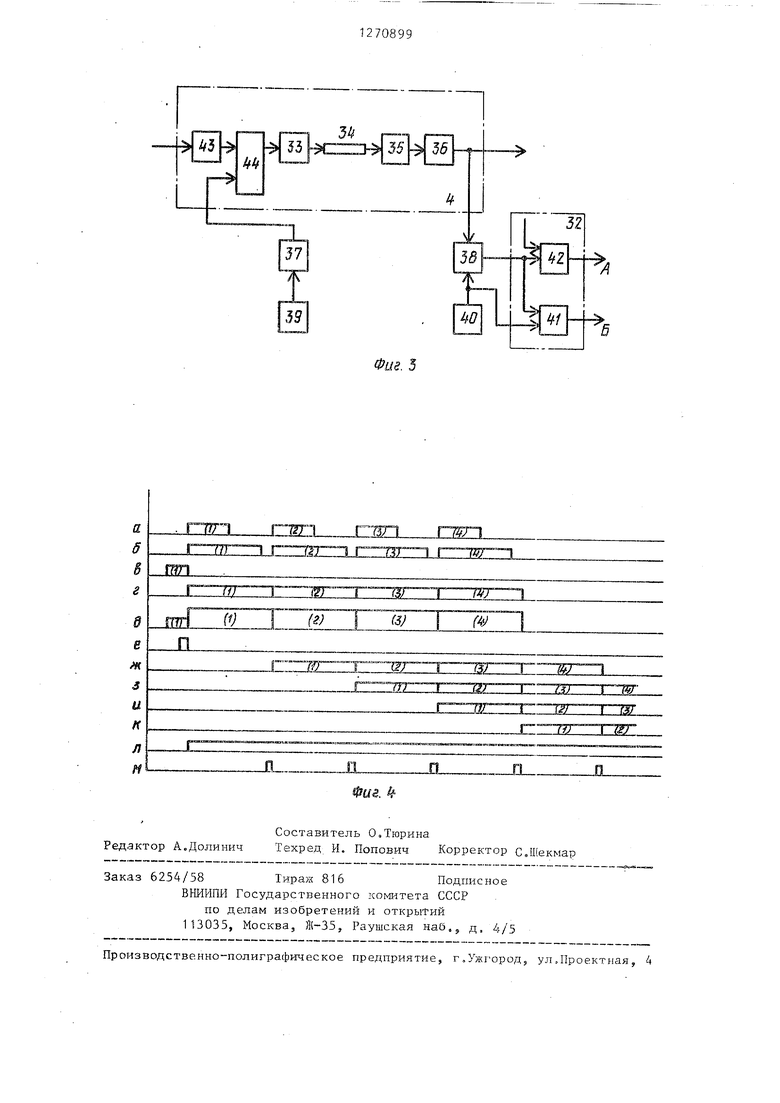

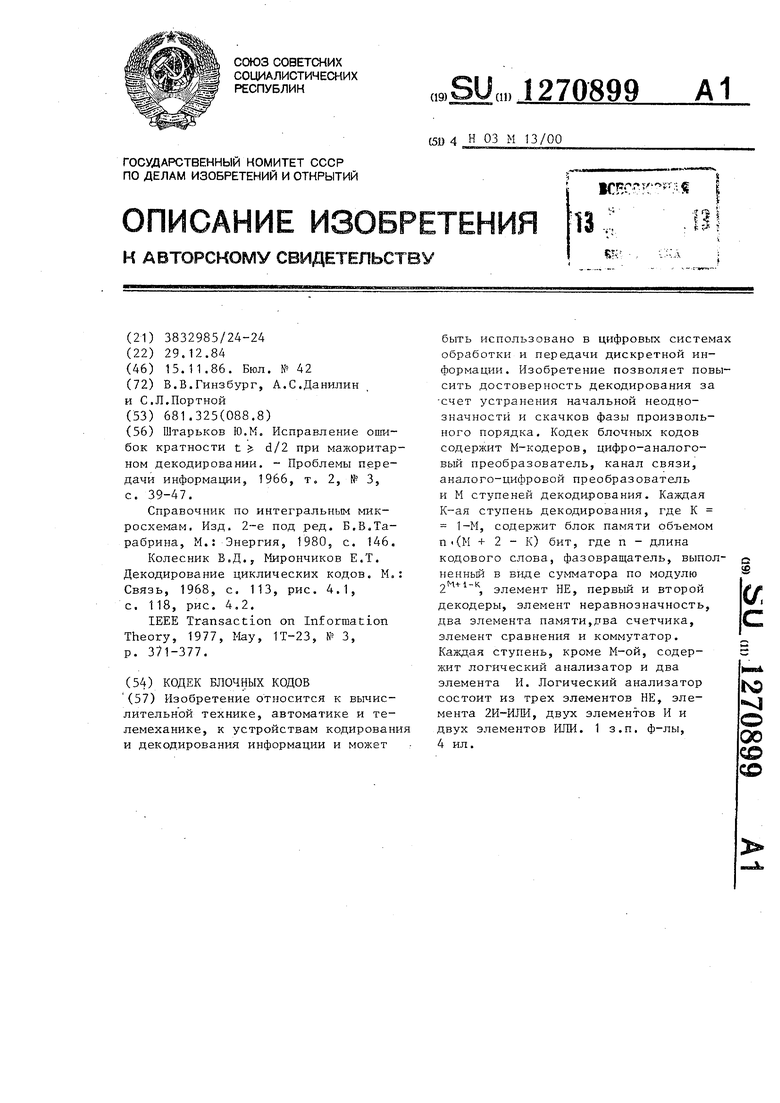

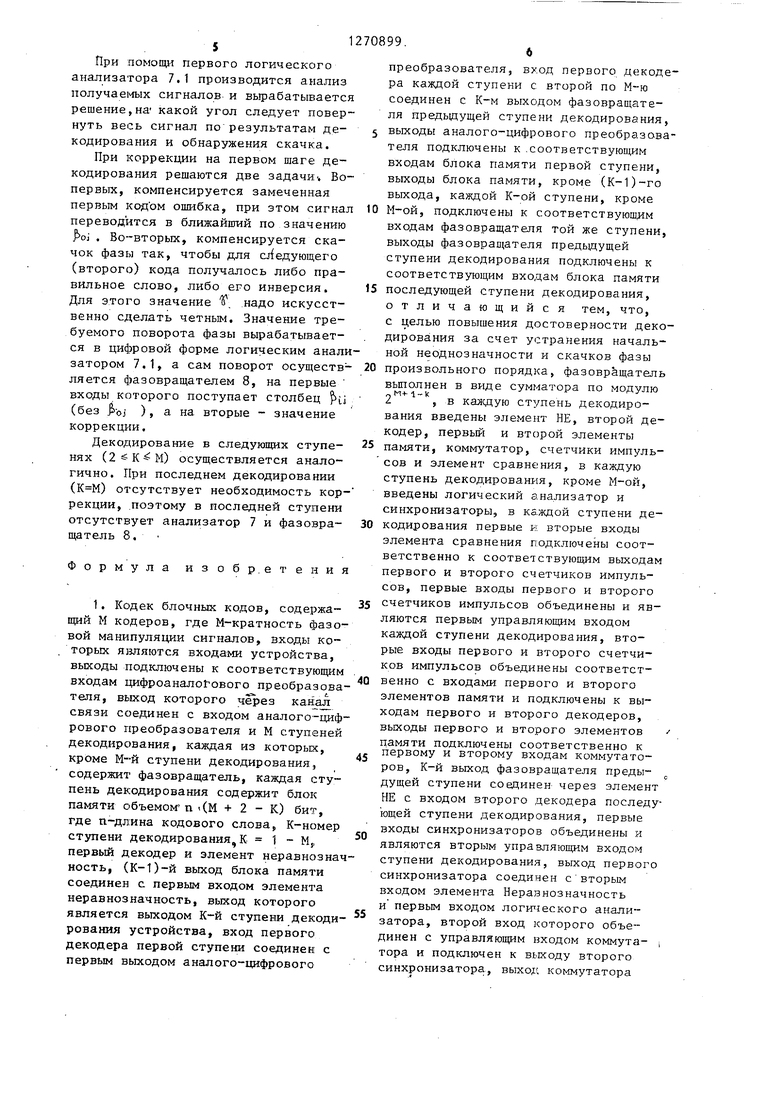

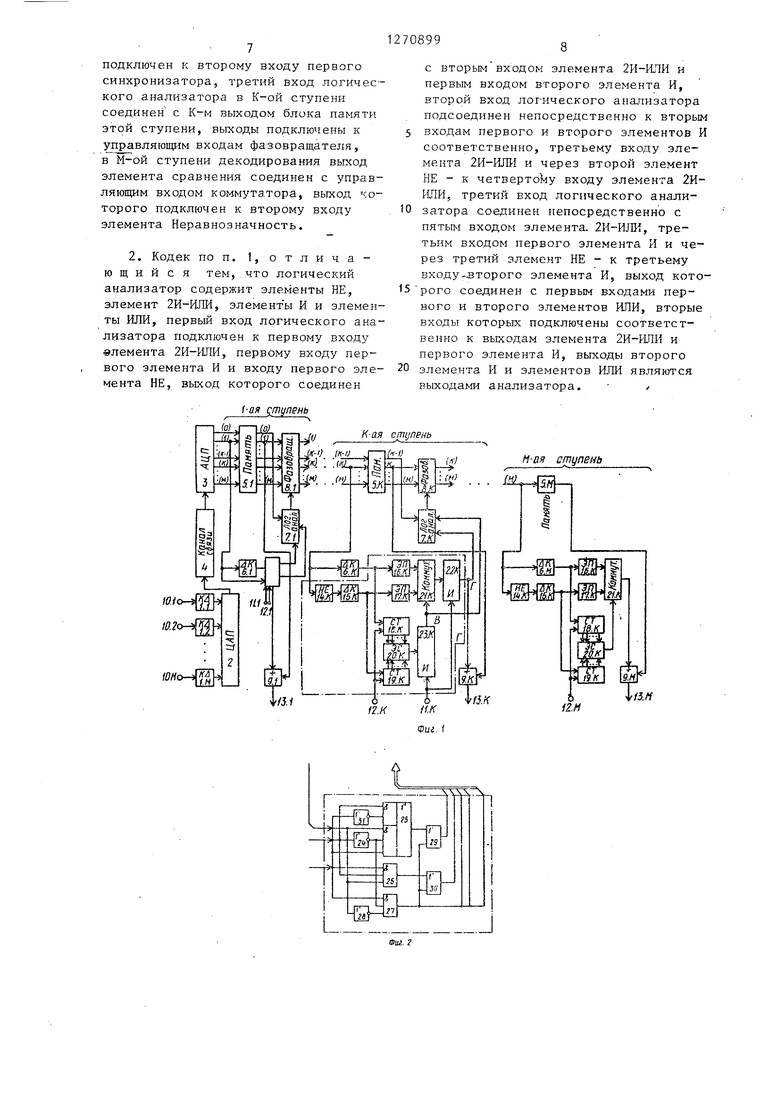

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 схема логического анализатора; на фиг. 3 - схема канала связи, включающего систему цикловой синхронизащ и, на фиг. 4 - временные диаграммы работы устройства.

Кодек блочных кодов содержит М кодеров 1.1-1.М, цифроаналоговый преобразователь 2 (ЦАП), аналого-цифровой преобразователь 3 (АЦП), канал 4 связи. Каждая ступень декодирования содержит блок 5 памяти, объемом П(М + + 2 - К) бит (где п - длина кодового слова, К - номер ступени 1 - М), первый декодер 6, выполненньй в виде декодера фазируемых кодов, логический анализатор 7 (кроме М-й ступени), фазовращатель 8, выполненный в виде

.vl V 1/

сумматора по модулю 2 , элемент 9 неравнозначность, входы 10.1-10,М являются входами устройства, вход 1 1 является первым управляющим входом устройства, вход 12 - вторым управляю1цим входом устройства, выходы 13.1-13,М - входом устройства, элемент 14 НЕ, второй декодер 15, идентичньш первому декодеру 6, два элемента 16 и 17 памяти, два счетчика 18 и 19 импульсов, элемент 20 сравнения и коммутатор 21. Каждая ступень декодирования, кроме М-й,содержит также два синхронизатора 22 и 23,

Логический анализатор 7 (фиг. 2) представляет собой комбинационную логическую схему и содержит первый элемент 24 НЕ, элемент 25 2И-ИЛИ., элементы 26 и 27 И, второй элемент 28 НЕ, два элемента 29 и 30 {ШИ, третий элемент 31 НЕ.

Канал 4 связи, включающий систему цикловой синхронизации, изображен на фиг, 3, Синхронизация осуществляется с помощью коротких цикловых меток, размещенных во времени мелоду.

группами кодовых слов в информационном сигнале, поступающем на вход канала 4 связи.

Канал 4 связи состоит из элемента 32 управления, фазового модулятора 33, линии 34 связи, фазового демодулятора 35, второго усилителя 36, генератора 37 ЦИКЛОВЕ Х меток, приемника 38 цикловых меток, двух генераторов 39 и 40 тактовых импульсов, делителя 41 частоты, триггера 42, первого усилителя 43, аналогового сумматора 44,

Триггер 42 и делитель 41 частоты входят в состав элемента 32 управления. Аналоговый сумматор 44 включен в состав канала 4 связи для введения в информационный сигнал цикловых .меток для чего один из его входов соединен с выходом генератора 37 цикловых меток. Первый усилитель 43 имеет коэффициент усиления 21Г/2 для того, чтобы сигнал на входе фазового модулятора 33 менялся в пределах от О до 2ТГ. На выходе фазового модулятора 33 в этом случае получается сигнал, необходимый для передачи по линии 34 связи. На выходе фазового де1хГодулятора 35 получается сигнал, меняющийся от О до 2Ji, Второй усилитель 36 имеет коэффициент усиления 2 /(2J7) и необходим для того, чтобы сигнал на его выходе менялся в

Mt 1 пределах от О до 2

Работа кодека блочных кодов поясняется временными диаграммами сигналов в характерных точках схем (фиг. 4)5 где указаны следующие синалы:

а)на входе 1-го кодера 1,1;

б)на входе М-го кодера 1.М;

в)на выходе генератора 37 циклвых метокJ

г)на выходе К-го )содера 1,К,

К 1,м;

д)на выходе аналогового сумматора 44;

е)на выходе приемника 38 цикловых меток

ж)на выходах деко,еров 1-й ступени;

з)на выхэдах 1-й с:тупени;

и) на выходах декодеров 2-й ступени;

к) на выходах 2-й ступени;

л) на втором выходе элемента 32 управления; м) на первом выходе элемента 32 управления. Кодек блочных кодов работает следующим образом. Информационные сигналы поступают на входы 10.1,.,.,10.М кодеров 1.1, ..., 1 .М блочньт кодов (п, К;, dj,), i 1.М,где п - длина кода; К; - чис ло информационных символов, d - минимальное хеммингово расстояние i-ro кода. Коды выбраны фазируемьгми и двоичными. Сигналы с выходов кодеров 1.1-1.М поступают на соответствующие входы ЦАП 2, на выходе которого образуется 2 -ичный сигнал, отвечающий номеру передаваемого си-гнала на единичной окружности. При этом удельная скорость переда ваемого сигнала в битах на символ равна Амплитуда сигнала с выхода ЦАП 2 нор мируется при помощи первого усилителя 43 канала 4 связи, чтобы соответствовать значению фазы передаваемого сигнала М-кратной фазовой манипуляции. После передачи группы 2 -ичных кодовых слов в канал 4 связи (фиг.З) при помощи генератора 37 цикловых меток передается короткая метка для цикловой синхронизации, которая объединяется с информационным сигналом в общий сигнал в аналоговом сумматоре 44. самым передаваемое в канал 4 кодовое слово jiMeeT вид матрицы АО .J| i - , J . Каждая строка матрицы А соответствует елову кода (i-я строка соответствует i-му коду); каждый столбец матрицы А, соответствует в двоичном виде номеру передаваемой фазы на j-ом тактовом интервале. С выхода демодулятора 35 на входе второго усилителя 36 получается-значение принимаемой фазы, отличающееся От передаваемого за счет шумов линии 34 связи и начальной неоднозначности 50 ра

фазы. На выходе усилителя 36 формируется сигнал в диапазоне от О до 2 которьй поступает на вход АЦП 3.

Сигнал на выходах АЦП 3 сбответствует матрице Б J | , i 0,М, 55 j 1,п. Каждая строка матрицы Б от первой до М-й соответствует принятому слову i-ro кода (п, К|, d),

ся. Независимо от наличия или отсутствия Скачка фазы принятого сигнала в слове первого кода исправляется t (d ; - 2)/2 ошибок. После выбора минимального вектора ошибок по команде элемента 20 сравнения через коммутатор 21 пропускается именно этот вектор. а каждый столбец, за исключением символа &oi , соответствует жесткому значению номера принятой фазы. Символ oj указывает к какому из двух соседних возможных значений фазы ближе принятый сигнал. Кроме того, за счет начальной неоднозначности фазы 2 -го порядка каждьй столбец ,.у (без oj ) может быть повернут напостоянньй угол Т 2ТГ/2 ( Of 0, 1,2, 3, ...,). . Процесс декодирования состоит из М шагов, осуществляемых в М последовательных ступенях декодирования (фиг.1), при этом на К-м шаге (К 1,М) производится три операции: декодирование К-м кодом (п, Кц, обнаружение скачка фазы; коррекция всего сигнала по результатам декодирования и обнаружения скачка. Если на первом шаге декодирования () значение У четно, то для первого кода скачка фазы не происходит. Если же Y нечетно, то для первого кода происходит как бы обратная работа, т.е. кодовое слово меняется на инверсное. В предлагаемом кодеке декодируется и само слово (п, К, d), кода и его инверсная в идентичных декодерах 6 и 15. Затем векторы ошибок запоминаются в элементах 16 и 17 памяти и одновременно поступают на счетчики 18 и 19, которые за п тактов вырабатывают в двоичной форме число, соответствующее числу ошибок. Далее с п-омощью элемента 20 сравнения вьщеляется вектор ошибок, имеющий минимальное число ошибок, который прибавляется к принятому слову кода (п, К, dj) для нахождения переданного слова. Если минимальным оказывается вектор ошибок с первого декодера 6, то в канале 4 связи не было скачка фазы. Б противном случае минимальным будет вектор ошибок со второго декоде15, и скачок фазы обнаруживаетПри помощи первого логического анализатора 7,1 производится анализ получае1чых сигналов и вьфабатывается решение,на какой угол следует повернуть весь сигнал по результатам декодирования и обнаружения скачка. При коррекции на первом шаге декодирования решаются две задачи. Во первых, компенсируется замеченн:ая первым кодом ошибка, при этом сигнал переводится в ближайщий по значению oj . Во-вторых, компенсируется скачок фазы так, чтобы для следующего (второго) кода получалось либо правильное слово, либо его инверсия. Для этого значение У. надо искусственно сделать четным. Значение требуемого поворота фазы вырабатывается в цифровой форме логическим анал затором 7.1, а сам поворот осуществ ляется фазовращателем 8, на первые входы которого поступает столбец U (без ), а на вторые - значение коррекции. Декодирование в следующих ступенях () осуществляется аналогично. При последнем декодировании () отсутствует необходимость кор рекции, поэтому в последней ступени отсутствует анализатор 7 и фазовращатель 8. Формула изобр.етени 1. Кодек блочных кодов, содержащий М кодеров, где М-кратность фазо вой манипуляции сигналов, входы которых я зляются входами устройства, выходы подключены к соответствующим входам цифpoaнaлo oвoгo преобразова теля, выход которого через кан:ал связи соединен с входом аналого-циф рового преобразователя и М ступеней декодирования, каждая из которых, кроме М-й ступени декодирования, содержит фазовращатель, каждая ступень декодирования содержит блок памяти объемом-п «(М + 2 - К) бит, где п-длина кодового слова, К-номер ступени декодирования,К 1 - М, первый декодер и элемент неравнозна ность, (К-1)-й выход блока памяти соединен с первым входом элемента неравнозначность, выход которого является выходом К-й ступени декоди рования устройства, вход первого декодера первой ступени соединен с первым выходом аналого-цифрового преобразователя, вход первого декодера каждой ступени с второй по М-ю соединен с К-м выходом фазовращателя предыдущей ступени декодирования, выходы аналого-цифрового преобразователя подключены к ,соответствуюпд-1м входам блока памяти первой ступени, выходы блока памяти, кроме (К-1)-го выхода, каждой К-ой ступени, кроме М-ой, подключены к cooтвeтcтвyюш м входам фазовращателя той же ступени, выходы фазовращателя предыдущей ступени декодирования подключены к соответствующим входам блока памяти последующей ступени декодирования, отличающийся тем, что, с целью повышения достоверности декодирования за счет устранения начальной неоднозначности и скачков фазы произвольного порядка, фазовращатель выполнен в виде сумматора по модулю 2 , в каждую ступень декодирования введены элемент НЕ, второй декодер, первьм и второй элементы памяти, коммутатор, счетчики импульсов и элемент сравнения, в каждую ступень декодирования, кроме М-ой, введены логический анализатор и синхронизаторы, в каждой ступени декодирования первые и вторые входы элемента сравнения подключены соответственно к соответствующим выходам первого и второго счетчиков импульсов, первые входы первого и второго счетчиков импульсов объединены и являются первым управляющим входом каждой ступени декодирования, вторые входы первого и второго счетчиков импульсов объединены соответственно с входами первого и второго элементов памяти и подключены к выходам первого и второго декодеров, выходы первого и второго элементов памяти подключены соответственно к первому и второму входам коммутаторов, К-й выход фазовращателя предыдущей ступени соединен через элемент НЕ с входом второго декодера последующей ступени декодирования, первые входы синхронизаторов объединены и являются вторым управляющим входом ступени декодирования, выход первого синхронизатора соединен свторым входом элемента Неравнозначность и первым входом логи1еского анализатора, второй вход которого объединен с управляющим входом коммута- , тора и подключен к выходу второго синхронизатора, выход коммутатора подключен к второму входу первого синхронизатора5 третий вход логичес кого анализатора в К-ой ступени соединен с К-м выходом блока памяти этой ступени, выходы подключены к управляющим входам фазовращателя, в М-ой ступени декодирования выход элемента сравнения соединен с управ ляющим входом коммутатора, выход торого подключен к второму входу элемента Неравнозначность, 2. Кодек по п. 1, отличающийся тем, что логический анализатор содержит элементы НЕ, элемент 2И-ШШ, элементы И и элемен ты ИЛИ, первый вход логического ана лизатора подключен к первому входу элемента 2И-1ШИ, первому входу первого элемента И и входу первого эле мента НЕ, выход которого соединен с вторымвходом элемента 2Р1-ИЛИ и первым входом второго элемента И, второй вход логического анализатора подсоединен непосредственно к вторым входам первого и второго элементов И соответственно, третьему входу элемента 2И-ИЛИ и через второй элемент НЕ - к четвертому входу элемента 2ИИЛИ, третий вход логического анализатора соединен непосредственно с пятым входом элемента. 2И-ШШ, третьим входом первого элемента И и через третий элемент НЕ - к третьему входу-аторого элемента И, выход которого соединен с первым входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к выходам элемента 2И-КПИ и первого элемента И, выходы второго элемента И и элементов ИШ являются выходами анализатора, /

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| Кодек каскадного мажоритарного кода | 1984 |

|

SU1185613A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| Кодек каскадного блочного кода | 1985 |

|

SU1338075A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Устройство для декодирования итеративного кода | 1988 |

|

SU1547080A1 |

| Кодек блочных кодов | 1986 |

|

SU1401613A1 |

Изобретение относится к вычислительной технике, автоматике и телемеханике, к устройствам кодирования и декод.ирова ия информации и может быть использовано в цифровых системах обработки и передачи дискретной информации. Изобретение позволяет повысить достоверность декодирования за счет устранения начальной неоднозначности и скачков фазы произвольного порядка. Кодек блочных кодов содержит М-кодеров, цифро-аналоговый преобразователь, канал связи, аналого-цифровой преобразователь и М ступеней декодирования. Каждая К-ая ступень декодирования, где К , содержит блок памяти объемом п-(М + 2 - К) бит, где п - длина кодового слова, фазовращатель, выполQ ненньш в виде сумматора по модулю 2М-и-к элемент НЕ, первый и второй декодеры, элемент неравнозначность, два элемента памяти,два счетчика, элемент сравнения и коммутатор. Каждая ступень, кроме М-ой, содержит логический анализатор и два элемента И. Логический анализатор ГО состоит из трех элементов НЕ, эле-ч мента 2И-ИЛИ, двух элементов И и о 00 двух элементов ИЛИ. 1 з.п. ф-лы, 4 ил. г (

:

J

Авторы

Даты

1986-11-15—Публикация

1984-12-29—Подача