1

(21)4615475/09

(22)05.12.88

(46) 15.02.91.БЮЯ. № 6

(71)Институт кибернетики им.В.М.Глуш- кова

(72)С.Н.Жаровский, А.М.Лучук, и Н.В с Лунине кий

(53)621.394.6 (088.8)

(56)Авторское свидетельство СССР № 1019661, кл. Н 04 L 27/10, 1981.

(54)ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДАННЫХ

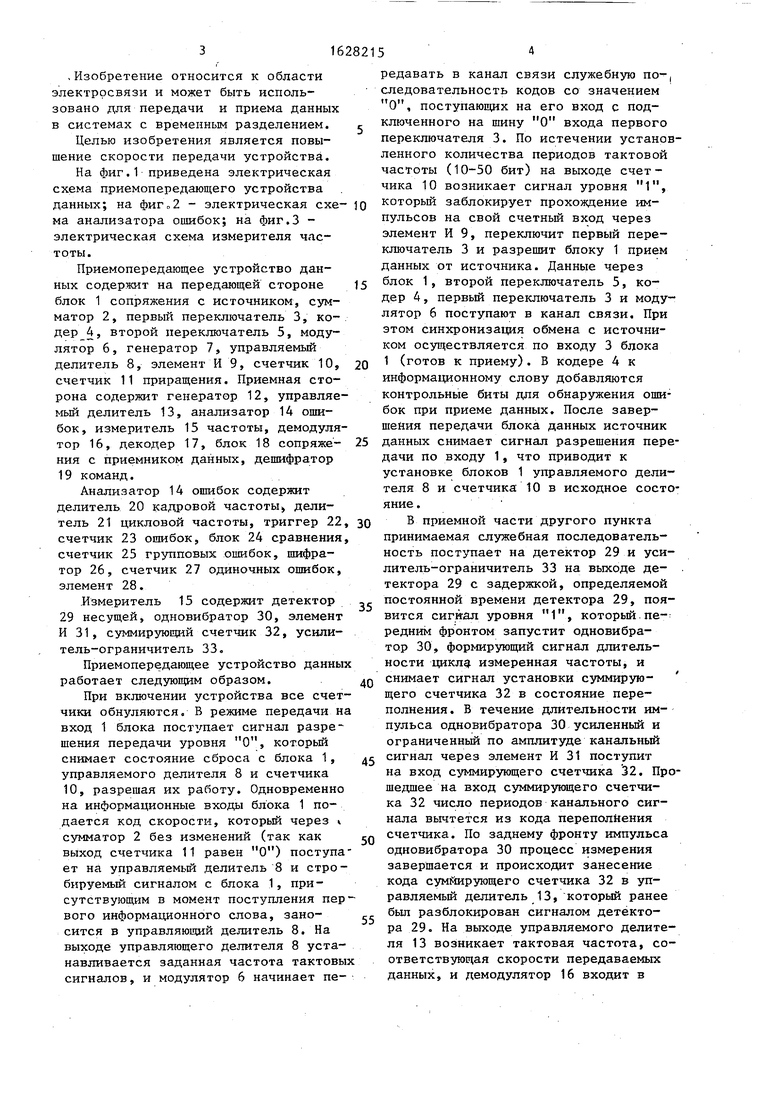

(57)Изобретение относится к электросвязи. Цель изобретения - повышение скорости передачи. Устройство содержит на передающей стороне блок 1 сопряжения с источником, сумматор 2, переключатели 3 и 5, кодер 4, модулятор 6, генератор 7, управляемый делитель 8, элемент И 9, счетчик 10 и счетчик 11 приращения, а на приемной стороне - генератор 12, управляемый делитель 13, анализатор 14 ошибок,

измеритель 15 частоты, демодулятор 16, декодер 17, блок 18 сопряжения с приемником данных и дешифратор 19 команд. Данные через блок 1, переключатель 5, кодер 4, переключатель 3 и модулятор 6 поступают в канал связи. В кодере 4 к информационному слову добавляются контрольные биты для обнаружения ошибок при приеме данных. Анализатор 14 выполняет подсчет количества ошибок за один кадр данных, а также за время анализа канала. Команда изменения скорости возбуждает один из двух выходов дешифратора 19. В результате в счетчик 11 добавляется или вычитается единица. При изменении направления передачи код скорости, формируемый на выходе сумматора 2, уменьшается или увеличивается в зависимости от кода счетчика 11, соответственно уменьшается или увеличивается скорость передачи данных. 2 з.п.ф-лы, 3 ил.

SS

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ИСПОЛЬЗОВАНИЕМ БЛОЧНЫХ РАЗДЕЛИМЫХ КОДОВ, ОТ ИМИТИРУЮЩИХ ДЕЙСТВИЙ ЗЛОУМЫШЛЕННИКА | 2019 |

|

RU2738789C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| Адаптивная радиолиния связи | 1976 |

|

SU661824A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| ПРИЕМНАЯ И ПЕРЕДАЮЩАЯ АППАРАТУРА И СПОСОБ, ВКЛЮЧАЮЩИЙ ПУНКТУРИРОВАННОЕ СВЕРТОЧНОЕ КОДИРОВАНИЕ И ДЕКОДИРОВАНИЕ | 1994 |

|

RU2117390C1 |

Bxf

8x2 ВхЗ

Передающая

о

ГС

Выход

,Изобретение относится к области электросвязи и может быть использовано для передачи и приема данных в системах с временным разделением.

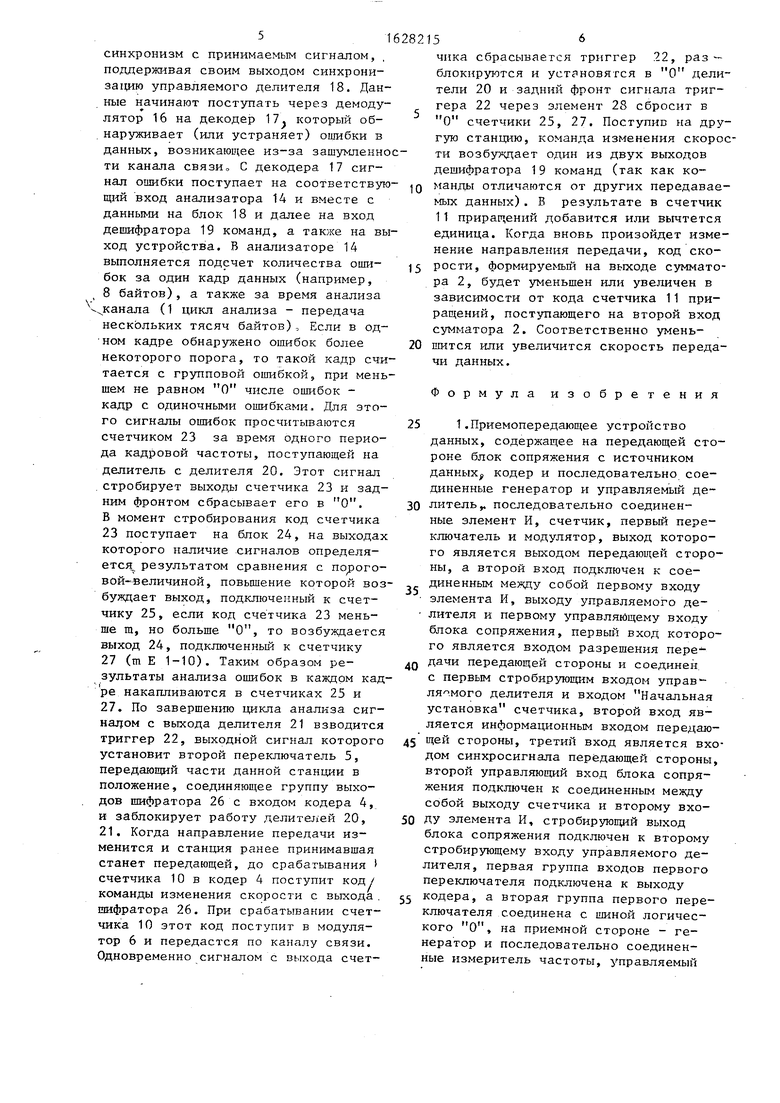

Целью изобретения является повышение скорости передачи устройства. На фиг.1 приведена электрическая схема приемопередающего устройства данных; на фиг„2 - электрическая схе- ма анализатора ошибок; на фиг.З - электрическая схема измерителя частоты.

Приемопередающее устройство данных содержит на передающей стороне блок 1 сопряжения с источником, сумматор 2, первый переключатель 3, кодер 4, второй переключатель 5, модулятор 6, генератор 7, управляемый делитель 8, элемент И 9, счетчик 10, счетчик 11 приращения. Приемная сторона содержит генератор 12, управляемый делитель 13, анализатор 14 ошибок, измеритель 15 частоты, демодулятор 16, декодер 17, блок 18 сопряже- ния с приемником данных, дешифратор 19 команд.

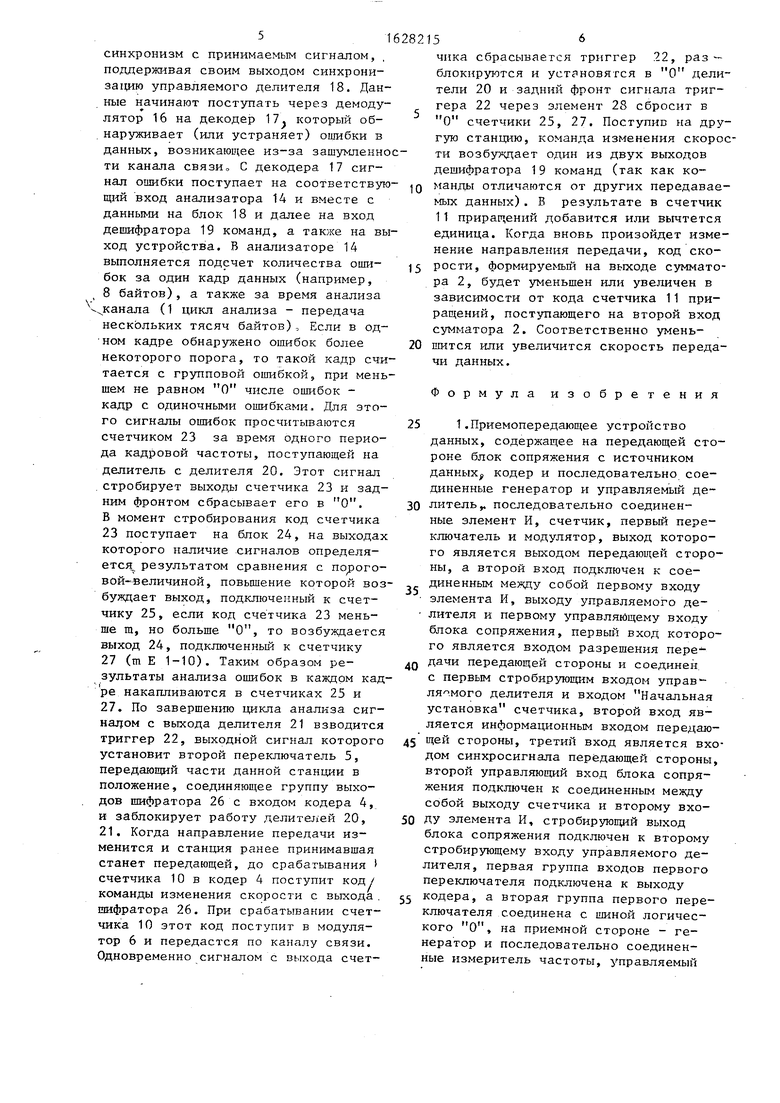

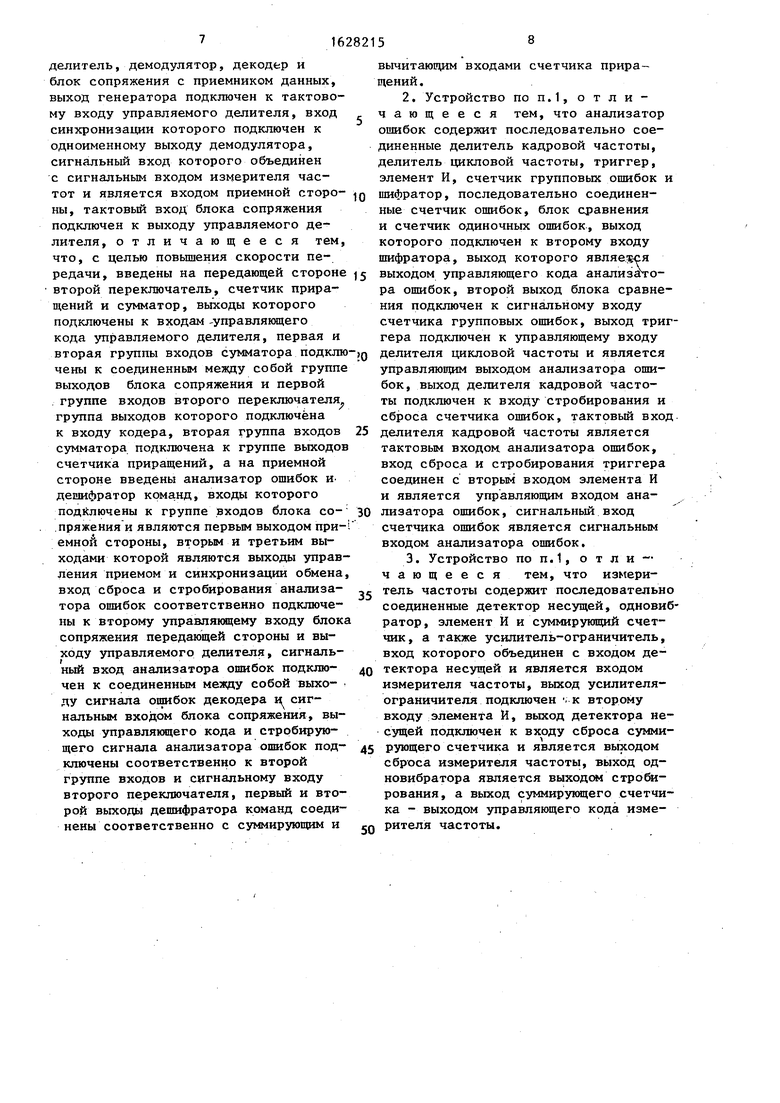

Анализатор 14 ошибок содержит делитель 20 кадровой частоты,, делитель 21 цикловой частоты, триггер 22, счетчик 23 ошибок, блок 24 сравнения, счетчик 25 групповых ошибок, шифратор 26, счетчик 27 одиночных ошибок, элемент 28.

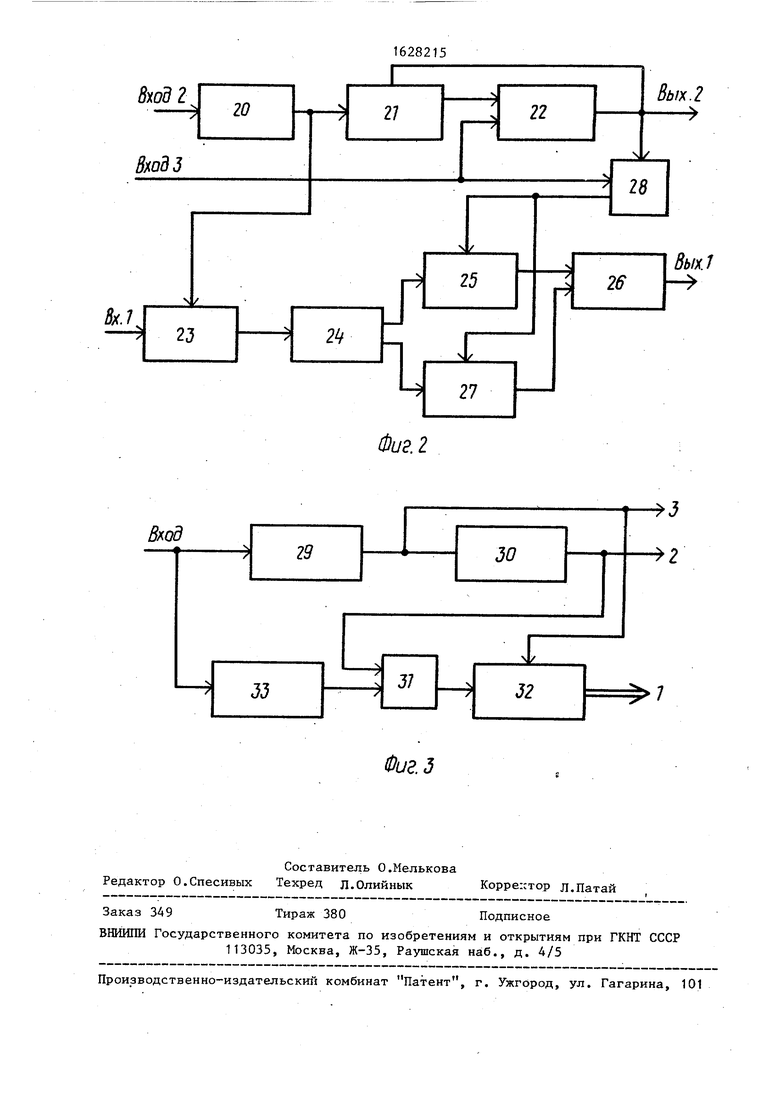

Измеритель 15 содержит детектор 29 несущей, одновибратор 30, элемент И 31, суммирующий счетчик 32, усилитель-ограничитель 33.

Приемопередающее устройство данных работает следующим образом.

При включении устройства все счетчики обнуляются. В режиме передачи на вход 1 блока поступает сигнал разрешения передачи уровня О, который снимает состояние сброса с блока 1, управляемого делителя 8 и счетчика 10, разрешая их работу. Одновременно на информационные входы блока 1 подается код скорости, который через i сумматор 2 без изменений (так как выход счетчика 11 равен О) поступает на управляемьй делитель 8 и стро - бируемый сигналом с блока 1, присутствующим в момент поступления первого информационного слова, зано- сится в управляющий делитель 8. На выходе управляющего делителя 8 устанавливается заданная частота тактовы сигналов, и модулятор 6 начинает передавать в канал связи служебную по-, следовательность кодов со значением О, поступающих на его вход с подключенного на шину О входа первого переключателя 3. По истечении установленного количества периодов тактовой частоты (10-50 бит) на выходе счетчика 10 возникает сигнал уровня 1, который заблокирует прохождение импульсов на свой счетный вход через элемент И 9, переключит первый переключатель 3 и разрешит блоку 1 прием данных от источника. Данные через блок 1, второй переключатель 5, кодер 4, первый переключатель 3 и модулятор 6 поступают в канал связи. При этом синхронизация обмена с источником осуществляется по входу 3 блока 1 (готов к приему). В кодере 4 к информационному слову добавляются контрольные биты для обнаружения ошибок при приеме данных. После завершения передачи блока данных источник данных снимает сигнал разрешения передачи по входу 1, что приводит к установке блоков 1 управляемого делителя 8 и счетчика 10 в исходное состояние.

В приемной части другого пункта принимаемая служебная последовательность поступает на детектор 29 и усилитель-ограничитель 33 на выходе детектора 29 с задержкой, определяемой постоянной времени детектора 29, появится сигнал уровня 1, который передним фронтом запустит одновибратор 30, формирующий сигнал длительности цикла измеренная частоты, и снимает сигнал установки суммирующего счетчика 32 в состояние переполнения. В течение длительности импульса одновибратора 30 усиленный и ограниченный по амплитуде канальный сигнал через элемент И 31 поступит на вход суммирующего счетчика 32. Прошедшее на вход суммирующего счетчика 32 число периодов канального сигнала вычтется из кода переполнения счетчика. По заднему фронту импульса одновибратора 30 процесс измерения завершается и происходит занесение кода суммирующего счетчика 32 в управляемьй делитель 13, который ранее был разблокирован сигналом детектора 29. На выходе управляемого делителя 13 возникает тактовая частота, соответствующая скорости передаваемых данных, и демодулятор 16 входит в

516282

синхронизм с принимаемым сигналом, . поддерживая своим выходом синхронизацию управляемого делителя 18. Данные начинают поступать через демодулятор 16 на декодер 17, который обнаруживает (или устраняет) ошибки в данных, возникающее из-за зашумленности канала связи С декодера 17 сигнал ошибки поступает на соответствую- JQ щий вход анализатора 14 и вместе с данными на блок 18 и далее на вход дешифратора 19 команд, а также на выход устройства. В анализаторе 14 выполняется подсчет количества оши- j 5 бок за один кадр данных (например, 8 байтов), а также за время анализа канала (1 цикл анализа - передача нескольких тясяч байтов), Если в од- ном кадре обнаружено ошибок более 20 некоторого порога, то такой кадр считается с групповой ошибкой, при меньшем не равном О числе ошибок - кадр с одиночными ошибками. Для этого сигналы ошибок просчитываются 25 счетчиком 23 за время одного периода кадровой частоты, поступающей на делитель с делителя 20. Этот сигнал стробирует выходы счетчика 23 и задним фронтом сбрасывает его в О.

В момент стробирования код счетчика 23 поступает на блок 24, на выходах которого наличие сигналов определяется результатом сравнения с по рого- вой-величиной, повышение которой воз буждает выход, подключенный к счетчику 25, если код счетчика 23 меньше т, но больше О, то возбуждается выход 24, подключенный к счетчику 27 (m E 1-10). Таким образом ре- зультаты анализа ошибок в каждом кад ре накапливаются в счетчиках 25 и 27. По завершению цикла анализа сигналом с выхода делителя 21 взводится триггер 22, выходной сигнал которого установит второй переключатель 5, передающий части данной станции в положение, соединяющее группу выходов шифратора 26 с входом кодера 4, и заблокирует работу делителей 20, 21. Когда направление передачи изменится и станция ранее принимавшая станет передающей, до срабатывания счетчика 10 в кодер 4 поступит код у1 команды изменения скорости с выхода. шифратора 26. При срабатывании счетчика 10 этот код поступит в модулятор 6 и передастся по каналу связи. Одновременно сигналом с выхода счет

Q 5 0 5

0

0 5 0

156

чика сбрасывается триггер 22, разблокируются и установятся в О делители 20 и задний фронт сигнала триггера 22 через элемент 28 сбросит в О счетчики 25, 27. Поступив на другую станцию, команда изменения скорости возбуждает один из двух выходов дешифратора 19 команд (так как команды отличаются от других передаваемых данных). В результате в счетчик 11 приращений добавится или вычтется единица. Когда вновь произойдет изменение направления передачи, код скорости, формируемый на выходе сумматора 2, будет уменьшен или увеличен в зависимости от кода счетчика 11 приращений, поступающего на второй вход сумматора 2. Соответственно уменьшится или увеличится скорость передачи данных.

Формула изобретения

делитель, демодулятор, декодер и блок сопряжения с приемником данных, выход генератора подключен к тактовому входу управляемого делителя, вход синхронизации которого подключен к одноименному выходу демодулятора, сигнальный вход которого объединен с сигнальным входом измерителя частот и является входом приемной сторо- ны, тактовый вход блока сопряжения подключен к выходу управляемого делителя, отличающееся тем, что, с целью повышения скорости передачи, введены на передающей стороне второй переключатель, счетчик приращений и сумматор, выходы которого подключены к входам -управляющего кода управляемого делителя, первая и вторая группы входов сумматора ПОДКЛЮ чены к соединенным между собой группе выходов блока сопряжения и первой группе входов второго переключателя, группа выходов которого подключена к входу кодера, вторая группа входов сумматора подключена к группе выходов счетчика приращений, а на приемной стороне введены анализатор ошибок и дешифратор команд, входы которого подключены к группе входов блока со- пряжения и являются первым выходом приемкой стороны, вторым и третьим выходами которой являются выходы управления приемом и синхронизации обмена, вход сброса и стробирования анализа- тора ошибок соответственно подключены к второму управляющему входу блока сопряжения передающей стороны и выходу управляемого делителя, сигнальный вход анализатора ошибок подклю- чен к соединенным между собой выходу сигнала ошибок декодера и сигнальным входом блока сопряжения, выходы управляющего кода и стробирую- щего сигнала анализатора ошибок под- ключены соответственно к второй группе входов и сигнальному входу второго переключателя, первый и второй выходы дешифратора команд соединены соответственно с суммирующим и

вычитающим входами счетчика приращений .

и счетчик одиночных ошибок, выход которого подключен к второму входу шифратора, выход которого являе ся выходом управляющего кода анализатора ошибок, второй выход блока сравнения подключен к сигнальному входу счетчика групповых ошибок, выход триггера подключен к управляющему входу делителя цикловой частоты и является управляющим выходом анализатора ошибок, выход делителя кадровой частоты подключен к входу стробирования и сброса счетчика ошибок, тактовый вход делителя кадровой частоты является тактовым входом, анализатора ошибок, вход сброса и стробирования триггера соединен с вторым входом элемента И и является управляющим входом анализатора ошибок, сигнальный вход счетчика ошибок является сигнальным входом анализатора ошибок.

Фиг. 2

Фиг.з

Авторы

Даты

1991-02-15—Публикация

1988-12-05—Подача