R-входы которого соединены с вторым и третьим входами селектора 2 грубого otc4eTa соответственно. Старт- стопный интерполятор 7 выполнен на элементе 16 ИСЮЮЧДЮиЩЕ 1ШИ, входы которого соединены с прямыми выходами RS-триггера 12 и D-триггера 13

селектора 2грубого отсчета. Выход

ла за счет повышения точности измере-|л. ...,,„,,„,,„.,„,,.„„,,„,.,

элемента 16ИСКЛЮЧАЮЩЕЕ ИЛИ соединен НИН интерполяционных интервалов меж, т

ционно-иэмерительнои технике и может быть использовано в автоматике, экспериментальной физике для измерения временных интервалов с высокой точностью.

Цель изобретения - повьпиение точности измерения временного интервас выходом старт-стопного интерполятора 7. Элемент 11 задержки выполнен в виде регистра 17 сдвига, С-вход которого соединен с выходом генератора 1 тактовых импульсов, а В-вход регистра 17 сдвига соединен с прямым выходом D-триггера 13 селектора 2 грубого отсчета. Прямой и инверсный выходы старшего разряда регистра 17 сдвига соединены с первым и вторым входами элемента I1 задержки. Первый вход блока 8 управления соединен с вторым выходом элемента 11 задержки, а второй вход блока 8 управления соединен с выходом генератора 1 тактовых импульсов. Пер- вьш выход блока 8 управления соединен с входом перезаписи регистра 4 памяти, а второй выход блока 8 управления соединен с установочным входом счетчика 3 грубого -отсчета и входом обнуления интегратора.

ду старт (стоп)-сигналами и тактовыми импульса14и и упрощение устройства.

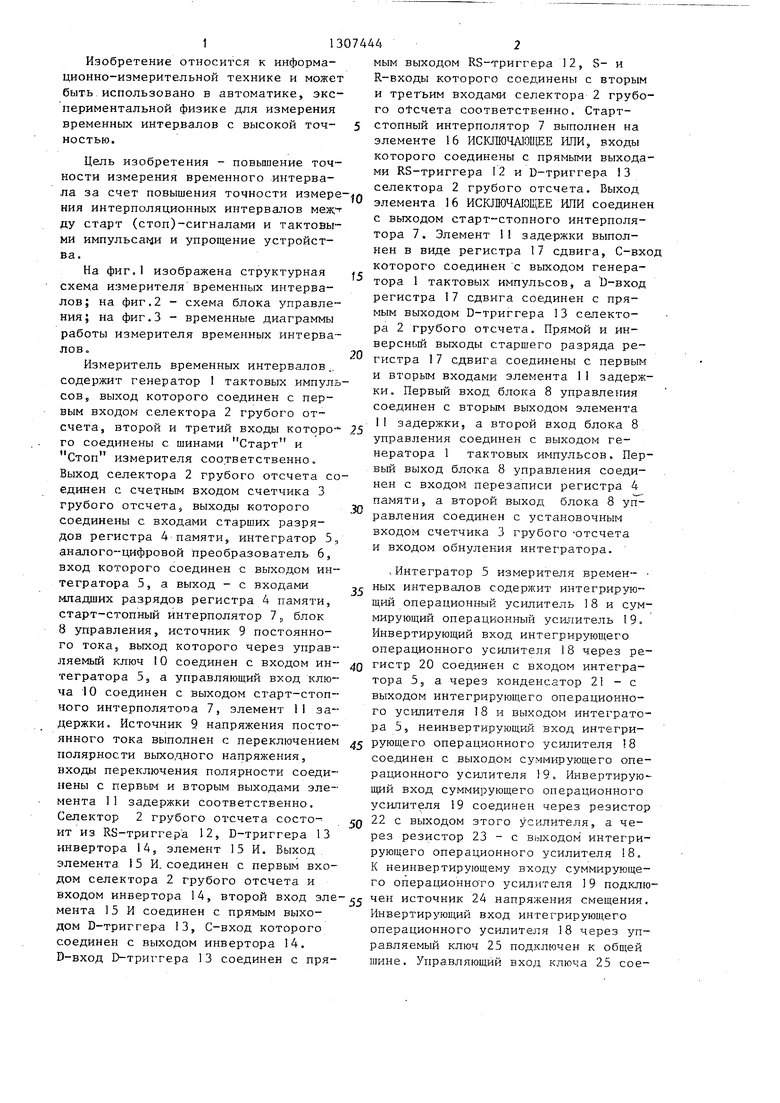

На фиг.1 изображена структурная схем.а измерителя временных интервалов; на фиг.2 - схема блока управления; на фиг.З - временные диаграммы работы измерителя временных интервалов.

Измеритель временных интервалов .. содержит генератор тактовых импульсов, выход которого соединен с первым входом селектора 2 грубого отсчета, второй и третий входы которо- го соединены с шинами Старт и Стоп измерителя соответственно. Выход селектора 2 грубого отсчета соединен с счетным входом счетчика 3

грубого отсчета, выходы которого соединены с входами старших разрядов регистра 4 памяти, интегратор 5., аналого-цифровой преобразователь 6, вход которого соединен с выходом интегратора 5, а выход - с входами младших разрядов регистра 4 памяти, старт-стопный интерполятор 7,, блок 8 управления, источник 9 постоянного тока, выход которого через управляемый ключ 10 соединен с входом гистр 20 соединен с входом интегра- тегратора 5, а управляющий вход клю- тора 5, а через конденсатор 21 - с ча 10 соединен с выходом старт-стоп- выходом интегрирующего операционно- ного интерполятора 7, элемент 11 за- го усилителя 18 и выходом интеграто- держки. Источник 9 напряжения посто- ра 5, неинвертирующий вход интегриянного тока выполнен с переключением рующего операционного усилителя 18

полярности выходного напряжения, входы переключения полярности соеди- 11ены с первым и вторым выходами элемента 11 задержки соответственно. Селектор 2 грубого отсчета состоит из RS-триггера 12, D-триггера 13 инвертора 14, элемент 15 И. Выход, элемента 15 И. соединен с первым входом селектора 2 грубого отсчета и

входом инвертора 14, второй вход эле-xj чен источник 24 напряжения смещения, мента 15 И соединен с прямым выхо- Р{нвертирующий вход интегрирующего дом D-триггер-а 13, С-вход которого операционного усилителя 18 через уп- соединен с выходом инвертора 14. равляемый ключ 25 подключен к обп1ей D-вход D-триггера 13 соединен с пря- шине. Управляющий вход ключа 25 соеэлемента 16ИСКЛЮЧАЮЩЕЕ ИЛИ соединен

с выходом старт-стопного интерполятора 7. Элемент 11 задержки выполнен в виде регистра 17 сдвига, С-вход которого соединен с выходом генератора 1 тактовых импульсов, а В-вход регистра 17 сдвига соединен с прямым выходом D-триггера 13 селектора 2 грубого отсчета. Прямой и инверсный выходы старшего разряда регистра 17 сдвига соединены с первым и вторым входами элемента I1 задержки. Первый вход блока 8 управления соединен с вторым выходом элемента 11 задержки, а второй вход блока 8 управления соединен с выходом генератора 1 тактовых импульсов. Пер- вьш выход блока 8 управления соединен с входом перезаписи регистра 4 памяти, а второй выход блока 8 управления соединен с установочным входом счетчика 3 грубого -отсчета и входом обнуления интегратора.

Интегратор 5 измерителя времен- ных интервалов содержит интегрирующий операционный усилитель 18 и суммирующий операционный усилитель 19. Инвертирующий вход интегрирующего операционного усилителя 18 через ре0

соединен с .выходом суммрфующего операционного усилителя 19. Инвертирую- ш;ий вход суммирующего операционного усилителя 19 соединен через резистор 22 с выходом этого усилителя, а через резистор 23 - с выходом интегрирующего операционного усилителя 18. К неинвертирующему входу суммирующего операционно го усилителя 19 подклю

динен с входом обнуления интегратора 5.

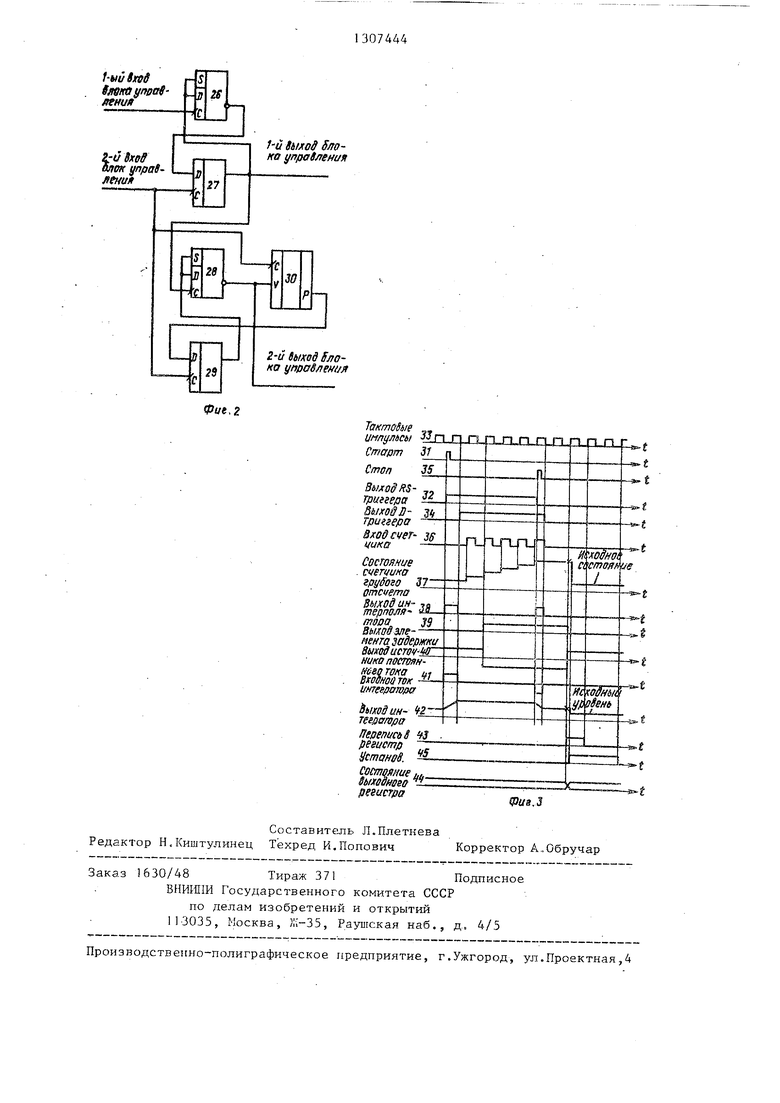

Блок 8 управления (фиг,2) содержит четыре триггера 26-29 и двоичный счетчик 30. Причем вход синхронизации первого триггера 26 соединен с первым входом блока 8 управления. . Входы синхронизации второго триггера 27, четвертого триггера 29 и двоичного счетчика 30 соединены с вторы входом блока управления.. Инверсный выход первого триггера 26 соединен с инфЬрмационным входом второго тригге ра 27, а прямой выход второго триггера 27 соединен с первым выходом блока 8 управления, с информационным и установочным входами первого триггера 26 и с входом синхронизации третьего триггера 28. Инверсный выход третьего триггера 28 соединен с входом разрешения счета двоичного счетчика 30 и с вторым в.ыходом блока 8 управления. Выход переноса двоично го счетчика 30 соединен с информационным входом четвертого триггера 29. Прямой выход четвертого триггера 29 .соединен с установочным и информационным входами третьего триггера 28. Первый 26 и второй 27 триггеры образуют генератор одиночного импульса, а третий 28 и четвертый 29 триггеры и двоичный счетчик 30 образует таймер..

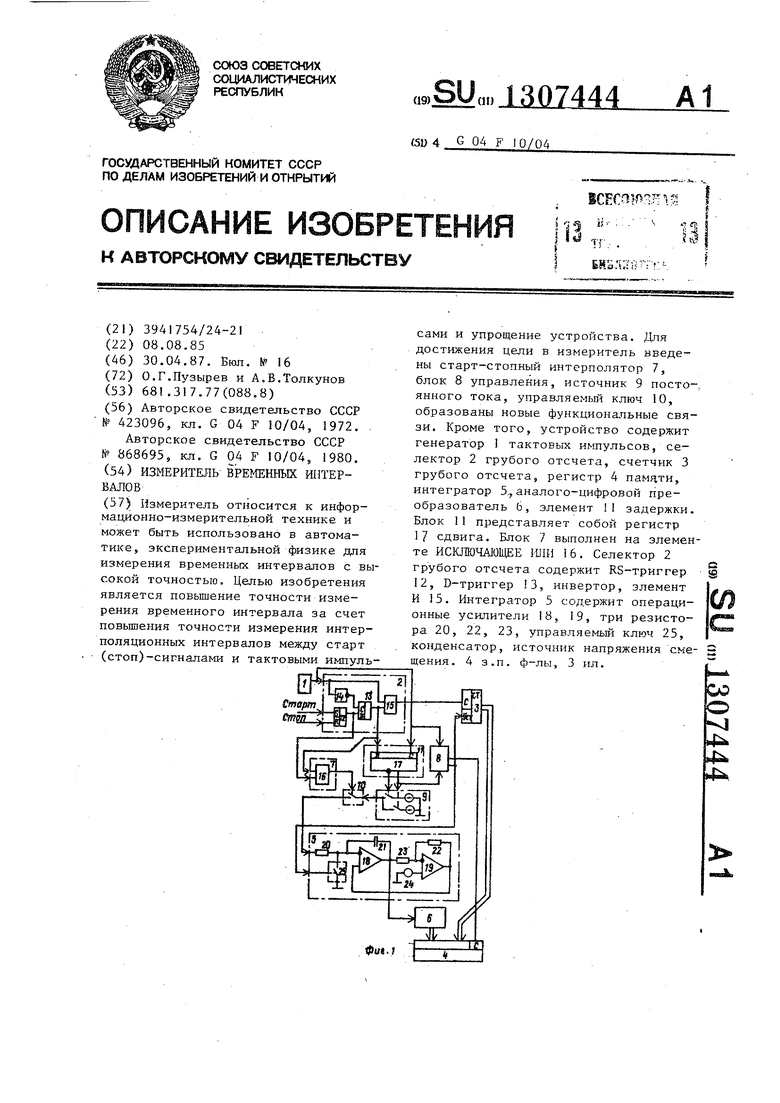

Измеритель временных интервалов - работает следующим образом ().

При поступлении стартового импульса 31 RS-т риггер 12 селектора 2 грубого отсчета меняет состояние 32 с нулевого на единичное. Первым же тактовым импульсом 33, следующим за стартовым импульсом 3.1, D-тригрер 13 селектора 2 грубого отсчета переводится в единичное состояние (фиг.З, 34). По прих оду стопового импульса 35 RS-триггер 12 переключается в нулевое состояние (фиг,3, 32), а D-три гер 13 переключается в нулевое состояние первым тактовым импульсом 33, прищедшим после стопового импульса 35. Во время нахождения D-тригге- ра 13 в единичном состоянии 34 через элемент I5 И селектора 2 грубого отсчета на счетный вход счетчика 3 грубого отсчета поступают импульсы 36. Состояние счетчика 3 грубого отсчета (сигнал 37) по окончании поступления импульсов 36 на счетный вход определяется количеством-импульсов 36, т .е

0

5

0

5

О

0

5

45

5

временем между стартовым 31 и стоповым 35 импульсами. Старт-стопный интерполятор 7 формирует .стартовый и стопов.ый интерполяционные интервалы 38. Длительности интерполяционных интервалов 38 равны временам между стартовым импульсом 31 (стоповым им- .пульсом 35) и первым следующим за ним тактовым импульсом 33. Так как времена прихода стартового импульса ЗГ и стопового импульса 35 не синхронизированы с тактовыми импульсами 33, то длительности интерполяционных интервалов 38 лежат в пределах от нуля до периода тактовых импульсов 33. Сигнал 39 на выходе элемента 11 задержки, управляющего переключением полярности (сигнал 40) источника 9 постоянного тока, задержан относительно сигнала 34 на выходе D-триг- гера 13 селектора 2 грубого отсчета на время, меньшее чем минимальный измеряемьй временной интервал, но . большее чем время суммарной задержки старт-стопного интерполятора 7 и ключа 10. Поэтому переключение полярности источника 9 происходит между замыканиями ключа 10, соответствующими стартовому и стоповому интерполяционным интервалам. Таким образом, во время стартового интерполяционного интервала 38 конденсатора 21 интегратора 5 заряжается входным током 41 интегратора 5, а во время стопового интерполяционного интерва- ла 38 разряжается. Напряжение 42 на выходе интегратора 5 по окончании стопового интерполяционного интервала 38 и, в свою очередь, код на выходе аналого-цифрового преобразователя 6 зависят от разности между длительностями 38 стартового и стопового интерполяционных интервалов. По заднему фронту сигнала 39 на пер-; вом выходе элемента 11 задержки блок 8 управления формирует сигнал 43 переписи инфо рмации из счетчика 3 грубого отсчета в старшие разряды выходного регистра 4, а из аналого- цифрового преобразователя 6 в младшие разряды выходного регистра 4. Информация 44 в выходном регистре 4 после прихода импульса переписи 43 соответствует длительности измеряемого временного интервала. Затем блок 8 управления формирует сигнал 45, устанавливающий счетчик 3 грубого отсчета в исходное состояние

(сигнал) 37 и замыкающий клкзч 25 интегратора 5, которьш разряжает конденсатор 21 интегратора 5 ,до исходного уровня (сигнал 42). Измеритель временных интерв.алов возвращается в исходное состояние.

Блок 8 управления работает следующим образом, . После включения питания за счет обратной связи, существующей между прямым выходом триггера 27 и S-вхо- дом триггера 26, триггер 26 устанавливается в единичное состояние, а триггер 27 устанавливается, в нулевое состояние за счет обратной связи, существующей между выходом переноса счетчика 30 и S-входом триггера 28 через триггер 29, триггер 28 устанавливается в единичное состояние, счет- . чик 30 в нулевое состояние, триггер 29 в нулевое состояние.

25

30

35

40

По отрицательному фронту сигнала 9, поступающего на С-вход триггера 6, триггер 26 переключается в нуле- .ое состояние и на D-входе триггера . 7 устанавливается уровень логичесой единицы. Теперь по положительноу фронту тактового импульса 33, потупающего на С-вход триггера 27, риггер 27 переключается в единичое состояние. На первом выходе блоа 8 управления появляется импульс ереписи 43, а на S-входе триггера 26 устанавливается уровень логической единицы, что приводит к переклюению триггера 26 в единичное состояние, и на D-входе триггера 27 устанавливается уровень логического нуля. Теперь по положительному фронту очередного тактового импульса 33 триггер 27 переключается в нулевое состояние и прекращается импульс переписи 43 на первом выходе блока 8 управления. Таким образом,.г, Ф о формирователь одиночного импульса, образованный триггерами 26 и 27, возвращается в исходное состояние.

По положительному фронту сигнала- 43 на первом выходе блока 8 управ- , ления происходит перепись информации, из счетчика 3 грубого отсчета в старшие разряды выходного регистра 4, а из аналого-цифрового преобразователя 6 в младшие разряды выходного регистра 4 „

По положительному фронту сигнгша 13, поступ ающего также на С-вход триггера 28, триггер -28 переключается

20 в ед выхо уров

сигн блок поло тово С-вх ключ чие де с сост пуль

ный возв

втор чик ется 37). ра разр НсШ

50

лрв импу с п и с выхо вход выхо с стар инт с вх зов тем

3074446

в нулевое состояние, что приводит к появлению уровня логической единицы на V-входе счетчика 30, а на втором выходе блока 8 управления начинает

Ф о

действовать сигнал 45 Установ. Теперь по положительному фронту каждого тактового импульса 33, поступающего с второго входа блока 8 управления на С-вход счетчика 30, счетчик

30 изменяет свое внутреннее состояние до тех пор, пока на его выходе переноса не появится уровень логической единищ.1. По положительному фронту следующего тактового импульса 33

счетчик 30 переходит в нулевое состояние, а триггер 29 - в единичное состояние. Это приводит к появлению уровня логической единицы на S-входе триггера 28. Триггер 28 переключается

в единичное состояние, на инверсном выходе триггера 28 устанавливается уровень логкгческого нуля, и действие

сигнала 45 Установ на втором выходе блока 8 управления прекращается. По . положительному фронту следующего тактового .импульса 33, поступающего на С-вход триггера 29, триггер 29 переключается в -нулевое состояние. Нали- , чие уровня логического нуля на V-входе счетчика 30 запрещает изменение состояния счетчика 30 по тактовым импульсам .33.

Таким образом, таймер, образован- ный триггерами 28, 29 и счетчиком 30, возвращается в исходное состояние.

Во время действия сигнала 45 на втором выходе блока 8 управления счетчик 3 грубого отсчета устанавливается, в исходное состояние (сигнал 37)., замыкается ключ 25 интегратора 5 и конденсатора 21 интегратора 5 разряжается до исходного уровня (сиг- НсШ 42). . .

рмула изобретения

.г, Ф о

50

I..Измеритель временных интерва- лрв, содержащий генератор тактовых импульсов, выход которого соединен с первыми входами элемента задержки и селектора грубого отсчета, первый выход которого соединен со счетным входом счетчика грубого отсчета, выходы которого соединены с входами с старших разрядов регистра памяти, интегратор, выход которого соединен с входом аналого-цифрового преобразователя, о тличающийся тем, что, с целью повышения точное

ти измерений и упрощения измерителя, в него введены старт-стопный интерполятор, блок управления, источник постоянного тока, выполненный G возможностью переключения полярности выходного напряжения, и управляемый ключ, причем второй выход селектор грубого отсчета подключен к первому входу старт-стопного интерполятора, второй вход которого подключен к третьему выходу селектора грубого отсчета и второму входу элемента задержки, первый выход которого соединен с первым управляющим входом источника постоянного тока, второй управляющий вход которого соединен с вторым выходом элемента задержки и первым входом блока управления, второй вход которого подключен к выходу -генератора тактовых импульсов, а первый выход - к входу перезаписи регистра памяти, входы младших разрядов которого соединены с выходами аналого-цифрового преобразователя, выход источника постоянного тока соединен с входом управляемого ключа, управляющий вход которого соединен с выходом старт-стопного интерполя- тора, а выход - с входом интегратора вход обнуления которого подключен к второму выходу блока управления и установочному входу счетчика грубого отсчета, шины Старт и МСтоп подключены соответственно к второму и третьему входам селектора грубого отсчета.

2, Измеритель по и. 1, о т л и- чающийся тем, что элемент задержки представляет собой регистр сдвига. С- и D-БХоды которого явля-

ются соответственно первым и вторым входами элемента задержки, а ин- версньш и прямой выходы старшего разряда - первым и вторьш выходами соответственно элемента задержки.

3. Измеритель по п. 1, о т л и - чающийся тем, что старт-стопfO

15

;

40

074448

ный интерполятор выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются входами интерполятора, а выход элемента ИСКЛЮЧАЮЩЕЕ 1ШИ - его выходом.

4,Измеритель по п. 1, отличающийся тем, что селектор грубого отсчета содержит RS-триггер, D-триггер, инвертор и элемент И, выход которого соединен с выходом селектора, а S- и R-входы RS-триггера являются соответственно вторым и третьим входами селектора, первый вход которого подключен к входу инвертора и первому входу элемента И, второй вход которого подключен к третьему выходу селектора и прямому выходу D-триггера, второй выход селектора соединен с прямым выходом RS-триггера и D-входом D-триггера, С-вход которого подключен к выходу инвертора.

5.Измеритель по п. 1, о т л и - ч-ающийся тем, что интегратор содержит два операционных усилителя, .три резистора, управляемьй ключ, конденсатор и источник напряжения смещения, причем вход интегратора- через первый резистор подключен к входу управляемого ключа и инвертирующему входу первого операционного усипу- теля, который через конденсатор соединен с выходом первого операционного усилителя и выходом интегратора, выход первого операционного усилителя через второй резистор подключен к инвертирующему входу второго операционного усилителя, который через третий резистор соединен с выходом второго операционного усилителя и неинвертирующим входом первого операционного усилителя, .выход источника напряжения смещения соединен с неинвертирующим входом второго опера45 ционного усилителя, управляющий вход управляемого ключа соединен с входом обнуления интегратора.

20

25

30

35

t-uu ixffd

вмнвуг а

яения

I uSbixoS Sno- KQ 1/п(}айления

2-й Sbfxod Saa- Ho упообления

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРПОЛЯТОР ПРЯМОГО КОДИРОВАНИЯ ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛОВ ВРЕМЕНИ | 2011 |

|

RU2467371C1 |

| Цифровой измеритель временных интервалов | 1984 |

|

SU1228065A1 |

| Цифровой измеритель временных интервалов | 1981 |

|

SU966662A1 |

| Способ однодорожечной старт-стопной магнитной записи-воспроизведения | 1984 |

|

SU1278940A1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 2014 |

|

RU2561999C1 |

| Интерполяционный измеритель вре-МЕННыХ иНТЕРВАлОВ | 1979 |

|

SU819790A1 |

| Многоканальный интерполяционный измеритель временных интервалов | 1982 |

|

SU1027695A1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| Устройство для многоканальной магнитной записи и воспроизведения последовательности импульсов | 1982 |

|

SU1026156A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307443A1 |

Измеритель относится к информационно-измерительной технике и может быть использовано в автоматике, экспериментальной физике для измерения временных интервалов с высокой точностью. Целью изобретения является повьшение точности измерения временного интервала за счет повышения точности измерения интерполяционных интервалов между старт (стоп)-сигналами и тактовыми импульсами и упрощение устройства. Для достижения цели в измеритель введены старт-стопный интерполятор 7, блок 8 управления, источник 9 посто-, янного тока, управляемый ключ 10, образованы новые функциональные связи. Кроме того, устройство содержит генератор 1 тактовых импульсов, селектор 2 грубого отсчета, счетчик 3 грубого отсчета, регистр 4 памдти, интегратор 5,, аналого-цифровой преобразователь 6, элемент 11 задержки. Блок 11 представляет собой регистр 17 сдвига. Блок 7 выполнен на злемен- те ИСКЛЮЧАЮЩЕЕ ШШ 6. Селектор 2 грубого отсчета содержит RS-триггер 12, D-триггер 3, инвертор, элемент И 15. Интегратор 5 содержит операционные усилители 18, 19, три резистора 20, 22, 23, управляемьш ключ 25, конденсатор, источник напряжения смещения. 4 з.п. ф-лы, 3 ил. с Фч.1 т

Составитель Л.Плетнева Редактор Н.Киштулинец Техред И,Попович Корректор А„0бручар

Заказ 1630/48 Тираж 371Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, /li-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1972 |

|

SU423096A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Двухшкальный измеритель временных интервалов | 1980 |

|

SU868695A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-04-30—Публикация

1985-08-08—Подача