Изобретение относится к области измерительной техники и может быть использовано в экспериментальной физике, а также в других областях науки и техники при измерении интервалов времени с помощью двухотсчетных измерительных устройств, т.е. устройств, включающих в себя интерполятор.

При создании двухотсчетных измерителей интервалов времени прямого кодирования, содержащих генератор тактовой частоты, счетчик канала грубого отсчета, схему фазирования стартового/стопового сигнала с периодом тактовой частоты Т0 и интерполятор, всегда возникают вопросы повышения точности интерполяции и вопросы о процедуре совмещения шкал грубого и точного отсчетов как на физическом (аппаратном), так и на программном уровнях.

Достижение предельной точности измерения, определяемой техническим решением построения интерполятора при конечном быстродействии выбранной элементной базы, и степень сложности задачи согласования шкал грубого и точного отсчетов зависят от типа интерполяторов, простейшими из которых являются интерполяторы прямого кодирования, т.е. интерполяторы без промежуточных преобразований интерполируемых интервалов времени, например преобразований вида время→время→код либо время→напряжение→код.

Известно устройство для измерения интервала времени [2], включающее кроме последовательно соединенных опорного генератора импульсов, элемента И, счетчика импульсов, а также триггера, выходом соединенного с оставшимся входом элемента И, последовательную цепь элементов задержки, подключенную к выходу опорного генератора импульсов. Выходы всех элементов задержки через соответствующие дополнительные элементы И, вторые входы которых подключены к выходу триггера, и соответствующие триггеры присоединены к входам шифратора. На выходах шифратора в процессе измерения образуются значения младших разрядов результата измерения. В данном устройстве с помощью последовательной цепи элементов задержки образована субшкала отсчета времени с меньшим шагом квантования времени, за счет чего повышается точность измерения интервала времени. Однако данный аналог имеет погрешность, связанную со старт-стопным режимом работы опорного генератора. В таком режиме не может работать точный кварцевый генератор, а в релаксационном генераторе трудно обеспечить высокую точность и стабильность опорной частоты. Дополнительную погрешность вносят элементы задержки, времена задержки которых могут различаться ввиду технологического разброса.

Известен временной интерполятор [3], содержащий счетчик импульсов и секционированную линию задержки, входы которых соединены с общим зажимом опорных сигналов. Устройство включает регистр в виде множества триггеров с общими информационными и сбросовыми входами, причем синхронизирующие входы триггеров соединены с соответствующими промежуточными отводами линии задержки. Кроме того, в схему входит постоянное запоминающее устройство, которое служит преобразователем термометрического кода регистра в двоичный код. Общее время задержки сакционированной линии задержки равно одному опорному периоду. Запуск устройства осуществляется синхронизированным с опорным сигналом стартовым импульсом, который разрешает работу счетчика импульсов. Одновременно опорные сигналы распространяются по линии задержки. В момент поступления стопового импульса счетчик импульсов фиксирует число полных опорных периодов, уложившихся в измеряемый интервал. В итоге счетчик отражает старшие биты результата измерения, а постоянное запоминающее устройство - младшие биты. Погрешность измерения определяется в данном устройстве временем задержки одной секции линии задержки, что существенно меньше опорного периода. Кроме того, имеется дополнительный источник погрешности преобразования из-за возможней неравномерности задержки отдельных секций линии задержки.

Фазовый интерполятор прямого кодирования [1], который принят в качестве прототипа, состоит из К триггеров D-регистра, D-входы всех К триггеров соединены между собой попарно через К-1 элементов задержек, причем D-вход первого триггера соединен с источником последовательности тактовой частоты, С-входы объединены между собой и соединены с источником стартового/стопового сигнала. Поскольку интервалом времени, подлежащим интерполяции, является период тактовой частоты Т0, очевидно, что время единичной задержки ΔT должно быть ΔТ<Т0 и что ΔТ определяет абсолютную точность при регистрации положения на временной шкале стартового/стопового сигнала, активизирующего триггеры по С-входам с активными уровнями на их D-входах. Двоичный код о положении стартового/стопового сигнала формируется внешним D-входовым приоритетным шифратором, соединенным своими входами с соответствующими выходами триггеров интерполятора. Реализация схемотехники данного интерполятора с использованием современной технологии представляет программируемую структуру полупроводниковых логических элементов со всеми присущими им характеристиками (быстродействие, конечные пороги включения/выключения, гистерезис). В этих реальных условиях при стремлении минимизировать отношение ΔТ/Т0 (с целью повышения точности интерполяции) наступает ограничение, когда при реально существующей дифференциальной нелинейности (из-за реальных неравенств (ΔТ≠ΔТ2……±ΔТк-1), а также при отклонении скважности в последовательностях тактовой частоты от идеального меандра (из-за гистерезиса пороговых элементов задержек) нарушается монотонность характеристики дискретизации интервала времени, что приводит к катастрофической ошибке.

Для фазового интерполятора прямого кодирования согласование шкал на физическом уровне будет выполнятся автоматически, если (ΔТ1=ΔТ2…ΔТк-1=ΔТ и К*ΔТ=Т0. Приближение реалий к идеалу - есть содержание технической задачи согласования шкал. Очевидно, что интерполятор, при использовании которого не требуется решать такую задачу, имеет самую высокую, с точки зрения эргономики, характеристику и, естественно, предпочтителен в практике создания двухотсчетных измерителей интервалов времени.

Задачей данного изобретения является улучшение динамических и эргономических характеристик интерполятора прямого кодирования, в частности, достижение гарантированной монотонности характеристики дискретизации интерполируемого интервала времени при предельном быстродействии элементной базы и автоматическом совмещении шкал точного и грубого отсчетов в двухотсчетных измерительных устройствах.

Поставленная задача достигается путем совмещения функций узлов известных фазовых интерполяторов прямого кодирования (таких как: дискретизация интерполярируемого интервала времени с помощью специально формируемых сдвинутых по фазе последовательностей тактовой частоты канала грубого отсчета, регистрация положения стартового/стопового сигнала на шкале точного отсчета и хранение результата регистрации) в каждом функциональном элементе предлагаемого интерполятора - триггере.

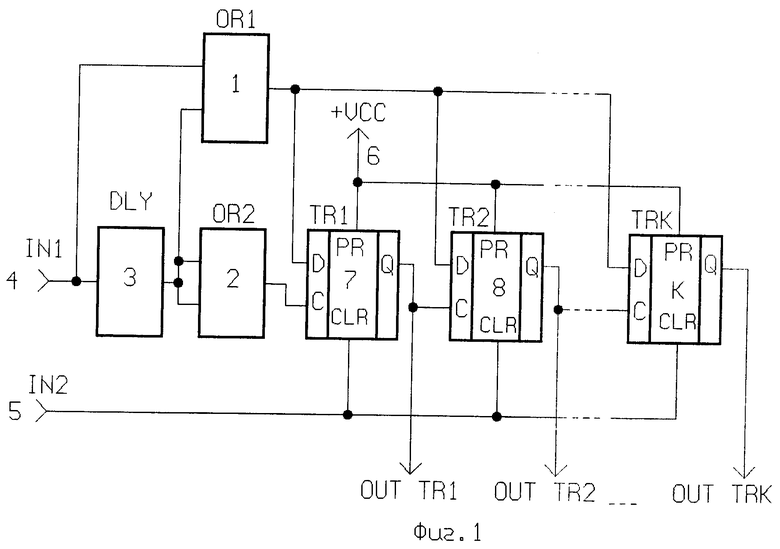

Предлагаемый интерполятор прямого кодирования для измерения интервалов времени (фиг.1) содержит D-регистр из К триггеров TR, один неинверсный элемент задержки DLY логического сигнала, а также два двухвходовых неинверсных элемента логического суммирования OR1 и OR2, при этом К D-триггеры TR последовательно соединены между прямым выходом предыдущего триггера с С-входом последующего триггера, один вход первого логического элемента OR1 и вход элемента задержки DLY объединены между собой и соединены с первым входом интерполятора IN1 для подключения внешнего источника интерполируемого интервала времени, выход элемента задержки DLY соединен с другим входом первого логического элемента OR1 и с двумя объединенными между собой входами второго логического элемента OR2, выход первого логического элемента OR1 соединен с объединенными между собой D-входами триггеров TR D-типа, а выход второго логического элемента OR2 - с С-входом первого триггера TR1, PR-входы предустановки триггеров TR D-типа объединены между собой и соединены с источником питания Vcc, CLR-входы установки исходного состояния триггеров TR D-типа объединены между собой и образуют второй вход интерполятора IN2 для подключения внешнего источника CLR-сигнала отрицательной полярности, прямые выходы триггеров TR соединены с соответствующими выходами OUTTR интерполятора.

На фиг.1 представлена принципиальная схема интерполятора прямого кодирования для измерения интервалов времени согласно настоящему изобретению:

1, 2 - два двухвходовых неинверсных элемента логического суммирования - OR1 и OR2;

3 - один неинверсный элемент задержки логического сигнала - DLY;

4 - первый вход интерполятора IN1;

5 - второй вход интерполятора IN2;

6 - источник питания Vcc;

7, 8,.…К - триггеры TR D-типа.

Принцип работы предлагаемого интерполятора прямого кодирования заключается в следующем. В исходном состоянии на D-входах триггеров TR, С-входе первого триггера TR1, на прямых выходах триггеров TR и, следовательно, на всех выходах ОUТ TR интерполятора уровни соответствуют логическому нулю. При поступлении от внешнего источника интерполируемого интервала времени в виде логического сигнала положительной полярности и длительностью от момента поступления стартового/стопового сигнала до момента фазирования его с началом периода тактовой частоты, используемой в канале грубого отсчета измерителя времени, на D-входах всех триггеров TR устанавливается уровень логической единицы. Его продолжительность во времени формируется на выходе первого логического элемента OR1 в результате логического суммирования прямого сигнала интерполируемого интервала времени и задержанного на элементе задержки DLY. С выхода второго логического элемента OR2 по переднему фронту задержанного сигнала интерполируемого интервала времени активизируется по С-входу первый триггер TR1, что приводит к последовательной активизации других триггеров на протяжении задержанного интерполируемого интервала времени. При последовательном во времени переходе триггеров в активное состояние осуществляется дискретизация задержанного интерполируемого интервала времени до его окончания с шагом, равным задержке триггера как функционального элемента. Очевидно, что характеристика дискретизации при этом принципиально не может быть немонотонной. Позиционный код результата дискретизации хранится триггерами TR до поступления от внешнего источника CLR-сигнала отрицательной полярности. Внешним приоритетным шифратором, подключенным к выходам интерполятора, позиционный код может быть преобразован в двоичный. Поскольку процесс дискретизации осуществляется на протяжении интерполируемого интервала времени, окончание которого соответствует моменту начала периода тактовой частоты, используемой в канале грубого отсчета измерителя времени, задача согласования шкал каналов точного и грубого отсчетов на физическом уровне не возникает.

Заметим, что число триггеров TR интерполятора находится в прямой зависимости от длительности интерполируемого интервала времени и от времени задержки единичного триггера интерполятора. При этом абсолютная точность интерполяции ограничивается предельным быстродействием триггеров TR. Длительность интерполируемого интервала времени t может находиться в пределах 0≤t≤T0 либо Т0≤t≤2T0 в зависимости от выбранной схемы фазирования стартового/стопового сигнала в канале грубого отсчета - с использованием одного триггера (0<t<То) либо двух триггеров (Т0≤t≤2T0).

Принципиальная схема предлагаемого интерполятора реализована на кристалле программируемой микросхемы EP2C2000240C8N, в которой переход D-триггеров TR из одного состояния в другое составил 1нсек. При этом проблем с монотонностью характеристики дискретизации интерполируемого интервала времени, равного периоду тактовой частоты опорного генератора грубого канала Т0=25 нсек, и согласования шкал не возникало.

Литература

1. Л.Вихарев. Микросхемы для прецизионного измерения. http://www.compitech.ru.

2. Шляндин В.М. Цифровые измерительные преобразователи и приборы. М.: Высшая школа, 1973.

3. Патент США №4439046.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Цифровой хронометр | 1989 |

|

SU1693588A1 |

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549248C1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Преобразователь время-код | 1975 |

|

SU551801A1 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

| Конвейерно-циклический временной интерполятор | 1980 |

|

SU951691A1 |

| Устройство интерполяции видеосигнала | 1987 |

|

SU1425872A1 |

Изобретение относится к области измерительной техники и может быть использовано в экспериментальной физике, а также в других областях науки и техники при измерении интервалов времени с помощью двухотсчетных измерительных устройств, т.е. устройств, включающих в себя интерполятор. Изобретение направлено на повышение точности измерения интервалов времени, что обеспечивается за счет того, что в интерполятор прямого кодирования для измерения интервалов времени, включающий набор триггеров TR D-типа, неинверсный элемент задержки DLY логического сигнала, введены два двухвходовых неинверсных элемента логического суммирования OR1 и OR2, причем один вход первого неинверсного элемента логического суммирования OR1 и вход неинверсного элемента задержки логического сигнала DLY объединены и являются первым входом интерполятора для подключения внешнего источника сигнала интерполируемого интервала времени положительной полярности, а выход неинверсного элемента задержки DLY логического сигнала соединен с другим входом первого неинверсного элемента логического суммирования OR1 и с объединенными между собой двумя входами второго неинверсного элемента логического суммирования OR2, выход которого соединен с С-входом первого триггера TR1 D-типа. При этом все триггеры TR D-типа последовательно соединены прямым выходом каждого предыдущего триггера с С-входом последующего триггера, D-входы всех вышеупомянутых триггеров объединены между собой и соединены с выходом первого неинверсного элемента логического суммирования OR1, PR-входы предустановки вышеупомянутых триггеров объединены между собой и соединены с источником питания Vcc, a CLR-входы исходного состояния вышеупомянутых триггеров объединены и образуют второй вход интерполятора для подключения внешнего источника CLR-сигнала отрицательной полярности, прямые выходы вышеупомянутых триггеров образуют соответствующие выходы OUT TR интерполятора. 2 з.п. ф-лы, 1 ил.

1. Интерполятор прямого кодирования для измерения интервалов времени, включающий набор триггеров TR D-типа, неинверсный элемент задержки DLY логического сигнала, отличающийся тем, что в него введены два двухвходовых неинверсных элемента логического суммирования OR1 и OR2, причем один вход первого неинверсного элемента логического суммирования OR1 и вход неинверсного элемента задержки логического сигнала DLY объединены и являются первым входом интерполятора для подключения внешнего источника сигнала интерполируемого интервала времени положительной полярности, а выход неинверсного элемента задержки DLY логического сигнала соединен с другим входом первого неинверсного элемента логического суммирования OR1 и с объединенными между собой двумя входами второго неинверсного элемента логического суммирования OR2, выход которого соединен с С-входом первого триггера TR1 D-типа, причем все триггеры TR D-типа последовательно соединены прямым выходом каждого предыдущего триггера с С-входом последующего триггера, D-входы всех вышеупомянутых триггеров объединены между собой и соединены с выходом первого неинверсного элемента логического суммирования OR1, PR-входы предустановки вышеупомянутых триггеров объединены между собой и соединены с источником питания Vcc, a CLR-входы исходного состояния вышеупомянутых триггеров объединены и образуют второй вход интерполятора для подключения внешнего источника CLR-сигнала отрицательной полярности, прямые выходы вышеупомянутых триггеров образуют соответствующие выходы OUT TR интерполятора.

2. Интерполятор прямого кодирования по п.1, отличающийся тем, что число триггеров TR D-типа выбирают из отношения максимальной длительности интерполируемого интервала времени t положительной полярности, обеспечиваемого внешним источником сигнала, к времени перехода триггера из одного состояния в другое - к Δt, определяемое предельным быстродействием вышеупомянутых триггеров.

3. Интерполятор прямого кодирования по п.1, отличающийся тем, что время задержки Δtd неинверсного элемента задержки DLY выбирают из соотношения Δtd≥Δt.

| ВИХАРЕВ Л.В | |||

| МИКРОСХЕМЫ ДЛЯ ПРЕЦИЗИОННОГО ИЗМЕРЕНИЯ, http://www.compitech.ru | |||

| Преобразователь напряжение-код | 1986 |

|

SU1317660A1 |

| 1971 |

|

SU416861A1 | |

| US 2009154300 A1, 18.06.2009 | |||

| US 2011040509 A1, 17.02.2011. | |||

Авторы

Даты

2012-11-20—Публикация

2011-05-30—Подача