2. Измеря вль по п. 1,о т л и чающийся тем что интерполя тор содержит хронизатор К групп одновибраторов и К дешифраторов , причем первые входы дешифраторов подключены к соответствующим информационным входам интерполятора, вторые входы дешифраторов объединены и подключены к первому входу хрониэатора, второй выход которого является выходом интерполятора, а группа выходов хронизатора подключена к группе входов всех дешифраторов,.входы каждого дешифратора подключены к входам соответствующей группы одновибраторов, группы выходов К групп -одновибраторов являются к группами выходов интерполятора.

3. Измеритель по п; 1, о т личаюадийся тем, что накопитель содержит элемент ИЛИ; вы|ходной регистр, счетчик адреса ,цешифратор адреса и /А линеек памя|ти, каждая из которых содержит элемент ИЛИ, усилитель, элемент И- и группу из Р последовательно соединенных регистров, причем инверсный выход разряда занятости Р-го регистра подключен к управляющему входу (Р -1)-го регистра, где Р 1, 2,.., Р вход разряда занятости первого регистра соединен с вйходом элемента ИЛИ, К разрядных входов

первого регистра соединенна с cooTBeT- ствуимцими входами элемента ИЛИ, входы которого в соответствии с номе- ром К , где К 1,2... подключены к i-входам К групп входов накопителя, дополнительная группа входов которого соединена с дополнительными разрядньади входами всех первых регистров в каждой линейке и первый вход накопителя подключен к входам всех М. усилителей, выход i -го усилителя соединен с входами синхронизации всех Р регистров i-и лйнейки памяти, первая и вторая группу разрядных выходов всех М последних регистров соединены соответственно С первой и второй группами разрядных входов выходного регистра, выходы разрядов которого являются выходами накопителя, а дополнительные входы выходного регистра соединены с выходами счетчика адреса И входами Дешифратора адреса, i выход которого соединен с первыми входами М элеглентов И, вторые входы которых подключены к прямым выходам разряда занятости последнего регистра, управляющий вход которого соединен с выходом , i-го элемента и, выходы всех М элементов И через элемент ИЛИ подключены к управлякяцему входу выходного регистра, счетный вход сче тчика адреса соединен с вторым входом накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

1

Р зобретение относится к информационно-измерительной технике и может быть использовано в информационно-измерительных системах ядерной и атомной физики и техники, в системах времяимпульсной метрологии, оптической и лазерной локации, в радио- и гидролокации, в навигации и технике связи.

Известен интервалометр с фемтосекундным разрешением, который измеряет интервалы времени методом, последовательного счета с времяам-плитудной интерполяцией и усреднение ем 13 .

Однако данный интервалометр ра- , ботает с увеличением масштаба времени на несколько порядков, что приводит к соответствующему увеличению затрат времени на .одно преобразование. Кроме того, при работе, .с потоками информационных сигналов большой интенсивности имеет место потеря измерительной информации.

известен также интерполяционный мамвритель временных интервалов в

кбтбром для снижения погрешностей измерения вводится автоматическая цифровая коррекция аддитивной, мультипликативной и нелинейной погрешностей путем кусочно-линейной аппроксимации передаточной характеристики преобразователя масштаба времени 23.

К недостаткам указанного измерителя относятся большие затраты времени на масштабные преоб.разования, относительно малую загрузку и дополнительные затраты времени и оборудования на обеспечение работы в режиме калибровки.

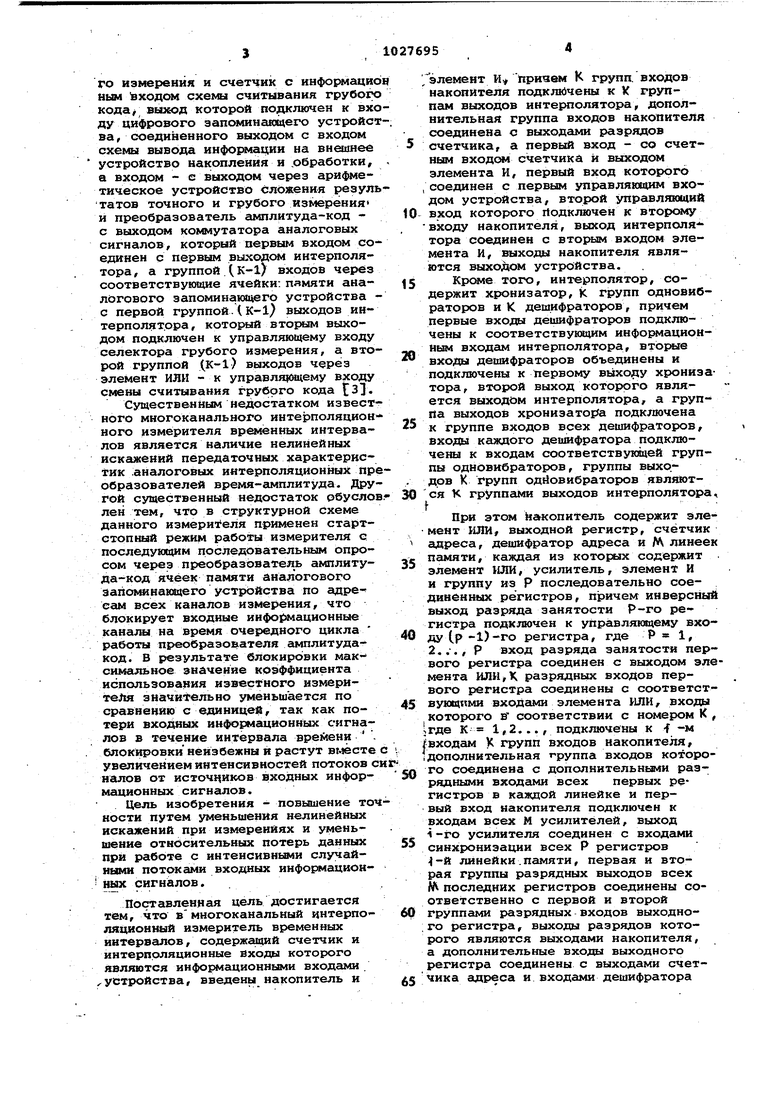

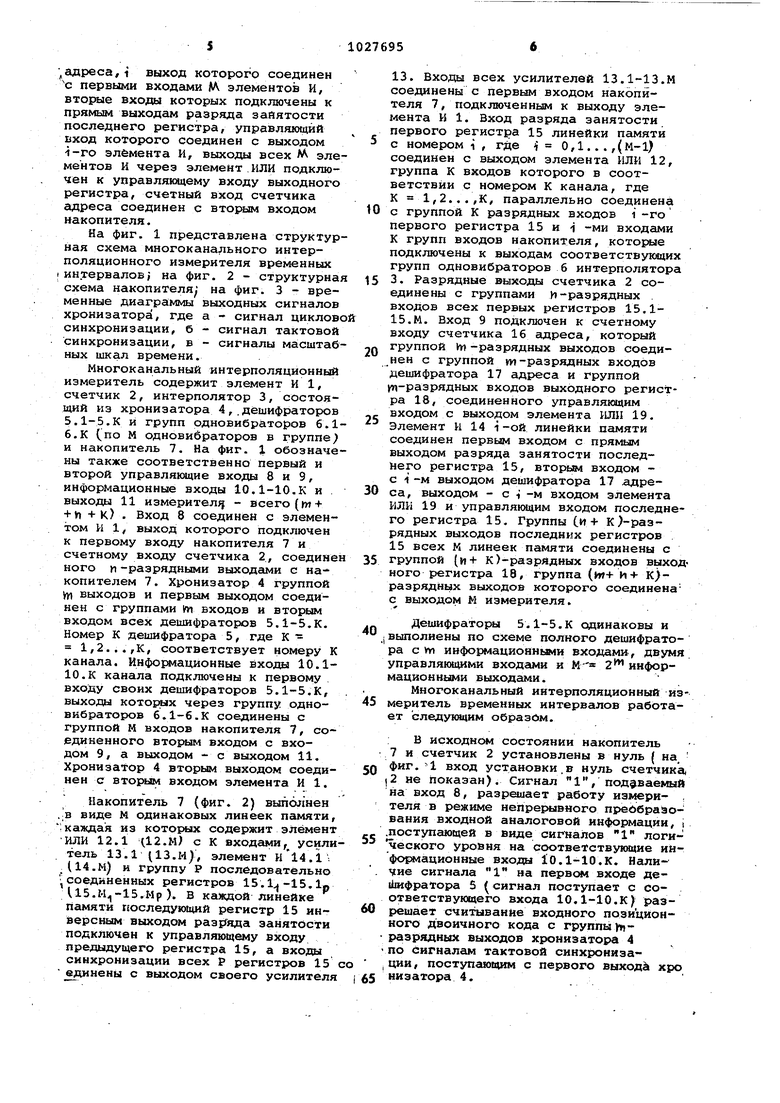

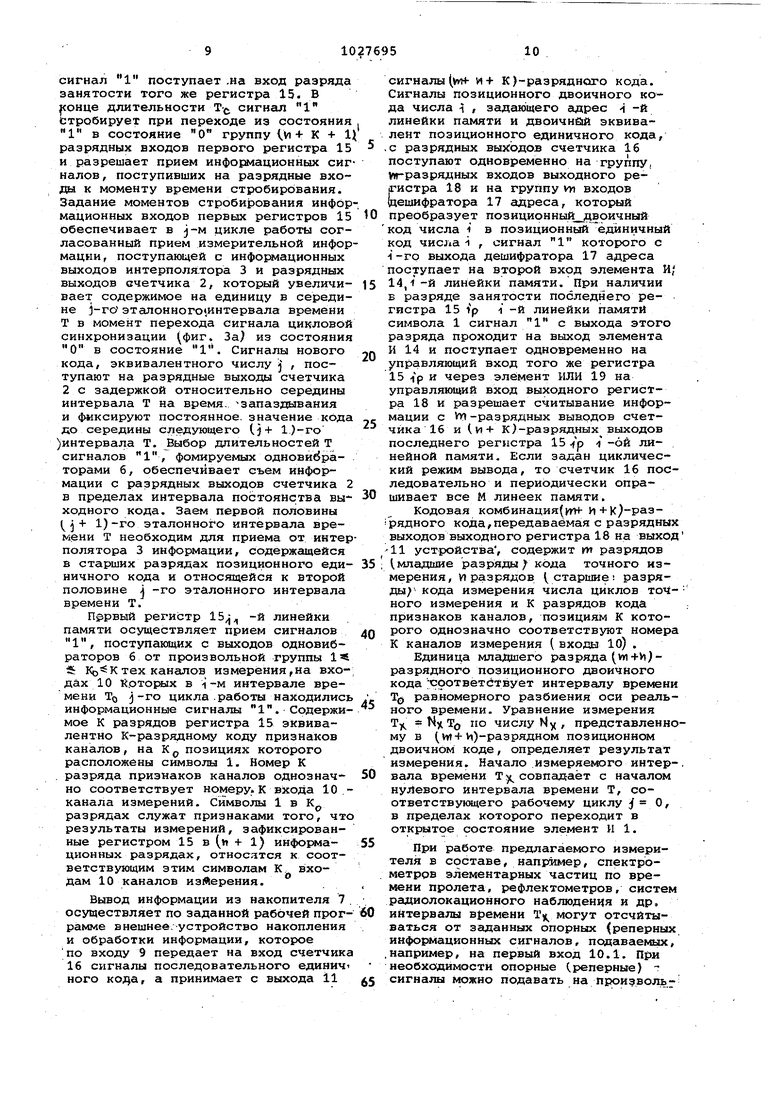

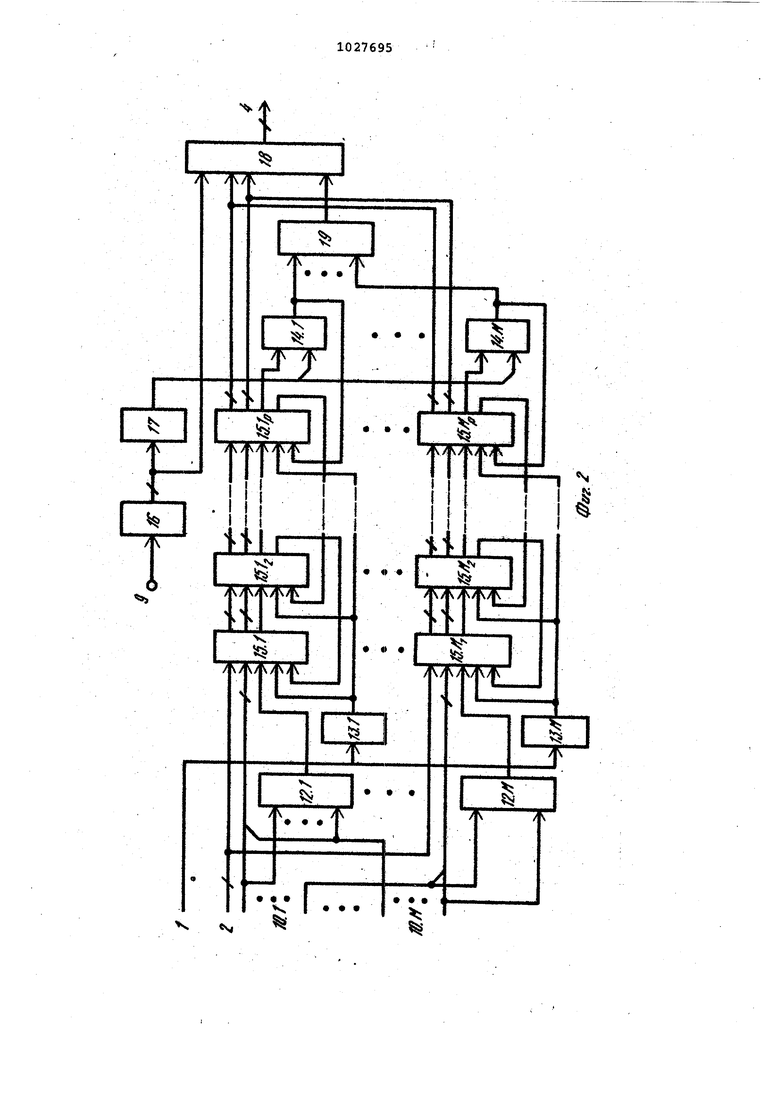

Наиболее близким к предлагаемому является многоканальный интерполяционный измеритель временных интервалов, содержащий счетчик и интерполятор, группа К входов которого является группой к информационных входов устройства, первый вход интерполятора параллельно соединен с выходом генератора импульсов времязадакяцей последовательности и через последовательно соединенные селектор грубоГО измерения и счетчик с информаци ным входом схемы считывания грубог кода выход которой подключен к вх ду цифрового запоминающего устройс ва, соединенного выходом с входом схемы вывода информации на внешнее устройство накопления и .обработки, а входом - с выходом через арифметическое устройство сложения резул татов точного и грубого измерения и преобразователь амплитуда-код с выходом коммутатора аналоговых сигналов, который первым входом со единен с первым выходом интерполятора, а группой Дк-l) входов через соответствующие ячейки: памяти аналогового запоминаказе го устройства с первой группой.(К-1} выходов интерполятрра, который вторым выходом подключен к управляимцему входу селектора грубого измерения, а вто рой группой (К-1) выходов через элемент ИЛИ - к управля|(йцему входу смены считывания грубого кода Существенным Недостатком извест ного многоканального интерполяцион ного измерителя вр ленных интервалов является наличие нелинейных искажений передаточных характеристик аналоговых интерполяционных пр образователей время-амплитуда. Дру гой существенный недостаток рбусло лен тем, что в структурной схеме данного измерителя применен стартстопный режим работы измерителя с последующим последовательным опросом через преобразователь амплитуда-код ячеек памяти аналогового запоминающего устройства по адресам всех каналов измерения, что блокирует входные информационные каналы на время очередного цикла работы преобразователя амплитудакод. В результате блокировки симальное значение коэффициента использования известного измериTeJra значиГельно уменьшается по сравнению с единицей, так как потери вход1даых информационных сигналов в течение интервала . блокировки неизбежны и растут вместе увеличением интёнсивностей потоков с нгитов ох источников входных информационных сигналов. Цель изобретения - повышение точ ности путем уменьшения нелинейных искажений при измерениях и уменьшение относительных потерь данных при работе с интенсивньши случайными потоками входных инфо ж ационных сигналов. Поставленная цель достигается тем, что вмногоканальный интерполяционный измеритель временных интервалов, содержащий счетчик и интерполяционные входы которого являются информационными входами. устройства, введены накопитель и /элемент И, призам К групп, входов накопителя подк;о)чены к X группам выходов интерполятора, дополнительная группа входов накопителя соединена с выходами разрядов счетчика, а первь вход - со счетным входом счетчика и выходом элемента И, первый вход которого ,соединен с первым управляющим входом устройства, второй управляющий вход которого rtодключен к вторсяу у входу накопителя, выход интерполятора соединен с в то{Из1м входом элемента И, выходал накопителя являются выходом устройства. Кроме того, интерполятор, содержит хронизатор, К групп одновибраторов и К дешифраторов, причем первые входы дешифраторов подключены к соответствующим информационHbBxt входам интерполятора, второе входы дешифраторов объединены и подключены к первому выходу хронизатора, второй выход которрго является выходом интерполятора, а группа выходов хронизаторга подключена к группе входов всех дешифраторов, входы каждого деигафратора подключены к входам соответствуквдей группы одновибраторов, группы выходрв К групп одйовибраторов являяотся К группами выходов интерполятора, При этом Накопитель содержит элемент ШИ, выходной регистр, счётчик адреса, дешифратор адреса и М линеек памяти, каждая из которых содержит элемент 1ШИ, усилитель, элемент И и группу из Р последовательно соединенных регистров, причем инверсный выход разряда занятости Р-го регистра подключен к управляихцему входу (р -1)-го регистра, где Р 1, 2..-., Р вход разряда занятости первого регистра соединен с выходом элемента ИЛИ,К разрядных входов первого регистра соединены с соответствующими входами элемента ИЛИ, входы которого в соответствии с нсмлером К , где К 1,2..., подключены к -f -м входам К групп входов накопителя, Дополнительная труппа входов которого соединена с дополнительными разрядными входс1ми всех первых ре гистров в каждой линейке и первый вход накопителя подключен к входам всех М усилителей, выход i-Го усилителя соединен с входами синхронизации всех Р регистров -и линейки.памяти, первая и вторая группы разрядных выходов всех Wk последних регистров соединены соответственно с первой и второй группами разрядных входов выходного регистра, выходы разрядов которого являются выходами накопителя, а дополнительные входел выходного регистра соединены с выходами счетика адреса и входами дешифратора адреса/ i выход которого соединен с первьлми входами М элементов И, BTOf&ie входы которых подключены к прямым выходам разряда зайятости последнего регистра, управляющий вход которого соединен с выходом i-ro элемента И, выходы всех АЛ элементов И через элемент.ИЛИ подключен к управляющему входу выходного регистра, счетный вход счетчика адреса соединен с входом накопителя. На фиг. 1 представлена структур ная схема многоканального интерполяционного измерителя временных I интервалов; на фиг. 2 - структурна схема накопителя на фиг. 3 - временные диаграммы выходных сигналов хронизатора, где а - сигнал циклов синхронизации, б - сигнал тактовой синхронизации, в - сигналы масштаб ных шкал времени. Многоканальный интерполяционный измеритель содержит элемент И 1, счетчик 2, интерполятор 3, состоящий из хрониэатора 4,.дешифраторов 5.1-5.К и групп одновибраторов 6.1 6.К (по М одновибраторов в группе и накопитель 7. На фиг. 1 обозначе ны также соответственно первый и второй управлякядие входы 8 и 9, информационные входы 10.1-10.К и выходы 11 измерител}} - всего ( 11 + к) . Вход 8 соединен с элементом И 1, выход которого подключен к первому входу накопителя 7 и счетному входу счетчика 2, соедине ного ц-разрядными выходами с накопителем 7. Хронизатор 4 группой Уи выходов и первым выходом соединен с группами п входов и вторым входом всех дешифраторов 5.1-5.К. Номер К дешифратора 5, где К 1,2...,К, соответствует номеру К канала. Информационные входа 10.110.К канала подключены к первому . входу своих дешифраторов 5.1-5.К, выходы KOtopax через группу одновибраторов б.1-6.К соединены с группой М входов накопителя 7, соединенного вторым входом с входом 9, а выходом - с выходом 11. Хронизатор 4 вторым выходом соединен с вторым входом элемента И 1. Накопитель 7 (фиг. 2) вып6;шен ,в виде М одинаковых линеек памяти, каждая из которых содержит элемент ИЛИ 12.1 (12.М) с К входами, усили тель 13.1 (13.М|, элемент Hl4.i Д14.М) и Группу Р последовательно соединенных регистров 15..1р Ч15.1-Ц-15.Мр ). В каждой линейке памяти последующий регистр 15 инверсным выходом разрйзда занятости подключен к управляющему входу предыдущего регистра 15, а входы синхронизации всех Р регистров 15 единены с выходом своего усилителя 13. Входы всех усилителей 13.1-13.М соединены с первым входом накопителя 7, подключенным к выходу элеента И 1. Вход разряда занятости первого регистра 15 линейки памяти с номером i , где i О,...,(М-1) соединен с выходом элемента ИЛИ 12, группа К входов которого в соответствии с номером К канала, где К 1,2...,К, параллельно соединена с группой К разрядных входов i-го первого регистра 15 и i -ми входами К групп входов накопителя, которые подключены к выходам соответствующих групп одновибраторов 6 интерполятора 3. Разрядные выходы счетчика 2 соединены с группами и-разрядных . входов всех первых регистров 15.115.М. Вход 9 подключен к счетному входу счетчика 16 адреса, который группой Уп -разрядных выходов соединен с группой ги-разрядных входов дешифратора 17 адреса и группой уп-разрядных входов выходного регистра 18, соединенного управляющим входом с выходом элемента ИЛИ 19. Элемент И 14 i-ой линейки памяти соединен первым входом с прямым выходом разряда занятости последнего регистра 15, вторЬвл входом с 1 -М выходом дешифратора 17 адреса, выходом - с 1 -М входом элемента ИЛИ 19 и управлянадим входом последнего регистра 15. Группы Си + К)-разрядных выходов последних регистров 15 всех М линеек памяти соединены с группой (и+ К)-разрядных входов выходного регистра 18, группа (м+ h-f к)разрядНых выходов которого соединенас выходом М измерителя. Дешифраторы 5.1-5.К одинаковы и выполнены по схеме полного дешифратора с УИ информационными входами, двумя управляющими входами и М-« информационньа и выходами. Многоканальный интерполяционный измеритель временных интервалов работает следующим образом. В исходном состоянии накопитель 7 и счетчик 2 установлены в нуль ( на, фиг. 1 вход установки.в нуль счетчика, 12 не показан). Сигнал 1, подаваемый на вход 8, разрешает работу измери- , теля в режиме непрерывного преобрааования входной аналоговой информации, i .поступающей в виде сигналов 1 логи ческого уровня на соответствующие инфОБ 1ационные входы lO.l-lD.K. Налина первсм входе дечие сигнала ЦшфраТора 5 (сигнал поступает с соответствующего входа 10.1-10.К) разрешает считывание входного позиционного двоичного кода с группыinразрядных выходов х юнизатора 4 по сигналам тактовой синхрониза. ции, поступающим с первого выходе хро низатора 4. Хронизафор 4 . в режиме непрёЕЯ:1Вно генерации шлрабатывает ч едукщие си налы: сигнал цикловой син;кронизацйи (фиг. За/ с периодом Т, котощй .с второго выхдда хрониэатора 4 через, открытый по первому входу элемент И 1 поступает на счетный вход счетчика 2 и одвовременбё на входы всех усйлиагелей 13.1-13.М накопителя 7/ сигнал тактовой синхронизации ( фиг. Зб) с периодом TO, которьй с первого выхода хронизатора 4 поступает одновременно на вторые входы всех де11Шф раторов 5.1-5.К и. составной параллельный сигнал циклической кодовой измерительной шкатш , состоящий простых Сигналов (фиг. с периодами 2Т,. кбфорые с группы п выходов хронизатора. 4 nocTynaiют одновременно на группы Hi входов всехК дешифраторов 5.1-5.К. Интервал Та равнс 1ерного разбиения оси .реального времени фиксирует цену де ления Tj Зф -( мааятабной шк лы времени где в - 1,2.. i. , Vnийдекс, характеризукиций цену делени данной шкалы в квантах ; Т - минимальный эталон (кваНт), соответству ашшй единице младшего разряда позиционного двоичного кода. Интервал Т 2 Т0 cooTBeTCTBjeT интервалу времени однозначного отсчета по циклической КОДОВОЙ измерительной шкале врекюни. Сигнал тактовой синхронизации обеспечивает то 1ную Фиксацию интё1 г вала Tjj - TQ (цена деления младшей шкалы из набора н . На иятв| г вале Т числовой эквивалент позицяонноГо двр ичного, кода обеспечивает фиксацию номера 1 этого интервала, где Ч 0/1... ,2 -1. Таким Образейи линейность функции преобразования и меряегшос интервалов времени s код обеспечена за счет равномерного ра;збиения интервала времени 7 однозначного отсчета с ,ъю заданного набора интервалов Tg {фиг. 3) Пйлноха набора Уп масштабных шкал вре мени для одновременной однозначной индикации номерам интервала TQ равномерного разбиения интервала Т на М 2 интервалов следует из условия кодирования (без избыточности) m -разрядньш двоичным кодом числа М. Символам О и 1 1сода соответСтвуют относительные уровни масштабных сигналов и -1 (фиг. Зв). На фиг. Зв заштри Сован интервал 70 при 4 14. Передний фронт сигнала цикловой синхронизации (фиг. За) совмеи н с нячапвм интервала времени, Т и началом нулевьос интервалов У f всех Уй Мас1атабных шкал времени хронизатора 4, что обеспечивает в каждсш flKKne единый отсчет нуля по всем масштабным шкалам времени интерполяtopa Зи счётчика 2, КОТОЕШЙ суммирует число одннаковш эталонозв, задаваемых на каящом цикле масштабным интервалом Т 2 Т,. Результат измерения представляет ( + и)-разрядное двоичное число. W мпадш1р разрядов числа определяются в результате преобразования позиционной двоичный код - ПОЗИЦИОННЫЙ единичный код - позиционный Двоичный код, выполняЕемого интерполятором 3 и Накопителем 7, и ц старших с азрядов - в результате преоб-: разования последовательного; единичного -кода в позиционный двоичный код, вьв1ОлНяемо17о счетчиком 2. Преобразование позиционного двоичного кода в ПОЗИЦИОННЫЙ единичшй код вьшолняют дешифраторы S.1-5.К при наличии на их первс входе сигнала 1 и на первом входе сигнала тактовой синхронизации. При работе дешифраторов 5.1-5.К К-го кансша на его -м выходе, где i - числовой эквивалент входного кода на; текущем интервале 7, ycтaнaвJIивaeтcя кратковременньш сигнал логического уровня 1, запускакя йй одновибратор 6, KOTOpbdt формирует сигнал i -заданной длительности, поступаккфий в {-ю линейку пгимяти накопителя 7. в начале каждого очередного цикла работы накопителя 7 по сигналам цикловой синхронизации (фиг.: За/, nocTynaKxmiM с вьцсодов усилителей 13.1-13.К на входы синхронизации регистров) 15, производят сдвиг информации в сторону последних регистров 15-1р -IS.Mp. Сигналы, управляющие сдвигеич, поступают с инверсных выходов разрядов занятости (Р + +1)-х регистров 15 на управляющие входы р-х регистров 15 и разрешаю передачу коДов с (Н+ К -f l)-разрядных выходов р-го регистра 15. Vp -и линейки памяти на разрядные входа (p-fll-ro регистра 15, где Р 1,2... {.P-i) . Передача информации с разрядных выходов регистров 15 производится в начале каждого -го интервала времени Т, где j 0,1...,, в, момент перехода синхросигнала из состояния в состояние вод информации из последнего Р-го регистра 15 производится 4epja3 выходной регистр 18 принудительно по Сигналам последовательного единичного кода,поступающим от вне11него устройст ва.накопления (не показано и обравотхи информации на вход 9. Первые perHCTJfaj 15.1-15.М при приеме информации работают одинаково. Сигнал 1 с выхода i-ro одновибратора б.К К-го канала длительностью И поступает одновременно на K-Й вход признаков каналов регистра 15 4-и линейки. пг««яти и на К-й вход элемента ИЛИ 12, с выхода которого сигнал 1 поступает ,на вход разряда занятости того же регистра 15. В онце длительности T-(j сигнал 1 Стробирует при переходе из состояния 1 в состояние О группу Си + К + 1 разрядных входов первого регистра 15 и разрешает прием информационных сиг налов , поступивших на разрядные входы к моменту времени стробирования. Задание моментов стробирования инфор мационных входов первых регистров 15 обеспечивает в j-м цикле работы согласованный прием измерительной инфор мации, поступающей с информационных выходов интерполятора 3 и разрядных выходов сгчетчика 2, который увеличивает содержимое на единицу в середине j-rc эталонного интервала времени Т в момент перехода сигнала цикловой синхронизации (фиг. За) из состояния Сигналы нового в состояние кода, эквивалентного числуj , поступают на разрядные выходы счетчика 2 с задержкой относительно середины интервала Т на время, запаздывания и |«1ксируют постоянное, значение кОда до середины следующего (}+ 1-)-го )интервала Т. Выбор длительностей Т сигналов 1, фомируемых одновибраторами б, обеспечивает съем информации с разрядных выходов счетчика в пределах интервала постоянства выходного кода. Заем первой половины j + 1)-го эталонного интервала времени Т необходим для приема от интер полятора 3 информации, содержащейся в старших разрядах позиционного еди ничного кода и относящейся к второй половине j -го эталонного интервала времени Т. Первый регистр , -и линейки памяти осуществляет прием сигналов 1, поступакяцих с выходов одновибраторов б от произвольной группы Iu $ тех каналов измерения,на входах 10 Которых в -i-м интервале времени TO j-го цикла.работы находилис информационные сигналы 1. Содержи мое К разрядов регистра 15 эквивалентно К-разрядному коду признаков каналов, на К позициях которого расположены символы 1. Номер К разряда признаков каналов однозначно соответствует номеру. К входа 10 канала измерений. Символы 1 в К, разрядах служат признаками того, чт результаты измерений, зафиксированные регистром 15 в (« + 1) информационных разрядах, относятся к соответствующим этим символам К. входам 10 каналов изЛереНия. Вывод информации из накопителя 7 осуществляет по заданной рабочей прог рамме внешнее, устройство накопления и обработки информации, которое по входу 9 передает на вход счетчик 16 сигналы последовательного единич ного коца, а принимает с выхода 11 сигналы( и+ К)-разрядного кода. Сигналы позиционного двоичного кода числа 1 , задак1щего адрес Н -и линейки памяти и двоичнШ} эквивалент позиционного единичного кода, с разрядных выходов счетчика 16 поступают одновременно на группу, у гразрядных входов выходного регистра 18 и на группу VM входов дешифратора 17 адреса, который преобразует позиционный двричный код числа ( в позиционный единичный код числа -i , сигнал 1 которого с i-rp выхода дешифратора 17 адреса поступает на второй вход элемента И/ 14,(-и линейки памяти. При наличии в разряде занятости последнего регистра 15 Ip 1 -и линейки памяти символа 1 сигнал 1 с выхода этого разряда проходит на выход элемента И 14 и поступает одновременно на управляющий вход того же регистра 15 ip и через элемент ИЛИ 19 на управляющий вход выходного регистра 18 и разрешает считывание информации с Vn -разрядных выводов счетчика 16 и (и + к)-разрядных выходов последнего регистра 15 Vp 1 -oft .линейной памяти. Если задан циклический режим вывода, то счетчик 16 последовательно и периодически опрашивает все М линеек памяти. Кодовая комбинация(т+- И+К)-разрядного кода,передаваемая с разрядных выходов выходного регистра 18 на выход 11 устройства , содержит ги разрядов младшие разряды кода точного измерения, VJ разрядов 1 старшие разряды; кода измерения числа циклов точ- ного измерения и К разрядов кода признаков каналов, позициям К которого однозначно соответствуют номера К каналов измерения ( входа 10) . Единица младшего разряда (v«+H)разрядного позиционного двоичного кода соответствует интервалу времени Т0 равномерного разбиения оси реального времени. Уравнение измерения Т по числу My , представленному в (wf-f И)-разрядном позиционном двоичном коде, определяет результат измерения. Начало измеряемого интер-, вала времени Т)( совпадает с началом нулевого интервала времени Т, соответствующего рабочему циклу j О, в пределах которого переходит в открытое состояние элемент Hi. При работе предлагаемого измерителя в составе, напрт ер, спектрометров элементарных частиц по времени пролета, рефлектометров, систем радиолокационного наблюдения и др, интервалы времени Т) могут отсчитываться от заданных опорных (реперных информационных сигналов, подаваемых, .например, на первый вход 10.1. При необходимости опорные (реперные) сигналы можно подавать на произволуйд заданный набор входов 10, различая их от сигналов, несущих изме р ятельнуку информацию, tto заданному закрйу модуляции во временной области, напр|Шер, ШИМ, КШ,

После Накопления заданного объема измерений и вьюода остаточной информации и д всех М лииеек пгшяти накопп-тепя 7 рабочий интервал времени заканчивается и Иа вход подается логического уровня О, ко закрывает. элемент И 1« Одновре йбнно сигнал 1 подается на вход установки в нуль счетчика 2 и

йавливает еЬо в исходное нулевое состояние.

Таким образом, предлагаемое H366peTjeHHe позволяет увеличить точность (на два порядка) за счет уменьшения нелинейных искажений (соответственно с 10 %j .передаточной характеристики преоб{ азователя аналог-код и уменьшить относительные потери данных при приеме входных сигналов от и ;точ- НИКОВ входных инфо1 ационных сигна лов большой интенсивности.

ч «Si

. J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, М., Ни|з, 4974, 19, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для передачи и приема по радиотелеграфу | 1927 |

|

SU6845A1 |

| ЖЕЛЕЗНЫЙ КАРКАС ДЛЯ ЭЛЕКТРОДВИГАТЕЛЯ | 1922 |

|

SU604A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-30—Подача