1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления электроприводами, в частности в регуляторах соотношение частот, скоростей, когда одна из двух сравнваемых частей остается постоянной, другая изменяется в процессе работы электропривода.

Целью изобретения является расширение диапазона измерения относителной разности частот,

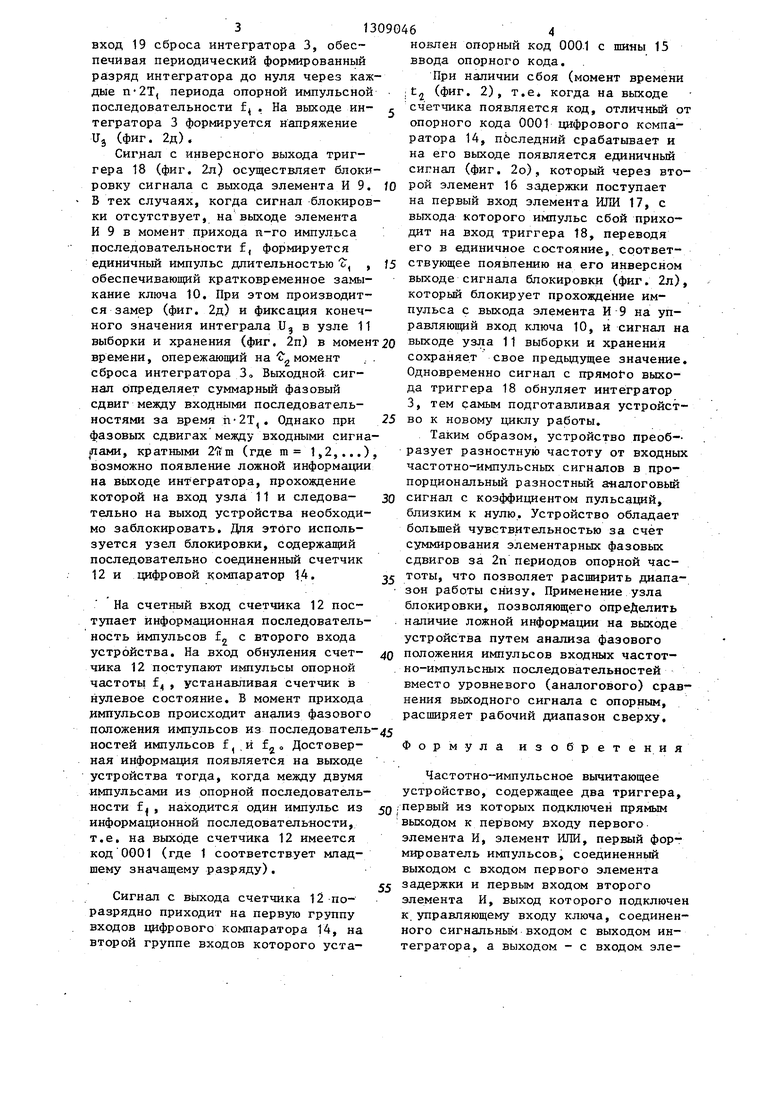

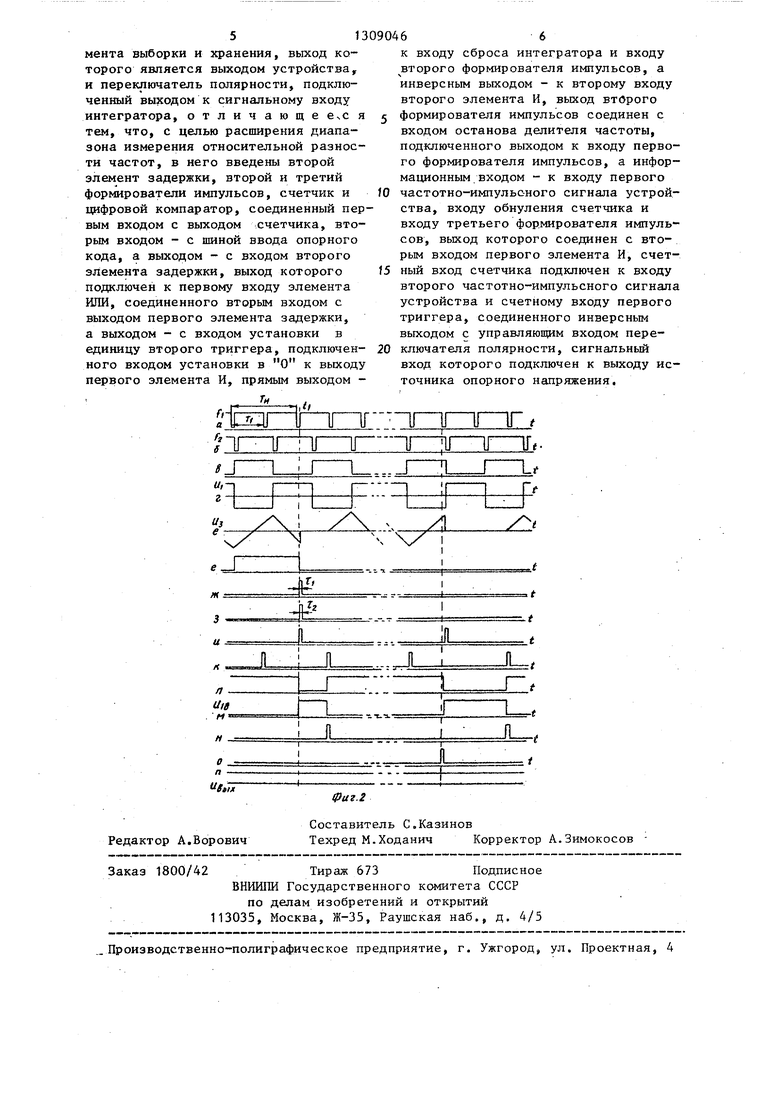

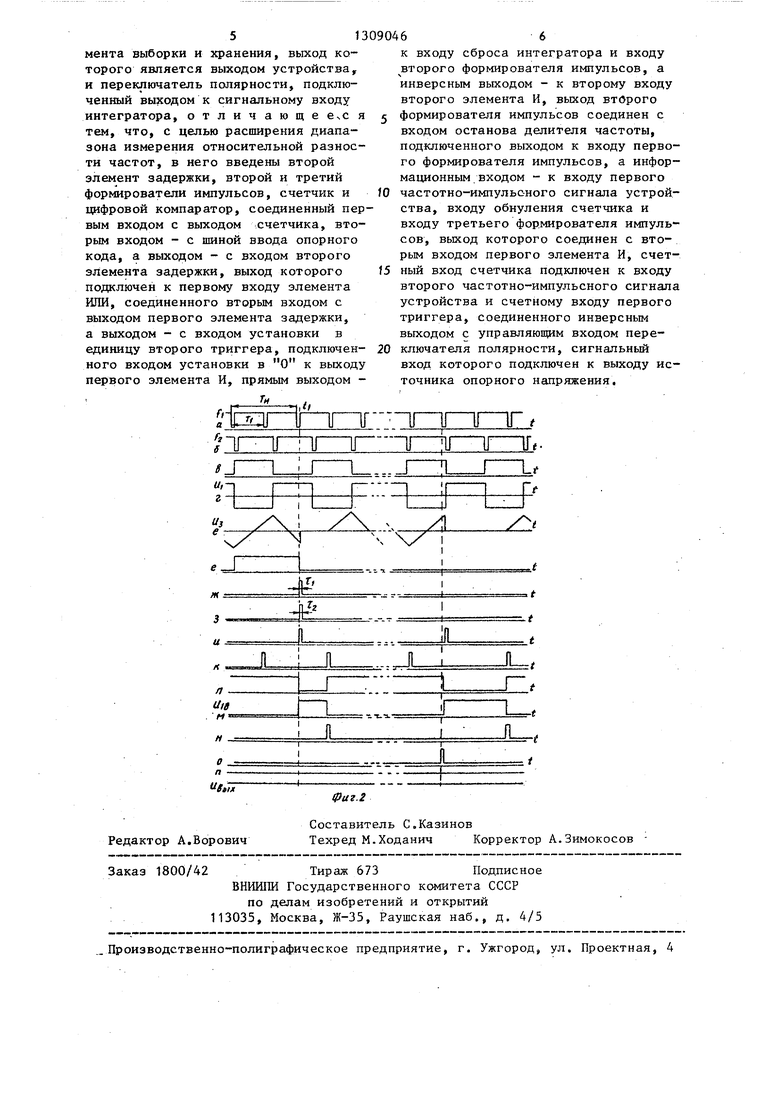

На фиг о 1 изображена блок-схема устройства; на фиг„ 2 - временная диаграмма работы устройства.

Устройство содержит переключател 1 полярности, источник 2 опорного напряжения, интегратор 3, первый тргер 4, первый элемент И 5, делител 6 частоты, первый формирователь 7 импульсов, первый элемент 8 задержки, второй элемент И 9, ключ 10, узел 1 Г выборки и хранения, счетчик 12, второй формирователь 13 импульсов, цифровой компаратор 14, шину 1 ввода опорного кода, второй элемен 16 задержки, элемент ИЛИ 17, второй триггер 18 (типа RS),, вход 19 сброс

интегратора 3 (управляющий вход раз „ ,

рядного ключа) и третий формировате

20 импульсов.

В устройстве реализуется известн

V.

соотношение: йц 2 irjufdt, где utf офазовый -сдвиг между входными частота-

ми, и, ,b(f f.{ - f-c

- разностная частота входных частотно-импульсных сигналов.

Производится интегрирование & Cj приращения сдвига по фазе между вход- ными частотами за каждый интервал измерения Тц 2Т, , где ьТ,, - эквивалентное приращение сдвига по времени:

ЬТ, - Т, - 1 uf.T,-T,,,

где Т, -f ; Т -р- .

J-,J-2

На выходе устройства калсдый п-й интервал измерения формирует конечное значение интеграла от сигнала Ut с переключателя 1 полярности за время П ЛТд, которое .фиксируется в

узле выборки и хранения

пьТ,

и

8Ъ1Х

J U,dt

n -f. . Т, Т. uf п.

if

5

К.

Таким образом, формируется выходной аналоговый сигнал, пропорциональный разностной относительной часто1ы входных импульсных последовательностей.

Устройство работает следующим образом.

На счетный вход делителя 6 частоты (фиг. 2) поступает первая (опорная) частотно-импульсная последовательность f( (фиг. 2а). В делителе происходит деление частоты с коэффициентом деления, равным

f

где f

J мин. раб

- минимальная допустимая

0

/ЛИН, раб

частота, с которой может быть представлена выходная информация.

На счетный вход триггера 4 посту- ,пает вторая (информационная) частот-, но-импульсная последовательность fg (фиг. 26). Выходной И1 ульсный сиг- 5 нал триггера 4 (фиг. 2в) поступает на управляющий вход переключателя 1 -полярности, при этом на выходе последнего формируется сигнал И1 (фиг. 2г), который подается на вход

Импульсный сигнал с выхода делителя 6 (фиг. 2е) поступает через первый формирователь 7 импульсов, укорачивающий импульсы до малой длительности о , (фиг. 2ж) J на первый вход второго элемента И 9 и через первый элемент 8 задержки (на время . фиг. 2з) на второй вход элемента ИЛИ 17. Импульсы с выхода элемента ИЛИ 17 (фиг. 2и, момент времени t,) поступают на S вход триггера 18, на R-вход которого приходят короткие импульсы с выхода первого элемента И 5 (фиг. 2к), на первый :вход последнего приходят импульсы с прямого выхода триггера 4, а на второй вход- с выхода третьего формирователя 20 импульсов, укорачивающего импульсы опорной последовательности f до малой длительности. Тем самым выходной

сигнал элемента И 5 определяет начало нового цикла работы устройства.

Сигнал с прямого выхода триггера 18 (фиг. 2м) поступает на вход фор- мирователя 20 импульсов, с выхода которого короткие импульсы установки нуля (фиг. 2н) поступают на делитель 6. С этого же выхода триггера 18 сигнал U,g приходит на управляющй

вход 19 сброса интегратора 3, обеспечивая периодический формированный разряд интегратора до нуля через каждые П 2Т, периода опорной импульсной последовательности f . На выходе ин- г тегратора 3 формируется напряжение Uj (фиг. 2д).

Сигнал с инверсного выхода триггера 18 (фиг. 2л) осуществляет блокировку сигнала с выхода элемента И 9. 10 В тех случаях, когда сигнал блокировки отсутствуетJ на выходе элемента И 9 в момент прихода R-ГО импульса последовательности f, формируется единичный импульс длительностью о, , 15 обеспечивающий кратковременное замыкание ключа 10. При этом производится замер (фиг. 2д) и фиксация конечного значения интеграла U, в узле 11

новлен опорный код 000.1 с шины 15 ввода опорного кода.

При наличии сбоя (момент времен ; t2 (фиг. 2), т.е когда на выходе сч етчика появляется код, отличный опорного кода 0001 цифрового компа ратора 14, пбследний срабатывает и на его выходе появляется единичный сигнал (фиг. 2о), который через вт рой элемент 16 задержки поступает на первый вход элемента ИЛИ 17, с выхода которого импульс сбой прихо дит на вход триггера 18, переводя его в единичное состояние, соответ ствующее появлению на его инверсно выходе сигнала блокировки (фиг. 2л которьм блокирует прохождение импульса с выхода элемента И 9 на уп равляющий вход ключа 10, и сигнал

выборки и хранения (фиг. 2п) в момент20 вькоде узла 11 выборки и хранения

времени, опережающий на с момент , сброса интегратора 3 Выходной сигнал определяет суммарный фазовый сдвиг между входными последовательностями за время h 2T,. Однако при фазовых сдвигах между входными сигналами, кратными 2 ит (где т 1,2,...) возможно появление ложной информации на вькоде интегратора, прохождение которой на вход узла 11 и следовательно на выход устройства необходимо заблокировать. Для этого используется узел блокировки, содержащий последовательно соединенный счетчик 12 и 1ЩФРОВОЙ компаратор 14.

На счетный вход счетчика 12 поступает информационная последовательность импульсов fj с второго входа

устройства. На вход обнуления счетчика 12 поступают импульсы опорной частоты f , устанавливая счетчик в нулевое состояние. В момент прихода импульсов происходит анализ фазового положения импульсов из последователь ностей импульсов f,,H f j, „ Достоверная информация появляется на выходе устройства тогда, когда между двумя импульсами из опорной последователь

ности f. , находится один импульс из 50 j из которых подключен прямым

информационной последовательности, т.е. на выходе счетчика 12 имеется код 0001 (где 1 соответствует младшему значащему разряду).

Сигнал с выхода счетчика 12 поразрядно приходит на первую группу входов цифрового компаратора 14, на второй группе входов которого уста-

выходом к первому входу первого элемента И, элемент ИЛИ, первый фор мирователь импульсов, соединенный выходом с входом первого элемента 55 задержки и первым входом второго

элемента И, выход которого подключ к управляющему входу ключа, соедине ного сигнальным входом с выходом ин тегратора, а выходом - с входом эле

новлен опорный код 000.1 с шины 15 ввода опорного кода.

При наличии сбоя (момент времени ; t2 (фиг. 2), т.е когда на выходе сч етчика появляется код, отличный от опорного кода 0001 цифрового компаратора 14, пбследний срабатывает и на его выходе появляется единичный сигнал (фиг. 2о), который через второй элемент 16 задержки поступает на первый вход элемента ИЛИ 17, с выхода которого импульс сбой приходит на вход триггера 18, переводя его в единичное состояние, соответствующее появлению на его инверсном выходе сигнала блокировки (фиг. 2л), которьм блокирует прохождение импульса с выхода элемента И 9 на управляющий вход ключа 10, и сигнал на

сохраняет свое предьщущее значение. Одновременно сигнал с прямо1 о выхода триггера 18 обнуляет интегратор 3, тем самым подготавливая устройство к новому циклу работы.

Таким образом, устройство преоб-- разует разностну1б частоту от входных частотно-импульсных сигналов в пропорциональный разностный аналоговый

сигнал с коэффициентом пульсаций, близким к нулю. Устройство обладает большей чувствительностью за счёт суммирования элементарных фазовых сдвигов за 2п периодов опорной частоты, что позволяет расширить диапазон работы снизу. Применение узла блокировки, позволяющего определить наличие ложной информации на выходе устройства путем анализа фазового положения импульсов входных частотно-импульсных последовательностей вместо уровневого (аналогового) срав - нения выходного сигнала с опорным, расширяет рабочий диапазон сверху.

Формула изобретения

Частотно-импульсное вычитающее устройство, содержащее два триггера.

выходом к первому входу первого элемента И, элемент ИЛИ, первый формирователь импульсов, соединенный выходом с входом первого элемента задержки и первым входом второго

элемента И, выход которого подключен к управляющему входу ключа, соединенного сигнальным входом с выходом интегратора, а выходом - с входом элемента выборки и хранения, выход которого является выходом устройства, и переключатель полярности, подключенный выходом к сигнальному входу интегратора, отличающе я тем, что, с целью расошрения диапазона измерения относительной разности частот, в него введены второй элемент задержки, второй и третий формирователи импульсов, счетчик и цифровой компаратор, соединенный первым входом с выходом счетчика, вторым входом - с пшной ввода опорного кода, а выходом - с входом второго элемента задержки, выход которого подключен к первому входу элемента ИЛИ, соединенного вторым входом с выходом первого элемента задержки, а выходом - с входом установки в единицу второго триггера, подключенного входом установки в О к выходу первого элемента И, прямым выходом Тн

Редактор А.Ворович

фиг. г

Составитель С.Казинов

Техред М.Ходанич Корректор А.Зимокосов

1800/42

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

к входу сброса интегратора и входу второго формирователя импульсов, а инверсным выходом - к второму входу второго элемента И, выход второго

формирователя импульсов соединен с входом останова делителя частоты, подключенного выходом к входу первого формирователя импульсов, а информационным/входом - к входу первого

частотно-импульсного сигнала устройства, входу обнуления счетчика и входу третьего формирователя импульсов, выход которого соединен с вторым входом первого элемента И, счетный вход счетчика подключен к входу второго частотно-импульсного сигнала устройства и счетному входу первого триггера, соединенного инверсным выходом с управляющим входом переключателя полярности, сигнальный

вход которого подключен к выходу источника опорного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Устройство для контроля динамических параметров аналого-цифровых преобразователей | 1987 |

|

SU1474839A1 |

| Умножитель частоты импульсного сигнала | 1972 |

|

SU447823A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Частотно-импульсное вычиттающее устройство | 1975 |

|

SU604002A1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| Инфранизкочастотный цифровой фазометр- чАСТОТОМЕР | 1979 |

|

SU805199A1 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1994 |

|

RU2079148C1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

Изобретение относится к автоматике и .вычислительной технике. Целью изобретения является расширение диапазона измерения относительной разности частот. Устройство содержит переключатель 1 полярности, источник 2 опорного напряжения, jiHTerpaTop 3, первый и второй триггеры 4 и 18, два элемента И 5 и 9, делитель частоты 6, три формирователя импу1}ьсов 7, 13 и 20, два элемента задержки 8 и 16, ключ 10, узел 11 выборки и хранения, счетчик 12, цифровой компаратор 14, шину 15 ввода опорного кода, элемент ИЛИ 17. Принцип действия устройства основан на интегрировании приращения сдвига по фазе между входными частотно-импульсными сигналами за каждый интервал измерения. Расширение диапазона измерения достигается за счет суммирования элементарных фазовых сдвигов на ряде периодов первой (опорной) входной частотно-импульсной последовательности и исключения ложной информации на основе анализа фазового положения импульсов входных частотно-импульсных последовательностей. 2 ил о § W 00 о со о 4 О5

| Устройство для измерения разности частот | 1980 |

|

SU997046A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Частотно-импульсное вычитающее устройство | 1977 |

|

SU646347A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-26—Подача