1

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля логических блоков.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности контроля байта информации и запоминания его значения в сбойных ситуациях.

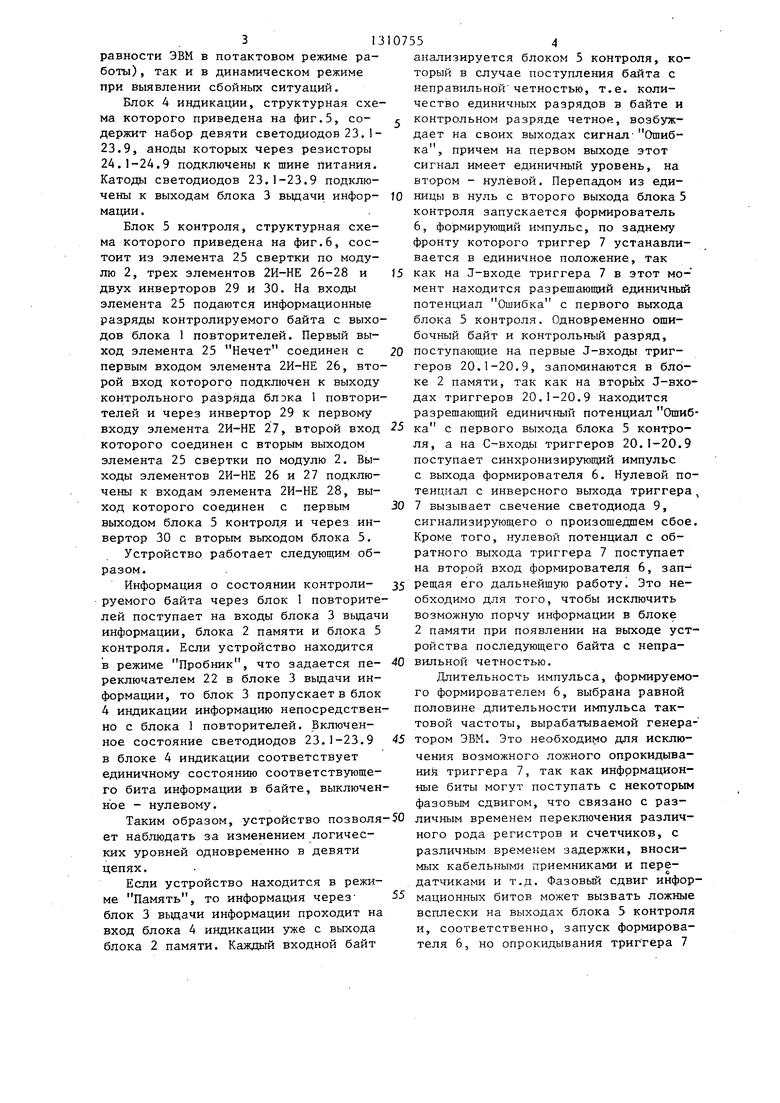

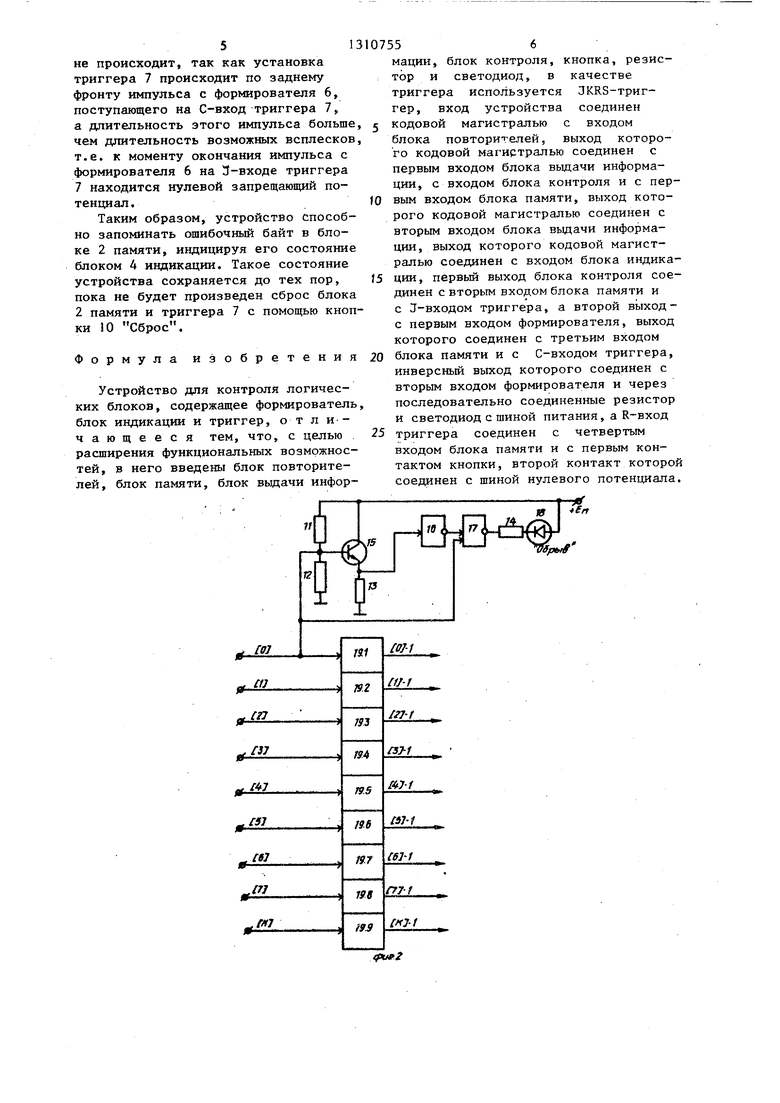

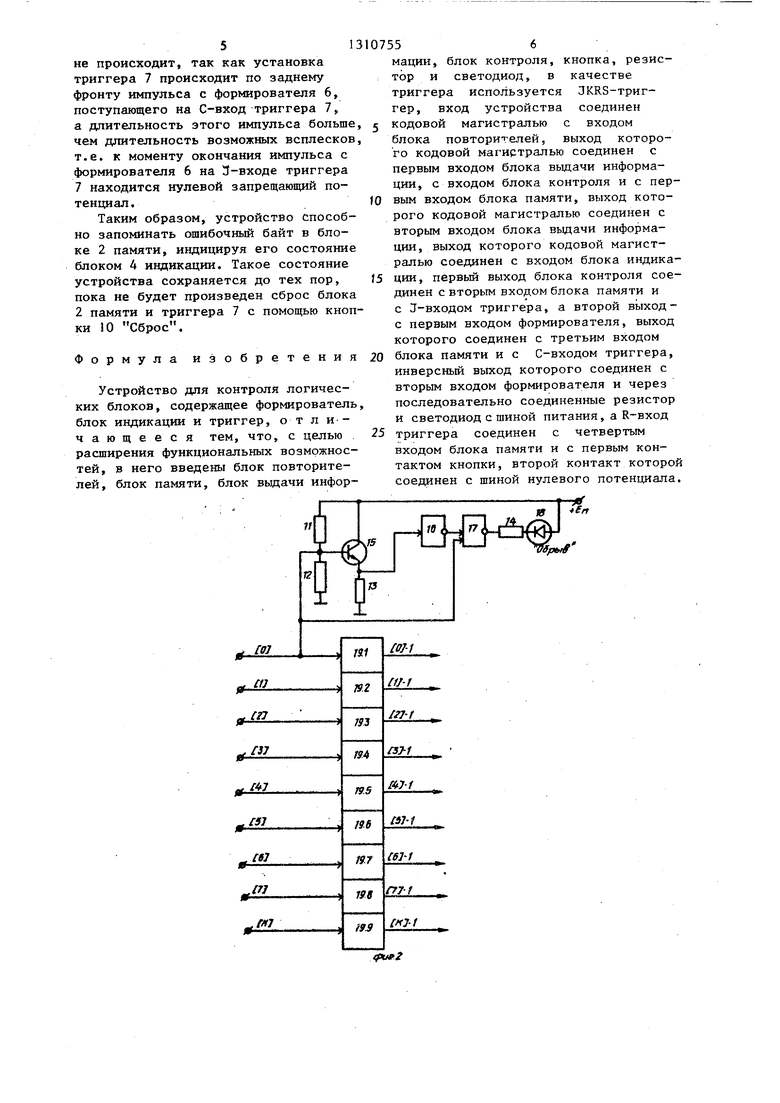

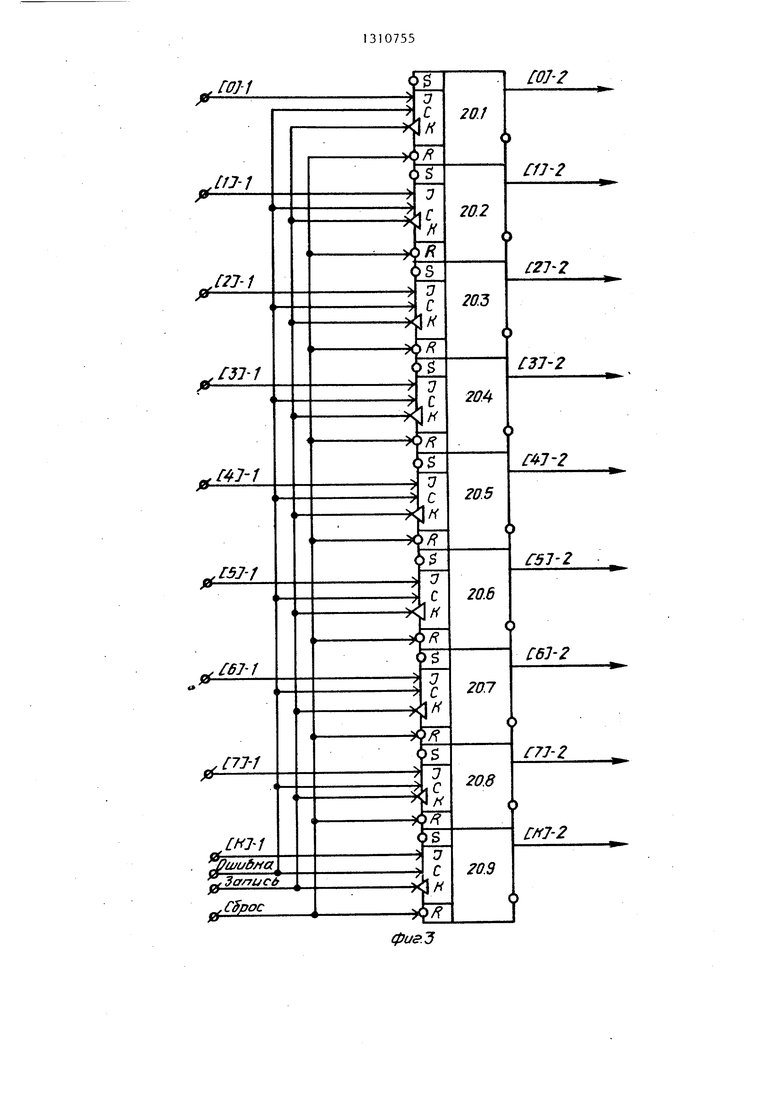

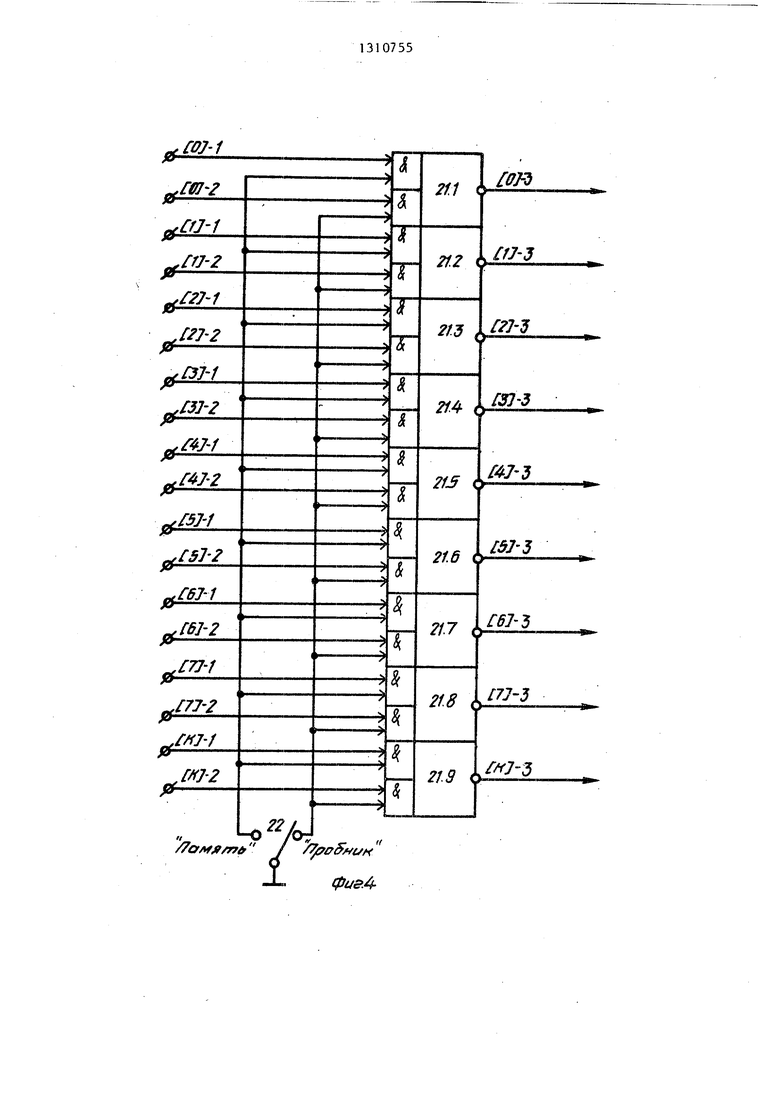

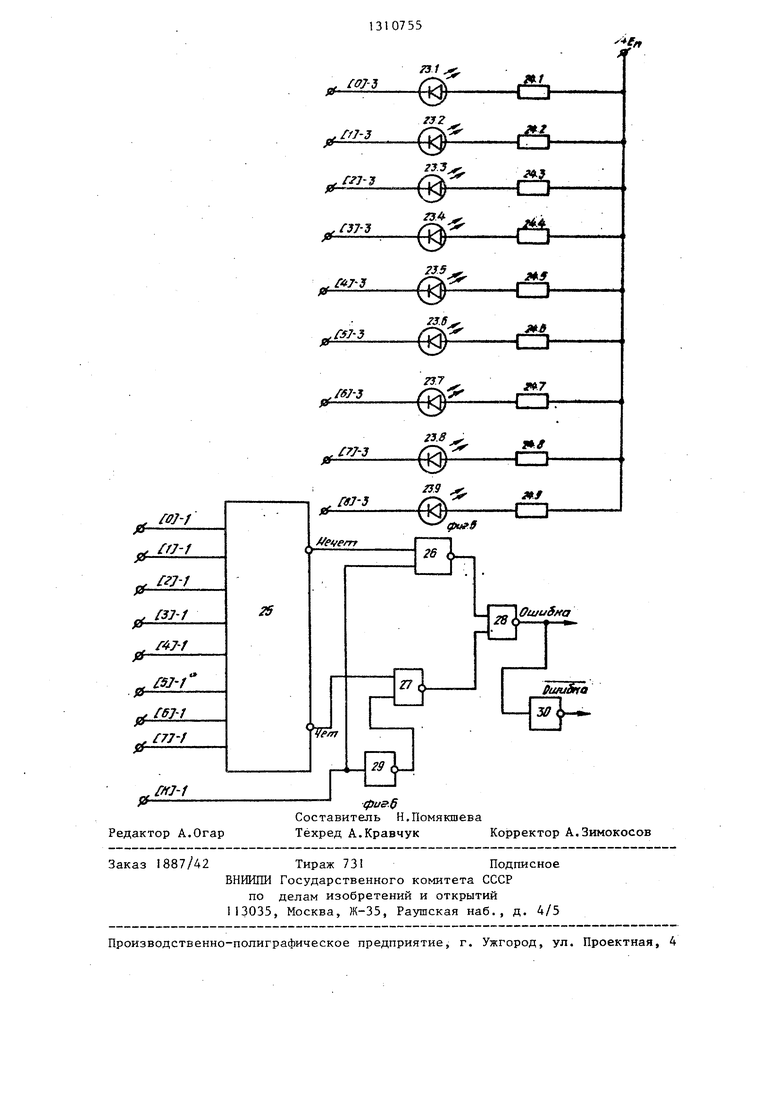

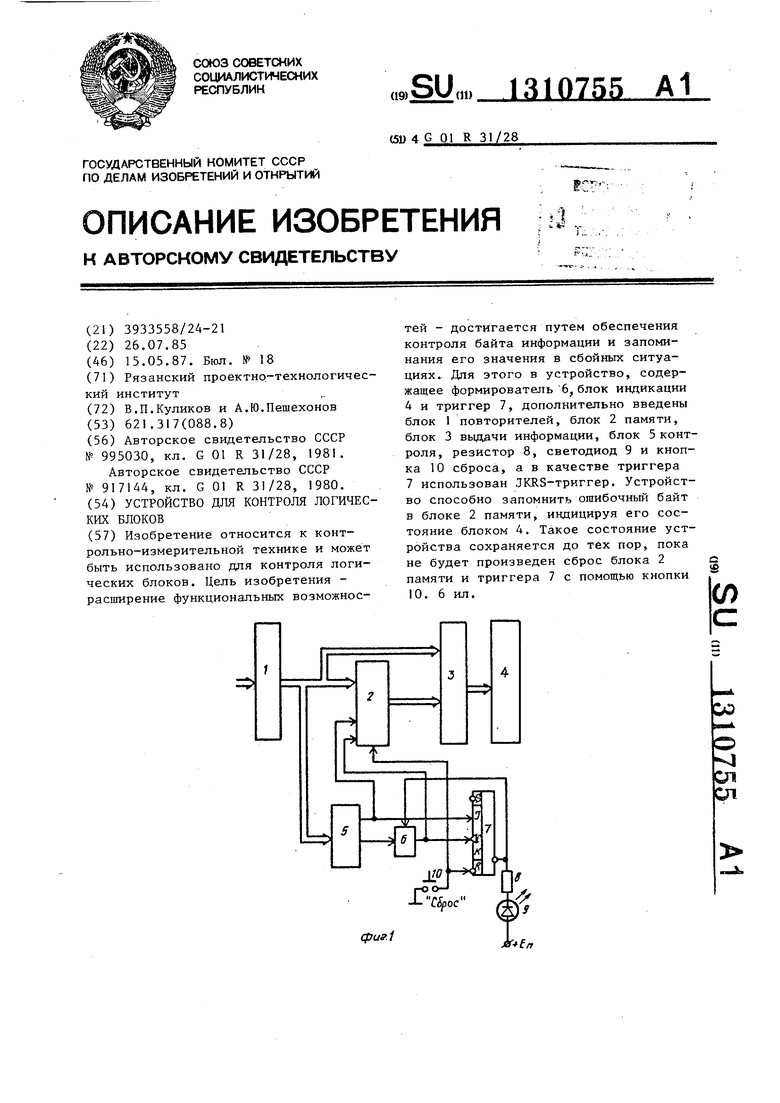

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 - структурная схема блока повторителей на фиг.З - структурная схема блока памяти; на фиг.4 - структурная схема блока вьщачи информации; на фиг.З - структурная схема блока индикации; на фиг.6 - структурная схема блока контроля.

Устройство содержит блок повторителей, блок 2 памяти, блок 3 вьщачи информации, блок 4 индикации, блок 5 контроля, формирователь 6, JKRS- триггер 7, резистор 8, светодиод 9 и кнопку 10, причем вход устройства соединен кодовой магистралью с входом блока I повторителей, выход которого кодовой магистралью подключен . к входу блока 5 контроля, к первому входу блока 2 памяти и к первому входу блока 3 вьщачи информации, второй вход которого кодовой магистралью соединен с выходом блока 2 памяти, а выход - с входом блока 4 индикации. Первый выход блока 5 контроля подключен к второму входу блока 2 памяти и к З -входу триггера 7, а второй выход к первому входу формирователя 6, выход которого подключен к третьему входу блока 2 памяти и к С-входу триггера 7, R-вход которого соединен с четвертым входом блока 2 памяти и через кнопку 10 с шиной нулевого потенциала. Нулевой выход триггера 7 подключен к второму входу формирователя 6 и через резистор 8 к катоду светодиода 9, анод которого соединен с шиной питания.

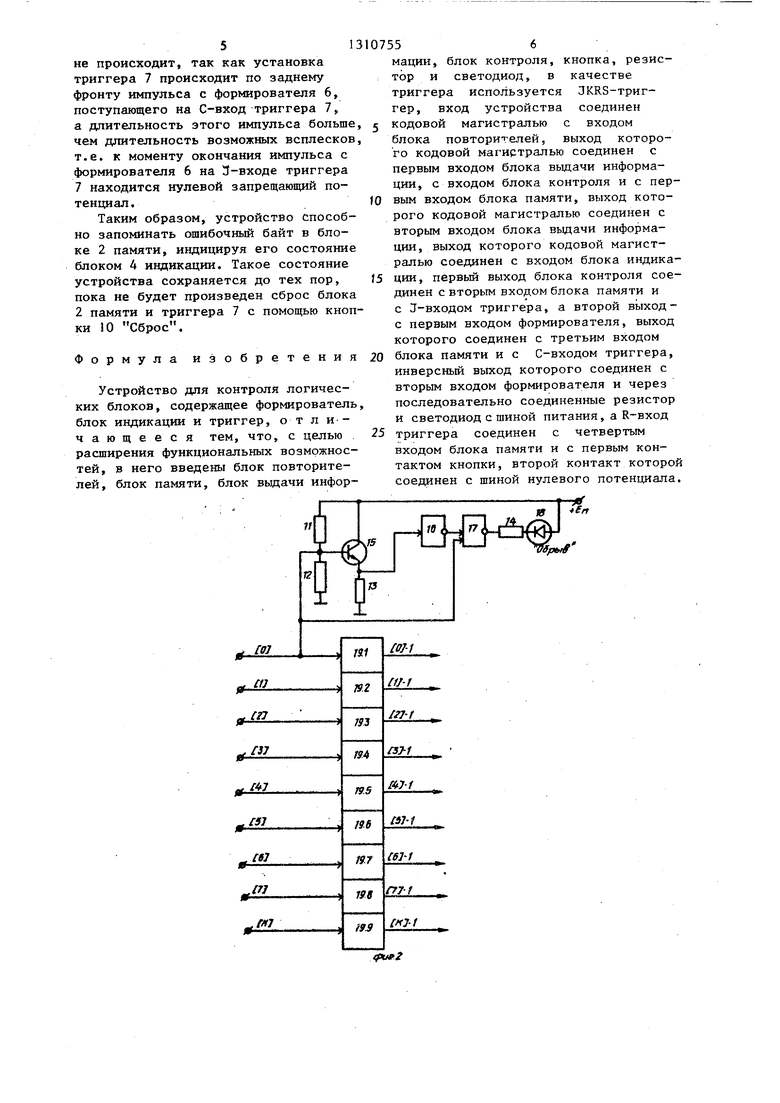

Блок 1 повторителей содержит резисторы П-14, транзистор 5, инвертор 16, элемент 2И-НЕ 17, светодиод 18 и повторители 19.1 - 19.9.

Повторители 19.1-19.9 необходимы для того, чтобы исключить возможность выхода из строя проверяемьтх логических элементов, имеющих ограниченную нагрузочную способность.

52

Нулевой вход (канал) блока 1 повторителей соединен также с базой транзистора 15 и через резистор 11 с шиной питания, а также через резистор I2 с шиной нулевого потенциала, к которой через резистор 13 подключен эмиттер транзистора 15, который, в свою очередь, соединен через инвертор I6 с первым входом элемента

2И-НЕ 17, второй вход которого подключен к нулевому входу блока 1 повторителей, а выход элемента 2И-НЕ 17 соединен через резистор 14 с катодом светодиода 18. Анод светоциода 18 и

коллектор транзистора 15 подключены к шине питания. Описанная схема предназначена для определения и индикации логического состояния Обрыв. Блок 2 памяти, структурная схема

которого приведена на фиг.З, выполнен в виде набора девяти JKRS-тригге- ров 20.1-20.9, первые П-входы которых подключены к выходам блока 1 повторителей. Вторые J-входы триггеров 20.120.9 объединены, на них подается потенциал Ошибка, формируемый блоком 5 контроля. На объединен11ые С входы триггеров 20.1-20.9 подается импульс Запись, формируемый формирователем

6. Объединенные R-входы триггеров 20.1-20.9 через кнопку 10 Сброс подключены к пшне нулевого потенциала.

Блок 3 выдачи информации, структурная схема которого приведена на фиг.4, состоит из набора девяти элементов 2-2И-ИЛИ-НЕ 21.1-21.9,,- причем первые входы первых схем 2И элементов 2-2И-ИЛИ-НЕ 21.1-21.9 соединены

с выходами блока 1 повторителей, а вторые входы объединены и подключены к первому контакту переключателя 22. Первые входы вторых схем 2И элементов 2-2И-РШИ-НЕ 21.1-21.9 соединены

с выходами блока 2 памяти, а вторые входы - с вторым контактом переключателя 22, третий контакт которого подключен к шине нулевого потенциала. Таким образом, в зависимости от положения переключателя 22 Память - Пробник на выход блока 3 вьщачи информации проходит информация либо с выходов блока 1 повторителей, либо с выходов блока 2 памяти, что обеспе

чивает возможность использования устройства для анализа состояния девяти логических цепей как в статическом режиме (например, при поиске неисп313

равности ЭВМ в потактовом режиме работы) , так и в динамическом режиме при выявлении сбойных ситуаций.

Блок 4 индикации, структурная схема которого приведена на фиг.5, содержит набор девяти светодиодов 23. - 23.9, аноды которых через резисторы 24.1-24.9 подключены к шине питания. Катоды светодиодов 23.1-23.9 подключены к выходам блока 3 выдачи информации .

Блок 5 контроля, структурная схема которого приведена на фиг.6, состоит из элемента 25 свертки по модулю 2, трех элементов 2И-НЕ 26-28 и двух инверторов 29 и 30. На входы элемента 25 подаются информационные разряды контролируемого байта с выходов блока 1 повторителей. Первый выход элемента 25 Нечет соединен с первым входом элемента 2И-НЕ 26, второй вход которого подключен к выходу контрольного разряда блэка 1 повторителей и через инвертор 29 к первому входу элемента 2И-НЕ 27, второй вход которого соединен с вторым выходом элемента 25 свертки по модулю 2. Выходы элементов 2И-НЕ 26 и 27 подключены к входам элемента 2И-НЕ 28, выход которого соединен с первым выходом блока 5 контроля и через инвертор 30 с вторым выходом блока 5.

Устройство работает следующим образом.

Информация о состоянии контролируемого байта через блок 1 повторителей поступает на входы блока 3 выдач информации, блока 2 памяти и блока 5 контроля. Если устройство находится в режиме Пробник, что задается переключателем 22 в блоке 3 выдачи информации, то блок 3 пропускает в блок 4 индикации информацию непосредственно с блока 1 повторителей. Включенное состояние светодиодов 23.1-23.9 в блоке 4 индикации соответствует единичному состоянию соответствующего бита информации в байте, выключенное - нулевому.

Таким образом, устройство позволяет наблюдать за изменением логических уровней одновременно в девяти цепях.

Если устройство находится в режиме Память, то информация через- блок 3 выдачи информации проходит на вход блока 4 индикации уже с выхода блока 2 памяти. Каждый входной байт

554

анализируется блоком 5 контроля, который в случае поступления байта с неправильной четностью, т.е. количество единичных разрядов в байте и

контрольном разряде четное, возбуждает на своих выходах сигнал- Ошибка, причем на первом выходе этот сигнал имеет единичный уровень, на втором - нулевой. Перепадом из единицы в нуль с второго выхода блока 5 контроля запускается формирователь 6, формирующий импульс, по заднему фронту которого триггер 7 устанавливается в единичное положение, так

как на J-входе триггера 7 в этот мо- мент находится разрешающий единичный потенциал Ошибка с первого выхода блока 5 контроля. Одновременно ошибочный байт и контрольнъй разряд,

поступающие на первые J-входы триггеров 20.1-20.9, запоминаются в блоке 2 памяти, так как на вторьгх J-вхо- дах триггеров 20.1-20.9 находится разрешающий единичный потенциал Ошибка с первого выхода блока 5 контроля, а на С-входы триггеров 20.1-20.9 поступает синхронизирующий импульс с выхода формирователя 6. Нулевой потенциал с инверсного выхода триггера,

7 вызывает свечение светодиода 9,

сигнализирующего о произошедшем сбое. Кроме того, нулевой потенциал с обратного выхода триггера 7 пост-упает на второй вход форьшрователя 6, запРбщая его дальнейшую работу. Это необходимо для того, чтобы исключить возможную порчу информации в блоке 2 памяти при появлении на выходе устройства последующего байта с неправильной четностью.

Длительность импульса, формируемого формирователем 6, выбрана равной половине длительности импульса тактовой частоты, вырабатываемой генератором ЭВМ. Это необходимо для исключения возможного ложного опрокидываний триггера 7, так как информационные биты могут поступать с некоторым фазовым сдвигом, что связано с различным временем переключения различного рода регистров и счетчиков, с различным временем задержки, вносимых кабельными приемниками и перео

датчиками и т.д. Фазовый сдвиг инфор- мационных битов может вызвать ложные всплески на выходах блока 5 контроля и, соответственно, запуск формирователя 6, но опрокидывания триггера 7

не происходит, так как установка триггера 7 происходит по заднему фронту импульса с формирователя 6, поступающего на С-вход триггера 7, а длительность этого импульса больше, чем длительность возможных всплесков, т.е. к моменту окончания импульса с формирователя 6 на 3-входе триггера 7 находится нулевой запрещающий потенциал.

Таким образом, устройство способно запоминать ошибочный байт в блоке 2 памяти, индицируя его состояние блоком 4 индикации. Такое состояние устройства сохраняется до тех пор, пока не будет произведен сброс блока 2 памяти и триггера 7 с помощью кнопки 10 Сброс.

Формула изобретения

Устройство для контроля логических блоков, содержащее формирователь, блок индикации и триггер, от л и - чающееся тем, что, с целью расширения функциональных возможностей, в него введены блок повторителей, блок памяти, блок вьщачи инфор

мации, блок контроля, кнопка, резистор и светодиод, в качестве триггера используется ЗККЗ-трнг- гер, вход устройства соединен кодовой магистралью с входом блока повторителей, выход которого кодовой магистралью соединен с первым входом блока вьщачи информации, с входом блока контроля и с первым входом блока памяти, выход которого кодовой магистралью соединен с вторым входом блока вьодачи информации, выход которого кодовой магистралью соединен с входом блока индикации, первый выход блока контроля соединен с вторым входом блока памяти и с J-входом триггера, а второй выход- с первым входом формирователя, выход которого соединен с третьим входом блока памяти и с С-входом триггера, инверсный выход которого соединен с вторым входом формирователя и через последовательно соединенные резистор и светодиод с шиной питания, а R-вход триггера соединен с четвертым входом блока памяти и с первым контактом кнопки, второй контакт которой соединен с шиной нулевого потенциала.

фиг. З

/7OAff/r7

I f, f«

J / ffffHC/H

-L. фи&.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических устройств | 1985 |

|

SU1290213A1 |

| Устройство для контроля блоков оперативной памяти | 1989 |

|

SU1689994A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА | 1996 |

|

RU2105348C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА | 1997 |

|

RU2118846C1 |

| Устройство для контроля электрического монтажа | 1990 |

|

SU1794258A3 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ СИГНАЛИЗАЦИИ | 2009 |

|

RU2406157C2 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля логических блоков. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения контроля байта информации и запоминания его значения в сбойных ситуациях. Для этого в устройство, содержащее формирователь 6, блок индикации 4 и триггер 7, дополнительно введены блок 1 повторителей, блок 2 памяти, блок 3 выдачи информации, блок 5 контроля, резистор 8, светодиод 9 и кнопка 10 сброса, а в качестве триггера 7 использован JKRS-триггер. Устройство способно запомнить ошибочный байт в блоке 2 памяти, индицируя его состояние блоком 4. Такое состояние устройства сохраняется до тех пор, пока не будет произведен сброс блока 2 памяти и триггера 7 с помощью кнопки 10. 6 ил. i (Л фиг.1 Vf/r

| Логический пробник | 1981 |

|

SU995030A1 |

| Логический пробник | 1980 |

|

SU917144A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-05-15—Публикация

1985-07-26—Подача