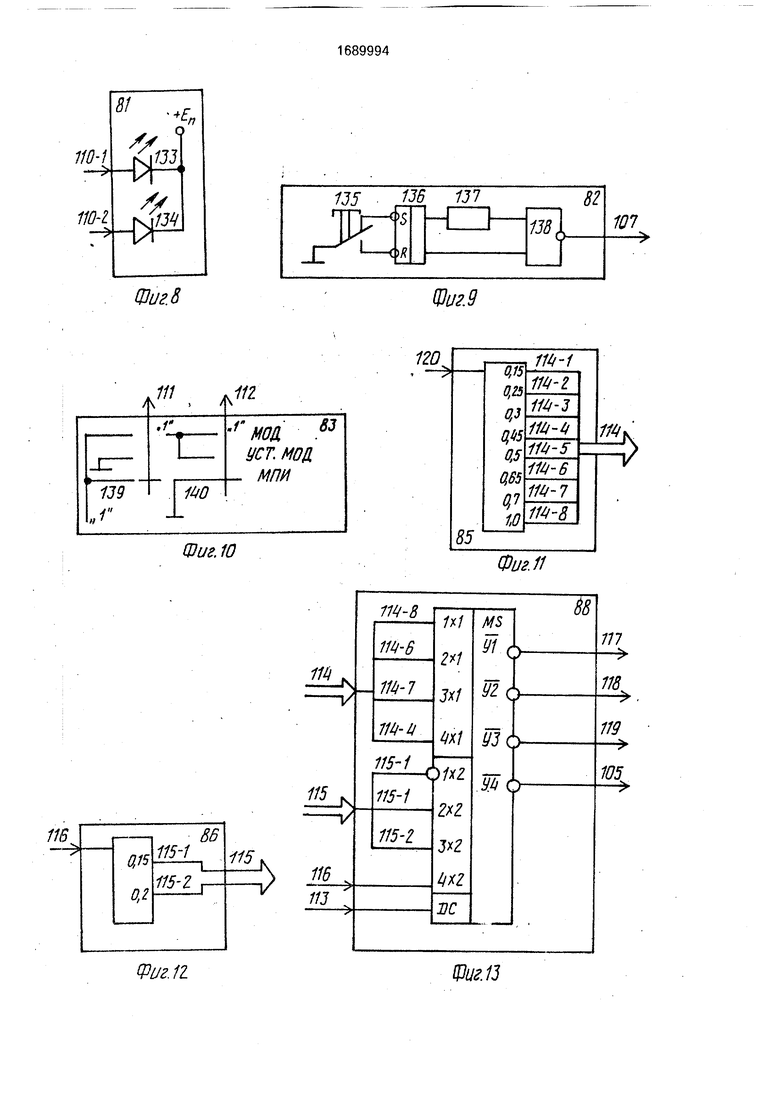

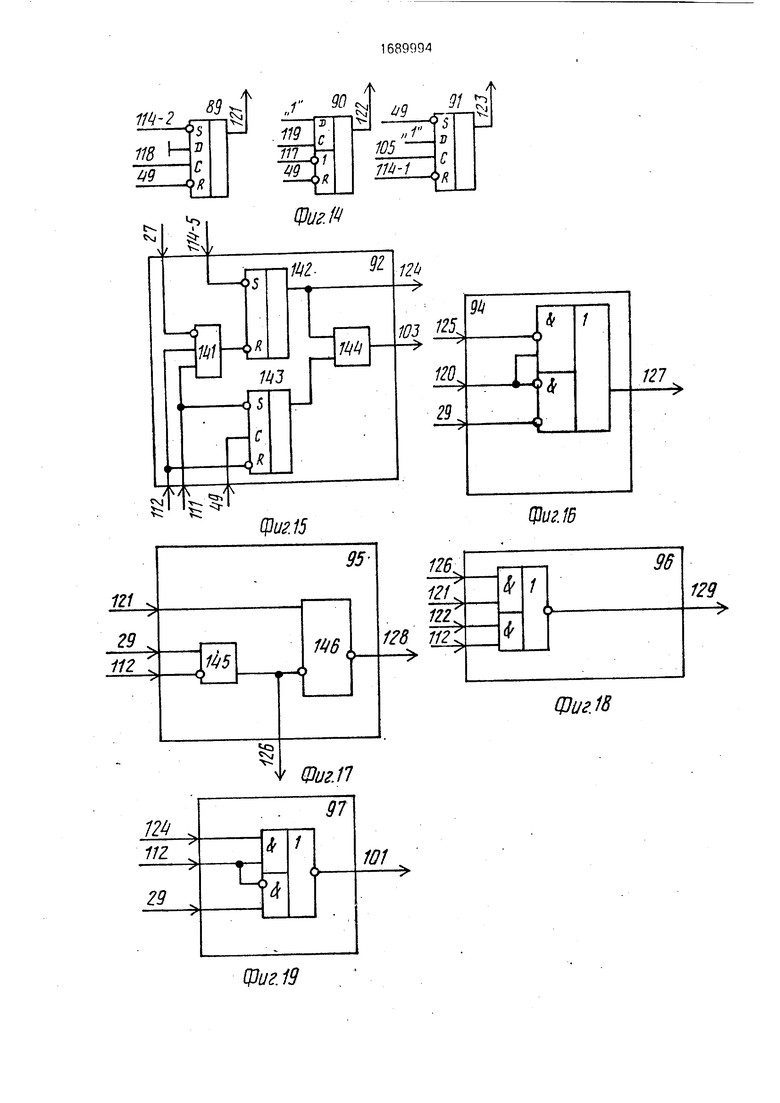

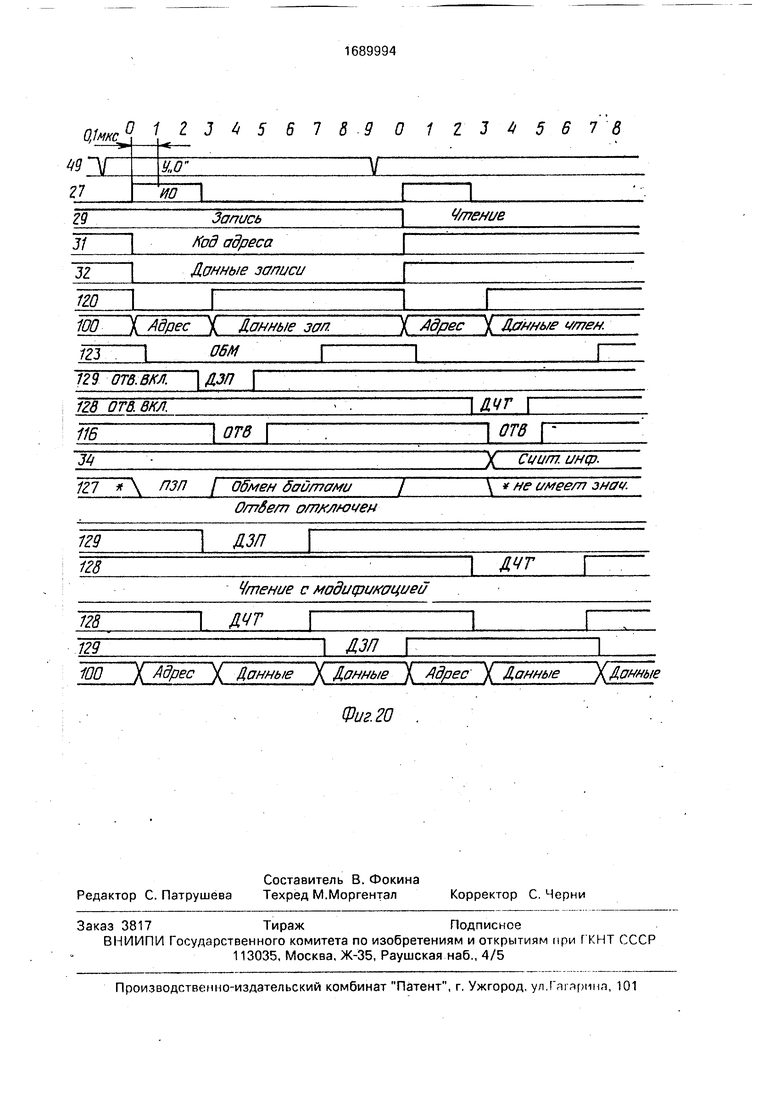

- схема третьего блока инверсии данных; на фиг. 5 - схема четвертого блока инверсии данных; на фип 6 - схема блока передатчиков информации; на фиг. 7 - схема блока фиксации ошибок; на фиг. 8 - схема пятого блока индикации; на фиг. 9 - схема второго блока сброса ошибки; на фиг. 10 - схема второго блока управления режимами; на фиг. 11 - схема первого распределителя импульсов; на фиг. 12 - схема второго распределителя импульсов; на фиг. 13 - схема третьего коммутатора; на фиг. 14 - схемы второго, третьего формирователей управляющих сигналов; на фиг. 15 - схема блока управления инверсиями; на фиг. 16 - схема первого блока формирования признака режима; на фиг, 17 - схема второго блока формирования признака режима; на фиг. 18 - схема третьего блока формирования признака режима; на фиг. 19 - схема блока управления приемопередатчиками; на фиг. 20 - временная диаграмма работы устройства.

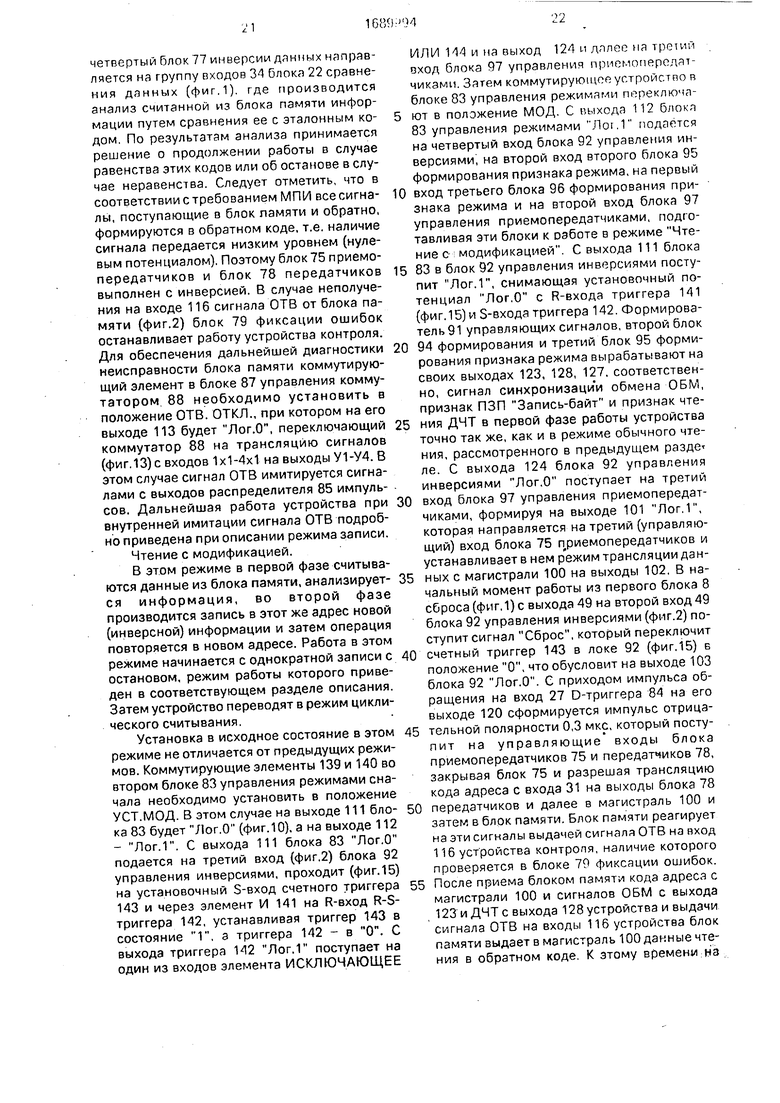

Устройство содержит (фиг, 1, 2) генератор 1 тактовых импульсов, первый формирователь 2 управляющих импульсов, счетчик 3 адреса, блок 4 установки адреса, первый коммутатор 5, второй коммутатор 6, второй блок 7 индикации адреса, первый блок 8 сброса, счетчик 9 циклов, блок 10 выбора адреса синхронизации, блок 11 сравнения адресов и циклов, блок 12 формирования признака операции, блок 13 управления режимами, блок 14 формирования признака режима, первый блок 15 задания начального кода, генератор 16 псевдослучайного кода, третий блок 17 индикации, первый блок 18 инверсий данных, формирователь 19 признака инверсии данных, второй блок 20 инверсии данных, четвертый блок 21 индикации числа, блок 22 сравнения данных, формирователь 23 сигнала опроса, блок 24 пуска, блок 25 коммутации, первый блок 26 индикации неисправных разрядов, первый выход 27 устройства (выход импульса обращения), второй выход 28 синхронизации, третий выход 29 признака операции, четвертый выход 30 сигнала неравенства (признака неисправности), пятую группу выходов 31 кода адреса, группу информационных выходов 32, первый вход 33 устройства (вход признака инверсии по адресам), вторую группу входов 34 устройства (входы считанной информации), группы связей (кодовые шины 35-46, а также отдельные связи 47-74.

Блоки 12-14, 19 со связями образуют блок местного управления. На фиг. 2 блок 74 приемопередатчиков информации,- третий 76 и четвертый 77 блоки инверсии данных,

блок 78 передатчиков информации, блок 79 фиксации ошибок, блок 80 выключения ошибок, пятый блок 81 индикации, второй блок 82 сброса, второй блок 83 управления режимами, D-триггер 84, первый распределитель 85 импульсов, второй распределитель 86 импульсов, блок 87 управления третьим коммутатором, третий коммутатор 88, второй 89, третий 90, четвертый 91 формирова0 тели управляющих сигналов, блок 92- управления инверсиями, третий блок 93 управления режимами, второй 94, третий 95 и четвертый 96 блоки формирования признака режима, блок97 управления приемопере5 датчиками, пятый блок 98 формирования признаков режимов.

На фиг. 2 показаны также связи и входы, выходы устройства 99-129.

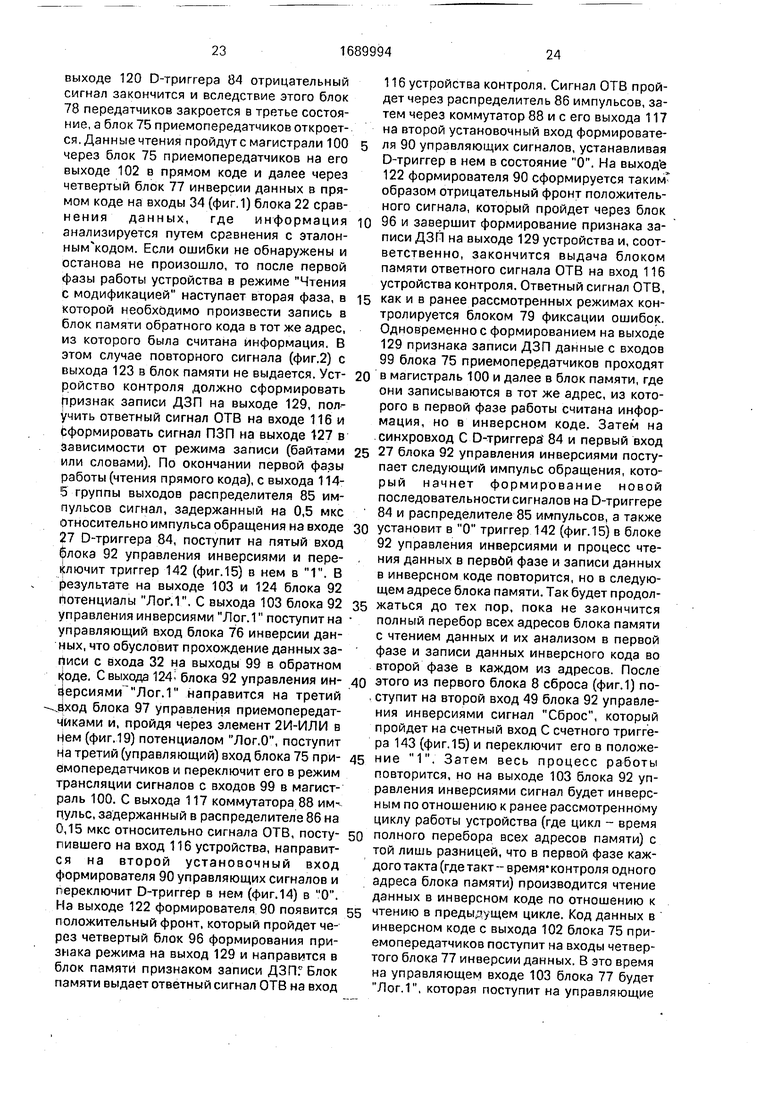

Блок 75 приемопередатчиков информа0 ции(см.фиг.З) содержит электронные переключатели, приемные входы которых являются групповыми входами 99 блока 75, а выходы - групповыми выходами 102, Магистральные входы-выходы электронных

5 переключателей соединены с магистральными шинами 100 блока 75 приемопередатчиков. Управляющие входы электронных переключателей соединены с соответствующими входами 101 и 120 блока 75. При этом

0 по входу 101 обеспечивается переключение режима работы электронных переключателей. При потенциале Лог.О электронные переключатели обеспечивают прием данных по входам 99 и выдачу в магистраль 100,

5 а при потенциале. Лог.1 на входе 101 прием с магистрали 100 и выдачу в магистраль 102. По входу 120 обеспечивается выключение блока приемопередатчиков, т.е. при потенциале лог.О на входе 120 разрешается

0 работа электронных переключателей в блоке 75, а при потенциале Лог.1 на выходе 120 электронные переключатели будут в третьем состоянии (закрыты) и на магистральных выходах 100 блока 75 приемопере5 датчиков будет высокое сопротивление. В опытном образце в качестве электронных переключателей использовались микросхемы 585 АП26, обеспечивающие переключение 16-ти разрядной информации данных

0 Третий блок 76 инверсии данных (фиг,4) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выполняющих функцию управляемых инверторов. Информационные входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соедине5 ны с группой одов 32, другие входы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены между собой и подключены к входу 103 блока 76 инверсии данных. При потенциале Лог.О на входе 103 данные с входов 32 транслируются на выходы 99 блока 76 в прямом коде, а при потенциале Лог.1 - в инверсном.

Четвертый блок 77 инверсии данных (фиг.5) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выполняющих роль управ- ляемых инверторов. Информационные входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с группой входов 102, другие входы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены между собой и подключены к входу 103 блока 77 инверсии данных. При потенциале Лог.О на входе 103 данные с входов 102 транслируются на выходы 34 блока 77 в прямом коде, а при потенциале Лог.1 - в инверсном. В опытном образце устройства блоки 76 и 77 инверсии данных имели 16 разрядов и выполнялись на микросхемах 133ЛП5.

Блок 78 передатчиков информации (фиг.6) содержит транслирующие элементы, приемные входы которых соединены с группой входов 31, а выходы - с группой выходов 100 блока 78. Управляющий вход транслирующих элементов соединен с входом 120 блока 78 передатчиков. При потенциале Лог.О на входе 120 транслирующие элементы открыты и обеспечивают передачу данных с входов 31 на выходы 100. При потенциале Лог.1 на входе 120 транслирующие элементы закрыты и на выходах 100 блока 78 передатчиков высокое сопротивление (третье состояние),

В опытном образце устройства в блоке 78 передатчиков в качестве транслирующих элементов использовались микросхемы КР 580ВА87, обеспечивающие трансляцию 16- ти разрядной информации адреса.

Блок 79 (фиг.7) содержит Ь-триггер 130, D-вход которого соединен с входом 105 блока 79. Установочный R-вход D-триггера 130 связан с входом 107 блока 79. Синхровход С D-триггера 130 соединен со входом 108 блока 79. Нулевой выход D-триггера 130 связан с первым входом элемента И 131 и с одним из выходов группы 110-1 блока 79. Второй вход элемента И 131 подключен к одному из выходов группы 110-2 блока 79 и к выходу элемента И-НЕ 132, первый и второй входы которого связаны соответственно с входом 104 и 106 блока 79. Наличие сигнала Ответ на входе 105 фиксируется в D-триггере 130 с приходом сигнала ЗП/ЧТ со входа 108. Признак отсутствия сигнала Ответ с выхода D-триггера 130 выдается на один из выходов 110-1. Признак неисп- равности НИС ЗУ поступает на вход 104 и через элемент И-НЕ 132 при условии разрешающего потенциала на управляющем входе элемента И-НЕ 132 проходит на один из выходов группы выходов 110-2. Признаки

ошибок объединяются на элементе И 131 и с его выхода направляются на выход 109 блока 79. D-триггер 130 в опытном образце выполнен на микросхеме 133 ТМ2.

Блок 80 выключения ошибок содержит коммутирующий элемент, один из контактов которого соединен с шиной Лог.1, а другой - с шиной Лог.О (1). Выход коммутирующего элемента является выходом 106 блока 80. В опытном образце устройства коммутирующий элемент был выполнен на тумблере П1ТЗ.

Пятый блок 81 индикации (фиг.8) содержит светодиоды 133, 134, аноды которых соединены, соответственно, с входами 110, а катоды объединены и подключены к источнику напряжения +Е (через резисторы, не показанные на схеме). В опытном образце блок 81 индикации выполнен на светодио- дах ЗЛ102.

Второй блок 82 ошибки (фиг.9) содержит коммутирующий элемент 135 (выполненный в виде кнопки), средний контакт которого соединен с шиной Лог.О (1), а выходы соответственно, с установочным и обнуляющим входами триггера 136, единичный выход которого через элемент 137 задержки соединен с первым входом элемента И-НЕ 138, а нулевой выход со вторым входом элемента И-НЕ 138, выход которого связан с выходом 107 блока 82.

В исходном состоянии средний контакт коммутирующего элемента 135 нормально замкнут со своим пе рвым выходом и нормально разомкнут со вторым выходом. При этом триггер 136 установлен в состояние 1, следовательно, на одном из входов элемента И-НЕ 138 будет единичный потенциал, а на другом - нулевой. Поскольку коммутирующий элемент 135 выполнен в виде кнопки с самовозвратом, то после нажатия оператором этой кнопки на выходе элемента И-НЕ 138 при отпускании кнопки сформируется импульс сброса отрицательной полярности, поступающий на выход 107. В опытном образце устройства коммутирующий элемент 135 выполнен на кнопочном переключателе типа ПКн2, триггер 136 - на микросхеме 133 ТМ2, а в качестве элемента задержки 137 использовались микросхемы 136 ЛН1.

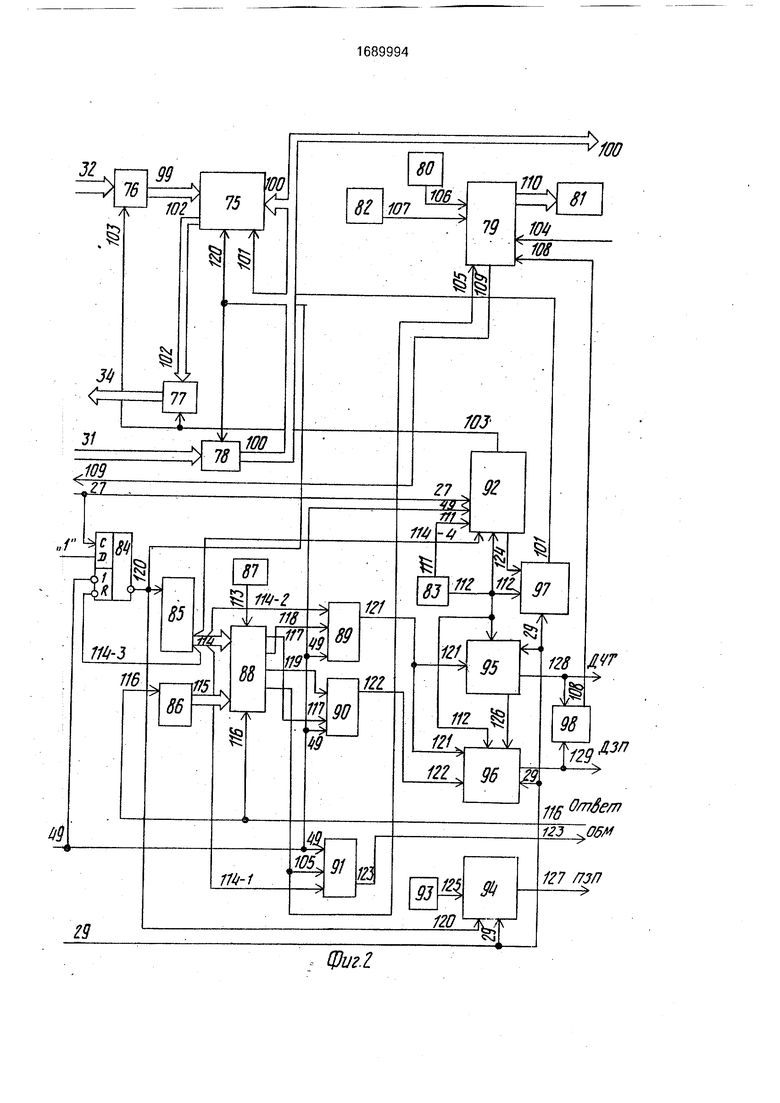

Второй блок 83 управления режимами (фиг. 10) содержит коммутирующие элементы 139, 140. Первый и третий контакт коммутирующего элемента 139, первый и второй контакты коммутирующего элемента 140 подключены к шине Лог.1, а второй контакт элемента 139 и третий контакт элемента 140 соединены с шиной Лог.О, Подвижные контакты коммутирующих элементов 139 и 140 являются выходами соответственно 111, 112 блока 83. Коммутирующие элементы 139, 140 механически связаны и переключаются синхронно. В опытном образце коммутирующие элементы 139 и 140 выполнены на переключателе типа ПГ2.

Первый распределитель 85 импульсов (фиг.11) выполнен на элементе задержки. Вход элемента задержки является входом 120 распределителя 85 импульсов, а выходы

-соответственно выходами 114-1, 114-2, 114-3, 114-4, 114-5, 114-6, 114-7, 114-8. В опытном образце устройства в качестве элемента задержки использовалась линия задержки типа ЛЗС-20-1-600 (элементы согласования входа и выходов линии задержки на схеме не показаны).

Второй распределитель 86 импульсов (фиг. 12) выполнен на элементе задержки. Вход элемента задержки соединен с входом 116 распределителя 86 импульсов, а выходы

-с соответствующими выходами 115-1 и 115-2, В опытном образце элемент задержки был выполнен на микролинии ЛМЗ-0,25- 600 (элементы согласования входа и выходов линий задержки на схеме не показаны).

Третий коммутатор 88 (фиг. 13) выполнен на селекторе-мультиплексоре. Первый, второй, третий и четвертый входы селектора-мультиплексора являются соответствующими входами 114-8, 114-6, 114-7, 114-4 коммутатора 88, Пятый (инвертирующий) и шестой входы селектора-мультиплексора соединены с входом 115-1 коммутатора 88, а седьмой и восьмой входы соединены, соответственно, со входами 115-2 и 116 коммутатора 88. Управляющий вход ДС селектора-мультиплексора подключен к входу 113 коммутатора 88. Первый, второй, третий, четвертый инвертирующие выходы селектора-мультиплексора являются, соответственно, выходами 117, 118, 119, 105 коммутатора 88. В опытном образце устройства в качестве селектора-мультиплексора использовалась микросхема 530 КП14.

Второй 89, третий 90, четвертый 91 формирователи,управляющих сигналов (фиг.14) выполнены на D-триггерах. Установочный S-вход триггера формирователя 89 является входом 114-2. Синхровход С-триггера - входом 118, обнуляющий R-вход - входом 49. D-вход триггера подключен к шине Лог .О. Выход триггера является выходом 121 формирователя 89.

Синхровход С триггера формирователя -90 является входом 119, первый обнуляющий R-вход входом 117, а второй обнуляющий R-вход - входом 49, D-вход триггера

подключен к шине Лог.1. Выход триггера является выходом 121 формирователя 89.

Установочный S-вход триггера формирователя 91 является входом 49. Синхровход С-входом 105, обнуляющий R-вход - входом 114-1, D-вход триггера соединен с шиной Лог,1. Выход триггера является выходом 123 формирователя 91.

В опытном образце устройства в формирователях 89-91 использовались триггеры на микросхемах 133 ТМ2. Во избежание временных накладок установки триггеров по входам R и S осуществляется укороченными импульсами. Схемы укорочения импульсов на входах R- и S-триггеров на фиг. 14 не показаны.

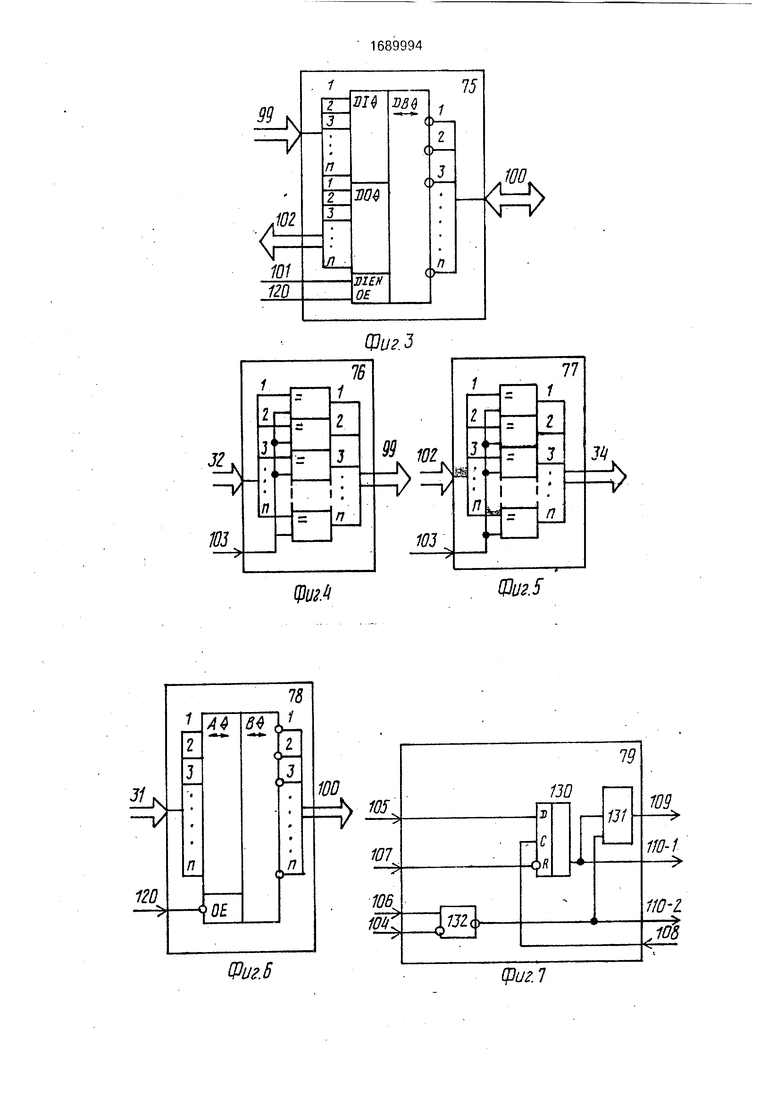

Блок 92 управления инверсия (фиг.15) содержит элемент И 141,выходом соединенный с обнуляющим R-входом R-S-триггера

142. Инвертирующий вход элемента 141 соединен со входом 27 блока 92, второй вход - с обнуляющим R-входом счетного тригера 143 и с входом 112 блока 92. Третий вход элемента И 141 связан с установочным Sвходом счетного триггера 143 и с входом 111 блока 92. Установочный S-вход триггера 142 является входом 114-5, а синхровход С триггера 143 - входом 49 блока 92, Выход триг- гера 142 соединен с выходим 124 блока 92 с

одним из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 144, другой вход которого связан с выходом триггера 143, а выход-с выходом 103 лока 92. В опытном образце устройства триггеры 142 и 143 выполнены на микросхемах 133 ТМ2, а элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 144 - на микросхеме 133 ЛП5.

Первый блок 94 формирования признака режима (фиг. 16) содержит цифровой узел, реализующий функцию 2И-ИЛИ. Первый (инвертирующий) вход первой группы И соединен с входом 125 блока 94. Второй вход первой группы соединен со вторым (инвертирующим) входом второй группы И и с входом 120 блока 94. Третий (инвертирующий) вход второй группы И подключен к входу 29 блока 94. В опытном образце блок 94 выполнен на микросхемах 133ЛН1; 133ЛР1. Третий блок 95 формирования признака режима (фиг.17) содержит элемент И

145, один из входов которого является входом 29 блока 95, другой (инвертирующий) - входом 112, а выход соединен с инвертирующим входом элемента НЕ 146 и является выходом 126 блока 95. Второй вход элемента НЕ 146 . н с входом 124 блока 89 Выход элемента hE 146 соединен с выходом 128. В опытном образце элементы И 145 и НЕ 146 выполнялись на микросхемах 133ЛН1, 133ЛПЗ, 133ЛИ1.

Третий блок 96 формирования признака режима (фиг. 18) содержит элемент 2И-ИЛ И- НЕ. Входы элемента 2И-ИЛИ-НЕ являются соответствующими входами 126, 121, 122, 112 блока 96, а выход соединен с выходом 129 блока 96. В опытном образце элемент 2И-ИЛИ-НЕ выполняется на микросхеме 133ЛР1.

Блок 97 управления приемопередатчиками (фиг.18) содержит элемент 2И-ИЛИ- НЕ. Один из входов первой группы И элемента 2И-ИЛИ-НЕ соединен с первым входом 29 блока 97, а другой инвертирующий - с одним из входов другой-группы И элемента 2И-ИЛИ-НЕ и с входом 112 блока 97. Второй вход второй группы И элемента 2И-ИЛИ-НЕ связан с третьим входом 124 блока 97, а выход является выходом 101.

Назначение отдельных узлов дополнительного устройства приведено на фиг. 2.

Блок 75 приемопередатчиков информации обеспечивает трансляцию данных при записи в блок памяти группы входов 99 в магистраль 100, подключенную к входам- выходам контролируемого блока памяти. В режиме чтения блок 75 приемопередатчиков пропускает данные из магистрали 100 на выходы 102, подключаемые к основной части устройства контроля блоков оперативной памяти для дальнейшего анализа информации. Управление переключением направления передачи данных осуществляется по входу 101 (Д1ЕМ) Выключение блока 75 в третье состояние осуществляется при поступлении Лог.1 на вход 120.

Третий блок 76 инверсии данных предназначен для инвертирования данных входной информации при записи данных в блок памяти при проверке его работоспособности в режиме Чтение с модификацией.

Четвертый блок 77 инверсии данных обеспечивает инвертирование данных выходной информации при чтении данных из блока памяти при контроле его в.режиме- Чтение с модификацией.

Блок 78 передатчиков информации транслирует коды адреса с группы адресных входов 31 в магистраль 100. Выключение блока 78 осуществляется при подаче на управляющий вход 120 потенциала Лог.1. При этом на его выходах будет третье состояние, характеризующееся высоким выходным сопротивлением.

Блок 79 фиксации ошибок регистрирует признаки ошибок контролируемого блока памяти. Всего предусмотрено два признака ошибок, сопровождающих процесс обмена информации между устройством контроля и блоком памяти.

На вход 104 поступает признак неисправности (НИС ЗУ) из блока памяти, на пход 105-признак(ОТВ)блока памяти при обмене информацией с устройством контроля. Отсутствие признака ОТВ воспринимается блоком 79 фиксации ошибок как неисправность блока памяти. Блок 79 фиксации ошибок формирует потенциалы ошибок на своих выходах 110 и посылает их в пятый

0 блок 81 индикации.

Блок 80 выключения ошибок обеспечивает отключение признака ошибок, поступающего по входу 104 (ошибка НИС ЗУ) в блок фиксации ошибок. Отключение признака

5 ошибок используется в режимах диагностики ошибок контролируемого блока памяти. Пятый блок 81 индикации обеспечивает визуальную сигнализацию о появлении ошибок, зафиксированных при выявлении

0 отсутствия сигнала ответа (ОТВ) или при поступлении сигнала ошибки (НИС ЗУ) из блока памяти.

Блок 82 сброса ошибок формирует сигнал для приведения блока 79 фиксации оши5 бок в исходное состояние.

Второй блок 83 управления режимами формирует потенциалы на выходах 111,112, для управления работой блока 92 управления инверсиями второго , третьего 95 и

0 четвертого 96 блоков формирования признаков режима и блока 97 управления приемопередатчиками при включении режима работы Чтение с модификацией.

D-триггер 84 форм ирует импульс для пу5 ска первого распределителя импульсов 85. D-триггер 84 включен так, что обеспечивается самоустановка его в исходное состояние, обуславливающая его готовность к работе сразу при включении напряжения питания.

0 В опытном образце устройства D-триггер 84 выполнен на микросхеме 133ТМ2.

Первый 85 и второй 86 распределители импульсов формируют сигналы на своих выходах 114 и 115 для управления работой

5 второго 89 и четвертого 91 формирователей управляющих сигналов и блока 92 управления инверсиями, а также для сброса D-триг- гера 84 в исходное состояние и для управления через третий коммутатор бло0 ком 79 фиксации ошибок и вторым 89, третьим 90 и четвертым 91 формирователями управляющих сигналов.

Блок 87 управления третьим коммутатором 88 обеспечивает переключение комму5 татора 88 при трансляции сигналов с входов на выходы. В опытном образце устройства блок 87 выполнен на тумблере П1ТЗ.

Третий коммутатор 88 обеспечивает трансляцию сигналов со входов 114 и 115 на выходы 105, 117-119. Переключение коммугатора осуществляется при изменении потенциала на управляющем входе 113, поступающего из блока 87 управления третьим коммутатором.

Второй формирователь 89 управляющих сигналов управляет работой третьего 95 и четвертого 96 блоков формирования признаков режима.

Третий формирователь 90 управляющих сигналов управляет работой четвертого блока 96 формирования признака режима.

Четвертый формирователь 91 управляющих сигналов формирует признак синхронизации обмена (ОБМ) при взаимодействии устройства контроля с блоком памяти.

Блок 92 управления инверсиями формирует признак инверсии для переключения третьего 76 и четвертого 77 блоков инверсии данных в режиме трансляции данных в прямом или обратном коде при контроле блоков памяти тестом Чтение с модификацией

Третий блок 93 управления режимами управляет работой второго блока 94 формирования признака режима при изменении режима записи информации в блок памяти с записи словами на запись байтами.

Второй блок 94 формирования признака режима формирует признак записи информации в блок памяти словами или байтами (признак ПЗП). , Третий блок 95 формирования признака режима вырабатывает признак операции Чтение (ДЧТ) при считывании данных из блока памяти.

Четвертый блок96формирования признака режима вырабатывает признак операции Запись СДЗП) при записи данных в блок памяти.

Блок 97 управления приемопередатчиками управляет работой блока 75 приемопередатчиков и блока 78 передатчиков.

Пятый блок 98 формирования признаков режимов формирует смешанный сигнал .Запись-чтение (ЗП/ЧТ) для синхронизации работы блока 79 фиксации ошибок.

Запись данных байтами.

Для работы в этом режиме органы управления устанавливаются в исходное состояние. Коммутирующий элемент блока 80 выключения ошибок - в положение НИС ЗУ, обеспечивающий Лог.1 на выходе 106. Механически связанные коммутирующие элементы 139 и 140 (фиг. 10) во втором блоке 83 управления режимами - в положение МПИ, формируя на выходах 111 и 112, соответственно, потенциалы Лог.1 и Лог.О. Коммутирующий элемент в блоке 87 управления третьим коммутатором - в положение Ответ, устанавливающий на выходе 113 потенциал Лог.1, разрешающий прохождение сигналов с входов Х2 на выходы У мультиплексора в коммутаторе 88. Входы XI при этом запираются. Коммутирующий элемент в третьем блоке 93 управления режимами - в положение ПЗП (байт), при этом на его выходе 125 будет потенциал

Лог.1. В этом случае на один из входов элемента И-НЕ 132 (см.фиг.7) в блоке 79 фиксации ошибок по входу 106 поступит Лог.1, разрешая прохождение сигнала ошибок (НИС ЗУ) из блока памяти по входу 104

0 через элемент И-НЕ 132 на один из входов элемента И 131 и на выход 110-2. На вход 112 блока 92 управления инверсиями поступит Лог.О, устанавливающий триггер 142 (см.фиг.15) через элемент И 141 и триггер

5 143 в состояние О, обеспечивающее на их выходах nv соответственно, на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 144 и на выходах 103, 124 Лог.О. С выхода 103 блока 92 управления инверсиями (фиг.2) Лог.О

0 направляется на управляющие входы 103 третьего 76 и четвертого 77 блоков инверсии данных, обеспечивая прохождение через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг. 2, фиг.5) данных с входов 32 на выходы 99

5 блока 76 и с входов 102 на выходы 34 блока 77 в прямом коде.

Режим записи задается потенциалом Лог.1, поступившим с выхода 29 блока 12 формирования признака операции на пер0 вые входы первого и второго блоков формирования 94 и 95 признака режима и блока 97 управления приемопередатчиками. При этом элемент 2И-ИЛИ в первом блоке 94 формирования (фиг.16) закрыт потенциала5 ми Лог,1, поступившими по входам 29 и 125. На выходе 127 будет сигнал Лог.О длительностью, равной длительности сигнала Запись на входе 29, что соответствует сигналу ПЗП на временной диаграмме на

0 фиг. 20 при записи данных байтами.

Триггерные схемы устройства устанавливаются в начальное состояние сигналом Сброс, поступившим с выхода 49 первого блока 8 сброса. Этим сигналом в исходное

5 состояние устанавливаются генератор 1 тактовых импульсов, первый формирователь 2 управляющих сигналов, счетчик 3 адреса, генератор 16 псевдослучайного кода, блок 22 сравнения данных, D-триггер 84,

0 второй 89, третий 90 и четвертый 91 формирователи управляющих сигналов. На нулевом выходе 120 D-триггера 84 будет Лог.1, на выходах 121 и 122 второго 89 и третьего 90 формирователей управляющих сигналов

5 установится Лог.О, а на выходе 123 четвертого формирователя 91 управляющих сигналов - Лог.1. После нажатия оператором кнопки Пуск в блоке 24 пуска в первом формирователе 2 нз выходе 27 (фиг. 1) вырабатывается импульс обращения положительной полярности, который направляется в блок 23, а также на сиихровход С D-триг- гера 84 (фиг.2) и на первый вход блока 92 управления инверсиями. Одновременно с выхода 31 второго коммутатора 6 (фиг.1) по- ступает код адреса в блок 78 передатчиков информации (фиг.2), а с выхода 32 второго блока 20 инверсии данных - код данных информации записи на входы 32 третьего блока 76 инверсии данных. С поступлением импульса обращения по входу 27 (фиг.2) D- триггер 84 переключается в состояние 1, а на его нулевом выходе появится сигнал Лог.О, отрицательный перепад этого сигнала поступит в первый распределитель 85 импульсов и будет распространяться по линии задержки внутри распределителя 85, формируя на выходах 114 сигнала, задержанные относительно импульса обращения на различное время. Так, на первом выходе 114-1 задержка составит 0,15 мкс, на втором 114-2 - 0,25 мкс, на третьем 114-3 - 0,3 мкс, на четвертом 1.14-4 - 0,45 мкс, на пятом 114-5 - 0,5 мкс, на шестом 114-6 - 0,65 мкс, на седьмом 114-7 - 0,7 мкс, на восьмом 114-8 - 1.0 мкс. С третьего выхода 114-3 первого распределителя 85 импульсов отрицательный сигнал, задержанный на 0,3 мкс, поступит на второй установочныый R-вход 0-триггера 84 и переключит его в состояние О. На выходе 120 D-триггера 84 снова станет Лог.1. Таким образом, на выходе 120 D-триггера 84 формируется сигнал отрицательной полярности длительностью 0,3 мкс, который подается на вход первого распред- лителя 85 импульсов. В результате на выходах 114 распредлеителя 85 будут импульсы отрицательной полярности с указанными задержками и длительностью 0,3 мкс, С выхода 120 D-триггера 84 импульс (длительно- стью 0,3 мкс) поступит в блок 75 приемопередатчиков и блок 78 передатчиков информации, выключая блок 75 приемопередатчиков в третье состояние на выходе и снимая запрет на работу блока 78 передат- чиков информации, В это время на выходе 101 блока 97 управления приемопередатчиками (фиг,2, 19) сигнал Лог.О, который направляется на третий вход 101 блока 75 приемопередатчиков и переключает его в режим пропуска данных с входов 99 в магистраль 100. Код адреса с выходов 31 второго коммутатора 6 (фиг. 1) проходит через открытый блок 78 передатчиков (фиг.2) и в инверсном коде направляется в магистраль 100 и далее в проверяемый блок памяти. Через 0,15 мкс отрицательный импульс с первого выхода 114-1 распределителя 85 импульсов поступит на третий вход четвертого формирователя 91 управляющих сигналов (фиг.11,

14), что обусловит на его выходе 123 сигнал ОБМ (синхронизация обмена), который направляется в блок памяти, подготавливая его к работе, Блок памяти принимает код адреса с магистрали 100 и запоминает его в своем регистре. Через 0,3 мкс отрицательный импульс на выходе 120 D-триггера 84 заканчивается, выключая этим блок 78 передатчиков и включая (снимая запрет) блок 75 приемопередатчиков. Данные записи с выходов 32 второго блока 20 инверсии данных (фиг.1) проходят в прямом коде через третий блок 76 инверсии данных (фиг.2), поступают на входы 99 блока 75 приемопередатчиков, транслируются через него в магистраь 100 в инверсном коде и далее направляются в блок памяти для записи эталонной информации.

В режиме Запись на выходе 128 третьего блока 95 формирования признака режима Лог.1, так как на вход 29 поступит Лог.1, а на вход 112 Лог.О. В этом случае на выходе элемента И 145 (фиг. 17) будет Лог.1, запирающая элемент НЕ 146, что вызовет Лог.1 на выходе 128. Это означает, чго при записи сигнал ДЧТ (признак чтения) не формируется.

В режиме записи с выхода 129 устройства в блок памяти должен поступить признак записи ДЗП в соответствии с временной диаграммой (фиг.20). Признак ДЗП формируется элементом 2И-ИЛИ-НЕ (фиг. 18) в четертом блоке 96 формирования признака режима. На вход 112 второй группы И элементов 2И-ИЛИ-НЕ блока 96 поступит Лог.О из второго блока 83 управления режимами и запретит прохождение сигнала с входа 122. На вход 126 первой группы И элемента 2И-ИЛИ-НЕ действует Лог.1 с первого выхода 126 третьего блока 95 формирования признака режима, разрешая прохождение через элемент 2И-ИЛИ-НЕ сигнала с выхода 121 второго формирователя 89 управляющих сигналов, В исходном состоянии на выходе 121 формирователя 89 будет Лог.О. С выхода 114-2 распределителя 85 импульсов через 0,25 мкс после включения D-триггера 84 поступит отрицательный импульс и переключит D- триггер во втором формирователе 89 управляющих сигналов (фиг. 14) в состояние 1, что обусловит сигнал Лог.1 на выходе 121, который поступит на третий вход третьего блока 96 формирования признака режима и, пройдя в нем через элемен 2И-ИЛИ-НЕ, появится на выходе 129 в инверсном виде, что означает начало формирования признака записи - ДЗП отрицательной полярности. Таким образом, в блок памяти пост/пили начала сигналов ДЗП с выхода 129 и ОБМ с

выхода 123. Блок памяти при его исправности реагирует на эти сигналы выдачей ответ- ного сигнала ОТВ отрицательной полярности и посылает его на вход 116 устройства (фиг.2), который направляется на вход второго распределителя 86 импульсов и на четвертый вход коммутатора 88. С первого выхода 115-1 распределителя 86 импульсов задержанный сигнал ОТВ попадает на первый (инвертирующий) и второй входы группы входов Х2 (фиг. 13) коммутатора 88 и проходит через него на выходы У1 и У2. С выхода У2 импульс, задержанный относительно сигнала ОТВ на 0,15 мкс, поступает (фиг.2) на второй вход 118 формирователя 89 управляющих сигналов и переключит D- триггер в нем в положение О положительным фронтом, поступившим с выхода 118 коммутатора 88, обусловив окончание формирования сигнала ДЗП в четвертом блоке 96 формирования признака режима, т.е. задний (положительный) фронт сигнала ДЗ-П на выходе 129 устройства формируется через 0,15 мкс после появления из блока памяти сигнала ОТВ на входе 116 устройства. Сигнал ДЗП с выхода 129 направляется в блок памяти, а через пятый блок 98 формирования признаков режимов - в блок 79 фиксации ошибок. Сигнал ОТВ с входа 116 Поступает на четвертый вход коммутатора и, (фойдя через него, направляется с выхода 105 на второй вход блока 79 фиксации ошибок, где он (фиг.7) попадает на D-вход D- триггера 130, на синхровход С которого Поступит сигнал с выхода четвертого блока 98 формирования признаков режимов. В Этом случае в D-триггере 130 будет записана 1 на нулевом выходе, что соответствует Признаку исправности, который в виде Лог.1 направляется на выход 110-1 и через элемент И 131 на выход 109. С выхода 110-1 признак исправности подается (фиг.2) на первый вход (фиг.8) пятого блока 81 индикации, в результате светодиод 133 не горит, что свидетельствует о своевременном приеме устройством контроля сигнала ОТВ на входе 116 и об исправности в этом смысле блока памяти. С выхода 109 (фиг.2) Лог.1 посылается в генератор 1 тактовых импульсов, не запрещая его работы. В блоке памяти предусмотрены автономные системы контроля, которые, в случае фиксации ошибки, формируют сигнал неисправности (НИС ЗУ), поступающий на вход 104 устройства контроля и далее на инвертирующий вход элемента И-НЕ 132 (фиг.7) и с его выхода на выход 110-2 блока 79 фиксации ошибок и затем на второй вход блока 81 индикации, зажигая соответствующий светодиод 134 ошибки. Кроме того, сигнал ошибки отрицательной полярности проходит через элемент И 131 и подается с выхода 109 на управляющий вход генератора 1 тактовых импульсов, прекращая его работу. После

этого оператор приступает к выяснению причин появления сигнала ошибки НИС ЗУ на входе 104 устройства. Если блок памяти в ответ на сигналы ДЗП и ОБМ, поступившие на его входы с выходов 129 и 123 уст0 ройства контроля, не выдал сигнала ОТВ на вход 116 устройства, то с выхода 105 коммутатора 88 на D-вход D-триггера 130 (фиг.7) поступит Лог.1, которая запишется с приходом синхросигнала по входу 108 в D-триг5 гер. На его нулевом выходе будет Лог.О, который с выхода 110-1 попадает на анод светодиода 133 (фиг.8) в блоке 81 индикации ошибок и включит его, что свидетельствует о наличии ошибки в блоке памяти, привед0 шей к появлению сигнала ОТВ на сответсву- ющем его выходе. Одновременно сигнал ошибки в виде Лог.О пройдет (фиг.7) через элемент И 131 блока.79 фиксации ошибок и с выхода 109 направится на управляющий

5 вход 109 генератора 1 тактовых импульсов, затормаживая его работу. Далее оператор поступает к выяснению причин отсутствия сигнала ОТВ с выхода блока памяти. Для проверки устойчивости характера ошибки

0 оператор с помощью кнопки 135 в блоке 82 сброса ошибки (фиг.9) обнуляет D-триггер 130 (фиг.7) в блоке 79 фиксации ошибок, снимая запрет на выходе 109 с генератора 109 с генератора 1 тактовых импульсов

5 (фиг.1). Если сбой повторяется, то это свидетельствует об устойчивом отказе блока памяти. Для дальнейшего поиска неисправности по отсутствию сигнала ОТВ из блока памяти в устройстве контроля пре0 дусмотрен режим диагностики с имитацией сигнала ОТВ. Для этого оператор переключает коммутирующий элемент в блоке 87 управления третьим коммутатором в положение ОТВ. ОТЛК., обуславливающее на

5 входе 113 коммутатора 88 Лог.О, который переключает коммутатор 88 на трансляцию сигналов (фиг. 13) со входов 1x1-4x1 на выходы У1-У4. В этом случае на выходе 118 коммутатора 88 появится сигнал, поступивший

0 на вход 2x1 (фиг. 13) с распределителя 85 и задержанный на 0,65 мкс (фиг.11) относительно импульса 27 обращения на синхров- ходе С D-триггера 84 (внутренние задержки микросхем не учитываются). При этом окон5 чаниесигнала ,Ј,ЗП на выходе 129 через 0,65 мкс от начала работы устройства (фиг.20). С выхода 114-4 распределителя 85 импульсов сигнал, задержанный на 0,45 мкс (фиг.11), поступит на вход 4x1 (фиг. 13) коммутатора 88 и пройдет на его выход 105, имитируя

наличие сигнала ОТВ. который направится на второй вход блока 79 фиксации ошибок, где этот сигнал будет принят и записан в D-триггер 130. Таким образом, в блок памяти поступят сигналы: в период 0-0,3 мкс от переднего фронта импульса 27 обращения - код адреса из блока 78 передатчиков в магистраль 100, а затем в магистраль 100 с выхода приемопередатчиков поступят данные записи. С выхода 123 - сигнал ОБМ (синхронизация обмена). С выхода 127 сигнал ПЗП - признак байтовой записи и с выхода 129 - ДЗП - признак операции Запись. Блок памяти принимает по магистрали 100 сначала код адреса, затем код данных записи и отвечает о приеме информации сигналов ОТВ, который посылает на вход 116 устройства контроля. После этого с поступлением нового импульса обращения на вход D-триггера 84, нового кода ад- реса на входы 31 блока 78 передатчиков информации и данных записи на входы 32 блока 76 инверсии данных процесс записи информации в блок памяти повторится.

Запись данных словами.

Для записи данных словами (по два байта) коммутирующий элемент в третьем бло- ке 93 управления режимами устнавливают в положение, обеспечивающее на выходе 125 Лог.О, который поступает на третий вход второго блока 94 формирования признака режима. В этом случае Лог.О (фиг. 16) попадает на инвертирующий вход первой группы И элемента 2И-ИЛИ в блоке 94 и разрешает импульсу отрицательной полярности прой- ти на выход 127 устройства контроля, что и является признаком записи данных в блок памяти словами (а не байтами). На временной диаграмме (фиг,20) признак записи словами отмечен на линии 127 с пометкой ПЗП. В остальном принцип работы устройства не отличается от работы в режиме записи данных байтами, описанный в предыдущем разделе.

Чтение данных из блока памяти.

Признаком операции чтения является Лог.О, поступающий с выхода 29 блока 12 формирования признака операции на первые входы второго 94 и третьего 95 блоков формирования признака режима.

В режиме чтения устройство контроля формирует и посылает в блок памяти (фиг.2) признак чтения ДЧТ на выходе 128, признак ПЗП на выходе 127, сигнал ОБМ на выходе 123, код адреса в магистраль 100 в.соответ- ствии с временной диаграммой на фиг.20. Из блока памяти в устройство контроля поступят ответные сигналы: сигнал ОТВ на вход 116, сигнал неисправности НИС ЗУ на вход 104, код данных чтения с магистрали

100. Коммутирующий элемент в блоке 87 устнавливают в положение Ответ. Из выходе 113 будет Лог.1. Работа начинается с поступлением сигнала Сброс с выхода 49 первого блока 8 сброса (фиг.1), При этом устанавливаются в исходное состояние узлы и локи, как и в режиме записи. На первый вход 29 блока 97 управления приемопередатчиками (фиг.2) проходит Лог.О, который запирает вторую группу И элемента 2И- ИЛИ-НЕ в блоке 97 (фиг. 19), а первая группа И закрыта потенциалом Лог.О со входа 112. В этом случае на выходе 101 блока 97 будет Лог.1, которая направляется на третий вход блока 75 приемопередатчиков (фиг.2) и переключает его в режим трансляции данных чтения из магистрали 100 на выходе 102. Затем с выхода 27 первого формирователя 2 управляющих сигналов (фиг. 1) на синхровход С D-триггера 84 (фиг.2) поступит импульс обращения и переключит его в состояние 1. Отрицательный фронт с триггера 84 попадет на вход 120 первого распределителя 85 импульсов и распространяется по линии задержки (фиг.11) в распределителе 85. Через 0,3 мкс с выхода 114-3 распределителя 85 (фиг.2) отрицательный фронт попадет на второй R-вход триггера 84 и переключит его в состояние О. На нулевом плече триггера 84 формируется отрицательный импульс, который распространяется по линии задержки распредел ителя 85. С выхода 120 триггера 84 ригнал отрицательной полярности поступает на управляющие входы 120 блока 75 приемопередатчиков и блока 78 передатчиков информации. В это время блок 78 открывается и код адреса транслируется с его входа 31 на выход, и далее в магистраль 100 и затем в блок памяти. В это время блок 75 приемопередатчиков закрыт и на его выходе 100 будет высокое сопротивление. После окончания отрицательного импульса на входах 120 блоков 75 и 78 блок 78 передатчиков закроется, а блок 75 приемопередатчиков откроется для трансляции данных чтения с магистарли 100 на выходы 102.

С задержкой 0,15 мкс отрицательный импульс с выхода 114-1 поступит на третий вход формирователя 91 управляющих сигналов и переключит D-триггер в нем в положение О. С поступлением сигнала с выхода 105 коммутатора 88 триггер в формирователе 91 переключится в 1 и на выходе фор- мирозателя 91 сформируется сигнал ОБМ в соответствии с временной диаграммой на фиг.20, который направится с выхода 123 в блок памяти.

На первом входе 29 блока 95 формирования признака режима действует Лог.О,

который проходит через элемент И 145 (фиг. 17), открывает элемент НЕ 146 с выхода 126 блока 95, направляется на четвертый вход блока 96, запрещая формирование в нем (фиг. 18) сигнала записи ДЗП на выходе 129 устройства.

С задержкой 0,25 мкс отрицательный импульс с второго выхода распределителя 85 импульса (фиг.11) подается на первый вход формирователя 89 управляющих сигналов, переключаетО-триггерв нем (фиг,14) в Г, С выхода 121 положительный перепад поступает на третий вход второго блока 95 формирования признака режима и, пройдя через элемент НЕ 146, появляется отрицательным фронтом на выходе блока 95 и далее с (фиг.2) выхода 128 устройства направляется в блок в виде признака чтения ДЧТ. Кроме того, в блок памяти поступит сигнал синхронизации обмена ОБМ с выхода 123 устройства. Сигнал ОБМ в режиме чтения формируется точно так же, как и .в режиме записи, поэтому при описании режима чтения подробно процесс формирования сигнала ОБМ в формирователе 91 не приводится

Блок памяти при его исправности реагирует на сигналы ОБМ 123 и ДЧТ 128 выдачей ответного сигнала ОТВ на вход 116 устройства контроля. Сигнал ОТВ отрицательной полярности с входа 116 направляется на вход распределителя 86 импульсов (фиг.2) и на четвертый вход коммутатора 88. С первого выхода 115-1 распределителя 86 импульсов задержанный сигнал ОТВ попадает на первый (инвертирующий) и второй входы группы входов Х2 (фиг, 13) коммутатора 88 и приходит через него на выходы У1. У2. С выхода У2 импульс, задержанный отрицательно сигнала ОТВ на 0,15 мкс (фиг.2) поступает на второй вход 118 формирователя 89 управляющих сигналов и переключит D- триггер в нем (фиг. 14) в положение О положительным фронтом, поступившим с выхода 118 коммутатора 88.и обусловит окончание формирования сигнала ДЧТ в третьем блоке 95 формирования признака режима. Таким образом, задний (положительный) фронт сигнала ДЧТ на выходе 128 устройства контроля сформируется через 0,15 мкс после появления из блока памяти сигнала ОТВ на входе 116 устройства. Сигнал ДЧТ с выхода 128 направляется в блок памяти, а через четвертый блок 98 формирования признаков режимов - в блок 79 фиксации ошибок.

В режиме чтения, как и в режиме записи в блоке 79 контролируется исправность блока памяти по двум признакам - по появлению сигнала неисправности НИС ЗУ на

входе 104 устройства и по наличию сигнала ОТВ на входе 116 устройства. Наличие сиг нала НИС ЗУ отрицательной полярности на входе 104 или отсутствие сигнала ОТВ на

входе 116 после выдачи сигналов ОБМ на выхое 123 и ДЧТ на выходе 128 устройства свидетельствует о неисправности блока памяти, что и фиксируется в блоке 79 фиксации ошибок и с выхода 109 блока 79 сигнал ос0 таяова направляется на управляющий вход генератора 1 тактовых импульсов (фиг.1) и останавливает его работу. Подробно процесс формирования сигнала останова 109 приведен при описании режима записи. Для

5 работы блока памяти в режиме чтения, помимо сигналов ДЧТ и ОБМ, на выходах 128 и 123 должен формироваться и сигнал ПЗП на выходе 127 устройства. Форма сигнала ПЗП на выходе 127 первого блока 94 форми0 рования признака режима зависит от положения коммутирующего элемента в блоке 93 управления режимами. Если коммутирующий элемент установлен в положение -ПЗП, то на его выходе 125 будет Лог.Г, которая

5 подается на третий вход блока 94 формирования признака режима и далее (фиг. 16) поступает на инвертирующий вход первой группы И элемента 2И-ИЛИ и закрывает эту группу И. На один из входов второй группы

0 И поступает признак чтения Лог.О с выхода 29 (фиг.1) блока 12 формирования признака операции, который разрешает (фиг. 16) прохождение импульса отрицательной полярности с выхода D-триггера 84

5 (фиг.1) через элемент 2И-ИЛИ блока 94 в инверсном коде на выход 127 устройства в соответствии с временной диаграммой (строка 127) на фиг.20. Если же коммутирующий элемент в блоке 93 установлен в по0 ложение Слово, то не его выходе 125 будет Лог.О. В результате этого первая группа I/I элемента 2И-ЙЛИ в блоке 94 будет открыта и импульс отрицательной полярности будет действовать на обоих входах каждой группы

5 И, причем один вход прямой, а другой инвертирующий. В этом случае реализуется функция а V а, что соответствует Лог.1 на выходе блока 94 и, соответственно, на выходе 127 устройства. Это не противоречит тре0 бованиям, предъявляемым к сигналу ПЗП в интерфейсе МПИ.

Блок памяти, получив из устройства контроля в первой фазе код адреса из магистрали 100 и с выходов 123, 127, 128 соот5 ветственно сигналы ОБМ, ПЗП и ДЧТ, выдает в магистраль 100 во второй фазе данные информации чтения, которые поступают на вторую группу входов-выходов блока 75 приемопередатчиков и транслируются через него на выходе 102 и далее через

четвертый блок 77 инверсии данных направляется на группу входов 34 блока 22 сравнения данных (фиг.1). где производится анализ считанной из блока памяти информации путем сравнения ее с эталонным кодом. По результатам анализа принимается решение о продолжении работы в случае равенства этих кодов или об останове в случае неравенства. Следует отметить, что в соответствии с требованием МПИ все сигналы, поступающие в блок памяти и обратно, формируются в обратном коде, т.е. наличие сигнала передается низким уровнем (нулевым потенциалом). Поэтому блок 75 приемо- передатчиков и блок 78 передатчиков выполнен с инверсией. В случае неполучения на входе 116 сигнала ОТВ от блока памяти (фиг.2) блок 79 фиксации ошибок останавливает работу устройства контроля. Для обеспечения дальнейшей диагностики неисправности блока памяти коммутирующий элемент в блоке 87 управления коммутатором 88 необходимо установить в положение ОТВ. ОТКЛ., при котором на его выходе 113 будет Лог.О, переключающий коммутатор 88 на трансляцию сигналов (фиг.13) с входов 1x1-4x1 на выходы У1-У4. В этом случае сигнал ОТВ имитируется сигналами с выходов распределителя 85 импульсов. Дальнейшая работа устройства при внутренней имитации сигнала ОТВ подробно приведена при описании режима записи.

Чтение с модификацией.

В этом режиме в первой фазе считываются данные из блока памяти, анализируется информация, во второй фазе производится запись в этот же адрес новой (инверсной) информации и затем операция повторяется в новом адресе. Работа в этом режиме начинается с однократной записи с остановом, режим работы которого приведен в соответствующем разделе описания. Затем устройство переводят в режим циклического считывания.

Установка в исходное состояние в этом режиме не отличается от предыдущих режимов. Коммутирующие элементы 139 и 140 во втором блоке 83 управления режимами сначала необходимо установить в положение УСТ.МОД. В этом случае на выходе 111 блока 83 будет Лог.О (фиг. 10), а на выходе 112 - Лог.1. С выхода 111 блока 83 Лог.О подается на третий вход (фиг.2) блока 92 управления инверсиями, проходит (фиг.15) на установочный S-вход счетного триггера 143 и через элемент И 141 на R-вход R-S- триггера 142, устанавливая триггер 143 в состояние 1, а триггера 142 - в О. С выхода триггера 142 Лог.1 поступает на один из входов элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ Н4 и на выход 124 и далее на трети оход блока 47 управления приемопередатчиками. Затем коммутирующее устройство в блоке 83 управления режимами переключа- 5 ют в положение МОД. С выхода 112 блока 83 управления режимами Ло1.1 подается на четвертый вход блока 92 управления инверсиями, на второй вход второго блока 95 формирования признака режима, на первый 0 вход третьего блока 96 формирования признака режима и на второй вход блока 97 управления приемопередатчиками, подготавливая эти блоки к работе в режиме Чтение с модификацией. С выхода 111 блока

5 83 в блок 92 управления инверсиями поступит Лог.1, снимающая установочный потенциал Лог.О с R-входа триггера 141 (фиг.15)и S-входа триггера 142. Формирователь 91 управляющих сигналов, второй блок

0 94 формирования и третий блок 95 формирования признака режима вырабатывают на своих выходах 123, 128, 127. соответственно, сигнал синхронизации обмена ОБМ, признак ПЗП Запись-байт и признак чте5 ния ДЧТ в первой фазе работы устройства точно так же, как и в режиме обычного чтения, рассмотренного в предыдущем разде ле. С выхода 124 блока 92 управления инверсиями Лог.О поступает на третий

0 вход блока 97 управления приемопередатчиками, формируя на выходе 101 Лог.1, которая направляется на третий (управляющий) вход блока 75 приемопередатчиков и устанавливает в нем режим трансляции дан5 ных с магистрали 100 на выходы 102. В начальный момент работы из первого блока 8 сброса (фиг,1)с выхода 49 на второй вход 49 блока 92 управления инверсиями (фиг.2) поступит сигнал Сброс, который переключит

0 счетный триггер 143 в локе 92 (фиг.15) в положение О, что обусловит на выходе 103 блока 92 Лог.О. С приходом импульса обращения на вход 27 D-триггера 84 на его выходе 120 сформируется импульс отрица5 тельной полярности 0,3 мкс, который посту- пит на управляющие входы блока приемопередатчиков 75 и передатчиков 78, закрывая блок 75 и разрешая трансляцию кода адреса с входа 31 на выходы блока 78

0 передатчиков и далее в магистраль 100 и затем в блок памяти. Блок памяти реагирует на эти сигналы выдачей сигналя ОТВ на вход 116 устройства контроля, наличие которого проверяется в блоке 79 фиксации ошибок.

5 После приема блоком памяти кода адреса с магистрали 100 и сигналов ОБМ с выхода 123 и ДЧТ с выхода 128 устройства и выдачи сигнала ОТВ на входы 116 устройства блок памяти выдаете магистраль 100 данные чтения в обратном коде. К этому времени из

ыходе 120 D-триггера 84 отрицательный игнал закончится и вследствие этого блок 8 передатчиков закроется в третье состояние, а блок 75 приемопередатчиков откроетя. Данные чтения пройдут с магистрали 100 ерез блок 75 приемопередатчиков на его выходе 102 в прямом коде и далее через четвертый блок 77 инверсии данных в прямом коде на входы 34 (фиг.1) блока 22 сравнения данных, где информация анализируется путем сравнения с эталон- нымчкодом. Если ошибки не обнаружены и останова не произошло, то после первой азы работы устройства в режиме Чтения с модификацией наступает вторая фаза, в которой необходимо произвести запись в блок памяти обратного кода в тот же адрес, из которого была считана информация. В этом случае повторного сигнала (фиг.2) с выхода 123 в блок памяти не выдается. Устройство контроля должно сформировать рризнак записи ДЗП на выходе 129, получить ответный сигнал ОТВ на входе 116 и Сформировать сигнал ПЗП на выходе 127 в зависимости от режима записи (байтами или словами). По окончании первой фазы работы (чтения прямого кода), с выхода 114- 5 группы выходов распределителя 85 импульсов сигнал, задержанный на 0,5 мкс относительно импульса обращения на входе 27 D-триггера 84, поступит на пятый вход блока 92 управления инверсиями и переключит триггер 142 (фиг.15) в нем в 1. В результате на выходе 103 и 124 блока 92 потенциалы Лог.1. С выхода 103 блока 92 управления инверсиями Лог.1 поступит на управляющий вход блока 76 инверсии данных, что обусловит прохождение данных записи с входа 32 на выходы 99 в обратном к|оде. С выхода 124 блока 92 управления ин- в|ерсиями Лог.Г направится на третий блока 97 управления приемопередатчиками и, пройдя через элемент 2И-ИЛЙ в Нем (фиг. 19) потенциалом Лог.О, поступит На третий (управляющий) вход блока 75 приемопередатчиков и переключит его в режим трансляции сигналов с входов 99 в магистраль 100. С выхода 117 коммутатора 88 им- пульс, задержанный в распределителе 86 на 0,15 мкс относительно сигнала ОТВ, поступившего на вход 116 устройства, направится на второй установочный вход формирователя 90 управляющих сигналов и переключит D-триггер в нем (фиг.14) в О. На выходе 122 формирователя 90 появится положительный фронт, который пройдет через четвертый блох 96 формирования признака режима на выход 129 и направится в блок памяти признаком записи ДЗП Блок памяти выдает ответный сигнал ОТВ на вход

116 устройства контроля. Сигнал ОТВ пройдет через распределитель 86 импульсов, затем через коммутатор 88 и с его выхода 117 на второй установочный вход формирователя 90 управляющих сигналов, устанавливая D-триггер в нем в состояние О. На выходе 122 формирователя 90 сформируется таким образом отрицательный фронт положительного сигнала, который пройдет через блок

96 и завершит формирование признака записи ДЗП на выходе 129 устройства и, соответственно, закончится выдача блоком памяти ответного сигнала ОТВ на вход 116 устройства контроля. Ответный сигнал ОТВ,

5 как и в ранее рассмотренных режимах контролируется блоком 79 фиксации ошибок. Одновременно с формированием на выходе 129 признака записи ДЗП данные с входов 99 блока 75 приемопередатчиков проходят

0 в магистраль 100 и далее в блок памяти, где они записываются в тот же адрес, из которого в первой фазе работы считана информация, но в инверсном коде. Затем на синхровход С D-триггерй 84 и первый вход

5 27 блока 92 управления инверсиями поступает следующий импульс обращения, который начнет формирование новой последовательности сигналов на D-триггере 84 и распределителе 85 импульсов, а также

0 установит в О триггер 142 (фиг.15) в блоке 92 управления инверсиями и процесс чтения данных в первой фазе и записи данных в инверсном коде повторится, но в следующем адресе блока памяти. Так будет продол5 жаться до тех пор, пока не закончится полный перебор всех адресов блока памяти с чтением данных и их анализом в первой фазе и записи данных инверсного кода во второй фазе в каждом из адресов. После

0 этого из первого блока 8 сброса (фиг.1) поступит на второй вход 49 блока 92 управления инверсиями сигнал Сброс, который пройдет на счетный вход С счетного триггера 143 (фиг.15) и переключит его в положе5 ние 1. Затем весь процесс работы повторится, но на выходе 103 блока 92 управления инверсиями сигнал будет инверсным по отношению к ранее рассмотренному циклу работы устройства (где цикл - время

0 полного перебора всех адресов памяти) с той лишь разницей, что в первой фазе каждого такта (где такт-время контроля одного адреса блока памяти) производится чтение данных в инверсном коде по отношению к

5 чтению в предыдущем цикле. Код данных в инверсном коде с выхода 102 блока 75 приемопередатчиков поступит на входы четвертого блока 77 инверсии данных. В это время на управляющем входе 103 блока 77 будет Лог.1, которая поступит на управляющие

входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ в блоке 77 (фиг.5), что обусловит работу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ как инверторов. Следовательно, на выходы 34 блока 77 данные пойдут в прямом коде. Далее они направятся в блок 22 сравнения данных (фиг.1) для анализа на правильность информации. Во второй фазе каждого такта второго цикла работы устройства на вход 114-5 блока 92 управления инверсиями (фиг,2) поступит сигнал, задержанный на 0,5 мкс относительно импульса обращения, поступившего на синхровход С D-триггера 84, который переключит триггер 141 в блоке 92 (фиг. 15) в положение 1. Это обусловит Лог.О на выходе 103 блока 92. Этот сигнал направится на управляющий вход блока 76 инверсии данных, в результате чего блок 76 пропускает данные с входов 32 на выходы 99 в прямом коде. Следовательно, во втором цикле работы в первой фазе каждого такта будет чтение данных из блока памяти в инверсном коде с последующим преобразованием в блоке 77 в прямой код, а во второй фазе - запись данных в блок памяти в прямом коде (без учета инверсии в блоке 75 приемопередатчиков). В третьем цикле работа повторится как в первом и т.д. В режиме Чтение с модификацией в случае фиксации блоком 79 отсутствия сигнала ОТВ на входе 116 устройства оператор переводит устройство в режим имитации сигнала ОТВ от внутренних сигналов и далее производит диагностику неисправностей блока памяти.

Предлагаемое устройство реализует новый тест Чтение с модификацией, ранее не использовавшийся в контрольной аппаратуре. Этот режим обеспечивает чтение данных из определенного адреса с последующей записью в этот адрес иной (инверсной) информации и проверкой этой информации в следующем цикле контроля, что выявляет неустойчивость работы блоков памяти, имеющих место при работе в составе с ЭВМ. Обеспечение контроля блоков памяти с интерфейсом МПИ позволяет получить новое качество, технико-экономический эффект которого выражается в снижении затрат на наладку как самих блоков памяти, так и вычислительных систем в целом, куда входят проверяемые запоминающие устройства. При этом расширяется область использования устройства, повышается достоверность проверки блоков памяти.

Формула изобретения Устройство для контроля блоков оперативной памяти по авт.св. № 1265859, отличающееся тем, что, с целью расширения

области применения устройства путем обос печения возможности контроля блоков памяти с магистральным параллельным интерфейсом, в него введены блок приемопередзтчиков информации, третий и четвер- тый блоки инверсии данных, блок передатчиков информации, блок фиксации ошибок, блок выключения ошибок, пятый блок индикации, второй блок сброса, второй

0 и третий блоки управление режимами, D- триггер, первый и второй распределители импульсов, третий коммутатор, блок управления третьим коммутатором, второй, третий - и четвертый формирователи

5 управляющих сигналов, блок управления инверсиями, второй, третий, четвертый и пятый блоки формирования признака режима, блок управления приемопередатчиками информации, первый вход которого соединен

0 с первыми входами второго, третьего и четвертого блоков формирования признака режима, с одним из выходов блока формирования признака операции, с управляющим входом второго блока инверсии

5 данных и с седьмым входом блока сравнения данных, выход блока управления приемопередатчиками информации соединен с первым входом блока приемопередатчиков информации, входы первой группы которо0 го подключены к выходам третьего блока инверсии данных, входы группы которого подключены к информационным выходам устройства, входы второй группы блока приемопередатчиков информации соединены с

5 выходами блока передатчиков информации и являются информационными входами-выходами устройства, выходы группы блока приемопередатчиков информации подключены к входам группы четвертого блока ин0 веосии данных, вход которого подключен к входу третьего блока инверсии данных и к первому выходу блока управления инверсиями,выходы группы четвертого блока инверсии данныхподключены к

5 информационным входам устройства, второй вход блока приемопередатчиков инфор- мации соединен с входом блока передатчиков информации, с входом первого распределителя импульсов, с вторым вхо0 дом второго блока формирования признака режима и с нулевым выходом D-триггера, синхровход которого соединен с первым входом блока управления инверсиями, с первым выходом первого формирователя

5 управлюящих сигналов и с входом формирователя сигнала опроса, второй вход блока управления инверсиями соединен с первыми входами второго, третьего и четвертого формирователей управляющих сигналов, с первым установочным входом D-триггера, с

третьим входом генератора, с третьим выходом первого блока сброса, с вторым входом первого формирователя управляющих сигналов, с входом сброса счетчика адреса и с четвертым входом блока сравнения данных, третий вход блока управления инверсиями соединен с первым выходом второго блока управления режимами, второй выход которого подключен к вторым входам третьего и четвертого блоков формирования признака режима, к второму входу блока управления приемопередатчиками информации и к четвертому входу блока управления инверсиями, второй выход которого соединен с третьим входом блока управления приемопередатчиками, а пятый вход подключен к четвертому выходу из группы выходов первого распределителя импульсов, третий выход из группы выходов которого подключен к второму установочному входу D-триггера, второй выход из группы выходов первого распределителя импульсов соединен с вторым входом второго формирователя управляющих сигналов, а первый выход из группы выходов первого распределителя импульсов соединен с вторым входом четвертого формирователя управляющих сигналов, третий вход которого соединен с первым выходом третьего коммутатора и с вторым входом блока фиксации ошибок, первый вход которого является входом сигнала неисправности устройства, третий вход блока фиксации ошибок соединен с выходом блока выключения ошибок, четвертый вход соединен с выходом второго блока сброса, пятый вход подключен к выходу пятого бло-- ка формирования признака режима, выход блока фиксации ошибок соединен с входом останова генератора, а выходы группы блока фиксации ошибок подключены к пятому

блоку индикации, выходы групп первого и второго распределителей импульсов подключены соответственно к входам первой и второй групп третьего коммутатора, первый вход которого подключен к выходу блока управления третьим коммутатором, а второй вход соединен с входом второго распре- делителя импульсов и является входом Ответ устройства, второй и третий выходы

третьего коммутатора соединены соответственно с вторым входом третьего и третьим входом второго формирователей управляющих сигналов, четвертый выход третьего коммутатора соединен с третьим входом

третьего формирователя управляющих сигналов, выход которого соединен с четвертым входом четвертого блока формирования признака режима, третий вход которого соединен с выходом второго

формирователя управляющих сигналов и с третьим входом третьего блока формирования признака режима, первый выход которого соединен с пятым входом четвертого блока формирования признака режима, а

второй выход подключен к первому входу пятого блока формирования признака режима и является выходом признака чтения устройства,выход четвертого блока формирования признака режима соединен

с вторым входом пятого блока формирования признака режима и является выходом

признака записи устройства, выход третьего блока управления режимами соединен с третьим входом второго блока формирования признака режима, выход которого является выходом признака байтовой, записи устройства, выход четвертого формирователя управляющих сигналов является выходом Обмен устройства, D-вход D-триггера

подключен к шине Лог.1 устройства.

$9

v 601AM

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Устройство для формирования тестов памяти | 1989 |

|

SU1711235A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Система поездной радиосвязи | 1989 |

|

SU1693730A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| Устройство для сравнения кодов | 1990 |

|

SU1758643A1 |

| Устройство для сжатия информации | 1988 |

|

SU1536418A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

Изобретение относится к запоминающим устройствам статического типа, конкретно - к контролю запоминающих устройств на правильность их работы и может быть использовано при разработке, отладке и диагностике неисправностей оперативных запоминающих устройств. Цель изобретения - расширение области применения устройства за счет возможности контроля блоков памяти с магистральным параллельным интерфейсом. Устройство содержит генератор, формирователи управляющих сигналов, счетчик ад; реса, блок установки адреса, коммутаторы, блоки индикации, блоки сброса, счетчик циклов, блок выбора адреса синхронизации, блок сравнения адресов и циклов, блок Изобретение относится к запоминающим устройствам статического типа, конкретно к контролю запоминающих устройств на правильность их работы, может быть использовано при разработке, отладке и диагностике неисправностей оперативных запоминающих устройств и является усовершенствованием изобретения по авт.св. № 1265859. формирования признака операции, блоки управления режимами, формирователи признака режима, блок задания начального кода, блоки инверсии данных, формирователь признака инверсии данных, блок сравнения данных, формирователь сигнала опроса, блок пуска, блок приемопередатчиков, блок передатчиков, блок фиксации ошибок, блок выключения ошибок, D-триггер, распределители импульсов, блокуправления третьим коммутатором, блок управления инверсиями, блокуправления приемопередатчиками. Введенные признаки - блок приемопередатчиков, третий и четвертый блоки инверсии данных, блок передатчиков, блок фиксации ошибок, бдок выключения ошибок, D-триггер, распределители импульсов, блок управления третьим коммутатором, третий коммутатор, пятый блок индикации, второй блок сброса ошибок, второй и третий блоки управления режимами, второй, третий и четвертый формирователи управляющих сигналов, блок управления инверсиями, второй, третий и четвертый формирователи признака режима, блок управления приемопередатчиками обеспечивают возможность проверки блоков памяти со стандартным интерфейсом МПИ без привлечения дефицитных персональных компьютеров. 20 ил. Цель изобретения - расширение области применения устройства путем обеспечения возможности контроля блоков памяти с магистральным параллельным интерфейсом. На фиг. 1 и 2 приведена схема устройства для контроля блоков оперативной памяти; на фиг. 2 - схема блока приемопередатчиков информации; на фиг. 4 сл с о со Ч о ю 4 ГО

Щш.г

Фиг 11

Фиг. 11

/fe./J

№K/J

(Риг. 19

012J45678901Z345678

Фиг. 20

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-07—Публикация

1989-10-12—Подача