fO

15

- 20

1129021

Изобретение относится к контрольо-измерительной технике и может быть спользовано для контроля логических стройств ЭВМ.

Цель изобретения - расширение фун- 5 циональных возможностей устройства утем контроля правильности передачи байта информации и выявления неверно переданного бита информации.

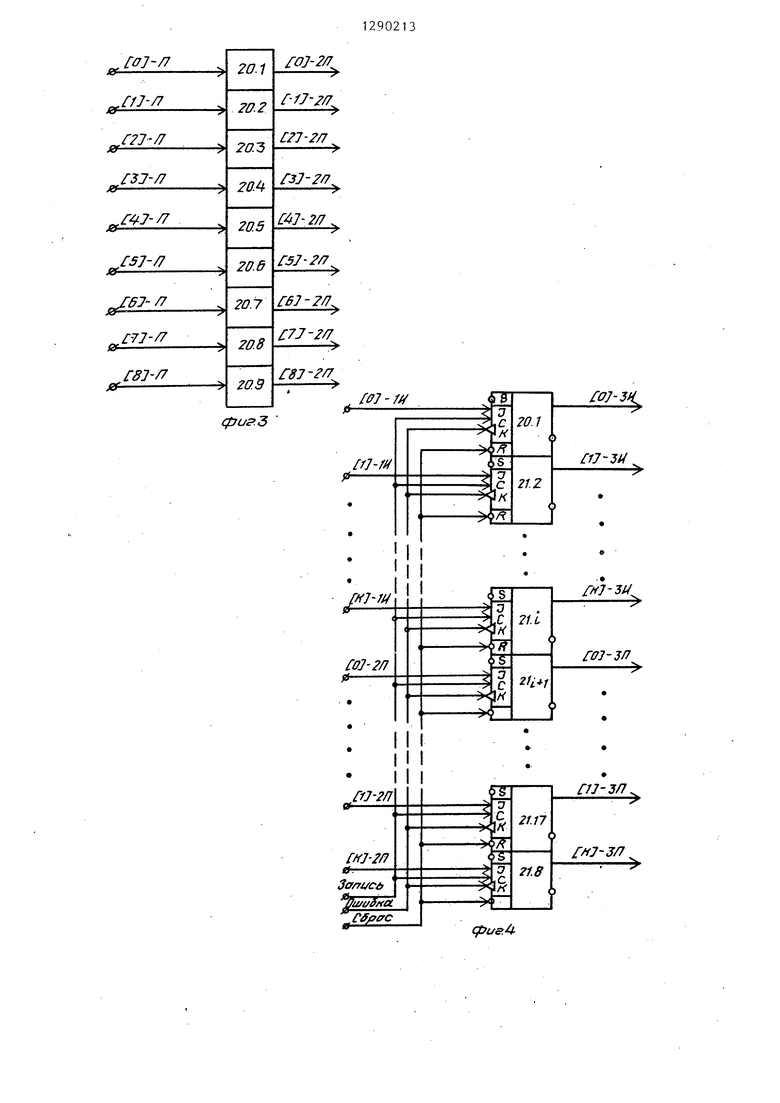

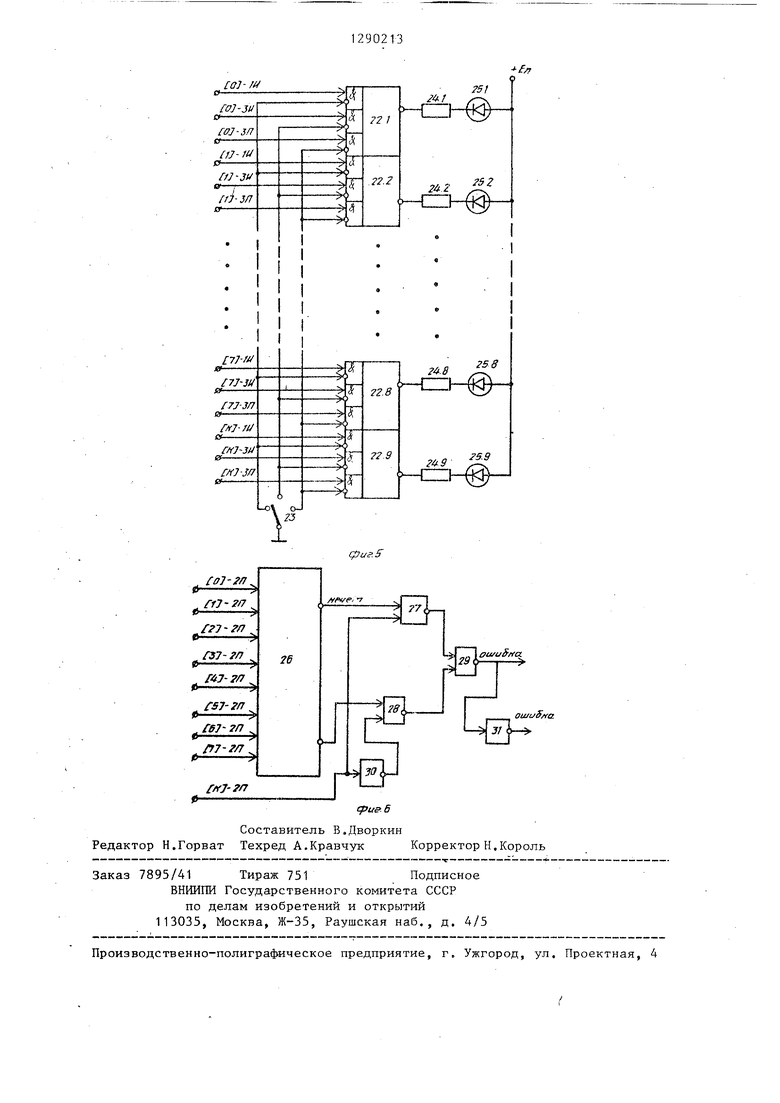

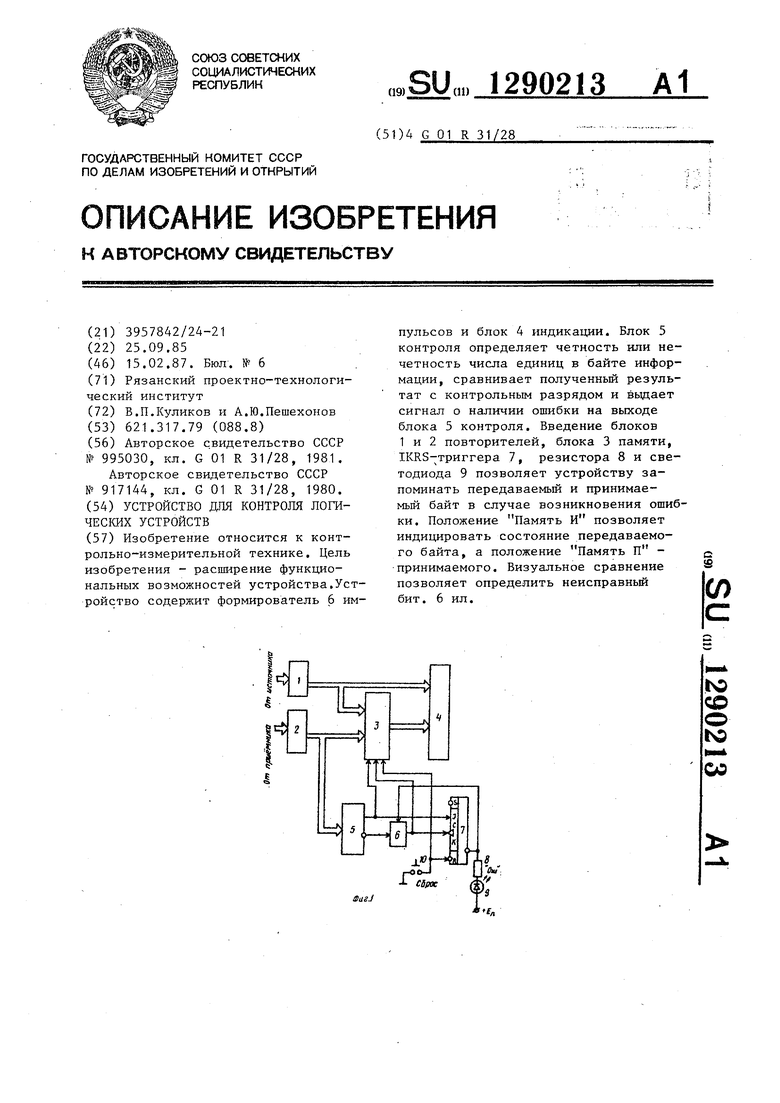

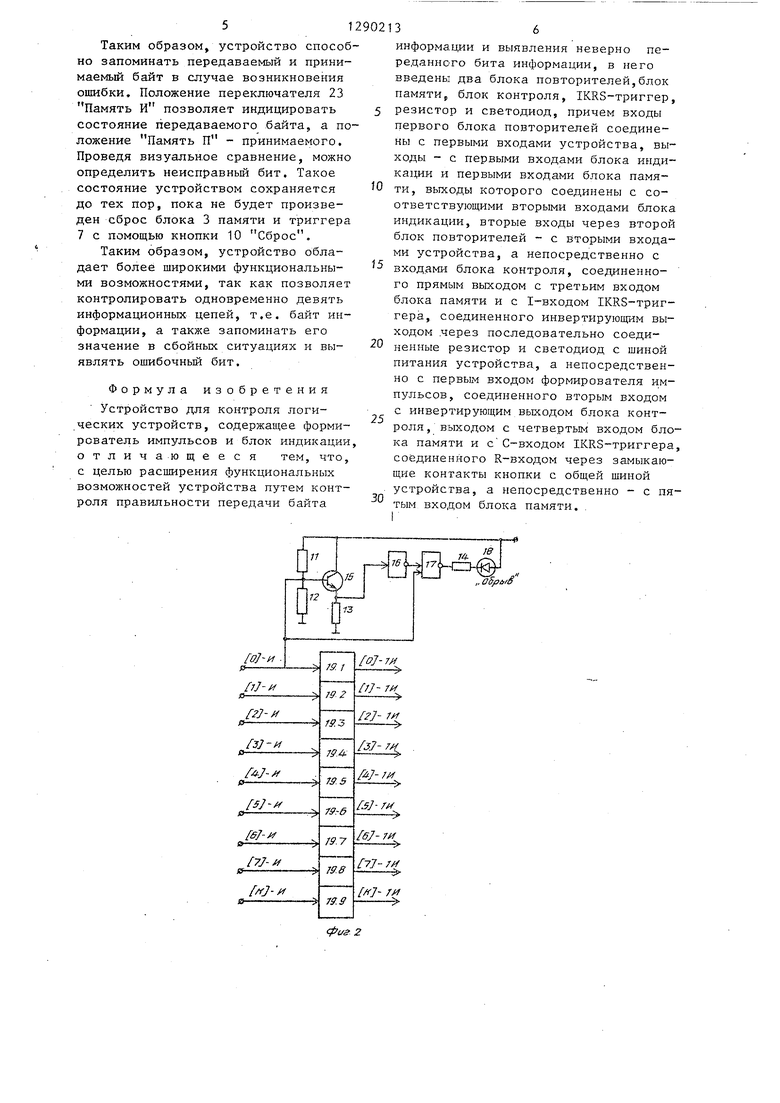

На фиг, 1 приведена схема устройства; на фиг. 2 - схема первого блока повторителей; на фиг. 3 - схема второго блока повторителейJ на фиг. 4 - схема блока памяти; на фиг.5 - схема блока индикации, на фиг. 6 - схема блока контроля.

Устройство (фиг. 1) содержит первый 1 и второй 2 блоки повторителей, блок 3 памяти, блок 4 индикации,блок 5 контроля, формирователь 6 импуль сов, например, управляемый одновиб- ратор, IKRS-триггер 7, резистор 8,

светодиод 9 и кнопку 10. (

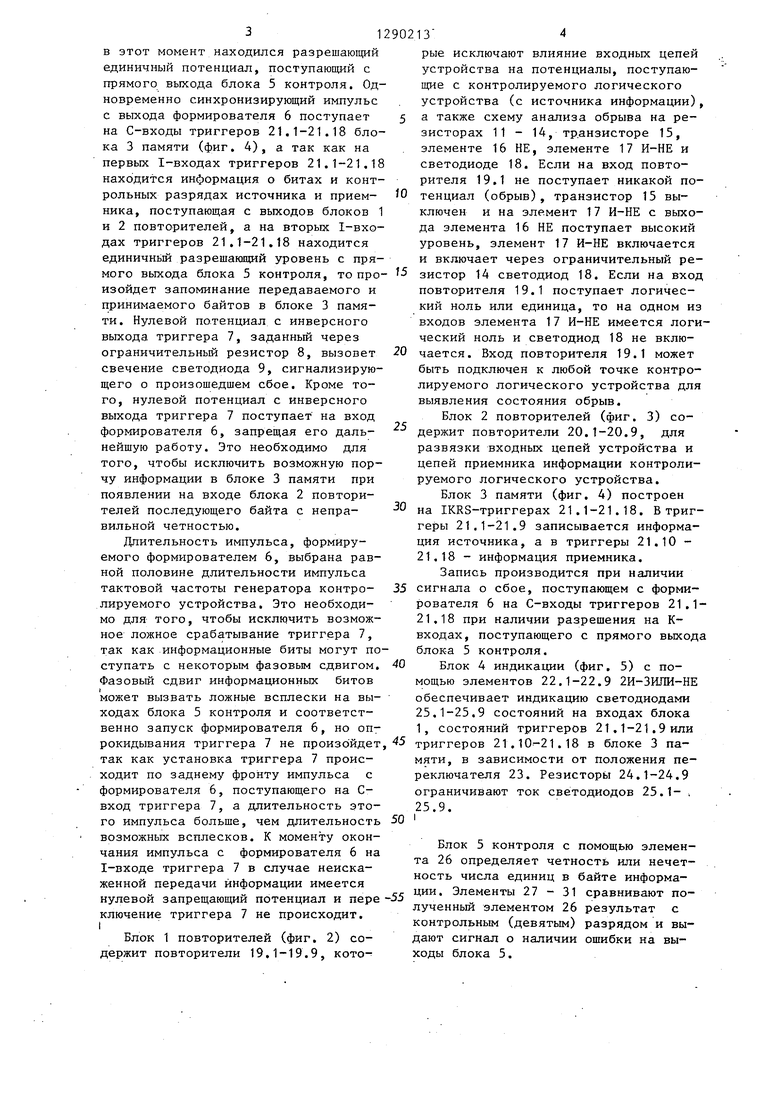

Блок 1 повторителей (фиг. 2) со- 25

держит резисторы 11 - 14, транзистор 15, элемент 16 НЕ, элемент 17 И-НЕ, светодиод 18, повторители 19.1-19.9.

Блок 2 повторителей (фиг. 3) содержит повторители 20.1-20.9. 30

Блок памяти (фиг. 4) содержит IKRS-триггеры 21.1-21.18.

Блок 4 индикации (фиг. 5) содержит элементы 2И-ЗИЛИ-НЕ 22.1-22.9, переключатель 23, резисторы 24.1 - 24.9, светодиоды 25.1-25.9.

Блок 5 контроля (фиг. 6) содержит элемент 26 свер;гки по модулю два,элементы 27-29 2И-НЕ, элементы 30, 31 НЕ.

Входы первого блока 1 повторите- 40 лей соединены с первыми входами устройства, выходы - с первыми входами блока 4 индикации и первыми входами блока 3 памяти, выходы которого соединены с соответствующими вторыми 45 входами блока 4 индикации, вторые входы через второй блок 2 повторителей - со вторыми входами устройства, а непосредственно со входами блока 5 контроля, соединенного прямым выходом jo с третьим входом блока 3 памяти и с 1-входом IKRS-триггера 7, соединенного инвертирующим выходом через после- довательно соединенные резистор 8 и светодиод 9 - с шиной питания устрой- 55 ства, непосредственно - с первым входом формирователя 6 импульсов, соединенного вторым входом с инвертирующим выходом блока 5 контроля, выходом с

O

15

0

21

5

5

30

40 45 jo 55

32

четвертым входом блока 3 памяти и с С-входом IKRS- триггера 7 , соединенного R-входом через замыкающие контакты кнопки 10 с общей шиной устройства , а непосредственно - с пятым входом блока 3 памяти.

Устройство работает следующим образом.

Если устройство находится в режиме Пробник, что задается переключателем: 23 в блоке 4 индикации, то информация о состоянии контролируемого байта, поступающего на вход блока 1 повторителей,с выхода последнего поступает на вход блока 4 индикации. Включенное состояние светодиода 25,i в блоке 4 индикации соответствует единичному состоянию соответствующего i-го бита информации в байте, поступившем на входы блока 1, выключенное - нулевому.

В режиме Пробник устройство позволяет наблюдать за изменением логических уровней одновременно в девяти логических цепях, что создает большие удобства при поиске неисправности ЭВМ в потактовом режиме работы.

В режиме контроля передачи информации для выявления исчезновения или

возбулсдения лишнего бита в передава1

емом байте информации от какого-либо источника (передатчика) в приемник неисправность носит сбойный характер (т.е. имеет малую частоту повторения) выходы источника подсоединяют к входам блока 1 повторителей, а выходы приемника - к входам блока 2 повторителей. Выходы блоков 1 и 2 подключены к входам блока 3 памяти. Переключатель 23 в блоке 4 находится в положении, Память И или Память П. Информация о принимаемом приемником байте поступает с выходов блока 2 повторителей на вход блока 5 контроля. Блок 5 контроля в случае поступления байта с неисправной четностью (если количество единичных разрядов в ба:йте и контрольном разряде четное) возбуждает на своих выходах сигнал, причем на прямом выходе этот сигнал имеет единичный уровень, на инверсном - нулевой. Перепадом из единихда в нуль с инверсного выхода блока 5 контроля запускается формирователь 6, формирующий импульс, по заднему фронту которого триггер 7 устанавливается в единичное положение, так как на 1-входе триггера 7

в этот момент находился разрешающий единичный потенциал, поступающий с прямого выхода блока 5 контроля. Одновременно синхронизирующий импульс с выхода формирователя 6 поступает на С-входы триггеров 21.1-21.18 блока 3 памяти (фиг. 4), а так как на первых 1-входах триггеров 21.1-21.18 находится информация о битах и контрольных разрядах источника и приемника, поступающая с выходов блоков 1 и 2 повторителей, а на вторых 1-входах триггеров 21.1-21.18 находится единичньш разрешающий уровень с прямого выхода блока 5 контроля, то произойдет запоминание передаваемого и принимаемого байтов в блоке 3 памяти. Нулевой потенциал с инверсного выхода триггера 7, заданный через ограничительный резистор 8, вызовет свечение светодиода 9, сигнализирующего о произошедшем сбое. Кроме того, нулевой потенциал с инверсного выхода триггера 7 поступает на вход формирователя 6, запрещая его дальнейшую работу. Это необходимо для того, чтобы исключить возможную порчу информации в блоке 3 памяти при появлении на входе блока 2 повторителей последующего байта с неправильной четностью.

Длительность импульса, формируемого формирователем 6, выбрана равной половине длительности импульса тактовой частоты генератора контролируемого устройства. Это необходимо для того, чтобы исключить возможное ложное срабатывание триггера 7, так как информационные биты могут поступать с некоторым фазовым сдвигом.

Фазовый сдвиг информационных битов 1

может вызвать ложные всплески на выходах блока 5 контроля и соответственно запуск формирователя 6, но опрокидывания триггера 7 не произо йдет так как установка триггера 7 происходит по заднему фронту импульса с формирователя 6, поступающего на С- вход триггера 7, а длительность этого импульса больше, чем длительность возможных всплесков. К моменту окончания импульса с формирователя 6 на 1-входе триггера 7 в случае неискаженной передачи информации имеется нулевой запрещающий потенциал и пере

ключение триггера 7 не происходит. I

Блок 1 повторителей (фиг, 2) содержит повторители 19,1-19,9, кото25

рые исключают влияние входных цепей устройства на потенциалы, поступающие с контролируемого логического устройства (с источника информации), 5 а также схему анализа обрыва на резисторах 11 - 14, транзисторе 15, элементе 16 НЕ, элементе 17 И-НЕ и светодиоде 18. Если на вход повторителя 19,1 не поступает никакой по 0 тенциал (обрыв), транзистор 15 выключен и на элемент 17 И-НЕ с выхода элемента 16 НЕ поступает высокий уровень, элемент 17 И-НЕ включается и включает через ограничительный ре 5 зистор 14 светодиод 18. Если на вход повторителя 19.1 поступает логический ноль или единица, то на одном из входов элемента 17 И-НЕ имеется логический ноль и светодиод 18 не вклю20 чается. Вход повторителя 19.1 может быть подключен к любой точке контролируемого логического устройства для выявления состояния обрыв.

Блок 2 повторителей (фиг. 3) содержит повторители 20.1-20.9, для развязки входных цепей устройства и цепей приемника информации контролируемого логического устройства. Блок 3 памяти (фиг. 4) построен

30 на IKRS-триггерах 21.1-21.18. В триггеры 21.1-21.9 записывается информация источника, а в триггеры 21.10 - 21,18 - информация приемника.

Запись производится при наличии

35 сигнала о сбое, поступающем с формирователя 6 на С-входы триггеров 21,1- 21,18 при наличии разрешения на К- входах, поступающего с прямого выхода блока 5 контроля.

40 Блок 4 индикации (фиг, 5) с помощью элементов 22.1-22,9 2И-ЗИЛИ-НЕ обеспечивает индикацию светодиодами 25,1-25.9 состояний на входах блока 1, состояний триггеров 21,1-21,9 или 45 триггеров 21,10-21,18 в блоке 3 памяти, в зависимости от положения переключателя 23, Резисторы 24,1-24,9 ограничивают ток светодиодов 25,1- .

25.9, 50 I

Блок 5 контроля с помощью элемента 26 определяет четность или нечетность числа единиц в байте информа- ции. Элементы 27-31 сравнивают полученный элементом 26 результат с контрольным (девятым) разрядом и выдают сигнал о наличии ошибки на выходы блока 5,

51

Таким образом, устройство способно запоминать передаваемый и принимаемый байт в случае возникновения ошибки. Положение переключателя 23 Память И позволяет индицировать состояние передаваемого байта, а положение Память П - принимаемого, Проведя визуальное сравнение, можно определить неисправньй бит. Такое состояние устройством сохраняется до тех пор, пока не будет произведен сброс блока 3 памяти и триггера 7 с помощью кнопки 10 Сброс.

Таким образом, устройство обладает более широкими функциональными возможностями, так как позволяет контролировать одновременно девять информационных цепей, т.е. байт информации, а также запоминать его значение в сбойных ситуациях и выявлять ошибочный бит.

Формула изобретения

Устройство для контроля логических устройств, содержащее формирователь импульсов и блок индикации, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем контроля правильности передачи байта

36

информации и выявления неверно переданного бита информации, в него введены два блока повторителей,блок памятир блок контроля, IKRS-триггер, резистор и светодиод, причем входы цервого блока повторителей соединены с первыми входами устройства, выходы - с первыми входами блока инди- кахщи и первыми входами блока памяти, выходы которого соединены с соответствующими вторыми входами блока индикации, вторые входы через второй блок повторителей - с вторыми входами устройства, а непосредственно с входами блока контроля, соединенного прямым выходом с третьим входом блока памяти и с 1-входом IKRS-триг- гера, соединенного инвертирующим выходом .через последовательно соединенные резистор и светодиод с шиной питания устройства, а непосредственно с первым входом формирователя импульсов, соединенного вторым входом с инвертирующим выходом блока контроля , выходом с четвертым входом блока памяти и с С-входом IKRS-триггера, соединенного R-входом через замыкающие контакты кнопки с общей шиной устройства, а непосредственно - с пя- тьм входом блока памяти. .

rfJ-3/7.

21.8

f 7-J/7

г52

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1310755A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА | 1996 |

|

RU2105348C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА | 1997 |

|

RU2118846C1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Устройство для контроля электрического монтажа | 1990 |

|

SU1794258A3 |

| Устройство сопряжения для контроля блоков памяти | 1991 |

|

SU1836723A3 |

Изобретение относится к контрольно-измерительной технике. Цель изобретения - расишрение функциональных возможностей устройства.Устройство содержит формирователь 6 импульсов и блок 4 индикации. Блок 5 контроля определяет четность или нечетность числа единиц в байте информации, сравнивает полученный результат с контрольным разрядом и вьщает сигнал о наличии ошибки на выходе блока 5 контроля. Введение блоков 1 и 2 повторителей, блока 3 памяти, IKRS-триггера 7, резистора 8 и све- тодиода 9 позволяет устройству запоминать передаваемый и принимае- мьй байт в случае возникновения ошибки. Положение Память И позволяет индицировать состояние передаваемого байта, а положение Память П - принимаемого. Визуальное сравнение позволяет определить неисправньй бит. 6 ил. с (Л to ;о о 1C N4 Од HiieJ

срие.б

Составитель В.Дворкин Редактор Н.Горват Техред А.Кравчук Корректор Н.Король

Заказ 7895/41 Тираж 751Подписное

ВНИИПИ Государственно1 о комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, , д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

ou/ufffa

| Логический пробник | 1981 |

|

SU995030A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический пробник | 1980 |

|

SU917144A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-15—Публикация

1985-09-25—Подача