N)

Изобретение относится к цифровой вычислительной технике, мoжef быть использовано для контроля функционирования логических блоков, содержа- щих БИС ОЗУ (памяти), в условиях производства и при техническом обслуживании средств вычислительной техники .и автоматики и является усовершенствованием устройства по основному авт св. № 1327107.

Цель изобретения - расширение функциональных возможностей путем обеспечения контроля и диагностики последовательностных блоков.

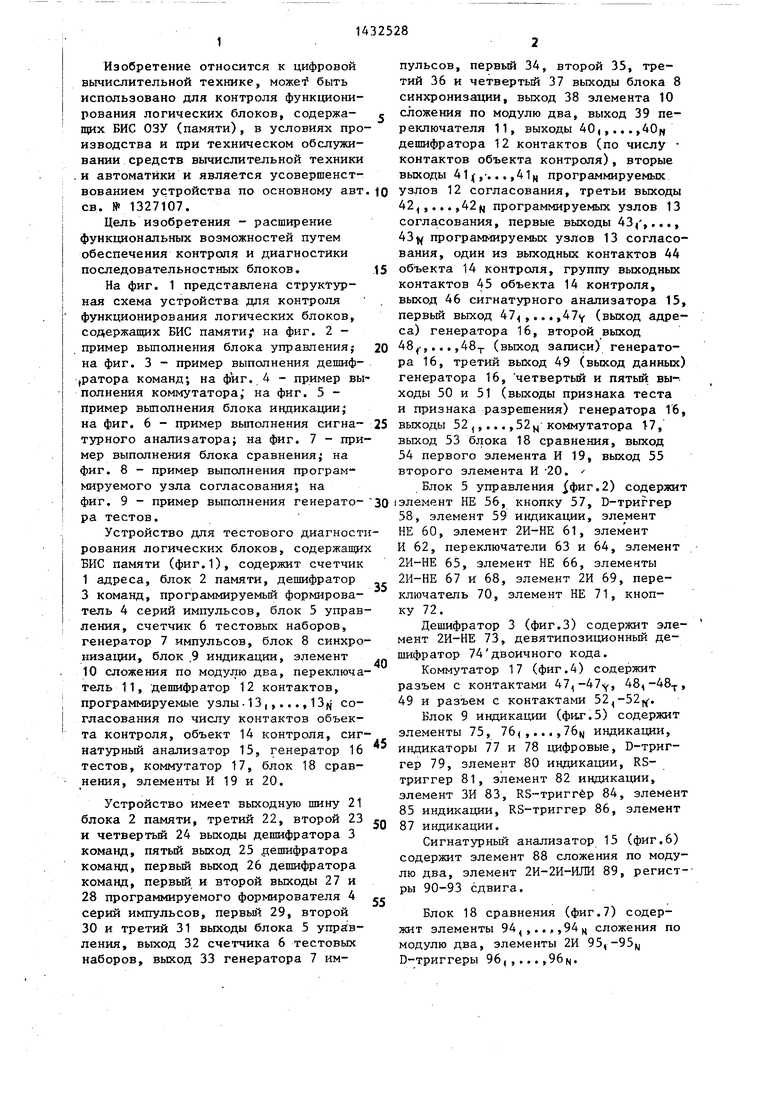

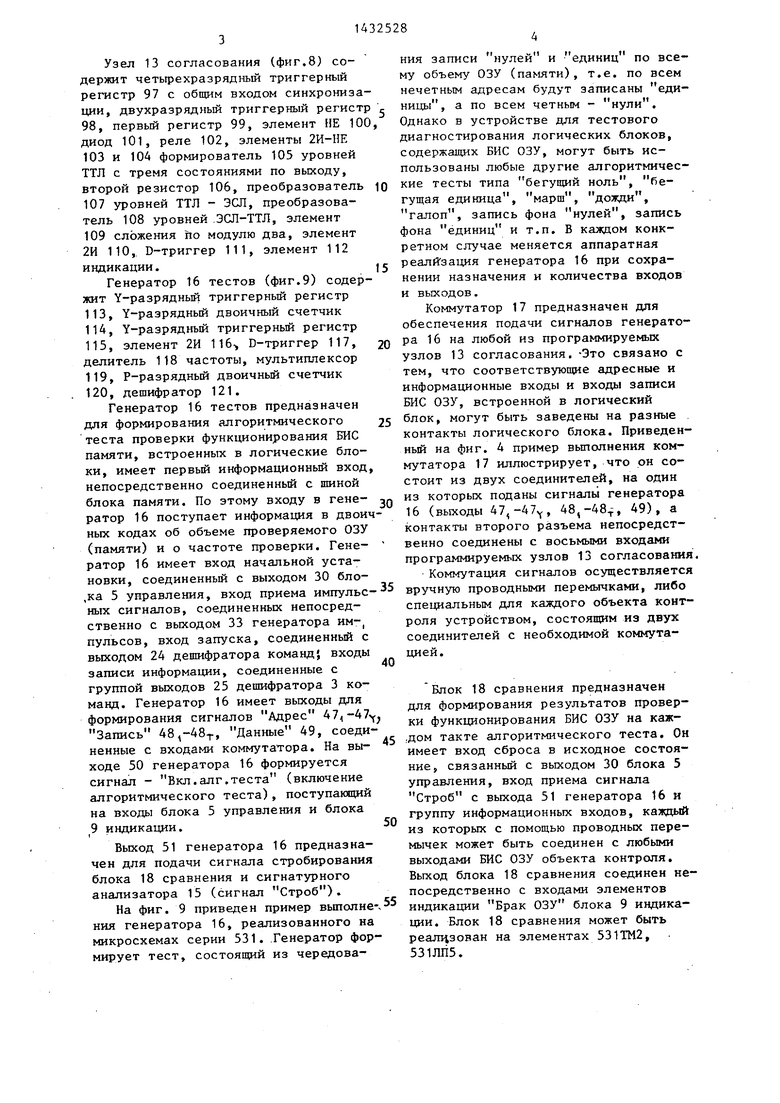

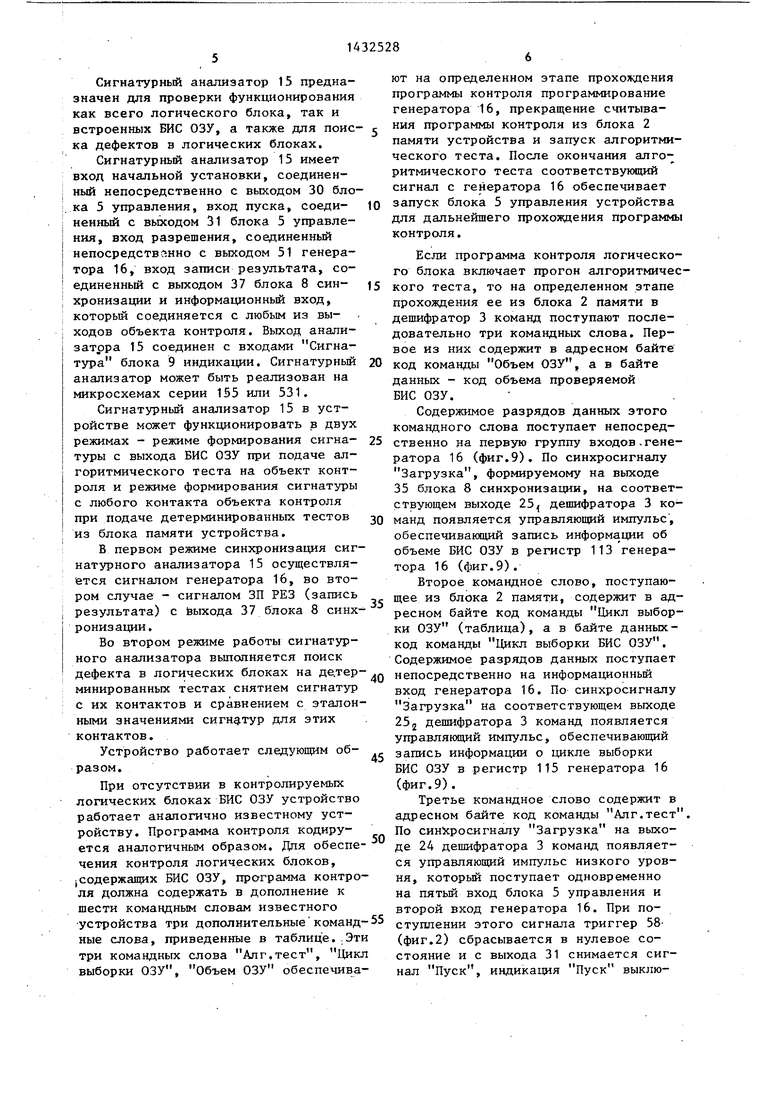

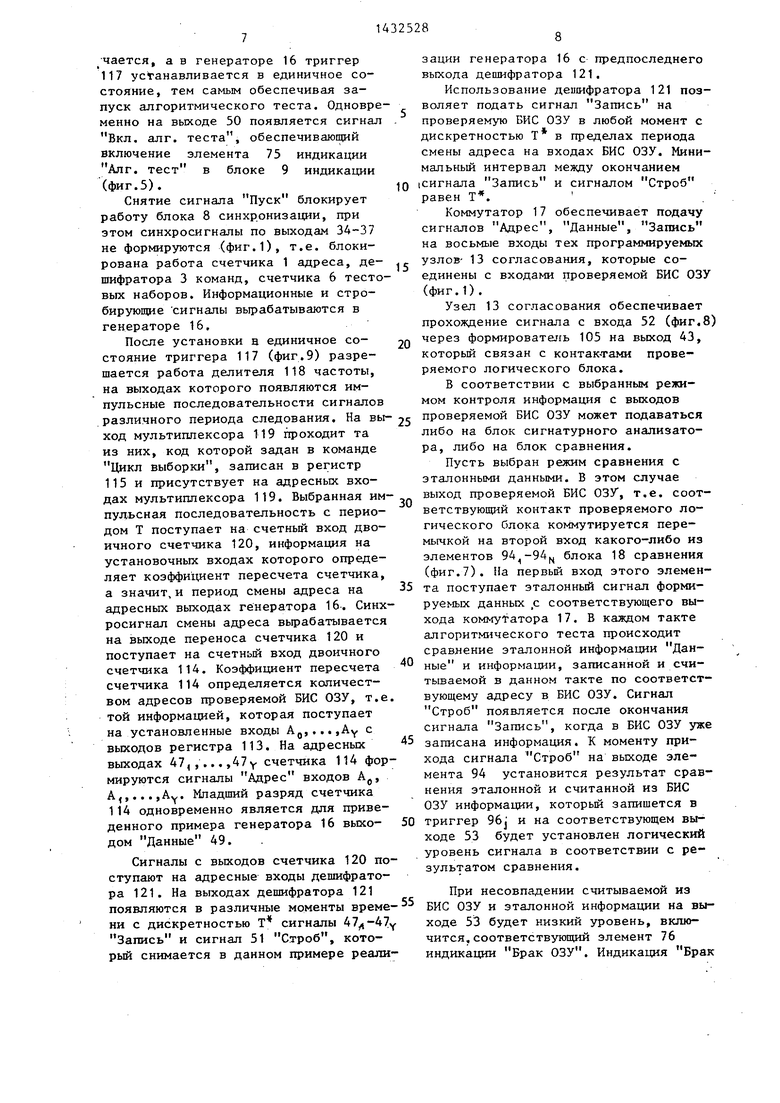

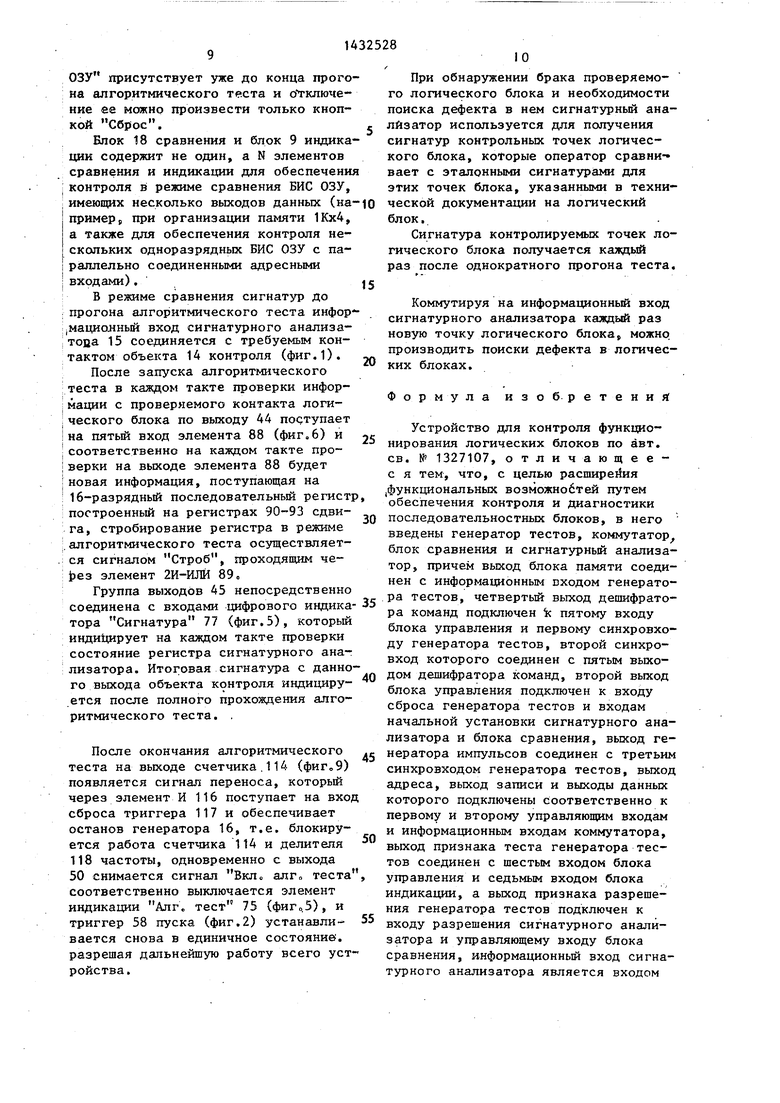

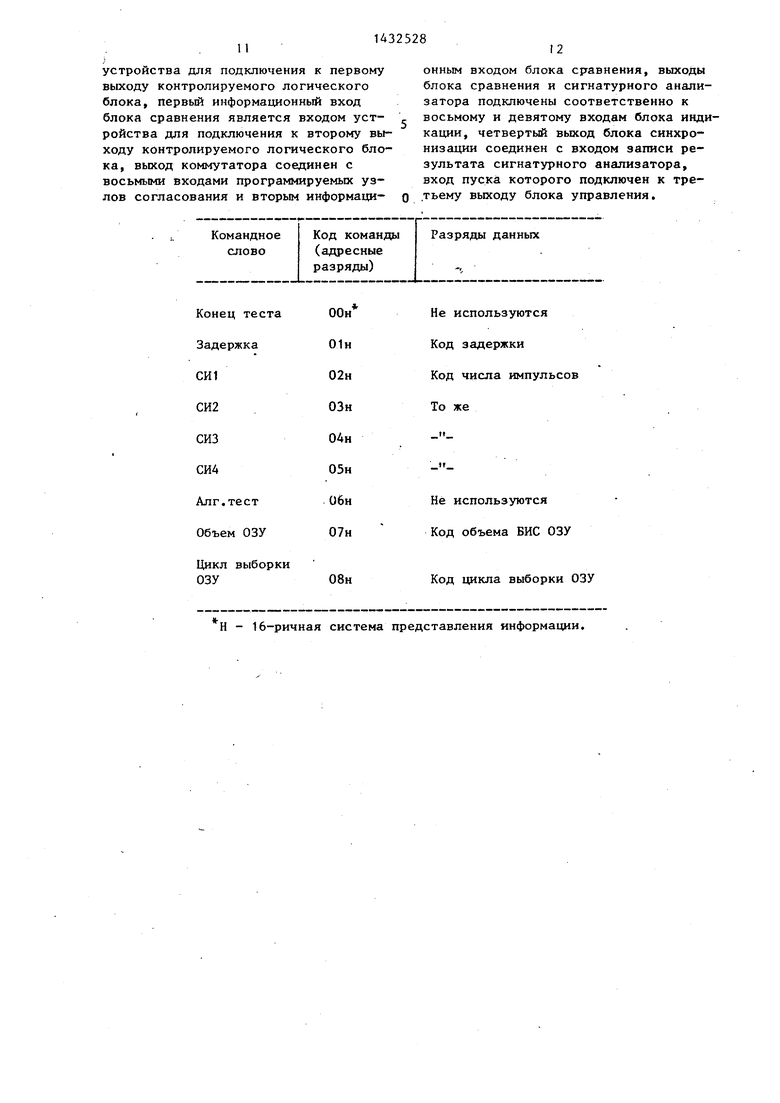

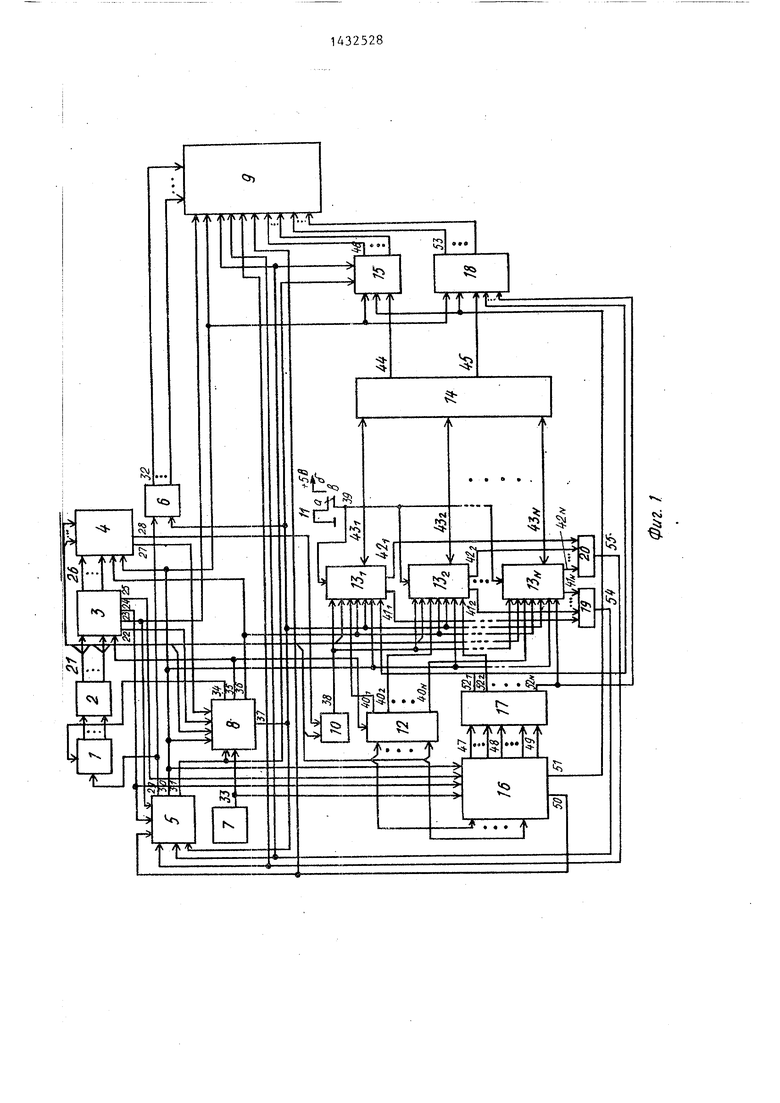

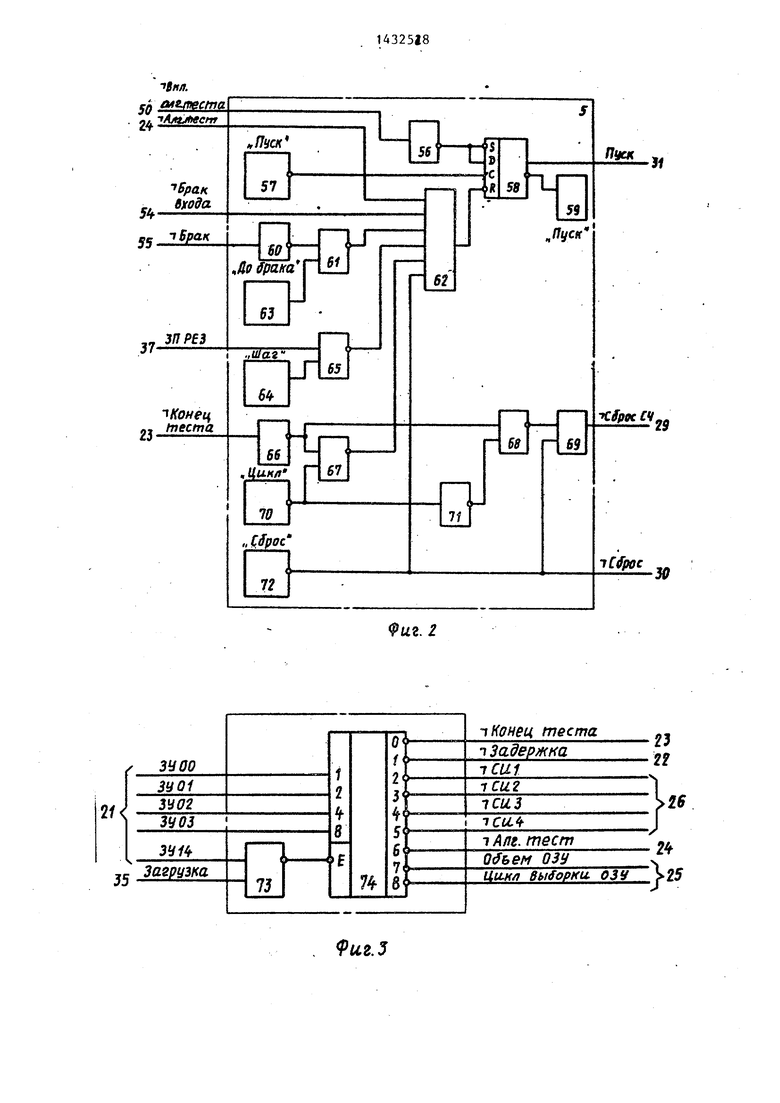

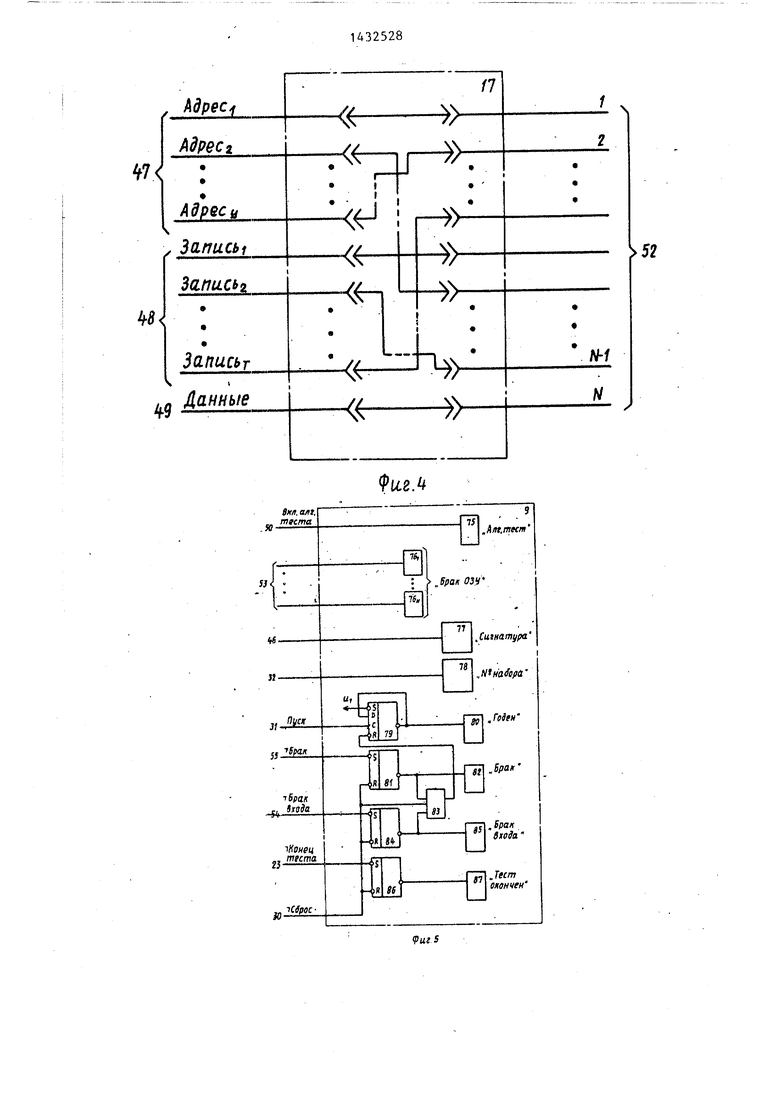

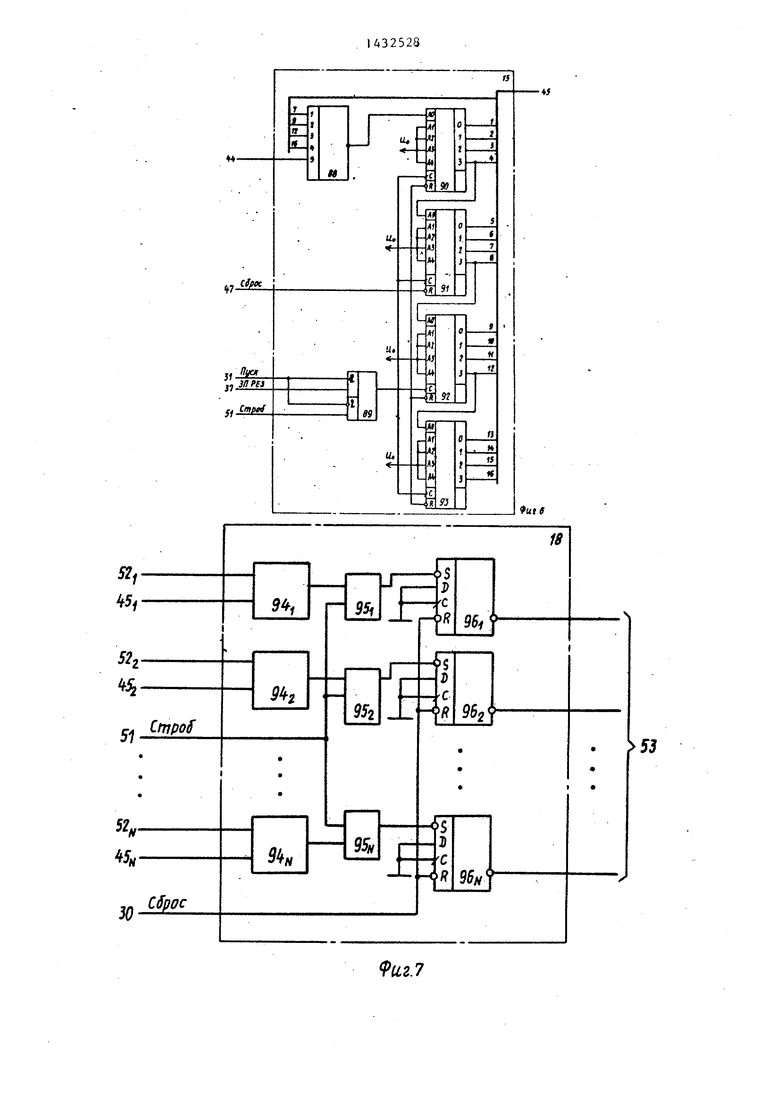

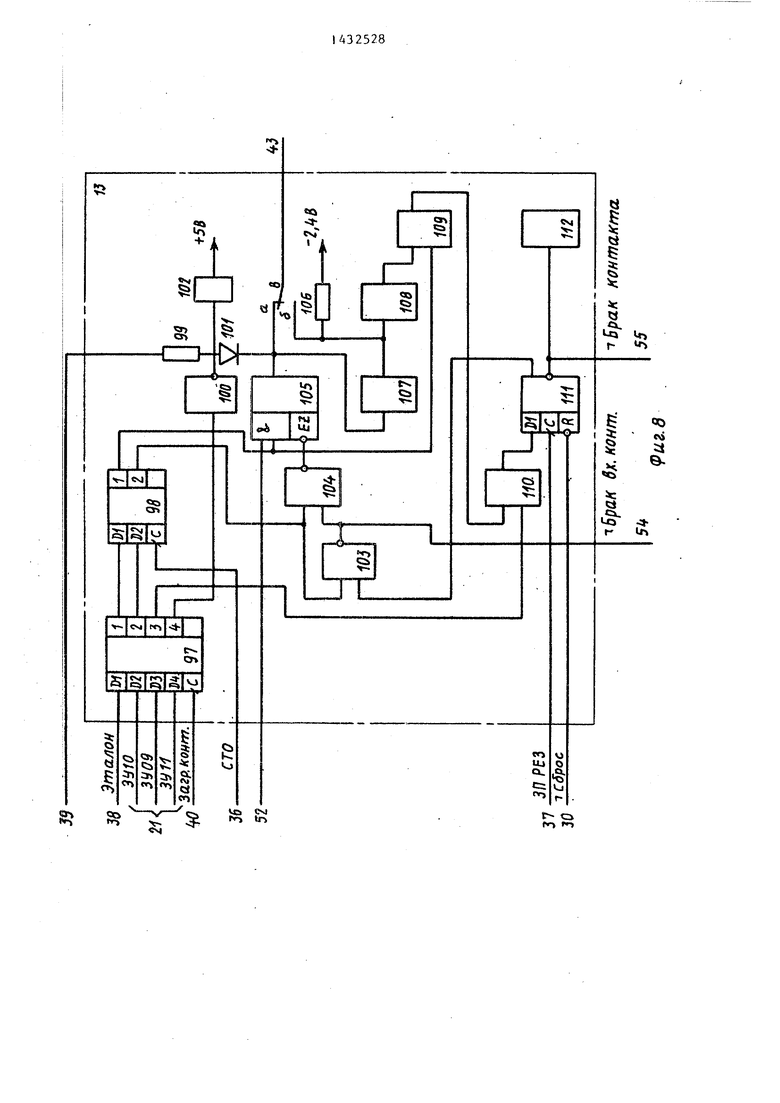

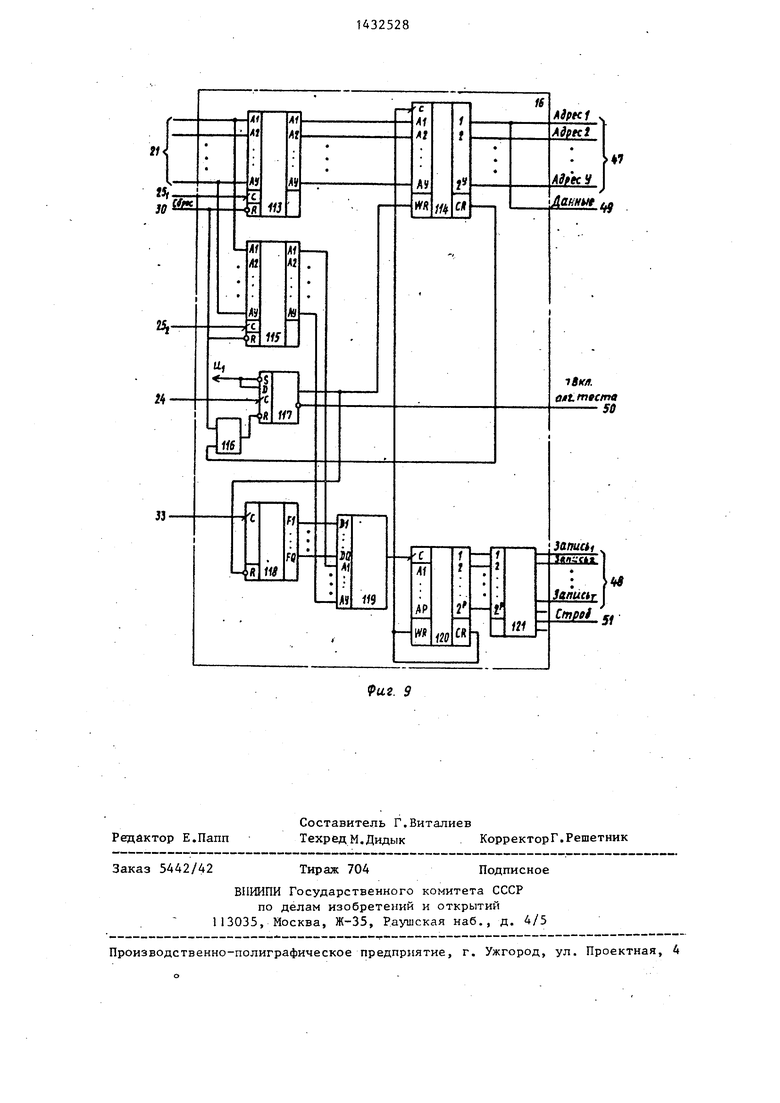

На фиг. 1 представлена структурная схема устройства для контроля функционирования логических блоков, содержащих БИС памяти; на фиг. 2 - пример выполнения блока управления; на фиг. 3 - пример выполнения дешиф- (Ратора команд; на фиг. 4 - пример выполнения коммутатора; на фиг. 5 - пример выполнения блока индикации; на фиг. 6 - пример выполнения сигна- турного анализатора; на фиг. 7 - пример выполнения блока сравнения; на фиг. 8 - пример выполнения программируемого узла согласования; на фиг. 9 - пример выполнения генерато- ра тестов.

Устройство для тестового диагностирования логических блоков, содержащих БИС памяти (фиг.1), содержит счетчик 1 адреса, блок 2 памяти, дешифратор 3 команд, программируемьй формирователь 4 серий импульсов, блок 5 управления, счетчик 6 тестовых наборов, генератор 7 импульсов, блок 8 синхронизации, блок .9 индикации, элемент 10 сложения по модулю два, переключатель 1 1 , дешифратор 12 контактов, программируемые узлы13,,...,13(ij согласования по числу контактов объекта контроля, объект 14 контроля, сигнатурный анализатор 15, генератор 16 тестов, коммутатор 17, блок 18 сравнения, элементы И 19 и 20.

Устройство имеет выходную шину 21 блока 2 памяти, третий 22, второй 23 и четвертый 24 выходы дешифратора 3 команд, пятый выход 25 дешифратора команд, первый выход 26 дешифратора команд, первый и второй выходы 27 и 28 программируемого формирователя 4 серий импульсов, первьй 29, второй 30 и третий 31 выходы блока 5 управления, выход 32 счетчика 6 тестовых наборов, выход 33 генератора 7 им

- ю

5

. 0 5 0

.„

5

пульсов, первый 34, второй 35, третий 36 и четвертый 37 выходы блока 8 синхронизации, выход 38 элемента 10 сложения по модулю два, выход 39 переключателя 11, выходы 40,,...,40 дешифратора 12 контактов (по числу контактов объекта контроля), вторые выходы 41 (,-... ,41ц программируемых узлов 12 согласования, третьи выходы 42,... ,42||, программируемых узлов 13 согласования, первые выходы 43,,..., 431( программируемых узлов 13 согласования, один из выходных контактов 44 объекта 14 контроля, группу выходньк контактов 45 объекта 14 контроля, выход 46 сигнатурного анализатора 15, первьй выход 47,...,47у (выход адреса) генератора 16, второй выход 48,,... ,48-г (выход записи) генератора 16, третий выход 49 (выход данных) генератора 16, четвертьй и пятый выходы 50 и 51 (выходы признака теста и признака разрешения) генератора 16, выходы 52,,...,52ц коммутатора 17, выход 53 блока 18 сравнения, выход 54 первого элемента И 19, выход 55 второго элемента И -20.

Блок 5 управления фиг.2) содержит (элемент НЕ 56, кнопку 57, В-три1ггер 58, элемент 59 индикации, элемент НЕ 60, элемент 2И-НЕ 61, элемент И 62, переключатели 63 и 64, элемент 2И-НЕ 65, элемент НЕ 66, элементы 2И-НЕ 67 и 68, элемент 2И 69, переключатель 70, элемент НЕ 71, кнопку 72.

Дешифратор 3 (фиг.З) содержит элемент 2И-НЕ 73, девятипозиционньй дешифратор 74 двоичного кода.

Коммутатор 17 (фиг.4) содержит разъем с контактами 47,-47у, 48,-48-j., 49 и разъем с контактами 52,.

Блок 9 индикации (фаг.5) содержит элементы 75, 764,...,76ц индикации, индикаторы 77 и 78 цифровые, D-триг- гер 79, элемент 80 индикации, RS- триггер 81, элемент 82 индикации, элемент ЗИ 83, RS-триггёр 84, элемент 85 индикации, RS-триггер 86, элемент 87 индикации.

Сигнатурный анализатор 15 (фиг.6) содержит элемент 88 сложения по модулю два, элемент 2И-2И-ИЛИ 89, регист-- ры 90-93 сдвига.

Блок 18 сравнения (фиг.7) содержит элементы 94,,..,,94 ц сложения по модулю два, элементы 2И 95 -95|g D-триггеры 96, ,... ,96(ц.

Узел 13 согласования (фиг,8) содержит четьфехразрядный триггерный регистр 97 с общим входом синхронизации, двухразрядный триггерный регистр 98, первый регистр 99, элемент НЕ 100 диод 101, реле 102, элементы 2И-НЕ 103 и 104 формирователь 105 уровней ТТЛ с тремя состояниями по выходу, второй резистор 106, преобразователь 107 уровней ТТЛ - ЭСЛ, преобразователь 108 уровней .ЭСЛ-ТТЛ, элемент 109 сложения по модулю два, элемент 2И 110,. D-триггер 111, элемент 112 индикации.

Генератор 16 тестов (фиг.9) содержит Y-разрядный триггерный регистр

113,Y-разрядный двоичный счетчик

114,Y-разрядный триггерньй регистр

115,элемент 2И 116 D-триггер 117, делитель 118 частоты, мультиплексор

119,Р-разрядный двоичньш счетчик

120,дешифратор 121.

Генератор 16 тестов предназначен для формирования алгоритмического теста проверки функционирования БИС памяти, встроенных в логические блоки, имеет первый информационньш вход, непосредственно соединенный с шиной блока памяти. По этому входу в гене- ратор 16 поступает информация в двоичных кодах об объеме хфоверяемого ОЗУ (памяти) и о частоте проверки. Гене- ратор 16 имеет вход начальной установки, соединенный с выходом 30 бло- ,ка 5 управления, вход приема импульсных сигналов, соединенных непосредственно с выходом 33 генератора им-, пульсов, вход запуска, соединенный с выходом 24 дешифратора команд} входы записи информации, соединенные с группой выходов 25 дешифратора 3 команд. Генератор 16 имеет выходы для формирования сигналов Адрес Запись 48,-48т, Данные 49, соединенные с входами коммутатора. На выходе 50 генератора 16 формируется сигнал - Вкп.алг.теста (включение алгоритмического теста) , поступакнций на входы блока 5 управления и блока 9 индикации.

Выход 51 генератора 16 предназначен для подачи сигнала стробирования блока 18 сравнения и сигнатурного анализатора 15 (сигнал Строб).

На фиг. 9 приведен пример вьшолнения генератора 16, реализованного на микросхемах серии 531. Генератор формирует тест, состоящий из чередова

ния записи нулей и единиц по всему объему ОЗУ (памяти), т.е. по всем нечетным адресам будут записаны единицы ,

а по всем четным - нули,

Однако в устройстве для тестового диагностирования логических блоков, содержащих БИС ОЗУ, могут быть использованы любые другие алгоритмические тесты типа бегущий ноль, бегущая единица, марш, дозкди, галоп, запись фона нулей, запись фона единиц и т.п. В кахдом конкретном случае меняется аппаратная реалйГзация генератора 16 при сохранении назначения и количества входов и выходов.

Коммутатор 17 предназначен для обеспечения подачи сигналов генерато- ра 16 на любой из программируемых узлов 13 согласования. -Это связано с тем, что соответствующие адресные и информационные входы и входы записи БИС ОЗУ, встроенной в логический блок, могут быть заведены на разные контакты логического блока. Приведенный на фиг. 4 пример вьшолнения коммутатора 17 иллюстрирует, что он состоит из двух соединителей, на один из которых поданы сигналы генератора 16 (выходы 47,-47, 48,, 49), а контакты второго разъема непосредственно соединены с восьмыми входами программируемых узлов 13 согласования.

Коммутация сигналов осуществляется вручную проводными перемычками, либо специальным для каждого объекта контроля устройством, состоящим из двух соединителей с необходимой коммутацией.

Блок 18 сравнения предназначен для формирования результатов проверки функционирования БИС ОЗУ на каждом такте алгоритмического теста. Он имеет вход сброса в исходное состояние, связанный с выходом 30 блока 5 управления, вход приема сигнала Строб с выхода 51 генератора 16 н группу информационных входов, каждьЛ из которых с помощью проводных перемычек может быть соединен с любыми выходами БИС ОЗУ объекта контроля. Выход блока 18 сравнения соединен непосредственно с входами элементов индикации Брак ОЗУ блока 9 индикации. Блок 18 сравнения может быть реализован на элементах 531ТМ2, 531ЛП5.

Сигнатурный анализатор 15 предназначен для проверки функционирования как всего логического блока, так и встроенных БИС ОЗУ, а также для поиска дефектов в логических блоках.

Сигнатурный анализатор 15 имеет вход начальной установки, соединенный непосредственно с выходом 30 блока 5 управления, вход пуска, соединенный с вьгходом 31 блока 5 управления, вход разрешения, соединенный непосредств.нно с выходом 51 генератора 16, вход записи результата, соединенный с выходом 37 блока 8 синхронизации и информационный вход, который соединяется с любым из выходов объекта контроля. Выход анализатора 15 соединен с входами Сигнатура блока 9 индикации. Сигнатурньй анализатор может быть реализован на микросхемах серии 155 или 531,

Сигнатурный анализатор 15 в устройстве может функционировать в двух режимах - режиме формирования сигнатуры с выхода БИС ОЗУ при подаче алгоритмического теста на объект контроля и режиме формирования сигнатуры с любого контакта объекта контроля при подаче детерминированных тестов из блока памяти устройства.

В первом режиме синхронизация сигнатурного анализатора 15 осуществляется сигналом генератора 16, во втором случае - сигналом ЗП РЕЗ (запись результата) с йыхода 37 блока 8 синхронизации.

Во втором режиме работы сигнатурного анализатора выполняется поиск дефекта в логических блоках на де.тер- минированных тестах снятием сигнатур с их контактов и сравнением с эталонными значениями сигнатур для этих контактов.

Устройство работает следующим образом.

При отсутствии в контролируемых логических блоках БИС ОЗУ устройство работает аналогично известному устройству. Программа контроля кодируется аналогичным образом. Для обеспечения контроля логических блоков, )Содержащих БИС ОЗУ, программа контроля должна содержать в дополнение к шести командным словам известного устройства три дополнительные командные слова, приведенные в таблице..Эти три командных слова Алг.тест, Цикл выборки ОЗУ, Объем ОЗУ обеспечива0

5

0

5

0

5

0

5

0

5

ют на определенном этапе прохождения 1фограммы контроля программирование генератора 16, прекращение считывания программы контроля из блока 2 памяти устройства и запуск алгоритмического теста. После окончания алгоритмического теста соответствующий сигнал с генератора 16 обеспечивает запуск блока 5 управления устройства для дальнейшего прохождения программы контроля.

Если программа контроля логического блока включает прогон алгоритмического теста, то на определенном этапе прохождения ее из блока 2 памяти в дешифратор 3 команд поступают последовательно три командных слова. Первое из них содержит в адресном байте код команды Объем ОЗУ, а в байте данных - код объема проверяемой БИС ОЗУ.

Содержимое разрядов данных этого командного слова поступает непосредственно на первую группу входов.генератора 16 (фиг.9). По синхросигналу Загрузка, формируемому на выходе 35 блока 8 синхронизации, на соответствующем выходе 25 дешифратора 3 команд появляется управляющий импульс, обеспечиваняций запись информации об объеме БИС ОЗУ в регистр 113 генератора 16 (фиг.9).

Второе командное слово, поступающее из блока 2 памяти, содержит в адресном байте код команды Цикл выборки ОЗУ (таблица), а в байте данных- код команды Цикл выборки БИС ОЗУ. Содержимое разрядов данных поступает непосредственно на информационньй вход генератора 16. По синхросигналу Загрузка на соответствующем выходе 252 дешифратора 3 команд появляется управляющий импульс, обеспечивающий запись информации о цикле выборки БИС ОЗУ в регистр 115 генератора 16 (фиг.9).

Третье командное слово содержит в адресном байте код команды Алг.тест. По синхросигналу Загрузка на выходе 24 дешифратора 3 команд появляется управляющий импульс низкого уровня, который поступает одновременно на пятьш вход блока 5 управления и второй вход генератора 16. При поступлении этого сигнала триггер 58- (фиг.2) сбрасывается в нулевое состояние и с выхода 31 снимается сигнал Пуск, индикация Пуск выклю чается, а в генераторе 16 триггер 117 устанавливается в единичное состояние, тем самым обеспечивая запуск алгоритмического теста. Одновременно на выходе 50 появляется сигнал Вкл, алг. теста, обеспечивающий включение элемента 75 индикации Алг. тест в блоке 9 индикации (фиг.5).

Снятие сигнала Пуск блокирует работу блока 8 синхронизации, при этом синхросигналы по выходам ЗД-37 не формируются (фиг.1), т.е. блокирована работа счетчика 1 адреса, дешифратора 3 команд, счетчика 6 тестовых наборов. Информационные и стро- бирующие сигналы вырабатываются в генераторе 16.

После установки а единичное состояние триггера 117 (фиг.9) разрешается работа делителя 118 частоты, на выходах которого появляются импульсные последовательности сигналов различного периода следования. На выход мультиплексора 119 гфоходит та из них, код которой задан в команде Цикл выборки, записан в регистр 115 и присутствует на адресных входах мультиплексора 119. Выбранная им пул ьсная последовательность с периодом Т поступает на счетный вход двоичного счетчика 120, информация на установочных входах которого определяет коэффициент пересчета счетчика, а значит, и период смены адреса на адресных выходах генератора 16. Синхросигнал смены адреса вырабатывается на выходе переноса счетчика 120 и поступает на счетньй вход двоичного счетчика 114. Коэффициент пересчета счетчика 114 определяется количеством адресов проверяемой БИС ОЗУ, т.е той информацией, которая поступает на установленные входы Ад,...,Ау с выходов регистра 113. На адресных выходах 47,,...,47у счетчика 114 формируются сигналы Адрес входов А,

А,Ау. Младший разряд счетчика

114 одновременно является для приведенного примера генератора 16 выходом Данные 49.

Сигналы с выходов счетчика 120 поступают на адресные входы дешифратора 121. На выходах дешифратора 121 появляются в различные моменты времени с дискретностью Т сигналы Запись и сигнал 51 Строб, кото- рьш снимается в данном примере реали0

5

0

5

0

5

0

5

0

5

зации генератора 16 с предпоследнего выхода дешифратора 121.

Использование дешифратора 121 позволяет подать сигнал Запись на проверяемую БИС ОЗУ в любой момент с дискретностью Т в пределах периода смены адреса на входах БИС ОЗУ. Минимальный интервал между окончанием {Сигнала Запись и сигналом Строб равен Т.

Коммутатор 17 обеспечивает подачу сигналов Адрес, Данные, Запись на восьмые входы тех программируемых узлов- 13 согласования, которые соединены с входами проверяемой БИС ОЗУ (фиг.1).

Узел 13 согласования обеспечивает прохождение сигнала с входа 52 (фиг,8) через формирователь 105 на выход 43, который связан с контак-тами проверяемого логического блока.

В соответствии с выбранным режимом контроля информация с выходов проверяемой БИС ОЗУ может подаваться либо на блок сигнатурного анализатора, либо на блок сравнения.

Пусть выбран режим сравнения с эталонными данными. В этом случае выход проверяемой БИС ОЗУ, т.е. соответствующий контакт проверяемого логического блока коммутируется перемычкой на второй вход какого-либо из элементов , блока 18 сравнения (фиг.7). 1а первый вход этого элемента поступает эталонный сигнал формируемых данных с соответствующего выхода коммутатора 17. В каждом такте алгоритмического теста происходит сравнение эталонной информации Данные и информации, записанной и счи- тьшаемой в данном такте по соответствующему адресу в БИС ОЗУ. Сигнал Строб появляется после окончания сигнала Запись, когда в БИС ОЗУ уже записана информация. К моменту прихода сигнала Строб на выходе элемента 94 установится результат сравнения эталонной и считанной из БИС ОЗУ информации, которьй запишется в триггер 96j и на соответствующем выходе 53 будет установлен логический уровень сигнала в соответствии с результатом сравнения.

При несовпадении считываемой из БИС ОЗУ и эталонной информации на выходе 53 будет низкий уровень, включится, соответствующий элемент 76 индикации Брак ОЗУ. Индикация Брак

ОЗУ присутствует уже до конца прогона алгоритмического теста и о тключе- ние ее можно произвести только кнопкой Сброс.

Елок 18 сравнения и блок 9 индикации содержит не один, а N элементов сравнения и индикации для обеспечения контроля в режиме сравнения БИС ОЗУ,

При обнаружении брака проверяем го логического блока и необходимос поиска дефекта в нем сигнатурный а лизатор используется для получения сигнатур контрольных точек логичес кого блока, кotopыe оператор сравн вает с эталонными сигнатурами для этих точек блока, указанными в тех

; имеющих несколько выходов данных (на-ю ческой документации на логический

При обнаружении брака проверяемого логического блока и необходимости поиска дефекта в нем сигнатурный анализатор используется для получения сигнатур контрольных точек логического блока, кotopыe оператор сравни- вает с эталонными сигнатурами для этих точек блока, указанными в технической документации на логический

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля функционирования логических блоков, содержащих БИС ОЗУ (памяти), в условиях производства и при техническом обслуживании средств вычислительной техники и автоматики. Целью изобретения является расширение функциональных возможностей устройства путен обеспечения контроля и диагностики последовательных блоков. С этой целью в устройство, содержащее счетчик адреса, блок памяти, дешифратор команд, программируемый формирователь серий импульсов, блок управления, счетчик тестовых наборов, генератор импульсов, блок синхронизации, блок индикации, элемент сложения по модулю два, переключатель, дешифратор контактов, N программируемых узлов согласования и два элемента И, введены сигнатурный анализатор, генератор тестов, коммутатор и блок сравнения. 9 ил. 1 табл. с S (Л

I примере при организации памяти 1Кх4, а также для обеспечения контроля не- I скольких одноразрядных БИС ОЗУ с па- I раллельно соединенными адресными I входами).

В режиме сравнения сигнатур до : прогона алгоритмического теста инфор ;|Мациояньй вход сигнатурного анализа- ;това 15 соединяется с требуемым контактом объекта 14 контроля (фиг.1).

После запуска алгоритмического теста в каждом такте проверки инфор- Iмации с проверяемого контакта логи- ческого блока по выходу 44 поступает I на пятый вход элемента 88 (фиг.6) и ;соответственно на каждом такте про- 1верки на выходе элемента 88 будет ;новая информация, поступающая на : 16-разрядный последовательный регистр : построенный на регистрах 90-93 сдвига, стробирование регистра в режиме 1, алгоритмического теста осуществляет- . ся сигналом Строб, проходящим че- i)e3 элемент 2И-ИЛИ 89,

Группа выходов 45 непосредственно соединена с входами цифрового индика тора Сигнатура 77 (фиг.5), который индицирует на каждом такте проверки состояние регистра сигнатурного ана- ; лизатора. Итоговая сигнатура с данного выхода объекта контроля индицируется после полного прохождения алгоритмического теста. .

После окончания алгоритмического теста на выходе счетчика. 114 (фиГо9) появляется сигнал переноса, который через элемент И 116 поступает на вход сброса триггера 117 и обеспечивает останов генератора 16, т.е. блокируется работа счетчика 114 и делителя 118 частоты, одновременно с выхода 50 снимается сигнал ВкЛс алг теста соответственно выключается элемент индикации Алг. тест 75 (фиг5,5), и триггер 58 пуска (фиг.2) устанавливается снова в единичное состояние, разрешая дальнейшую работу всего устройства.

блок.

Сигнатура контролируемых точек логического блока получается каждый раз после однократного прогона теста,

Коммутируя на информационный вход сигнатурного анализатора каждый раз новую точку логического блока, можно. производить поиски дефекта в логических блоках.

Формула изобретения

Устройство для контроля функционирования логических блоков по авт. св. № 1327107, отличающее- с я тем, что, с целью расширейия (функциональных возможнобтей путем обеспечения контроля и диагностики

последовательностных блоков, в него введены генератор тестов, коммутатор, блок сравнения и сигнатурньй анализатор, причем выход блока памяти соединен с информационным входом генератора тестов, четвертьй выход дешифратора команд подключен к пятому входу блока управления и первому синхровхо- ду генератора тестов, второй синхро- вход которого соединен с пятым выходом дешифратора команд, второй выход блока управления подключен к входу сброса генератора тестов и входам начальной установки сигнатурного анализатора и блока сравнения, выход генератора импульсов соединен с третьим синхровходом генератора тестов, выход адреса, выход записи и выходы данных которого подключены Соответственно к первому и второму управляющим входам и информационным входам коммутатора, выход признака теста генератора тестов соединен с шестым входом блока

управления и седьмым входом блока индикации, а выход признака разрешения генератора тестов подключен к входу разрешения сигнатурного анализатора и управляющему входу блока сравнения, информационный вход сигнатурного анализатора является входом

устройства для подключения к первому выходу контролируемого логического блока, первый информационный вход блока сравнения является входом устройства для подключения к второму выходу контролируемого логического блока, выход коммутатора соединен с восьмыми входами программируемых узлов согласования и вторым информаци- о тьему выходу блока управления.

Конец теста

Задержка

СИ1

СИ2

СИЗ

СИ4

Алг.тест

Объем ОЗУ

Цикл выборки

ОЗУ

Н - 16-ричная система представления информации.

онным входом блока сравнения, выходы блока сравнения и сигнатурного анализатора подключены соответственно к восьмому и девятому входам блока индикации, четвертый выход блока синхронизации соединен с входом записи результата сигнатурного анализатора, вход пуска которого подключен к треНе используются

Код задержки

Код числа импульсов

То же

ti

if

Не используются Код объема БИС ОЗУ

Код цикла выборки ОЗУ

iffiff. Q fusifliectna

2i

23

21

35

, 9uz,5

If

PU2. 2

ФигЛ

9uiff

иг.7

id Csl

rr lo

«ч

QO

esi

:i Bt- О

f

tSt SO

«

7

SO

fu2. 9

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-06—Подача