10

t5

20

25

11310836-

Изобретение относится, к цифровой вычислительной технике и может быть использовано при разработке и моде- лировании вычислительных систем.

Цель изобретения - расширение функциональных возможностей за счет моделирования последовательного распределения заданий на обработку между процессорами.

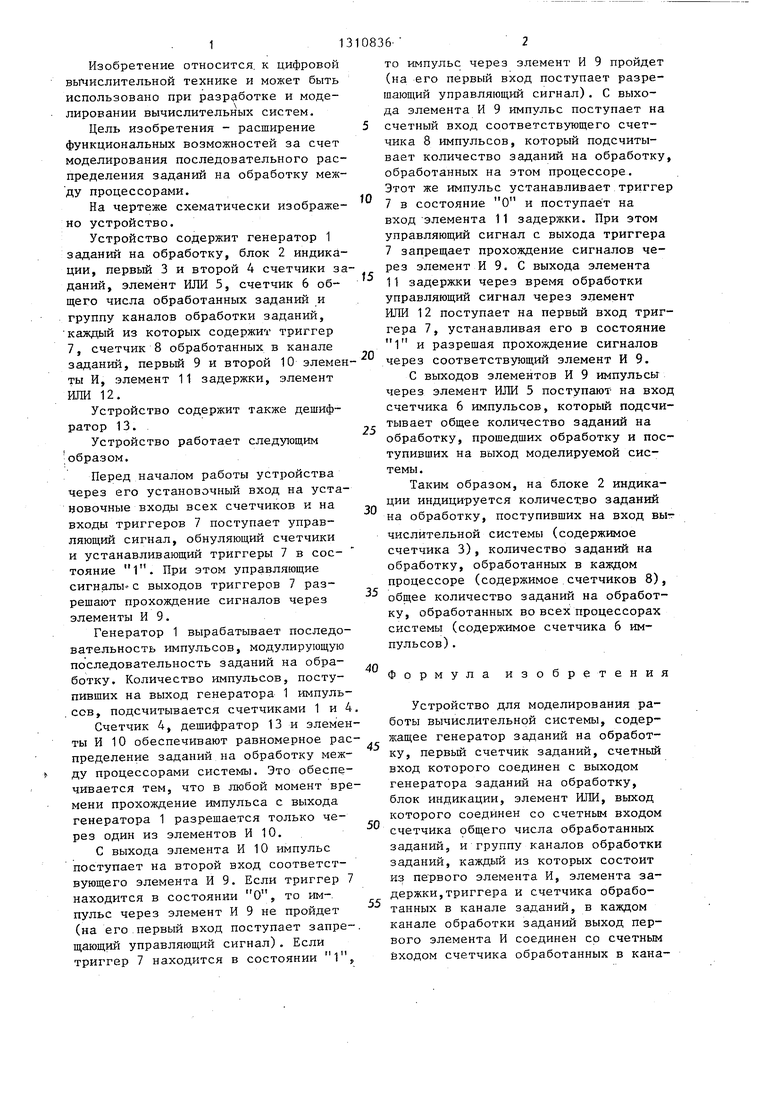

На чертеже схематически изображено устройство.

Устройство содержит генератор 1 заданий на обработку, блок 2 индикации, первый 3 и второй 4 счетчики заданий, элемент ИЛИ 5, счетчик 6 общего числа обработанных заданий и группу каналов обработки заданий, каждый из которых содержит триггер 7, счетчик 8 обработанных в канале заданий, первый 9 и второй 10 элементы И, элемент 11 задержки, элемент ИЛИ 12.

Устройство содержит также дешифратор 13.

Устройство работает следу7ощим образом.

Перед началом работы устройства через его установочный вход на установочные входы всех счетчиков и на входы триггеров 7 поступает управляющий сигнал, обнуляющий счетчики и устанавливающий триггеры 7 в состояние 1. При этом управляющие сигналы-с выходов триггеров 7 разрешают прохождение сигналов через элементы И 9.

Генератор 1 вырабатывает последовательность импульсов, модулирующую последовательность заданий на обработку. Количество импульсов, поступивших на выход генератора 1 импуль- . сов, подсчитывается счетчиками 1 и 4.

Счетчик 4, дешифратор 13 и элементы И 10 обеспечивают равномерное распределение заданий на обработку меж- ду процессорами системы. Это обеспечивается тем, что в любой момент времени прохождение импульса с выхода генератора 1 разрешается только через один из элементов И 10.

С выхода элемента И 10 импульс поступает на второй вход соответствующего элемента И 9. Если триггер 7 находится в состоянии О, то импульс через элемент И 9 не пройдет (на его первый вход поступает запре-. щающий управляющий сигнал). Если триггер 7 находится в состоянии 1,

то (на шаю да 5 сче чик вае обр Это 7 в вхо упр 7 з рез 11 упр ИЛИ гер 1 чер

чер сче тыв обр туп тем

ции на чис сче обр про

зс

общ ку, сис пул

40

Фо

бот жащ ку, вхо ген бло кот сче зад зад из дер тан кан вог вхо

30

45

55

5

0

5

то импульс через элемент И 9 пройдет (на его первый вход поступает разрешающий управляющий сигнал). С выхода элемента И 9 импульс поступает на счетный вход соответствующего счетчика 8 импульсов, который подсчитывает количество заданий на обработку, обработанных на этом процессоре. Этот же импульс устанавливает триггер 7 в состояние О и поступает на вход элемента 11 задержки. При этом управляющий сигнал с выхода триггера 7 запрещает прохождение сигналов через элемент И 9. С выхода элемента 11 задержки через время обработки управляющий сигнал через элемент ИЛИ 12 поступает на первый вход триггера 7, устанавливая его в состояние 1 и разрешая прохождение сигналов через соответствующий элемент И 9.

С выходов элементов И 9 импульсы через элемент ИЛИ 5 поступают на вход счетчика 6 импульсов, который подсчитывает общее количество заданий на обработку, прошедших обработку и поступивших на выход моделируемой системы .

Таким образом, на блоке 2 индикации индицируется количество заданий на обработку, поступивших на вход вычислительной системы (содержимое счетчика 3), количество заданий на обработку, обработанных в каждом процессоре (содержимое счетчиков 8),

с

общее количество заданий на обработку, обработанных во всех процессорах системы (содержимое счетчика б импульсов) .

0

Формула изобретения

Устройство для моделирования работы вычислительной системы, содержащее генератор заданий на обработку, первый счетчик заданий, счетный вход которого соединен с выходом генератора заданий на обработку, блок индикации, элемент ИЛИ, выход которого соединен со счетным входом счетчика рбщего числа обработанных заданий, и группу каналов обработки заданий, каждый из которых состоит из пе рвого элемента И, элемента задержки, триггера и счетчика обработанных в канале заданий, в каждом канале обработки заданий выход первого элемента И соединен со счетньм входом счетчика обработанных в кана0

5

5

ле заданий, входом элемента задержки и первым входом триггера, выход которого подключен к первому входу первого элемента И, выходы первых элементов И всех каналов обработки заданий подключены соответственно к входам элемента ИЛИ устройства, информационные выходы первого счетчика заданий, счетчика общего числа обработанных заданий, счетчиков обработанных в канале заданий соединены соответственно с входами блока индикации, а установочные входы счетчиков объединены и являются установочным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования последовательного распределения заданий на обработку между процессорами, оно дополнительно содержит второй счетчик заданий, дешифратор, а в каждом кана-.

Редактор Н.Горват Заказ 1893/46

Составитель В.Фукалов

Техред Л.Олейник Корректор С.Шекмар

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ле обработки заданий второй элем нт И и элемент ИЛИ, причем первые входы вторых элементов И всех каналов обработки заданий подключены к выходу

генератора заданий и счетному входу второго счетчика заданий устройства, разрядные выходы которого подключены к входам дешифратора, выходы которого соединены соответственно с вторыми входами вторых элементов И каналов обработки заданий, в каждом канале обработки заданий выход второго . элемента И соединен с вторым входом первого элемента И, выход элемента задержки подключен к первому входу элемента ИЛИ, выход которого соединен с вторым входом триггера, установочный вход второго счетчика заданий и вторые входы элементов ИЛИ

всех каналов обработки заданий соединены с установочным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем передачи и обработки данных | 1983 |

|

SU1150629A1 |

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1151983A1 |

| Устройство для моделирования систем обработки данных | 1983 |

|

SU1151982A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ | 1990 |

|

RU2041487C1 |

| Устройство для моделирования системы сбора и обработки информации | 1983 |

|

SU1107129A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1783539A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для моделирования систем передачи и обработки данных | 1987 |

|

SU1444804A1 |

| Устройство для моделирования системы связи | 1984 |

|

SU1229770A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет моделирования последовательного распределения заданий на обработку между процессорами. Устройство для моделирования работы вычислительной системы содержит генератор 1 заданий на обработку, блок 2 индикации, первый 3 и второй 5 счетчики заданий, дешифратор 13, элемент ИЛИ 5, счетчик 6 общего числа обработанных заданий и группу каналов обработки,каждый из которых содержит два элемента И 9, 10, триггер 7, элемент 11 за держки, элемент ИЛИ 12 и счетчик 8 обработанных в канале заданий. 1 ил. (Л оо 00 00 а

| Авторское свидетельство СССР цо заявке № 3591021, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем связи | 1984 |

|

SU1185347A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-05-15—Публикация

1985-11-05—Подача