Изобретение относится к вычислительной технике и может быть использовано при создании аналого-цифровых устройств и систем для моделирования динамических объектов и систем управления в реальном масштабе времени.

Известно устройство для сопряжения аналоговой и цифровой вычислительных машин, содержащее АЦП, ЦАП, 2 счетчика, 2 регистра, схему сравнения, элементы И, НЕ, задержки, триггеры, генератор импульсов, взаимосвязанные в соответствии с алгоритмом функционирования устройства.

Недостатком данного устройства является выполнение операций взаимодействия пользователя с цифровой частью системы последовательно с выполнением операций вычисления, аналого-цифрового преобразования, периодического запуска и управления работой АЦП, цифроаналогового преобразования.

Наиболее близким к предлагаемому устройству является устройство для обмена информацией между цифровой и аналоговой вычислительными машинами, содержащее АЦП, ЦАП, блок памяти, дешифратор адреса, три счетчика адреса, два блока сравнения, два регистра, триггера, генератор импульсов, шинные формирователи, элементы И, ИЛИ, НЕ, задержки.

Недостатком указанного устройства является достаточно большие затраты времени при вводе и выводе информации пользователем в цикле реального времени решения. Недостаток является следствием того, что ввод-вывод информации в аналого-ч ел ел со

XI

ю

вую и цифровую часть системы производится с раздельных пультов управления соответствующих частей, Причем при вводе-выводе информации через серийные устройства ввода и отображения информа- ции в цифровой процессор происходит пре- рывание программы цикла реального времени решения гибридной задачи, что нарушает совмещение операций преобразования информации в системе связи и вычисления в цифровом процессоре.

Цель изобретения - сокращение времени ввода-вывода информации в цикле реального времени решения задач моделирования динамических систем.

Поставленная цель достигается тем, что в устройство, содержащее аналого-цифровой преобразователь (АЦП) цифроаналого- вый преобразователь (ЦАП), генератор импульсов, блок памяти, дешифратор адреса, триггера, два регистра, три счетчика, два блока сравнения, шинные формирователи, элементы И, ИЛИ и НЕ, задержки, причем информационный вход аналого-цифрового преобразователя является входом устройства для подключения к аналоговой вычислительной машине, выход генератора импульсов соединен с первым входом первого элемента И, первый вход первого блока сравнения соединен с первым выходом первого счетчика, информационный выход аналого-цифрового преобразователя через первый шинный формирователь соединен с входной шиной данных блока памяти, а адресный вход - с вторым выходом первого счетчика, соединенным через второй шинный формирователь с входной шиной адреса блока памяти, выход сигнала Конец преобразования АЦП соединен с первыми входами второго, третьего, четвертого элементов И, шиной Запись блока памяти, и через первый элемент НЕ - с первым входом пятого элемента И, шины Запись и Чтение блока памяти являются соответственно входами устройства для подключения к цифровой вычислительной машине и соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, через первый элемент задержки - со счетным входом счетчика адреса, а через второй элемент НЕ - с вторым входом пятого элемента И, третий вход которого соединен с выходом первого элемента И, выход первого элемента И соединен с вторым входом третьего элемента И и через третий элемент НЕ с вторым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ,

первый вход которого и первый вход третьего элемента ИЛИ соединены с выходом первого блока сравнения, второй вход которого соединен с выходом первого регистра,

информационный вход которого и информационный вход второго регистра являются шиной данных для подключения к цифровой вычислительной машине, входная адресная шина устройства соединена с входом де0 шифратора адреса, первый выход которого соединен с установочным входом первого регистра, выход первого триггера соединен с единичным входом третьего триггера, входами запуска цифроаналогового и аналого5 цифрового преобразователей и является входом запуска аналоговой вычислительной машины устройства, выход второго триггера соединен с нулевым входом третьего триггера, вторыми входами второго и третьего

0 элементов ИЛИ, первым входом пятого элемента ИЛИ и является установочным выходом устройства для подключения аналоговой вычислительной машины, выход третьего триггера соединен с вторым вхо5 дом первого элемента И, выход пятого элемента ИЛИ соединен с установочным входом второго счетчика, а второй вход - с выходом второго блока сравнения, первый и второй входы которого соединены с выхо0 дами второго счетчика и второго регистра, второй выход второго счетчика через третий шинный формирователь соединен с адресной шиной блока памяти и с адресным входом цифроаналоговоТо преобразователя,

5 информационный вход которого через шестой шинный формирователь соединен с выходной шиной данных блока памяти, а выход является информационным выходом для подключения аналоговой вычислитель0 ной машины, выход с четчика адреса через четвертый шинный формирователь, управляющим входом, соединенным с выходом первого элемента ИЛИ, соединен с адресной шиной блока памяти, выход третьего

5 элемента ИЛИ - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход подключен к шине прерывания цифровой вычислительной машины, выход

0 третьего элемента И соединен с управляю- щими входами первого и второго шинных формирователей, входная и выходная шина данных блока памяти через пятый и седьмой шинные формирователи, управляющими

5 входами, соединенными с шинами Запись и Чтение ЦВМ, соединены с входной и выходной шинами данных устройства, введены регистр адреса пользователя, дополнительные элементы И. ИЛИ. НЕ, регистр клавиатуры, шифратор и дешифратор пользователя, три шинных формирователя, устройство индикации, причем регистр адреса пользователя соединен через девятый шинный формирователь с шиной адреса блока памяти, выходная шина данных блока памяти через десятый шинный формирователь и дешифратор соединена с устройством индикации данных пользователя, первый вход десятого шинного формирователя соединен с выходом седьмого элемента И, первые входы шестого и седьмого элемента И соединены с выходом пятого элемента И, а вторые входы - с кнопками Запись и Чтение пользователя соответственно, выход Седьмого элемента И соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, а выход - с управляющим входом девятого шинного формирователя, сигналы Запись и Чтение пользователя через четвертый и пятый элементы НЕ соединены с первым и вторым входами восьмого элемента И, третий вход которого соединен с выходом пятого элемента И,а выход - с шиной Чтение блока памяти, с управляющими входами третьего и шестого шинных формирователей и через второй элемент задержки - со счетным входом второго счетчика, второй выход дешифратора адреса соединен с установочным входом второго регистра, третий - с R-входом второго триггера и S-входом первого триггера, а четвертый выход - с R-входом первого и S-входом второго триггера, выход седьмого элемента ИЛИ - с установочным входом счетчика адреса, а входы - с выходом первого блока сравнения и вторым выходом дешифратора.

Клавиатура пользователя через шифратор соединена с регистром адреса пользователя и через восьмой шинный формирователь с шиной данных блока памяти, второй вход восьмого шинного формирователя соединен с выходом шестого элемента И, первый вход девятого элемента И соединен с кнопкой Запись адреса пользователя, второй вход - с выходом пятого элемента И, а выход - с управляющим входом регистра адреса пользователя, выходы седьмого и шестого элементов И соединены с шинами Чтение и Запись блока памяти.

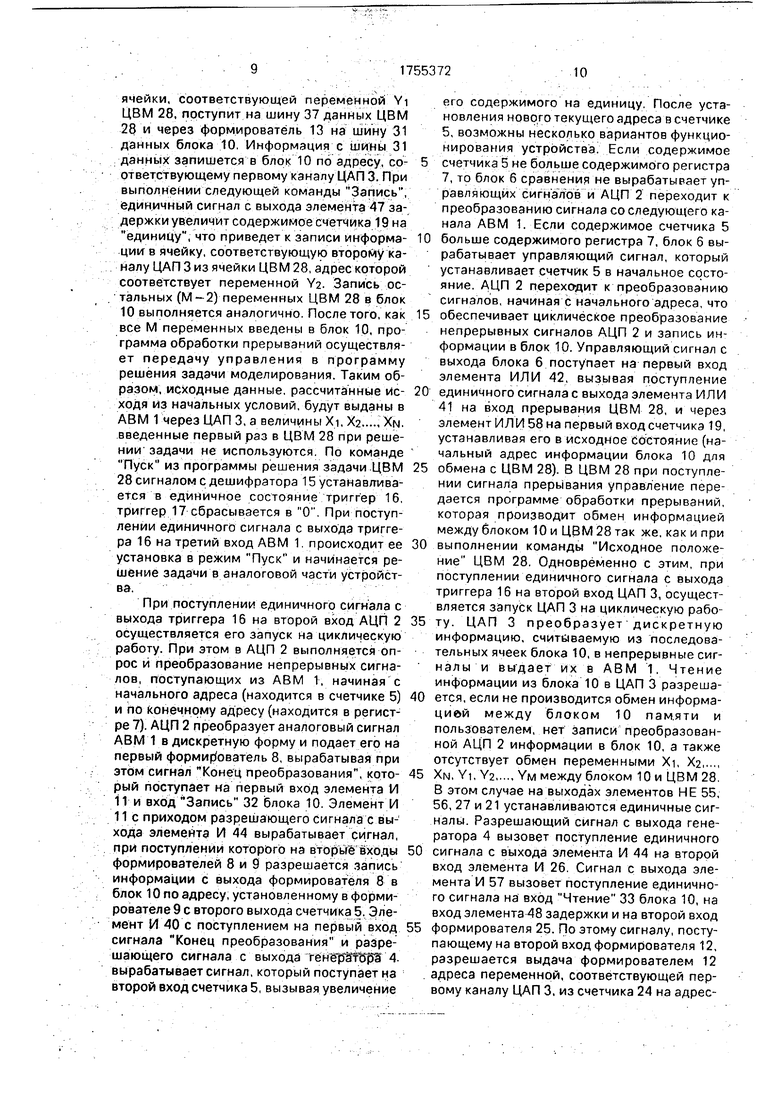

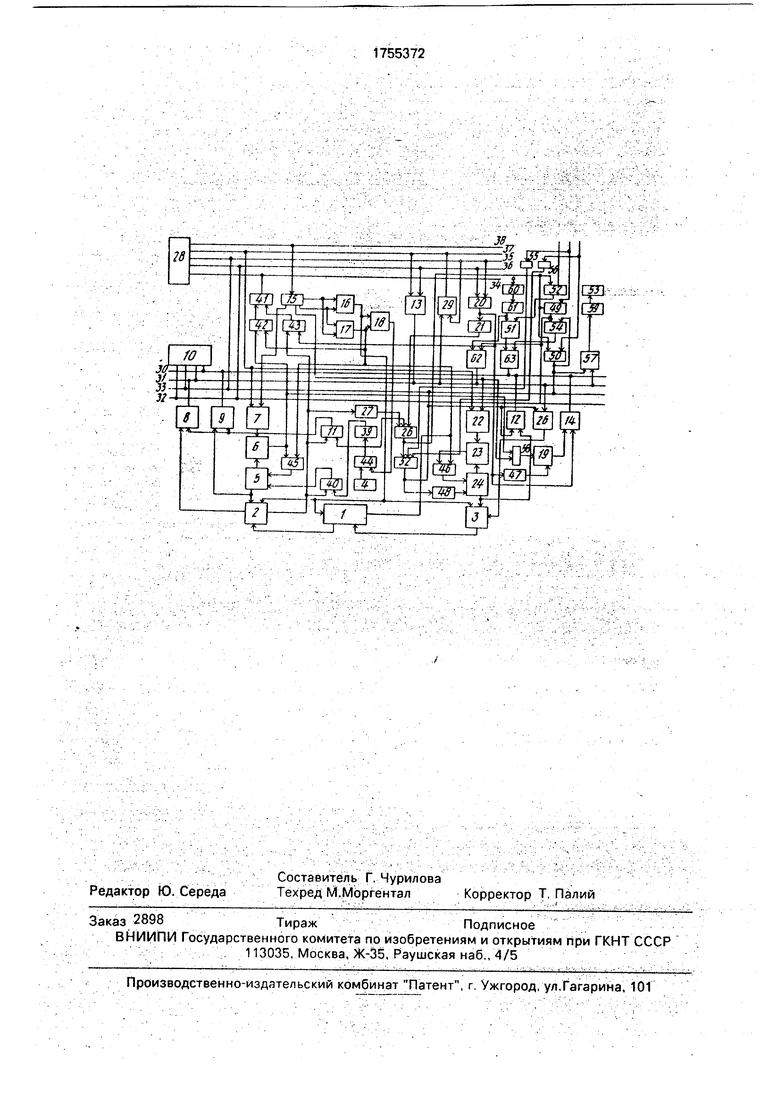

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами содержит АВМ1, аналого- цифровой преобразователь 2, цифроаналоговый преобразователь 3, генератор 4 тактовых импульсов, первый счетчик 5, первый блок 6 сравнения, первый

регистр 7, первый шинный формирователь 8, второй шинный формирователь 9, блок 10 памяти, третий элемент И 11, третий шинный формирователь 12, седьмой шинный формирователь 13, четвертый шинный формирователь 14, дешифратор 15 адреса, первый триггер 16, второй триггер 17, третий триггер 18, счетчик 19 адреса, первый элемент ИЛИ 20, второй элемент НЕ 21, второй

0 регистр 22, второй блок 23 сравнения, второй счетчик 24, шестой шинный формирова- тель 25, пятый элемент И 26, первый элемент НЕ 27, цифровую вычислительную машину 28, пятый шинный формирователь

5 29, адресную шину 30, шину данных 31, входы Запись 32 и Чтение 33 блока памяти, выходы Прерывание 34, Чтение 35, Запись 36, шины данных 37 и адреса 38 ЦВМ, третий элемент НЕ 39, второй элемент И 40,

0 четвертый элемент ИЛИ 41, третий элемент ИЛИ 42, четвертый элемент И 43, первый элемент И 44, второй элемент ИЛИ 45, пятый элемент ИЛИ 46, первый элемент 47 задержки, второй элемент 48 задержки, ше5 стой элемент И 49, седьмой элемент И 50, регистр 51 адреса.девятый элемент И 52, индикатор 53 данных пользователя, шестой элемент ИЛИ 54, четвертый 55 и пятый 56 элементы НЕ, восьмой элемент И 57, седь0 мой элемент ИЛИ 58, дешифратор 59, клавиатуру 60 пользователя, шифратор 61, восьмой 62 и девятый 63 шинные формирователи, десятый шинный формирователь 64 На чертеже указаны также входные сигналы

5 от кнопок пользователя.

Устройство работает следующим образом

При отладке аналого-цифровых задач, а также при проведений экспериментов с ана0 лого-цифровой моделью в режиме реального времени необходимо изменять данные и программы цифровой и аналоговой части, В случае, если аналоговый процессор не автоматизирован, коррекция аналоговой схемы

5 производится пользователем вручную В противном случае все изменения в аналоговом процессоре производятся под управлением программы, запускаемой пользователем в цифровой части, каждый

0 раз, когда требуется изменить параметры либо цифровой, либо аналоговой части задачи. Запуск такой программы вызывает прерывание программы цифровой части решения, запоминание словосостояния,

5 внесение изменений в данные и программу цифровой части и, если это необходимо, под управлением соответствующей программы через устройство обмена информации, в данные аналогового процессора. Аналогично производится и отображение затребованной пользователем информации о решении в цикле. Для корректировки решаемой задачи (выполнения запроса пользователя) требуется прервать цикл реального времени моделирования и затратить время цифрового процессора на ввод и преобразование информации от пользователя В предлагаемом техническом решении ввод-вывод информации от пользователя и в цифровую и аналоговую часть осуществляется без прерывания цикла реального времени моделирования, причем время ручного набора выводимой информации совмещено с выполнением операций вычисления в цифровой части системы и операциями цифроанэлогового и аналого-цифрового преобразования в устройстве обмена. На этапе подготовки исходная задача разделяется одним из известных способов на две части, одна из которых предназначена для решения на аналоговой (АВМ 1), а другая - на цифровой части устройства (ЦВМ 28). Связь между переменными в решаемой задаче осуществляется по каналам ЦАП 3 и АЦП 2. Пусть при решении задачи АВМ передаются переменные Yi.

Y2Ymi из ЦВМ 28, а из АВМ 1 в ЦВМ 28

переменные Xi,X2ХП1. В ЦВМ 28 вводится программа цифровой части задачи, в которой определено количество каналов цифроаналогового преобразования Mt, a также программа обработки прерываний, под управлением которой производится обмен информацией между памятью 10 и ЦВМ 28. В соответствии с этим первые N гц+П2 ячеек БП10 отводятся для хранения гн результатов преобразования с 1 по N-й канал АЦП 2 и П2 результатов ввода информации от пользователя, а следующие (N+1) -(N+M) ячеек БП 10 отводятся для хранения данных, предназначенных для выдачи с 1 по Mi канал ЦАП 3 и ГП2 ячеек данных, предназначенных для индикации пользователю (М

- ГТМНЛ2).

Программа аналоговой части вводится в АВМ 1. В начале программы решения задачи по командам ЦВМ 28 в регистры 7 и 22 записываются конечные адреса обмена, равные значению начального адреса, увеличенному на величину М, для каналов ЦАП и N для каналов АЦП, а также производится начальная установка счетчика 19 (начальный адрес обмена блока 10 с ЦВМ 28). По команде цифровой части задачи исходное положение дешифратор 15 вырабатывает сигнал Исходное положение, устанавливающий триггер 17 в единичное состояние. Сигнал с выхода триггера 17, поступая на

второй вход элемента ИЛИ 45, вызовет поступление с его выхода единичного сигнала на вход счетчика 5, устанавливая его в начальное состояние (начальный адрес аналого-цифрового преобразования) и на второй вход АВМ 1, устанавливая ее в режим Исходное положение, Единичный сигнал с выхода триггера 17, поступая на первый вход элемента ИЛИ 46, вызовет поступление с

его выхода единичного сигнала на вход счетчика 24, устанавливая его начальное состояние (начальный адрес цифроаналогового преобразования). Единичный сигнал с выхода триггера 17, поступив на второй вход

элемента ИЛИ 42, вызовет поступление единичного сигнала с выхода элемента ИЛИ 41 на вход прерывания ЦВМ 28. При этом в блоке 28 управление передается программе обработки прерываний. При обмене информацией на первом этапе производится чтение N переменных Xi, X2,... XN из блока 10 в ЦВМ 28, з на втором этапе - запись М переменных i i, YaYM из ЦВМ 28 в блок 10.

На первом этапе при выполнений команды

Чтение в ЦВМ 28 программой обработки прерываний сигнал с выхода Чтение 35 ЦВМ 28 вызовет поступление единичного сигнала е выхода элемента ИЛИ 20 на вход элемента 47 задержки и второй шинный

формирователь 14 и разрешит поступление начального адреса счетчика 19 на адресную шину блока 10. По сигналу Чтение ЦВМ 28, поступающему на вход Чтение блока 10, информация из ячейки, соответствующей

первому каналу АЦП 2, поступит на шину 31 данных блока 10 и через узел 29 на шину 37 ЦВМ 28. Информация с шины данных заносится в ЦВМ 28 по адресу, соответствующему переменной XL При выполнении

следующей команды Чтение единичный сигнал с выхода элемента 47 увеличит содержимое счетчика 19 на единицу, что приведет к чтению информации из ячейки, соответствующей второму каналу АЦП 2, и

записи ее в ЦВМ 28 по адресу, соответствующему переменной Xz. Чтение остальных N- - 2 переменных из блока 10 в ЦВМ 28 выполняется аналогично. После того, как все N переменных введены в ЦВМ 28, программа

обработки прерываний начинает запись переменных Yi, YaYm в блок 10. При этом

сигнал с выхода Запись ЦВМ 28 вызовет поступление единичного сигнала с элемента ИЛИ 20 на вход элемента 47 задержки и

второй вход формирователя 14 и разрешит поступление адреса переменной Yi из счетчика 19 на адресную шину 30 блока 10 По сигналу Запись ЦВМ 28, поступающему на вход Запись 32 блока 10, информация из

ячейки, соответствующей переменной YI ЦВМ 28, поступит на шину 37 данных ЦВМ 28 и через формирователь 13 на шину 31 данных блока 10. Информация с шины 31 данных запишется в блок 10 по адресу, со- ответствующему первому каналу ЦАП 3. При выполнении следующей команды Запись, единичный сигнал с выхода элемента 47 задержки увеличит содержимое счетчика 19 на единицу, что приведет к записи информа- ции в ячейку, соответствующую второму каналу ЦАП 3 из ячейки ЦВМ 28, адрес которой соответствует переменной Y2. Запись остальных (М -2) переменных ЦВМ 28 в блок

10выполняется аналогично. После того, как все М переменных введены в блок 10, программа обработки прерываний осуществляет передачу управления в программу решения задачи моделирования. Таким образом, исходные данные, рассчитанные ис- ходя из начальных условий, будут выданы в

АВМ 1 через ЦАП 3, а величины Xi, X2XN.

введенные первый раз в ЦВМ 28 при решении задачи не используются. По команде Пуск из программы решения задачи ЦВМ 28 сигналом с дешифратора 15 устанавливается в единичное состояние триггер 16, триггер 17 сбрасывается в О. При поступлении единичного сигнала с выхода триггера 16 на третий вход АВМ 1 происходит ее установка в режим Пуск и начинается решение задачи в аналоговой части устройства.

При поступлении единичного сигнала с выхода триггера 16 на второй вход АЦП 2 осуществляется его запуск на циклическую работу. При этом в АЦП 2 выполняется опрос и преобразование непрерывных сигналов, поступающих из АВМ 1, начиная с начального адреса (находится в счетчике 5) и по конечному адресу (находится в регистре 7). АЦП 2 преобразует аналоговый сигнал АВМ 1 в дискретную форму и подает его на первый формирователь 8, вырабатывая при этом сигнал Конец преобразования, кото- рый поступает на первый вход элемента 1/1

11и вход Запись 32 блока 10. Элемент И 11с приходом разрешающего сигнала с выхода элемента И 44 вырабатывает сигнал, при поступлении которого на вторые входы формирователей 8 и 9 разрешается запись информации с выхода формирователя 8 в блок 10 по адресу, установленному в формирователе 9 с второго выхода счетчика 5. Элемент И 40 с поступлением на первый вход сигнала Конец преобразования и разрешающего сигнала с выхода ген ф1Шр1 4. вырабатывает сигнал, который поступает на второй вход счетчика 5, вызывая увеличение

его содержимого на единицу. После установления нового текущего адреса в счетчике 5, возможны несколько вариантов функционирования устройства. Если содержимое счетчика 5 не больше содержимого регистра 7, то блок б сравнения не вырабатывает управляющих сигналов и АЦП 2 переходит к преобразованию сигнала со следующего канала АВМ 1. Если содержимое счетчика 5 больше содержимого регистра 7, блок 6 вырабатывает управляющий сигнал, который устанавливает счетчик 5 в начальное состояние. АЦП 2 переходит к преобразованию сигналов, начиная с начального адреса, что обеспечивает циклическое преобразование непрерывных сигналов АЦП 2 и запись информации в блок 10. Управляющий сигнал с выхода блока 6 поступает на первый вход элемента ИЛИ 42, вызывая поступление единичного сигнала с выхода элемента ИЛИ 41 на вход прерывания ЦВМ 28, и через элемент ИЛИ 58 на первый вход счетчика 19, устанавливая его в исходное состояние (начальный адрес информации блока 10 для обмена с ЦВМ 28). В ЦВМ 28 при поступлении сигнала прерывания управление передается программе обработки прерываний, которая производит обмен информацией между блоком 10 и ЦВМ 28 так же, как и при выполнении команды Исходное положение ЦВМ 28. Одновременно с этим, при поступлении единичного сигнала с выхода триггера 16 на второй вход ЦАП 3, осуществляется запуск ЦАП 3 на циклическую работу. ЦАП 3 преобразует дискретную информацию, считываемую из последовательных ячеек блока 10, в непрерывные сигналы и выдает их в АВМ 1. Чтение информации из блока 10 в ЦАП 3 разрешается, если не производится обмен информацией между блоком 10 памяти и пользователем, нет записи преобразованной АЦП 2 информации в блок 10, а также

отсутствует обмен переменными Xi, Ха

XN, Yi, Y2YM между блоком 10 и ЦВМ 28

В этом случае на выходах элементов НЕ 55, 56, 27 и 21 устанавливаются единичные сигналы. Разрешающий сигнал с выхода генератора 4 вызовет поступление единичного сигнала с выхода элемента И 44 на второй вход элемента И 26. Сигнал с выхода элемента И 57 вызовет поступление единичного сигнала на вход Чтение 33 блока 10, на вход элемента 48 задержки и на второй вход формирователя 25. По этому сигналу, поступающему на второй вход формирователя 12, разрешается выдача формирователем 12 адреса переменной, соответствующей первому каналу ЦАП 3, из счетчика 24 на адресную шину 30 блока 10 Информация из ячейки блока Ю, соответствующей переменной, передаваемой по первому каналу ЦАП 3, поступит на шину 31 данных блока 10 и на первый вход формирователя 25, откуда затем поступает на третий вход ЦАП 3. При поступлении следующего разрешающего сигнала с генератора 4 единичный сигнал с выхода элемента 48 задержки увеличит содержимое счетчика 24 на 1, что приводит к чтению информации из ячейки, соответствующей второму каналу ЦАП 3. Увеличение содержимого счетчика 24 будет происходить до тех пор, пока оно на станет больше содержимого регистра 22. В этом случае блок 23 сравнения вырабатывает единичный сигнал, который, поступив на первый вход счетчика 24, установит его в начальное состояние. При появлении очередного сигнала с выхода генератора 4 снова произойдет чтение информации из ячейки, соответствующей первому каналу ЦАП 3. Таким образом обеспечивается циклическая работа ЦАП 3,

В устройстве операции цифроаналого- вого преобразования не выполняются в случае, если производится обмен информацией между блоком 10 и ЦВМ 28 В этом случае единичные сигналы с выходов Чтение 35 или Запись 36 ЦВМ 28, поступив соответственно на первый и второй входы элемента ИЛИ 20, вызовут появление сигнала нулевого уровня на выходе элемента И 25 независимо от сигналов на первом и втором его входах. Сигнал с выхода элемента И 57, поступив на вторые входы формирователей 12 и 25, запрещает чтение информации с блока 10 в ЦАП 3. По этому же сигналу во время обмена информацией между блоком 10 и ЦВМ 28 содержимое счетчика 24 не увели чивается. Послгз окончания обмена между блоком 10 и ЦВМ 28 цифроэналоговое преобразование продолжится. Работа ЦАП 3 приостанавливается также при записи преобразованной АЦП 2 информации в блок 10. В этом случае запрещающий сигнал на выходе элемента И 26 появятся вследствие поступления инвертированного элементом НЕ 27 единичного сигнала Конец преобразования с первого выхода АЦП 2. Сигнал Конец преобразования, поступив на первый вход элемента И 43, в случае наличия единичного сигнала на втором его входе (свидетельствующего что производится обмен информацией между блоком 10 и ЦВМ 28), вызовет поступление единичного сигнала на второй вход элемента ИЛИ 41 и на вход Прерывание ЦВМ 28. По сигналу прерывания ЦВМ 28 начинает выполнять программу обработки прерываний, которая, определив по взведенному признаку повторного входа, что происходит обмен информацией между блоком 10 и ЦВМ 28,

организует задержку в обмене очередной информацией на время записи информации из АЦП 2 в блок 10. Сигнал Конец преобразования не вызовет прерывания работы ЦВМ 28, если обмен информацией между

блоком 10 и ЦВМ 28 не происходит (с выходов Чтение 35 и Запись 36 ЦВМ 28 поступают сигналы нулевого уровня на второй вход элемента И 43, запрещая прохождение единичного сигнала Конец преобразования на выход элемента И 43).

Запись данных клавишного регистра пользователя 60 в блок 10 осуществляется по адресу, записанному в регистр 51 адреса пользователя. Данные, считываемые из блока 10, высвечиваются на устройстве индикации данных пользователя. Чтение или запись информации пользователем разрешено, когда нет обмена информацией между блоком 10 и ЦВМ 28 и не производится

запись преобразованных АЦП 2 данных в блок 10 (с выхода элемента И 26 поступает запрещающий сигнал на элементы И 52, 49 и 50).

В конце программы решения задачи моделирования выдается команда Исходное положение, которая, поступив с выхода дешифратора 15 на триггеры 16 и 17, переводит устройство в исходное состояние.

Ввод-вывод информации пользователем в ЦВМ 28 и АВМ 1 осуществляется через блок 10 памяти. Для ввода информации а БП пользователь набирает адрес необходимой ячейки блока 10 памяти на клавишном регистре 60, который через шифратор 61 при

наличии разрешающего сигнала на выходе схемы И 52 заносится в регистр 51 адреса. После этого пользователь набирает на клавишном регистре требуемую информацию, которая через шифратор 61 поступает на

восьмой шинный формирователь 62. При нажатии пользователем кнопки Запись (ЗпД), единичный сигнал с выхода шестого элемента И 49 разрешит прохождение информации на шину 31 данных БП. Одновременно с этим единичный сигнал с выхода шестого элемента ИЛИ 54 вызовет прохождение адреса с девятого шинного формирователя 63 на шину адреса БП 30 и единичного сигнала на шину Запись БП

32. Чтение информации из БП 10 происходит аналогично. В этом случае информация из регистра адреса пользователя 61 поступает на шину адреса БП 30 при нажатии на кнопку Чтение (ЧтД). Появление единичного сигнала на выходе седьмого элемента И 50 разрешит чтение информации из БП 10. Через десятый шинный формирователь 64 данные, считанные из БП, поступают на дешифратор 59 и затем на устройство 60 инди- кации.i

Пользователь имеет доступ к любой ячейке БП при чтении, однако при записи данных в БП 10 он должен использовать лишь те ячейки, которые не участвуют в ана- лого-цифровом и цифроаналоговом обмене.

Введение пользователя в контур решения задачи позволяет производить с его сто- роны дополнительный контроль и диагностику прохождения аналого-цифрового моделирования

Индикация информации в цикле реального времени без прерывания аналого-цифровой задачи позволяет пользователю осуществлять контроль правильности решения, а также позволяет принять решение по дальнейшему плану исследования Возможность ввода информации в цифровую и аналоговую часть системы4 позволяет моделировать человеко-машинные системы (тренажеры), где пользователь управляет объектом в реальном времени. Дополнительно система для обмена информацией может осуществлять в автономном режиме контроль, в том числе и динамический, АВМ 1.

Формула изобретения

Устройство для обмена информацией между аналоговой и цифровой вычислитель- ными машинами, содержащее цифроанало- говый преобразователь, генератор тактовых импульсов, блок памяти, дешифратор адреса, первый, второй и третий триггеры, два регистра, два счетчика, счетчик адреса, два блока сравнения, шинные формирователи, с первого по седьмой элементы И, НЕ, задержки, элементы ИЛИ, с первого по пятый, аналого-цифровой преобразователь, информационный вход которого подключен к выходу аналоговой вычислительной машины, выход генератора тактового импульса соединен с первым входом первого элемента И, первый вход первого блока сравнения соединен с первым выходом первого счетчи- ка, информационные выходы аналого-цифрового преобразователя через первый шинный формирователь соединены с входами-выходами данных блока памяти, а адресный вход - с вторым выходом первого счетчика и через второй шинный формирователь - с входами-выходами адреса блока памяти, выход сигнала Конец преобразования аналого-цифрового преобразователя

соединен с первыми входами второго, третьего, четвертого элементов И, входом- выходом Запись блока памяти и через первый элемент НЕ - с первым входом пятого элемента И, входы-выходы Запись и Чтение блока памяти соединены соответственно с первым и вторым выходами цифровой вычислительной машины и объединены с первым и вторым входами первого элемента ИЛИ соответственно, выход которого соединен с вторым входом четвертого элемента И, через первый элемент задержки - со счётным входом счетчика адреса, а через второй элемент НЕ -с вторым входом пятого элемента И, третий вход которого соединен с выходом первого элемента И, выход которого соединен с вторым входом третьего элемента И и через третий элемент НЕ - с вторым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ, первый вход которого и первый вход третьего элемента ИЛИ соединены с выходом первого блока сравнения, второй вход которого соединен с выходом первоТд р ёТиБграГйнфо рмацион- ный вход которого и информационный вход второго регистра подключены к треть&иу выходу цифровой вычислительной машины, четвертый выход которой соединен с входом дешифратора адреса, первый выход которого соединен с установочным входом первого регистра, выход первого триггера соединен с единичным входом третьего триггера, входами запуска цифроаналогово- го и анэлогб-цифрового преобразователей и аналоговой вычислительной машины, выход второго триггера соединен с нулевым входом третьего триггера, вторыми входами второго и третьего элементов ИЛИ, первым входом пятого элемента ИЛИ и установочным входом аналоговой вычислительной машины, выход третьего триггера соединен с вторым входом первого элемента И, выход пятого элемента ИЛИ соединен с установочным входом второго счетчика, а второй вход - с выходом второго блока сравнения, первый и второй входы которого соединены с первым выходом второго счетчика и выходом второго регистра соответственно, второй выход второго счетчика через третий шинный формирователь соединен с входами-выходами адреса блока памяти и с адресным входом цифроаналогового преобразователя, информационный вход которого через шестой шинный формирователь соединен с входами-выходами данных блока памяти, а выход соединен с информационным входом аналоговой вычислительной машины, выход счетчика адреса через четвертый шинный формирователь соединен с входами-выходами адреса блока памяти, выход третьего элемента ИЛИ - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, и выход подключен к пятому выходу цифровой вычислительной машины, выход третьего элемента И соеди- нен с управляющими входами гтёрЪого и второго шинных формирователей, входы-выходы данных блока памяти через пятый и седьмой шинные формирователи соединены с третьим выходом цифровой вы- числительной машины, управляющий вход четвертого шинного формирователя подключен к выходу первого элемента ИЛИ, а управляющие входы пятого и седьмого шинных формирователей соединены с соответ- ствующими первым и вторым выходами цифровой вычислительной машины, отличающееся тем, что, с целью сокращения времени ввода-вывода информации в цикле реального времени моделирования динами- ческих систем, в него введены регистр адреса, с шестого по девятый элементы И, шестой и седьмой элементы ИЛИ, четвертый и пятый элементы НЕ, регистр клавиатуры, шифратор и дешифратор, восьмой, девятый и десятый шинные формирователи, второй элемент задержки и устройство индикации, причем выход регистрации адреса соединен через девятый шинный формирователь с входами-выходами адреса блока памяти, входы-выходы данных блока памяти через десятый шинный формирователь и дешифратор соединены с входом устройства индикации, управляющий вход десятого шинного формирователя соединен с выхо- дом седьмого элемента И, первый входы шестого и седьмого элементов И объединены и соединены с выходом пятого элемента И, а вторые входы являются соответственно шинами Запись и Чтение, выход седьмого элемента И соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, с выход - с управляющим входом девятого шинного формирователя, шины Запись и Чтение через четвертый и пятый элементы НЕ соответственно соединены с первым и вторым входами восьмого элемента И, третий вход которого соединен с выходом пятого элемента И, а выход - с входами-выходами Чтение блока памяти, с управляющими входами третьего и шестого шинных формирователей и через второй элемент задержки - со счетным входом второго счетчика, второй выход дешифратора адреса соединен с установочным входом второго регистра, третий - с S-входом первого триггера и R-входом второго триггера и четвертый выход - с R-входом первого и S-входом второго триггера, выход седьмого элемента ИЛИ соединен с установочным входом счетчика адреса, а первый и второй входы - с выходом первого блока сравнения и вторым выходом дешифратора соответственно, причем регистр клавиатуры через шифратор соединен с входом регистра адреса, который через восьмой шинный формирователь соединен с входами-выходами данных блока памяти, управляющий вход восьмого шинного формирователя соединен с выходом шестого элемента И, первый вход девятого элемента И является шиной Запись адреса, второй вход соединен с выходом пятого элемента И, а выход - с управляющим входом регистра адреса, выходы седьмого и шестого элементов И соединены с входами-выходами Чтение и Запись блока памяти соответственно,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для связи аналоговой и цифровых вычислительных машин | 1983 |

|

SU1140135A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

Изобретение относится к аналого-цифровой вычислительной технике и может быть использовано при моделировании динамических систем в реальном времени, а также создании тренажеров и систем полунатурного моделирования. В устройство для обмена информацией между цифровой 28 и аналоговой 1 вычислительными машинами, содержащее аналого-цифровой преобразователь 2, цифроаналоговый преобразователь 3, генератор тактовых импульсов 4, блок памяти 10, дешифратор адреса 15, три триггера 16-18, два регистра 7 и 22, счетчики 5 и 24, два блока сравнения 6 и 23, шинные формирователи 8, 9, 12,13, 14, 25 и 29, элементы И, ИЛИ, НЕ, задержки 11, 20, 21, 26, 27, 39-50, счетчик адреса 19, с целью сокращения времени ввода-вывода информации в цикле реального времени моделирования динамических систем введены регистры адреса 51 и клавиатуры 60, шифратор 61 и дешифратор 59, устройство индикации 53 и дополнительно элементы И, ИЛИ, НЕ 52, 54-57, 58 и шинные формирователи 62-64. 1 ил. (Л С

| Устройство для сопряжения аналоговой и цифровой вычислительных машин | 1979 |

|

SU858022A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1990-01-02—Подача