4;аь

00

Изобретение относится к вычислительной технике и может быть использовано для моделирования систем сбора, передачи и обработки данных.

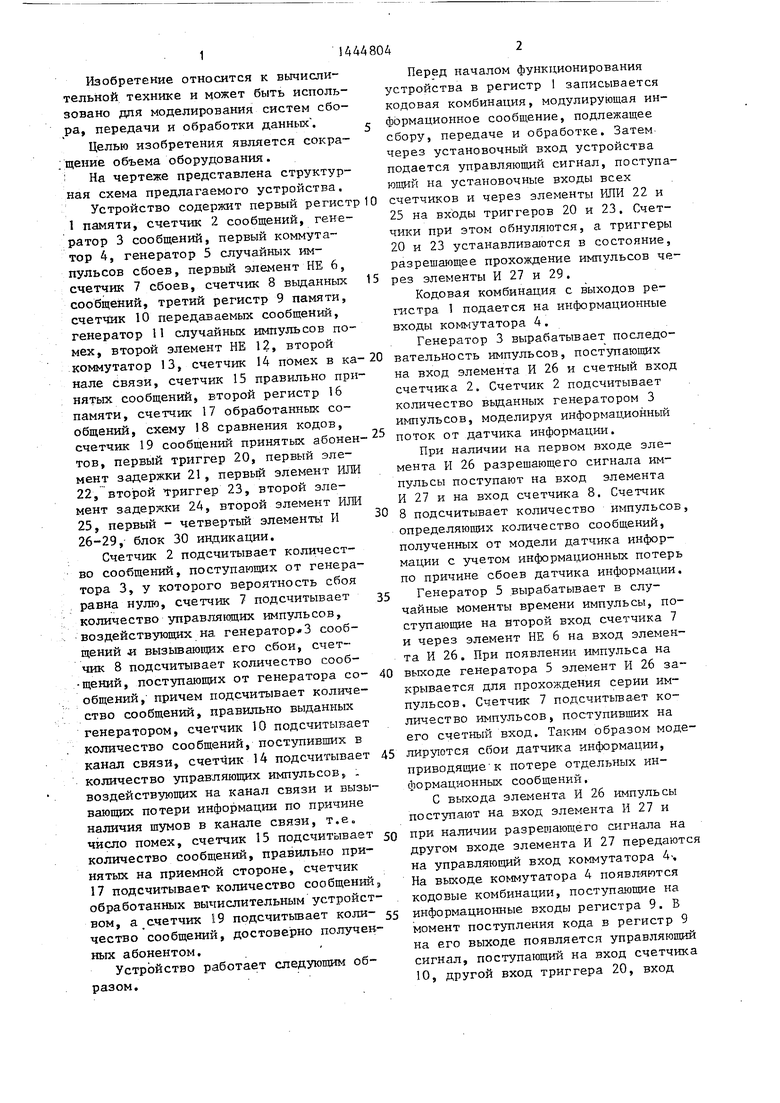

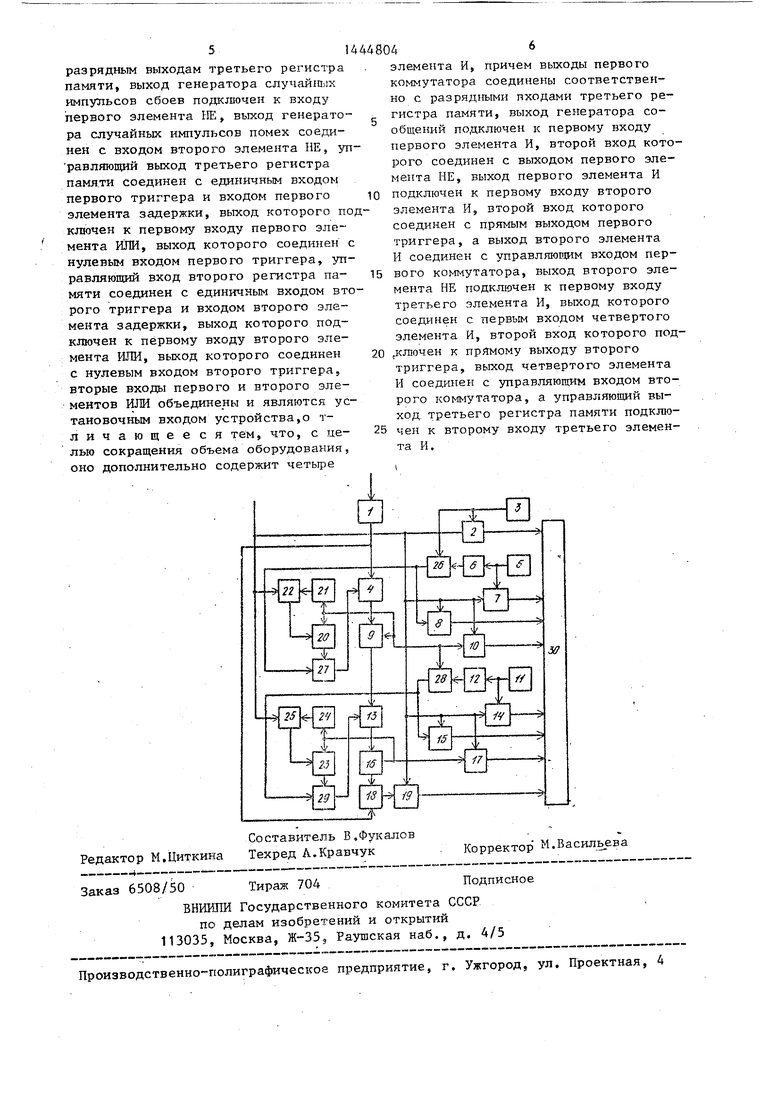

Целью изобретения является сокра- ;щение объема оборудования. На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит первый регист 1 памяти, счетчик 2 сообщений, генератор 3 сообщений, первый коммутатор 4, генератор 5 случайных импульсов сбоев, первый элемент НЕ 6, счетчик 7 сбоев, счетчик 8 вьщанных сообщений, третий регистр 9 памяти, счетчик 10 передаваемых сообщений, генератор 11 случайных импульсов помех, второй элемент НЕ 12, второй коммутатор 13, счетчик 14 помех в ка нале связи, счетчик 15 правильно принятых сообщений, второй регистр 16 памяти, счетчик 17 обработанных сообщений, схему 18 сравнения кодов, счетчик 19 сообщений принятых абонен тов, первый триггер 20, первый элемент задеряски 21 , первый элемент ИЛИ 22, второй триггер 23, второй элемент задержки 24, второй элемент ИЛИ 25, первый - четвертый элементы И 26-29, блок 30 ин,дикации.

Счетчик 2 подсчитывает количество сообщений, поступающих от генератора 3, у которого вероятность сбоя равна нулю, счетчик 7 подсчитывает количество управляющих импульсов, воздействующих на генератор 3 сообщений « вызьшающих его сбои, счетчик 8 подсчитывает количество сооб- щений, поступающих от генератора со- общений, причем подсчитывает количество сообщений, правильно выданных генератором, счетчик 10 подсчитывает количество сообщений, поступивших в канал связи, счетчик 14 подсчитывает количество управляющих импульсов, . воздействующих на канал связи и вызывающих потери информад1ш по причине наличия шумов в канале связи, т.е. число помех, счетчик 15 подсчитывает количество сообщений, правильно принятых на приемной стороне, счетчик 17 подсчитывает количество сообщений обработанных вычислительным устройством, а счетчик 19 подсчитывает коли- чество сообщений, достоверно полученных абонентом.

Устройство работает следующим образом.

Перед началом функционирования устройства в регистр 1 записывается кодовая комбинация, модулирующая информационное сообщение, подлежащее сбору, передаче и обработке. Затем- через установочный вход устройства подается управляющий сигнал, поступающий на установочные входы всех счетчиков и через элементы ИЛИ 22 и 25 на входы триггеров 20 и 23. Счетчики при этом обнуляются, а триггеры 20 и 23 устанавливаются в состояние, разрещающее прохождение импульсов через элементы И 27 и 29.

Кодовая комбинация с выходов регистра 1 подается на информационные входы коммутатора 4.

Генератор 3 вырабатывает последовательность импульсов, поступающих на вход элемента И 26 и счетный вход счетчика 2. Счетчик 2 подсчитывает количество выданных генератором 3 импульсов, моделируя информационный поток от датчика информации.

При наличии на первом входе элемента И 26 разрешающего сигнала импульсы поступают на вход элемента И 27 и на вход счетчика 8, Счетчик В подсчитывает количество импульсов определяющих количество сообщений, полученных от модели датчика информации с учетом информационных потерь по причине сбоев датчика информации.

Генератор 5 вырабатывает в случайные моменты времени импульсы, поступающие на второй вход счетчика 7 и через элемент НЕ 6 на вход элемента И 26 . При появлении импульса на выходе генератора 5 элемент И 26 закрывается для прохождения серии импульсов. Счетчик 7 подсчитывает количество импульсов, поступивших на его счетный вход. Таким образом моделируются сбои датчика информации, приводящие К потере отдельных информационных сообщений.

С выхода элемента И 26 импульсы поступают на вход элемента И 27 и при наличии разрешающего сигнала на другом входе элемента И 27 передаютс на управляющий вход коммутатора 4-. На выходе коммутатора 4 появляются кодовые комбинации, поступающие на информационные входы регистра 9. В момент поступления кода в регистр 9 на его выходе появляется управляющий сигнал, поступающий на вход счетчика 10, другой вход триггера 20, вход

элемента задержки 21 и другой вход элемента И 28. Триггер при этом устанавливается в состояние О, закрывая прохождение последующих импульсов через элемент И 27 на время определяемое временем задержки элемента задержки 21 (оно задается исходя из пропускной способности канала связи). Через время задержки импульс с выхода элемента задержки 21 через элемент ИЛИ 22 поступает на вход триггера 20, который устанавливается в состояние, разрешающее прохождение импульсов через элемент И 27. Таким образом моделируются информационные потери на входе канала связи по причине образования очереди. Счетчик 10 подсчитывает количество импульсов, имитирующих передаваемые сообщения. Генератор II вырабатывает в случайные моменты времени импульсы, поступающие на вход счетчика 14 и через элемент НЕ 12 на вход элемента И 28. Счетчик 14 подсчитывает количество импульсов, по- ступив1чих с генератора. Б момент появления импульса на выходе генератора 11 прохождение импульсов через элемент И 28 запрещено. Тем самым моделируется процесс потери информации из-за шумов в канале.

При наличии на первом входе элемента И 28 разрещающего сигнала импульсы с его выхода поступают на вход элемента И 29 и на вход счетчика 15. Счетчик 15 подсчитывает количество импульсов, определяющих количество сообщений, правильно принятых на приемной стороне канала связи.

При наличии на первом входе элемента И 29 разрешающего сигнала импульсы с выхода поступают на ттравля ющий вход коммутатора 13, разрешая прохождение кодовой комбинации с информационных; выходов регистра 9 на информационные входы регистра 16. В момент поступления кода в регистр 16 на его выходе появляется управляющий сигнал, поступаюп1 1й на вход счетчи- ка 17, вход второго триггера 23 и вход элемента задержки 24. Триггер при этом устанавливается в состояние О, закрывая прохождение последующих импульсов через элемент И 29 на время, определяемое временем :задержки элемента задержки 24 (оно задается исходя из времени обработк информационного кода вычислительным

5

0

0

устройством). Через время задержки импульс с выхода элемента задержки 24 поступает через элемент ИЛИ 25 на первый вход триггера 23, который устанавливается в состояние, разрешающее прохождение последующих импульсов через элемент Н 29. Таким образом моделируются информационные потери на входе вычислительного устройства по причине образования очереди. Счетчик 17 подсчитывает количество импульсов, определяющих число обработанных сообщений.

С выхода регистра 16 сообщение поступает на первые входы схемы сравнения 18, на вторые входы которой поступает код с выхода регистра 1. Если коды совпали, то на выходе схемы сравнения 18 появляется импульс, поступающий на вход счетчика 19, Счетчик 19 подсчитывает количество импульсов , определяющих количество сообщений, которые не были искажены и 5 потеряны по тем или иным причинам в отдельных блоках вычислительного устройства системы сбора, передачи и обработки данных.

Вероятностные характеристики системы определяются известными методами по показаниям счетчиков.

Формула изобретения

Устройство для моделирования систем передачи и обработки данных, содержащее генератор сообщений, три регистра памяти, два коммутатора, , схему сравнения кодов, два триггера,

два элемента задержки, два элемента ИЛИ, генератор случайных импульсов сбоев, генератор случайных импульсов помех, два элемента НЕ, разрядные входы первого регистра памяти являются информационными входами устройства, разрядные выходы которого соединены соответственно с информационными входами первого коммутатора и с информационными входами первой группы схемы сравнения, выход Равно которой является выходом сообщений, принятых абонентом, а информационные входы второй группы схемы сравнения подключены соответственно к разрядным выходам второго регистра памяти, разрядные входы которого соединены соответственно с выxoдaмli второго коммутатора, информационные входы которого подключены соответственно к

разрядным выходам третьего регистра памяти, выход генератора случай1й1х импульсов сбоев по;рслючен к входу первого элемента ЬЕ, выход генератора случайных импульсов помех соединен с входом второго элемента НЕ, уп равляющий выход третьего регистра памя.ти соединен с единичным входом первого триггера и входом первого элемента задержки, выход которого поключен к первому входу первого элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, управляющий вход второго регистра памяти соединен с единичным входом второго триггера и входом второго элемента задержки, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с нулевым входом второго триггера, вторые входы первого и второго элементов ИЛИ объединены и являются установочным входом устройства,о т- личающее ся тем, что, с целью сокращения объема оборудования, оно дополнительно содержит четьфе

элемента И, причем выходы первого коммутатора соединены соответственно с разрядными входами третьего регистра памяти, выход генератора сообщений подключен к первому входу первого элемента И, второй вход которого соединен с выходом первого элемента НЕ, выход первого элемента И подключен к первому входу второго элемента И, второй вход которого соединен с прямым выходом первого триггера, а выход второго элемента И соединен с управляюпдам входом первого коммутатора, выход второго элемента НЕ подключен к первому входу третьего элемента И, выход которого соединен с первым входом четвертого элемента И, второй вход которого под- 0 лКлючен к прймому выходу второго

триггера, выход четвертого элемента И соединен с ут1равляющим входом второго коммутатора, а управляющий выход, третьего регистра памяти подключен к второму входу третьего элемента И.

5

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем передачи и обработки данных | 1983 |

|

SU1150629A1 |

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1151983A1 |

| Устройство для моделирования систем связи | 1990 |

|

SU1741148A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2011219C1 |

| Устройство для моделирования канала передачи данных | 1989 |

|

SU1624474A1 |

| Устройство для моделирования вычислительной системы | 1990 |

|

SU1786492A1 |

| Устройство для моделирования системы связи | 1984 |

|

SU1229770A1 |

| Устройство для моделирования систем связи | 1986 |

|

SU1365093A1 |

| Устройство для моделирования гибких производных систем | 1988 |

|

SU1631551A1 |

| Устройство для испытания логичес-КиХ блОКОВ | 1979 |

|

SU832565A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования работы систем сбора, передачи и обработки сообщений.. Цель изобретения - сокращение объема оборудования. Поставленная цель достигается введением в : устройство четырех элементов И, что позволило упростить известное устройство, моделирующее сбор сообщений, сбои датчиков сообщений, помехи при передаче и обработку сообщений на приемной стороне. 1 ил.

| Устройство для моделирования работыСиСТЕМы СВязи | 1979 |

|

SU805331A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем передачи и обработки данных | 1983 |

|

SU1150629A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-27—Подача