10

15

20

25

Изобретение относится к вычислиельной технике и электросвязи и моет использоваться в передатчиках цифовых систем передачи, использующих етод двустороннего стаффинга с двух- омйндным управлением.

Цель изобретения - упрощение устройства и повышение его надежности за счет совмещения функций асинхронного сопряжения и перезаписи информации на отводимые позиции канала связи в одном оперативном запоминающем блоке.

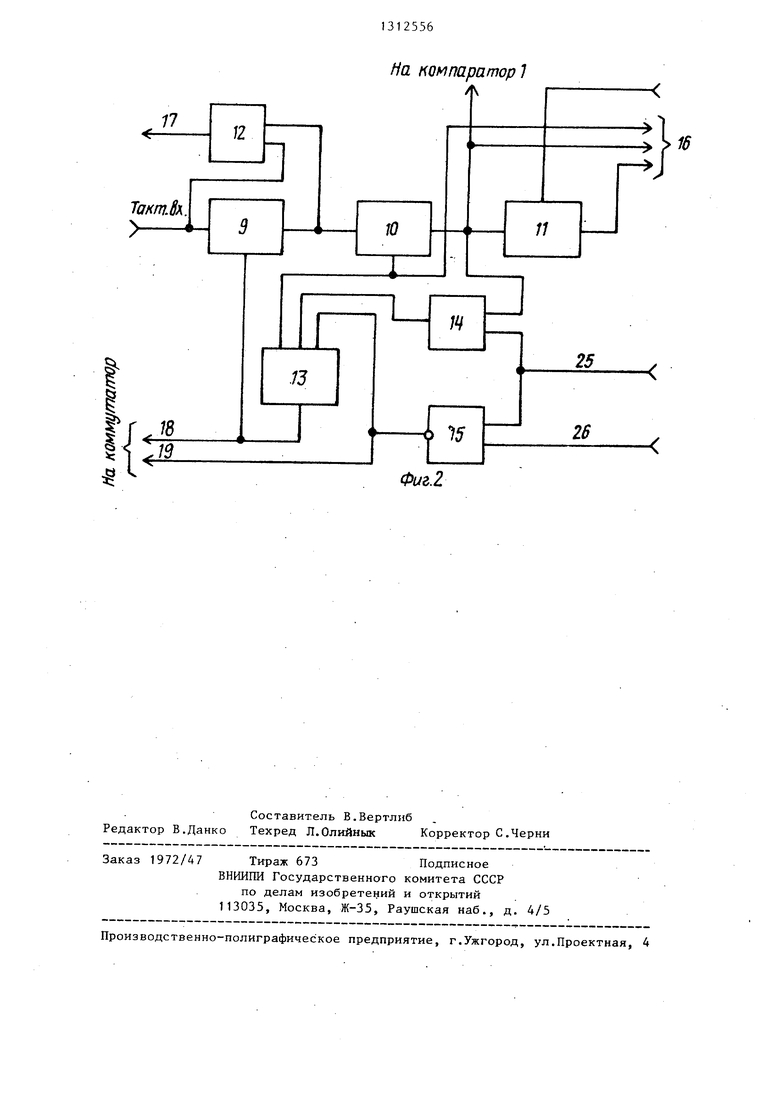

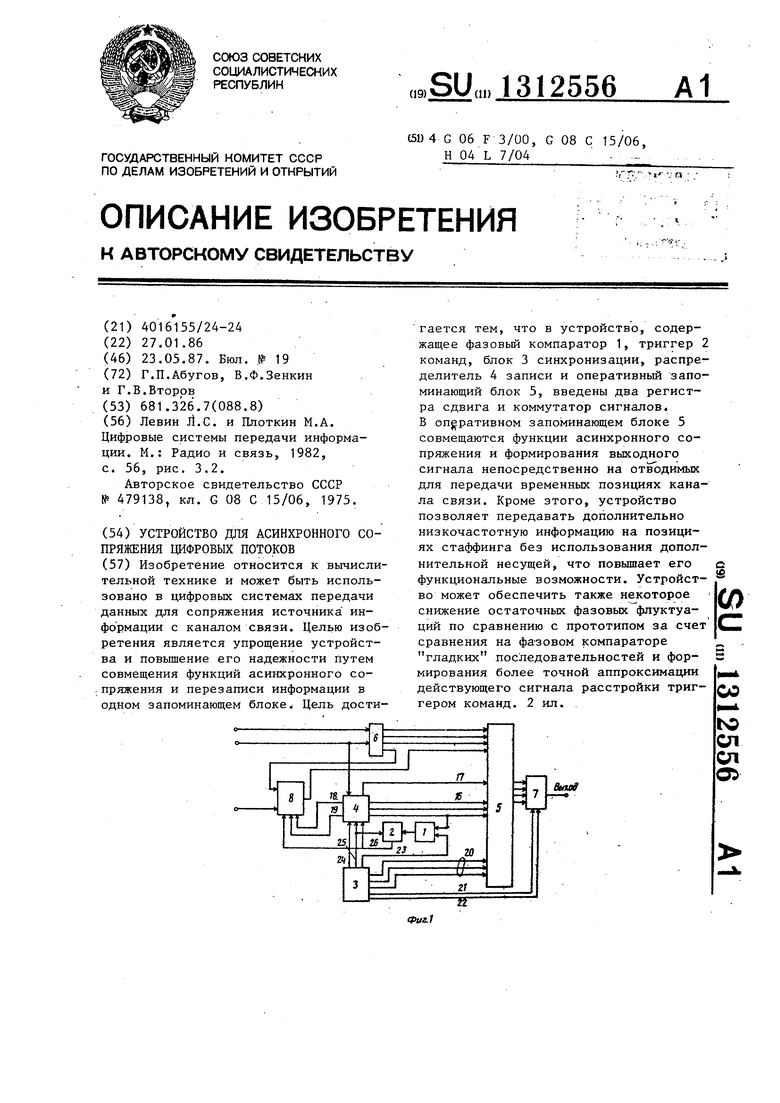

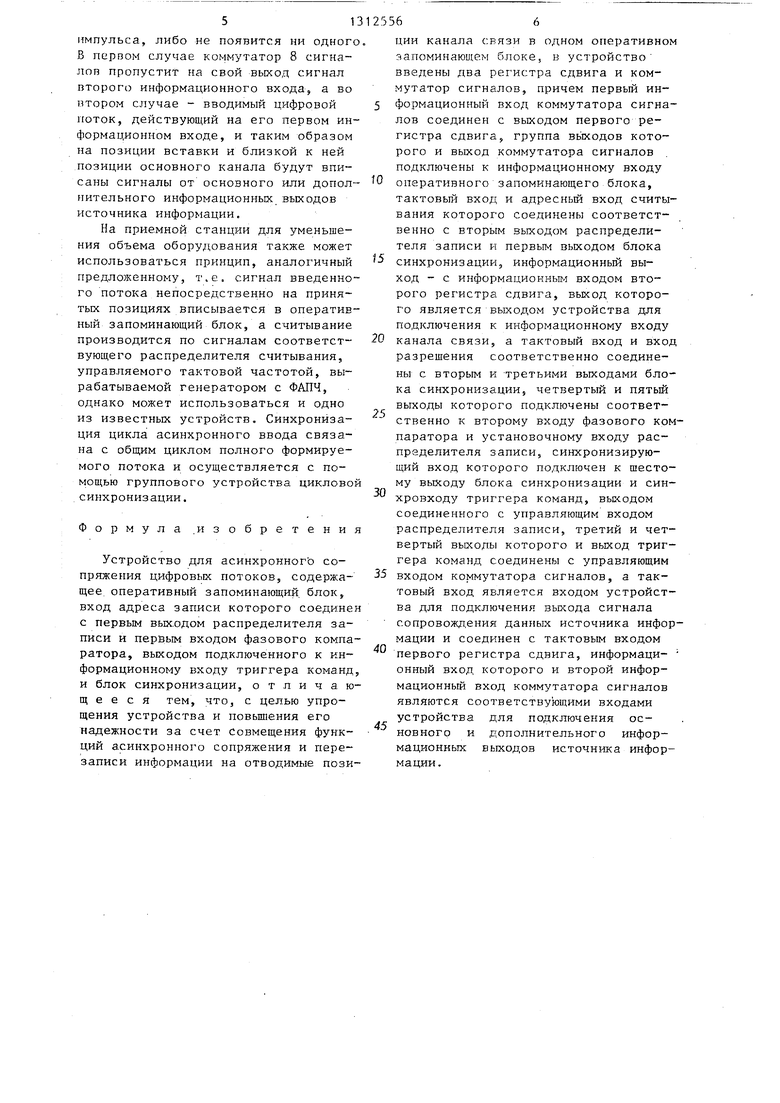

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема распределителя записи.

Устройство содержит (фиг. 1) фазовый компаратор 1, триггер (формирователь) 2 команд, блок 3 синхронизации, распределитель 4 записи, оперативный запоминающий блок 5, регистры 6 и 7 сдвига и коммутатор 8 сигналов ,

Распределитель 4 записи (фиг. 2) содержит последовательно соединенные управляемый делитель 9 частоты, первый и второй делители 10 и 11 частоты, первый и второй элементы И 12 и 13, элементы ИЛИ 14 и И-НЕ 15.

Устройство содержит также выходы 16-19 распределителя 4 записи, выходы 20-25 блока 3 синхронизации и выход 26 триггера 2,

Устройство работает следующим образом.

Вводимый информационный сигнал и сопровождающий его хронирующий (тактирующий) сигнал поступают на входы регистра 6, в котором информационный сигнал преобразуется в параллельную форму и в таком виде поступает, на информационные входы оперативного запоминающего блока 5, выполненного в виде многоцелевого регистра с раздельной адресацией записи и считывания информации. Процессом записи информации управляет распределитель 4, вырабатывающий на своем выходе 16 необходимые сигналы. Непосредственно запись информации осуществляется в момент действия тактового импульса на выходе 17 распределителя 4,

Считывание информации из оператив- ,с ного запоминающего блока 5 осуществляется по сигналам от блока 3, формирующего на адресных входах считывания оперативного запоминающего бло30

35

40

45

50

ка 5 став пози запо лель прео форм руем обра рует отве пози запи

пото пере нени ются ра ра 8 дит тоты вующ щей блок част ется запи поми чени торо их мом рас дей допу мых ния выр вход 2 в ких око тыв

фор нем обр ный дае а в мех ляе вс тел кан

ка 5 сигналы, соответствующие предоставляемым в канале связи тактовым позициям. Считанный из оперативного запоминающего блока 5 сигнал в параллельной форме с помощью регистра 7 преобразуется в последовательную форму по управляющему сигналу, формируемому на вьЕХОде 22 блока 3. Таким образом, на выходе регистра 7 формируется выходной сигнал, занимающий отведенные в канале связи временные позиции без дополнительной перезаписи.

5

0

5

,с

0

5

0

45

0

Выравнивание скоростей вводимого потока и синхронной несущей, а также передача команд управления и заполнение позиций стаффинга осуществляются с помощью фазового компаратора 1, формирователя 2 и коммутатора 8. Фазовый компаратор 1 производит сравнение фаз субгармоники частоты вводимого потока и соответствующей субгармоники импульсной несущей, вырабатываемой на выходе 23 блока 3. В качестве субгармоники частоты вводимого сигнала используется соответствующий адресный сигнал записи информации в оперативном запоминающем блоке 5. Номинальные значения сравниваемых фазовым компаратором 1 частот равны, однако ввиду их несинхронности в произвольный момент времени-может действовать расстройка любого знака. Границы действующей расстройки определяются допусками на стабильность сравниваемых частот. По результатам сравнения сигналов фазовый компаратор 1 вырабатывает сигнал, поступающий на вход формирователя 2. Формирователь 2 вырабатывает один из двух логических уровней - команду управления по окончании позиции стаффинга, вырабатываемой блоком 3.

В представляемом для передачи информации канале связи при двустороннем стаффинге все отводимые позиции образуют основной и дополнительный каналы. В основном канале передается вводимый асинхронный сигнал, а в дополнительном - передаются по- мехозащищенные (состоящие из несколь- бит) команды управления и вьще- ляется циклически следующая позиция вставки. При этом позиции дополнительного канала в предоставляемом канале связи равномерно распределены

31312556

с целью повышения помехоустойчивости к сосредоточенным помехам.

Выравнивание с коростей вводимого потока и отводимой несущей основного канала осуществляется с помощью пози- 5 ции вставки. В случае, если в отдельном цикле скорость вводимого потока превышает скорость основного канала, на позиции вставки передается бит инпервом входе фазового компар На выходе 21 действуют такто следовательность канала связ выходе 22 - тактовая последо ность с частотой в п раз ниже разрядность слова оперативног минающего блока 7. Адресные с на выходе 20 блока 3 формирую соответствии с выделяемыми дл

формации вводимого потока, в против- дачи позициями канала связи.

ном случае бли зкая по времени позиция к позиции вставки основ.ного -канала и сама позиция вставки являются балластными, т.е. не несут информации вводимого потока. Каждая из указанных ситуаций сопровождается - передачей соответствующей команды управления на отведенных позициях дополнительного канала. В тех циклах, в которых позиция вставки является балластной, на ней может быть организована передача дополнительной низкочастотной информации.

Заполнение информацией равномерно следующих позиций дополнительного ка нала осуществляется в .коммутаторе 8 по управляющим сигналам выходов 18 и 19 распределителя 4 и формирователя 2. На позициях основного канала и на позициях вставки, используемой для передачи основной информации, . на выход коммутатора 8 проходит вводимый сигнал с регистра 6. На позициях, отведенных для передачи команд управления, на выходе коммутатора 8 действует логический уровень с выхода формирователя 2, а на позициях вставки, не использующихся для передачи основной информации, на выход коммутатора 8 поступает сигнал второго информационного входа. Таким образом, в оперативный запоминающий блок 5 записывается вся информация, следующая как в основном, так и в дополнительном каналах.

Блок 3 синхронизации является блоком общего назначения, в состав которого входят задающий генератор, делители частоты и формирователи необходимых импульсных позиций. На вькоде 25 формируется позиция вставки, следующая с частотой циклов асинхронного ввода, на выходе 24 действует короткий фазирующий импульс, также следующий с частотой циклов асинхронного ввода. На выходе 23 действует импульсная последовательность с частотой, номинально равной частоте на

первом входе фазового компаратора 1. На выходе 21 действуют тактовая последовательность канала связи, а на выходе 22 - тактовая последовательность с частотой в п раз ниже, гдеп - разрядность слова оперативного запоминающего блока 7. Адресные сигналы на выходе 20 блока 3 формируются в соответствии с выделяемыми для передачи позициями канала связи.

15

25

30

-20

Распределитель 4 записи для рассматриваемого примера работает следующим образом (фиг. 2).

Нд вход цепочки делителей 9-11 поступает хронирующий сигнал вводимого потока. Коэффициент деления управляемого делителя 9 равен числу информационных разрядов слова оперативного запоминающего блока 5, а общий коэффициент деления m всего делителя - емкости памяти оперативного запоминающего блока 5 (в данном примере пусть , ). На выходе элемента И 12 формируется тактовая последовательность записи информации в оперативный запоминающий блок 5. Коэффициент деления делителя 10 равен 4, второго делителя 11 частоты - 2 . Импульсом с выхода 24 блока 3 производится фазировка делителя 11 частоты по его установочному входу один раз за цикл асинхронного ввода. Адресные сигналы записи информации снимаются с выходов делителей 10 и 11. 5 Коэффициент деления делителя 9 уменьшается на единицу при формировании позиции дополнительного канала (в данном примере это каждая 1б-я позиция) путем подачи на управляющий вход делителя 9 сигнала с элемента И 13. При этом за счет появления управляющего сигнала на соответствующем входе, коммутатор 8 подключает к икформаци- онному входу сигнал с выхода формирователя 2 команд, т.е. в соответствующую ячейку оперативного запоминающего блока 5 записывается очередной символ текущей команды. За полный цикл асинхронного ввода таким образом будут вписаны все символы команды.

При поступлении по входу 25 сигнала позиции вставки на входы элементов ИЛИ 14 и И-НЕ 15 в зависимости от значения очередной команды формирователя 2 управления на входе 26, на выходе элемента И 13 появятся либо два подряд следующих управляющих

40

0

513

импульса, либо не появится ни одного В первом случае коммутатор 8 сигна- лоп пропустит на свой выход сигнал второго информационного входа, а во втором случае - вводимый цифровой поток, действующий на его первом информационном входе, и таким образом на позиции вставки и близкой к ней позиции основного канала будут вписаны сигналы от основного или дополнительного информационных выходов источника информации.

На приемной станции для уменьшения объема оборудования также может использоваться принцип, аналогичный предложенному, т.е. сигнал введенного потока непосредственно на принятых позициях вписывается в оперативный запоминающий блок, а считывание производится по сигналам соответствующего распределителя считывания, управляемого тактовой частотой, вырабатываемой генератором с ФАПЧ, однако может использоваться и одно из известных устройств. Синхронизация цикла асинхронного ввода связана с общим циклом полного формируемого потока и осуществляется с помощью группового устройства цикловой синхронизации.

Формула .изобретения

Устройство для асинхронного сопряжения цифровых потоков, содержащее, оперативный запоминающий, блок, вход адреса записи которого соединен с первым выходом распределителя записи и первым входом фазового компаратора, выходом подключенного к информационному входу триггера команд, и блок синхронизации, отличающееся тем, что, с целью упрощения устройства и повьшюния его надежности за счет совмещения функций асинхронного сопряжения и перезаписи информации на отводимые пози66

ции канала связи в одном оперативном запоминающем блоке, в устройство введены два регистра сдвига и коммутатор сигналов, причем первый информационный вход коммутатора сигналов соединен с выходом первого регистра сдвига, группа вькодов которого и выход коммутатора сигналов подключены к информационному входу

оперативного запоминающего блока,

тактовьш вход и адресный вход считывания которого соединены соответственно с вторым выходом распределителя записи и первьп выходом блока

синхронизации, информационный выход - с информационньм входом второго регистра сдвига, выход которого является выходом устройства для подключения к информационному входу

канала связи, а тактовый вход и вход разрешения соответственно соединены с вторым и третьими выходами блока синхронизации, четвертый и пятый выходы которого подключены соответственно к второму входу фазового компаратора и установочному входу распределителя записи, синхронизирую- ЩИ.Й вход которого подключен к шестому выходу блока синхронизации и син- хровходу триггера команд, выходом соединенного с управляющим входом распределителя записи, третий и четвертый выходы которого и выход триггера команд соединены с управляющим

входом коммутатора сигналов, а тактовый вход является входом устройства для подключения выхода сигнала сопровождения данных источника информации и соединен с тактовым входом

первого регистра сдвига, информаци- онный вход которого и второй информационный вход коммутатора сигналов являются соответствующими входами устройства для подключения основного и дополнительного информационных выходов источника информации.

На t onnapamop 1

Изобретение относится к вычислительной технике и может быть использовано в цифровых системах передачи данных для сопряжения источника информации с каналом связи. Целью изобретения является упрощение устройства и повьппение его надежности путем совмещения функций асинхронного со.пряжения и перезаписи информации в одном запоминающем блоке. Цель достигается тем, что в устройство, содержащее фазовый компаратор 1, триггер 2 команд, блок 3 синхронизации, распределитель 4 записи и оперативный запоминающий блок 5, введены два регистра сдвига и коммутатор сигналов. В оперативном запоминающем блоке 5 совмещаются функции асинхронного сопряжения и формирования выходного сигнала непосредственно на отводимых для передачи временных позициях канала связи. Кроме этого, устройство позволяет передавать дополнительно низкочастотную информацию на позициях стаффинга без использования дополнительной несущей, что повышает его функциональные возможности. Устройство может обеспечить также некоторое снижение остаточных фазовых флуктуации по сравнению с прототипом за счет сравнения на фа-зовом компараторе гладких последовательностей и формирования более точной аппроксимации действующего сигнала расстройки триггером команд. 2 ил. Btasaff (Л оо to ел СП о

| Левин Jl.C | |||

| и Плоткин М.А | |||

| Цифровые системы передачи информации | |||

| М.: Радио и связь, 1982, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов | 1973 |

|

SU479138A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-27—Подача