Изобретение относится к электросвязи и может использоваться в системе цифровой связи.

Целью изобретения является упрощение устройства путем уменьшения объема памяти блоков асинхронного сопряжения

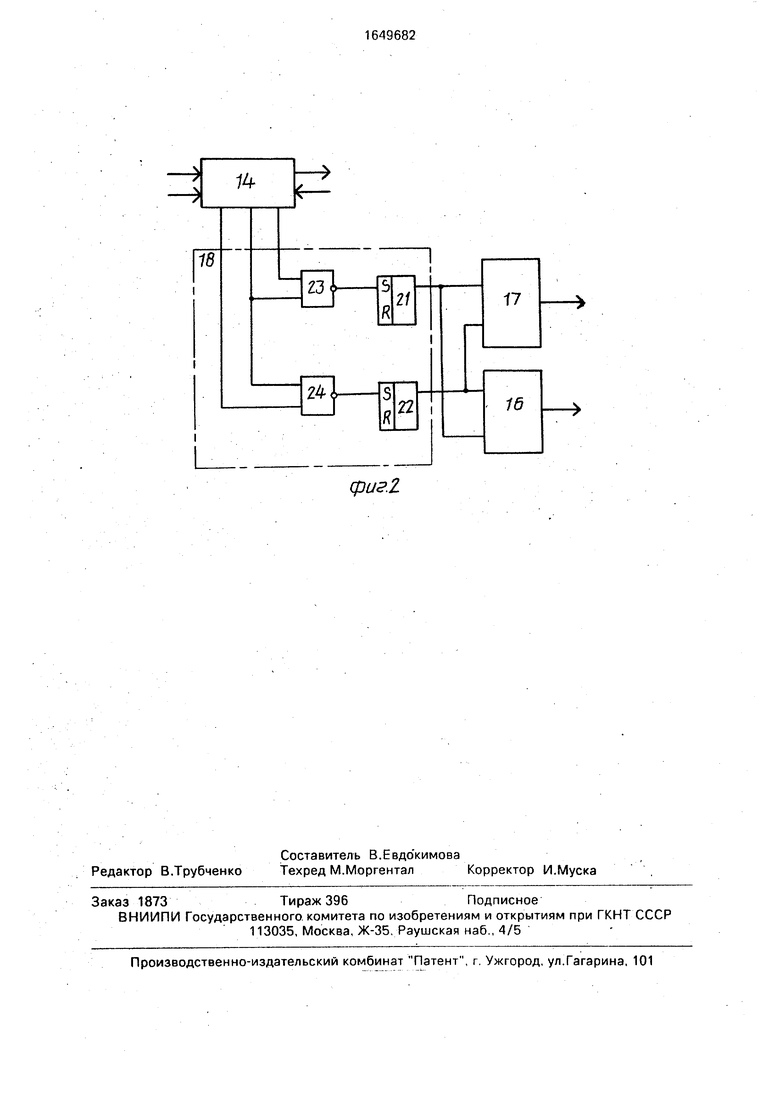

На фиг. 1 представлена структурная электрическая схема устройства для сопряжения асинхронных цифровых потоков; на фиг. 2 - вариант выполнения временного дискриминатора.

Устройство для сопряжения асинхронных цифровых потоков содержит канальный распределитель 1, выделитель 2 тактовой частоты (ВТЧ), приемник 3 синхросигнала, приемник команд согласования скоростей (КСС) 4, тактовый генератор 5 приема, п блоков асинхронного сопряжения (БАС) 6i - 6п, блок объединения 7, передатчик 8 синхросигнала, тактовый генератор 9 передачи, передатчик команд согласования скоростей (КСС) 10, при этом в состав приемника КСС 4 входят блок запуска 11, распределитель 12 и дешифратор 13, в состав каждого из п блоков АС 6П входят запоминающий узел (ЗУ) 14, коммутатор частот записи (43) 15, коммутатор частот считывания (ЧС) 16, коммутатор КСС 17 и временный дискриминатор (ВД) 18, а в состав передатчика КСС 10 входят распределитель 19 и формирователь КСС 20, причем в состав временного дискриминатора входят триггеры 21 и 22 и элементы 2И-НЕ 23 и 24.

Устройство для сопряжения асинхронных цифровых потоков работает следующим образом

Принимаемый из линейного тракта цифровой поток поступает в канальный распределитель 1, где выделяются индивидуальные цифровые потоки, которые подаются на информационные входы запоминающих узлов п блоков AC 6i - 6П и

Јь

Ю

записываются в них тактовой последовательностью тактового генератора 5 приема через коммутатор 43 15, управление которого происходит, в зависимости от поступившей из линейного тракта команды или ее отсутствия.

При .поступлении в дешифратор 13 на позициях какого-либо канала команды положительного согласования скоростей (101010) от тактового генератора 5 коммутатором 43 15 будет скоммутирован дополни- тельный тактовый импульс, которые запишет в запоминающий узел 14 с дополнительной позиции линейного сигнала избыточную информационную посылку, переданную с соседних станций, Если же поступает команда отрицательного согласования скоростей (010101), то через коммутатор 43 15 будет запрещено прохождение очередного тактового импульса основной тактовой последовательности и регистрации информации из пустого тактового интервала в запоминающий узел не произойдет. Если распределителем 12 в дешифратор 13 будут записаны нули, что соответствует отсутствию команды согласования, то через коммутатор 43 15 на вход запоминающего узла 14 пройдут только импульсы информационных тактовых позиций.

Вывод информации из запоминающего узла 14 п блоков AC 6i - 6п производится тактовой частотой передачи, поступающей от тактового генератора 9 передачи через коммутатор 4С 16. Если запоминающий узел 14 начинает переполняться, что определяется временным дискриминатором 18, сравнением фаз записи и считывания, то коммутатором КСС 17 в линию на соответствующих позициях будет скоммутирован сигнал команды положительного согласования скоростей, а через коммутатор 4С 16 будет скоммутирована дополнительная тактовая позиция. Таким образом освободится одна дополнительная ячейка в запоминающем узле 14.

Если запоминающий узел 14 начинает опустошаться, то в линию будет скоммутирована команда отрицательного согласования скоростей, а из основной тактовой последовательности коммутатором 4С 16 будет исключен очередной тактовый импульс, т.е. считывание из запоминающего узла 14 не будет произведено.

Тактовые генераторы 5 и 9 приема и передачи выполнены аналогично, но тактовый генератор 5 приема управляется прием- ником 3 синхросигнала, кдторый устанавливает и поддерживает его фазовые соотношения с тактовым генератором передачи соседней станции, а тактовый генератор 9 передачи через передатчик 8 синхросигнала передает на соседнюю станцию свое фазовое положение, тактовый генераторы 5 и 9 распределяют тактовые позиции по принадлежности индивидуальным информационным потоком, определяют служебные позиции, в том числе для передачи команд согласования скоростей и компен0 сации расхождения скоростей приема и передачи для каждого индивидуального потока.

Тактовые позиции информационных потоков и позиции компенсации расхождения

5 скоростей выделяются индивидуально и подаются на приеме в коммутаторы 43 15, а на передаче - в коммутатор 4С 16, где они коммутируются в запоминающий узел 14 в зависимости от команды согласования ско0 ростей или соотношения фаз записи и считывания.

Тактовые позиции команд согласования скоростей поочередно для каждого индивидуального канала поступают на приеме от

5 тактового генератора приема 5 в приемник КСС 4, где ими поочередно регистрируются команды, поступающие из линейного тракта, а на передаче тактовые позиции КСС поступают в передатчик КСС (10), где фор0 мируются пояснительные и отрицательные КСС и подаются на раздельные выходные шины, с которых коммутируются соответствующими коммутаторами КСС на соответст- вующих позициях того или иного

5 индивидуального потока в зависимости от управляющего сигнала, поступившего от временного дискриминатора 18.

Формула изобретения

0Устройство для сопряжения асинхронных цифровых потоков, содержащее п-бло- ков асинхронного сопряжения (БАС), в- состав каждого из которых входят последовательно соединенные запоминаюадой узел

5 и временной дискриминатор, к информационному входу запоминающего узла каждого БАС подключен соответствующий выход канального распределителя, вход которого соединен с входами выделителя тактовой

0 частоты и приемника синхросигнала, выходы которых соединены с соответствующими входами тактового генератора приема, один из выходов которого подключен к управляющему входу приемника команд согласова5 ния скоростей (КСС), а другой выход подключен к управляюа(ему входу канального распределителя, выход запоминающего узла каждого БАС подключен к соответствующему входу блока объединения, управляющий вход которого через пе- и

редатчик синхросигнала подключен к управляющему выходу тактового генератора передачи, тактовый выход которого подключен к соответствующему входу передатчика КСС, отличающееся тем, что, с целью упрощения устройства путем сокращения объема памяти, приемник КСС выполнен в виде последовательно соединенных блока запуска, распределителя и дешифратора, причем выход последнего разряда распределителя соединен с управляющим входом блока запуска, два входа которого являются дополнительными входами приемника КСС, сигнальный и управляющий входы дешифратора - соответственно сигнальным и управляющим входами приемника КСС, выходами которого являются выходы дешифратора, передатчик КСС выполнен в виде последовательно соединенных распределителя и формирователя КСС, причем тактовый вход и соответствующий выход распределителя являются соответственно тактовым входом и управляющим выходом передатчика КСС, выходами которого являются выходы формирователя КСС, а в каждый из п БАС введены коммутатор частот записи (43), коммутатор частот считывания (43) и коммутатор КСС, при этом дополнительные выходы тактового генератора приема подключены к соответствующим входам

приемника КСС, сигнальный вход которого соединен с входом канального распределителя, а выходы приемника КСС подключены к соответствующим входам коммутаторов 5 43 п БАС, к другим входам которых подключены соответствующие выходы канальных тактовых частот и дополнительных тактовых позиций тактового генератора приема, выход коммутатора 43 каждого из п БАС под0 ключей к тактовому входу приема соответствующего запоминающего узла, к тактовому входу передачи которого подключен выход соответствующего коммутатора 4С, к управляющим входам которого и ком5 мутатора КСС подключены соответствующие выходы временного дискриминатора, другие входы коммутаторов КСС всех п БАС соединены между собой и подключены к соответствующим выходам передатчика

0 КСС, управляющий выход которого подклю-, чен к соответствующему входу тактового генератора передачи, а выходы коммутаторов КСС п БАС соединены с соответствующими управляющими входами блока

5 объединения, один из дополнительных выходов тактового генератора передачи под- ключен к соответствующему входу временного дискриминатора, а три других дополнительных выхода тактового генера0 тора передачи подключены к соответствующим входам коммутаторов 4С п БАС.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи цифровых сигналов | 1980 |

|

SU919129A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство для передачи и приема цифровых сигналов | 1980 |

|

SU919113A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| СИСТЕМА СИНХРОННОГО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1995 |

|

RU2096916C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ПРИЕМА, ДЕМОДУЛЯЦИИ И ОБРАБОТКИ СИГНАЛОВ I-IV УРОВНЕЙ ИЕРАРХИЧЕСКОГО УПЛОТНЕНИЯ | 2001 |

|

RU2224375C2 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| Устройство цифрового транзита каналов в узлах сети связи | 1985 |

|

SU1320905A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ и КАНАЛЬНОЙ СИНХР011ИЗАЦИИ | 1970 |

|

SU259136A1 |

Изобретение относится к электросвязи Цель изобретения - упрощение устройства. Устройство для сопряжения асинхронных цифровых потоков содержит канальный распределитель 1. выделитель 2 тактовой частоты, приемник 3 синхросигнала, приемник 4 команд согласования скоростей, тактовый генератор 5 приема, блоки 6 асинхронного сопряжения, блок 7 объединения, передатчик 8 синхросигнала, тактовый генератор 9 передачи и передатчик 10 команд согласования скоростей. Цель достигается путем сокращения объема памяти блоков 6 Для этого приемник 4 выполнен из блока 11 запуска, распределителя 12 и дешифратора 13, передатчик 10 - из распределителя 19 и формирователя 20 команд согласования скоростей, а блок 6 - из запоминающего узла 14, коммутатора 15 частот записи, коммутатора 16 частот считывания, коммутатора 17 команд согласования скоростей и временного дискриминатора 18. 2 ил.

. Фиг. 1

фиг2

| Левин Л.С | |||

| и Плоткин М.А | |||

| Основы построения цифровых систем передачи М : Связь, 1975, с | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

Авторы

Даты

1991-05-15—Публикация

1988-06-23—Подача