о

to

о

Устройство относится к электросвязи, а именно к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне.

Цель изобретения - повышение степени ослабления временных флюктуации тактового сигнала путем выделения постоянной составляющей управляющего сигнала.

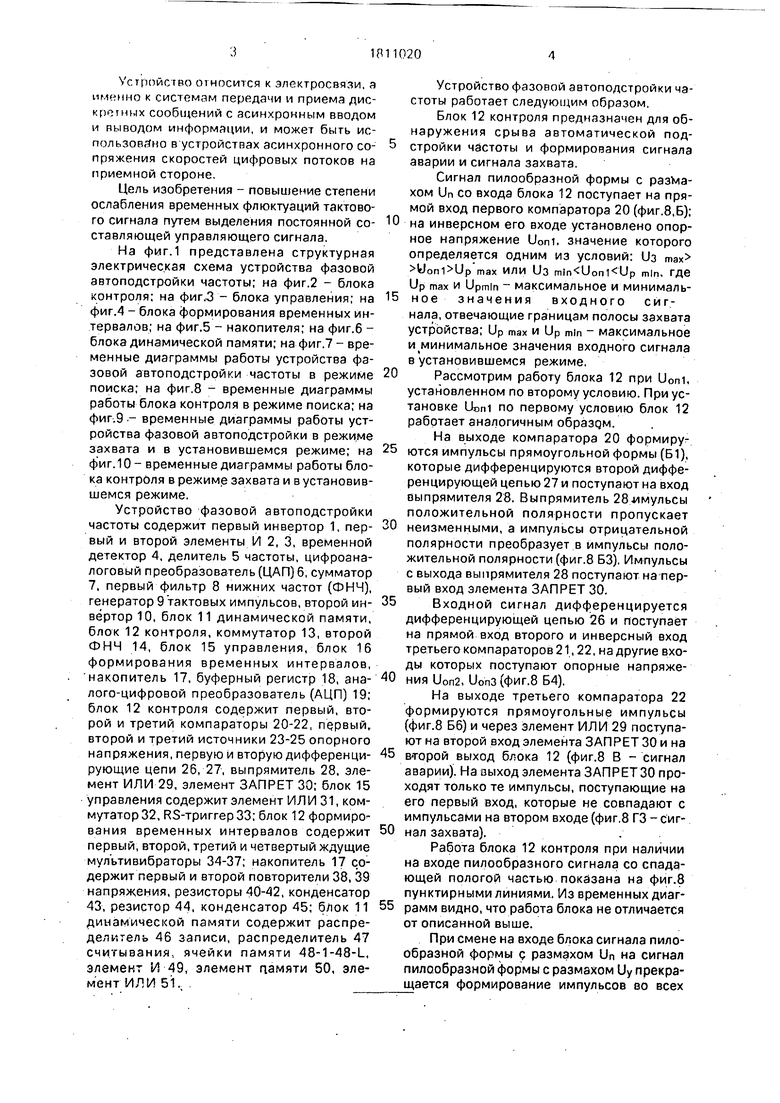

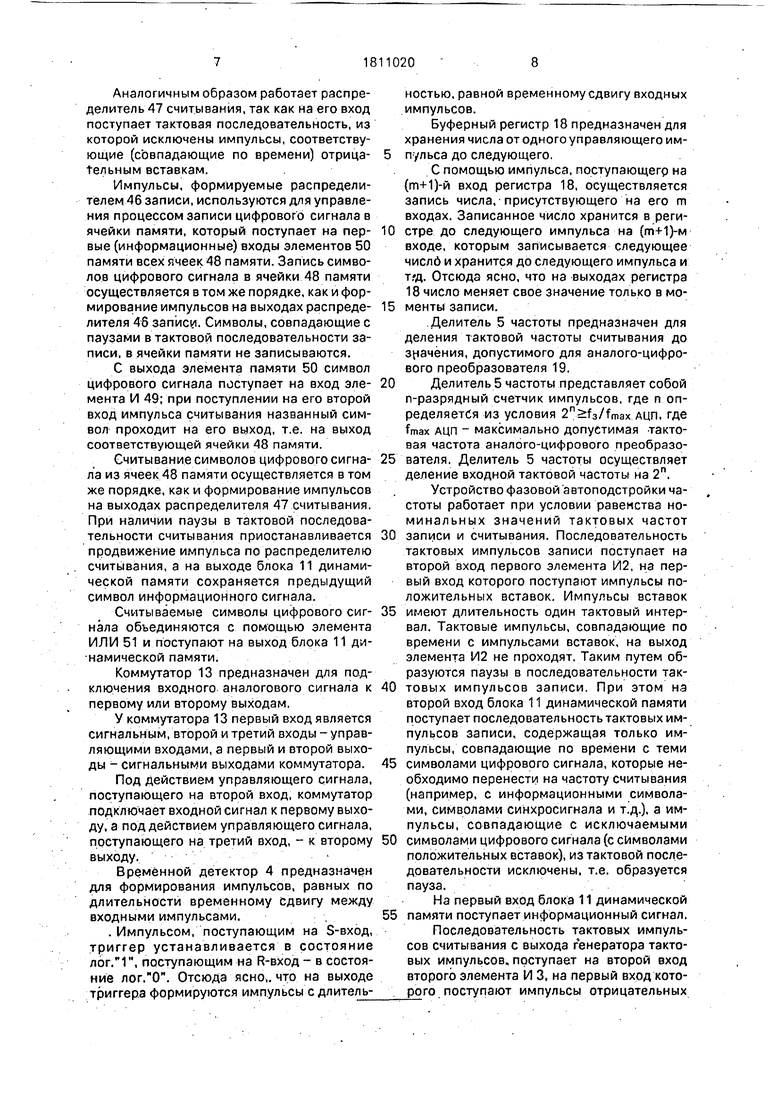

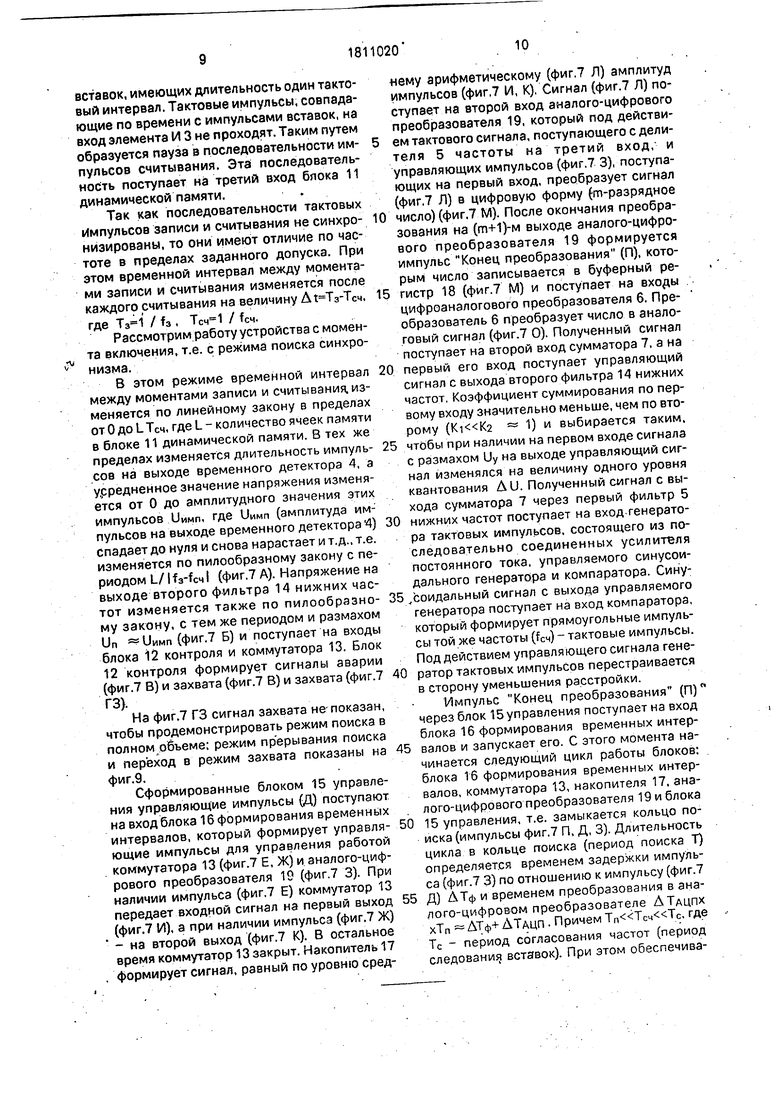

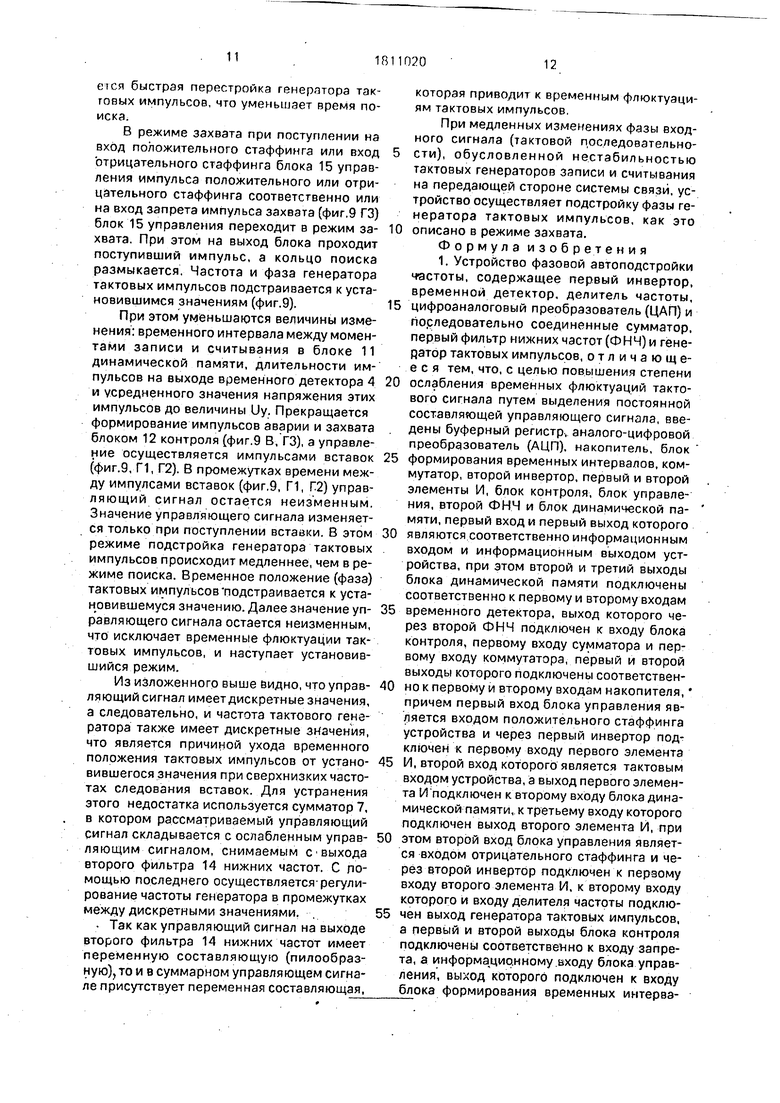

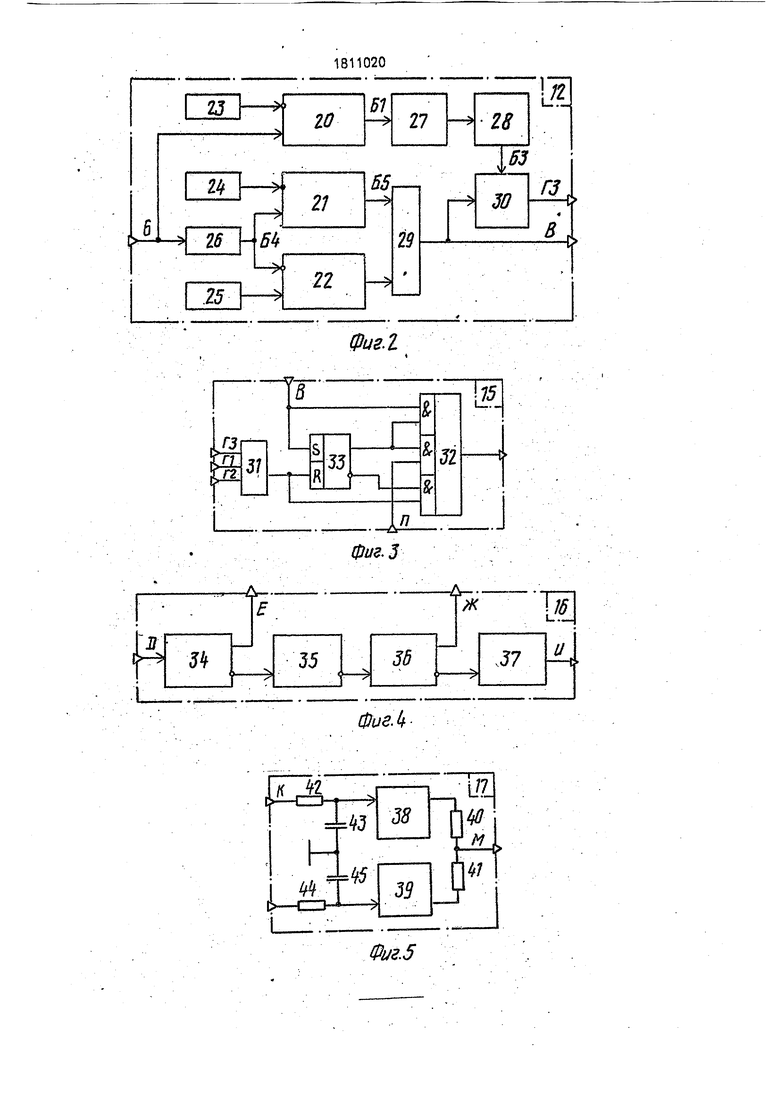

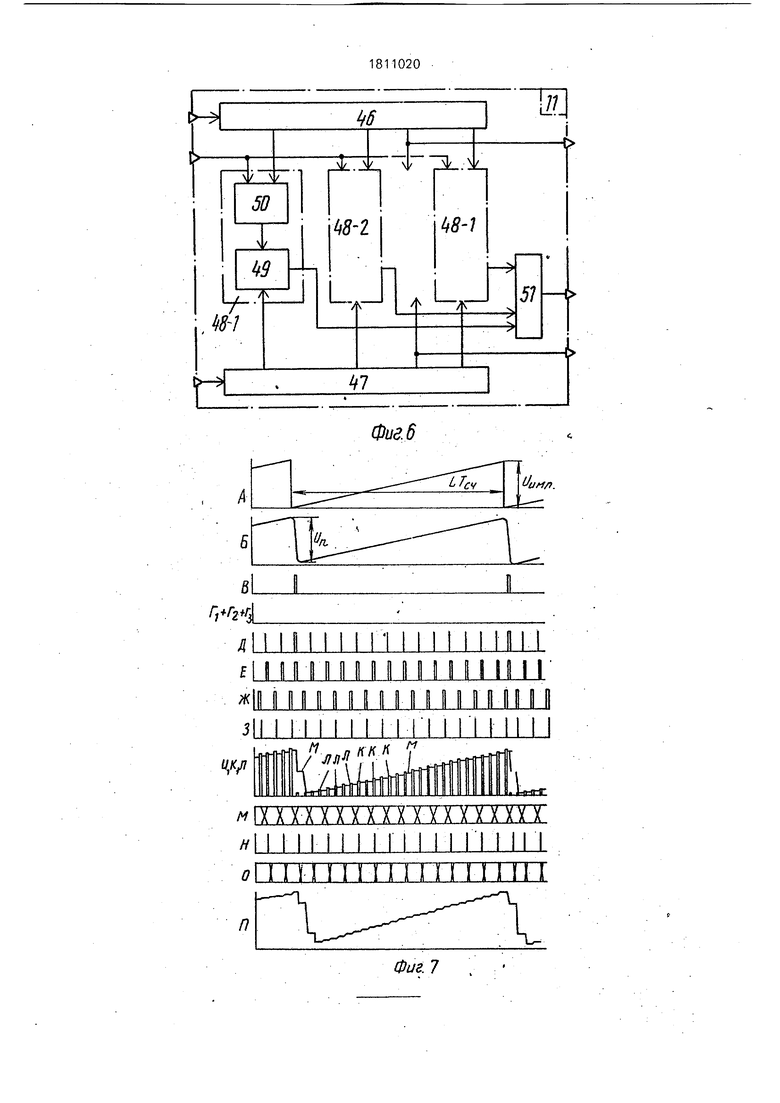

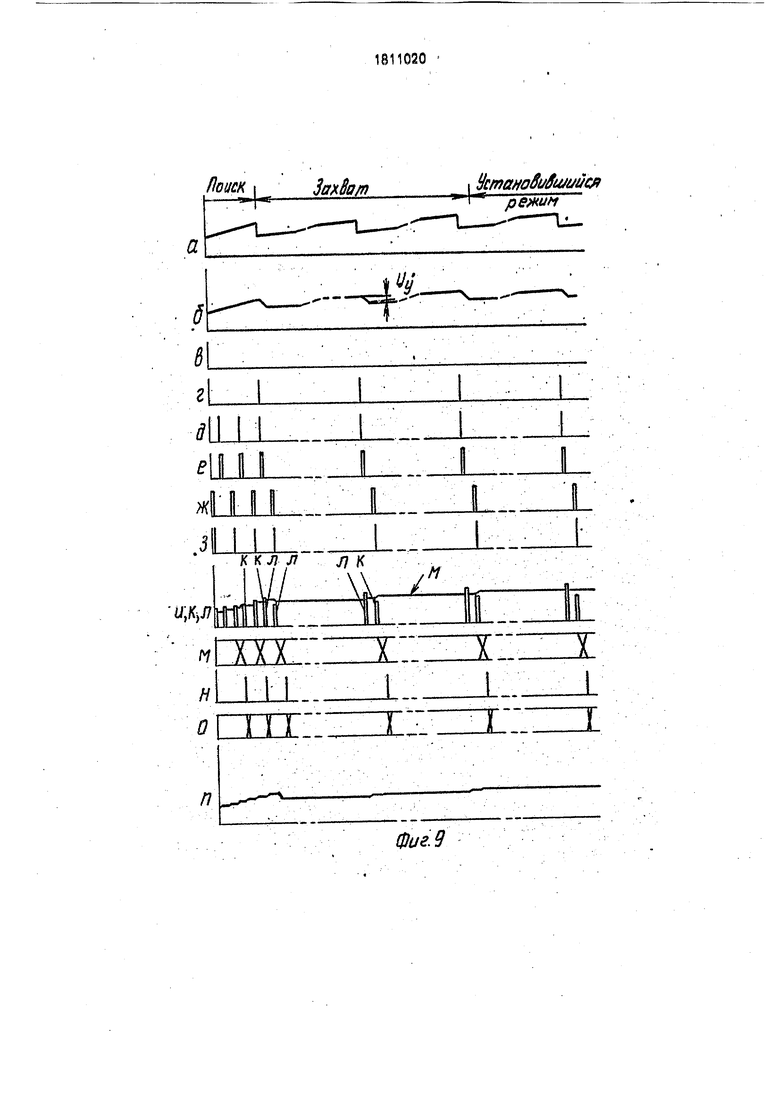

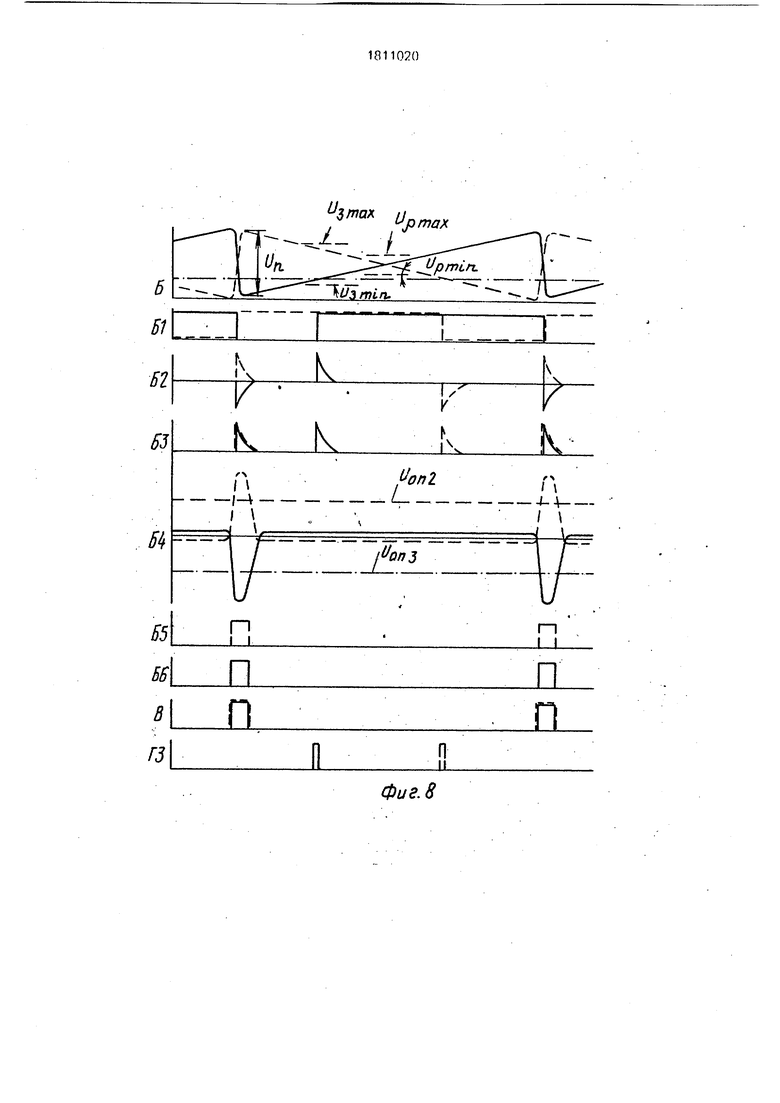

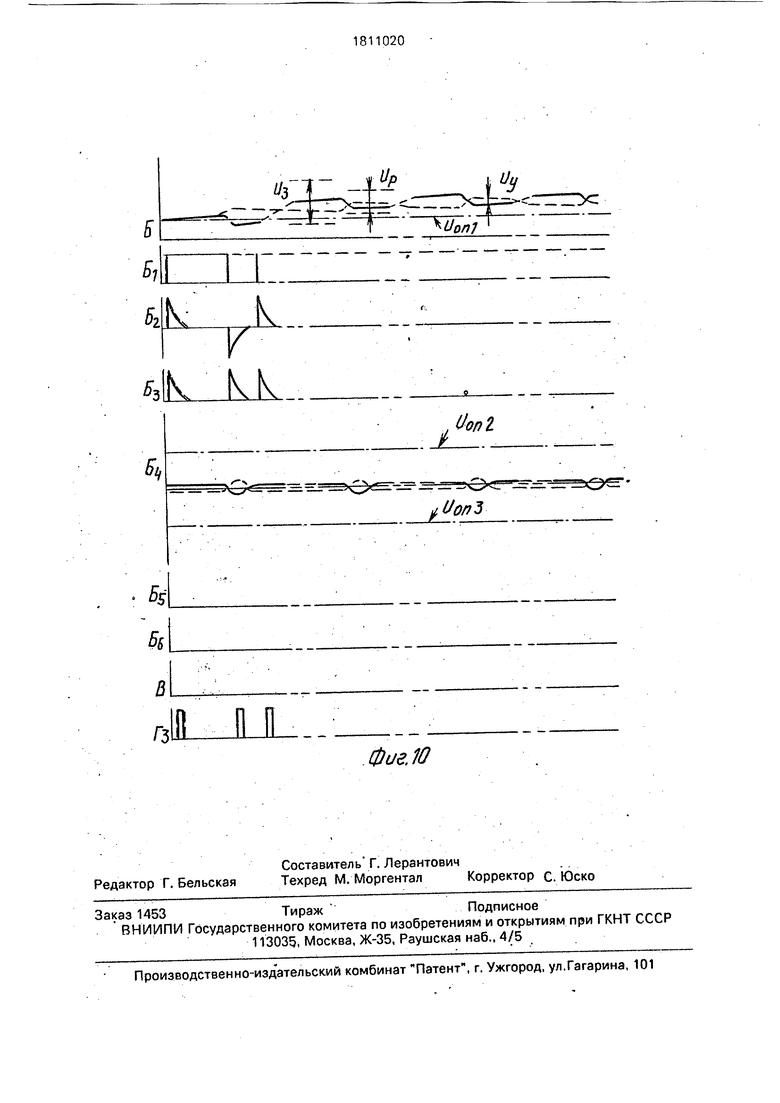

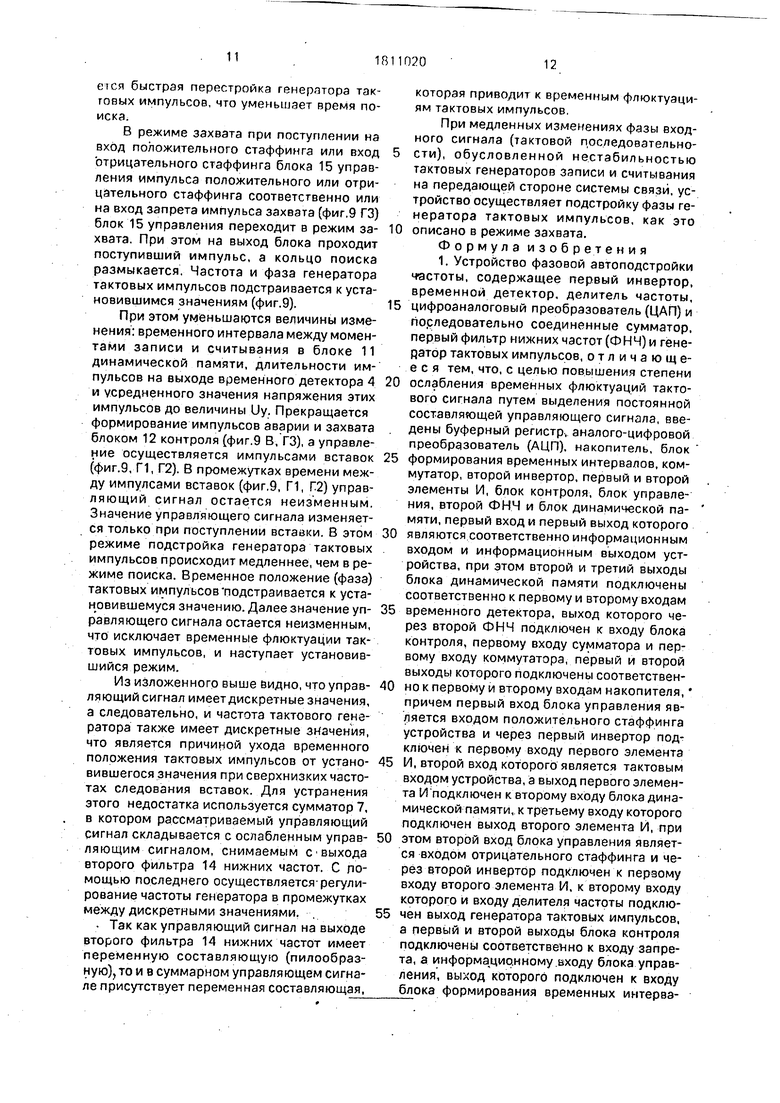

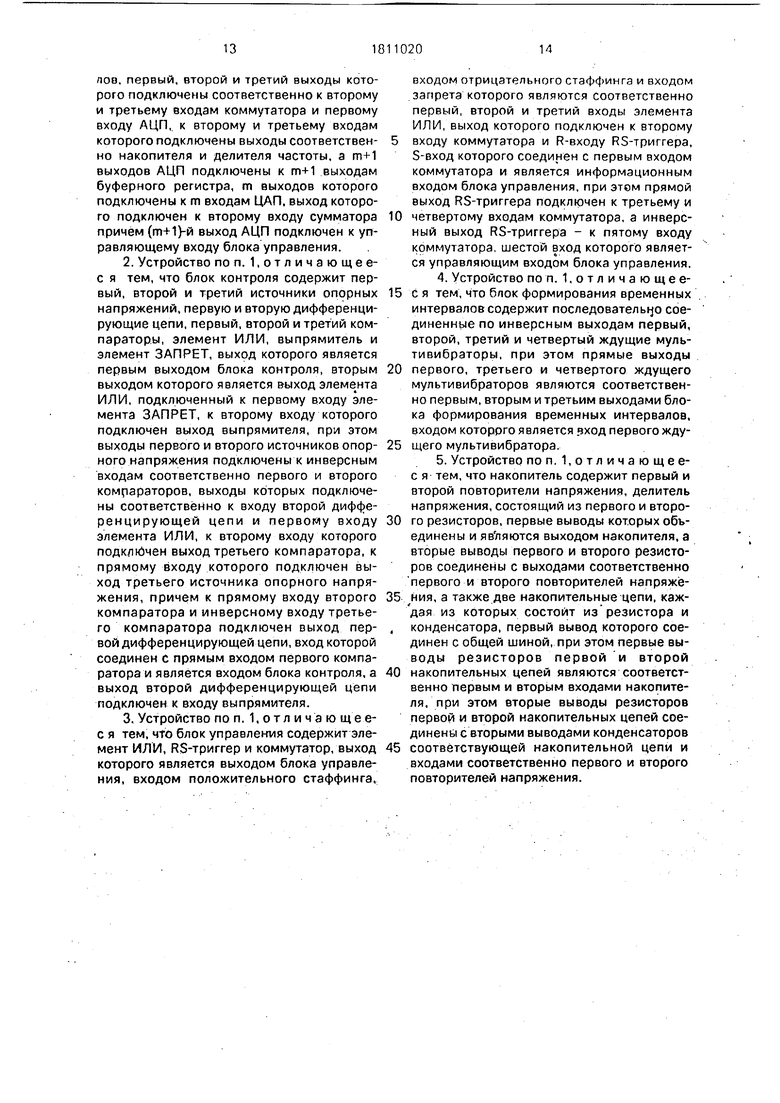

На фиг.1 представлена структурная электрическая схема устройства фазовой автоподстройки частоты; на фиг.2 - блока контроля; на фиг.З - блока управления; на фиг.4 - блока формирования временных интервалов; на фиг.5 - накопителя; на фиг.6 - блока динамической памяти; на фиг.7 - временные диаграммы работы устройства фазовой автоподстройки частоты в режиме поиска; на фиг.8 - временные диаграммы работы блока контроля в режиме поиска; на фиг.9 - временные диаграммы работы устройства фазовой автоподстройки в режиме захвата и в установившемся режиме; на фиг.10- временные диаграммы работы блока контроля в режиме захвата и в установившемся режиме.

Устройство фазовой автоподстройки частоты содержит первый инвертор 1, первый и второй элементы И 2, 3, временной детектор 4, делитель 5 частоты, цифроана- логовый преобразователь (ЦАП) б, сумматор 7, первый фильтр 8 нижних частот (ФНЧ), генератор 9 тактовых импульсов, второй инвертор 10, блок 11 динамической памяти, блок 12 контроля, коммутатор 13, второй ФНЧ 14, блок 15 управления, блок 16 формирования временных интервалов, накопитель 17, буферный регистр 18, ана- лого-цифровой преобразователь (АЦП) 19; блок 12 контроля содержит первый, второй и третий компараторы 20-22, пе.рвыйг второй и третий источники 23-25 опорного напряжения, первую и вторую дифференцирующие цепи 26, 27, выпрямитель 28, элемент ИЛИ 29, элемент ЗАПРЕТ 30; блок 15 управления содержит элемент ИЛИ 31, коммутатор 32, RS-триггерЗЗ; блок 12 формирования временных интервалов содержит первый, второй, третий и четвертый ждущие мультивибраторы 34-37; накопитель 17 содержит первый и второй повторители 38, 39 напряжения, резисторы 40-42, конденсатор 43, резистор 44, конденсатор 45; блок 11 динамической памяти содержит распределитель 46 записи, распределитель 47 считывания, ячейки памяти 48-1-48-L, элемент И 49, элемент памяти 50, элемент ИЛИ 51, .

Устройство фазовой автоподстройки частоты работает следующим образом.

Блок 12 контроля предназначен для обнаружения срыва автоматической под- стройки частоты и формирования сигнала аварии и сигнала захвата.

Сигнал пилообразной формы с размахом Un со входа блока 12 поступает на прямой вход первого компаратора 20 (фиг.8,Б);

0

на инверсном его входе установлено опорное напряжение Uoni. значение которого определяется одним из условий: Уз тах

max ИЛИ 11з mln, ГД6

Up max и Upmin - максимальное и минималь- 5 ное значения входного сигнала, отвечающие границам полосы захвата устройства; Up max и Up min - максимальное И(минимальное значения входного сигнала в установившемся режиме. 0 Рассмотрим работу блока 12 при Uoni, установленном по второму условию. При установке Uoni по первому условию блок 12 работает аналогичным образом.

На выходе компаратора 20 формируй 5 ются импульсы прямоугольной формы (Б1), которые дифференцируются второй дифференцирующей цепью 27 и поступают на вход выпрямителя 28. Выпрямитель 28имульсы положительной полярности пропускает 0 неизменными, а импульсы отрицательной полярности преобразует в импульсы положительной полярности (фиг.8 БЗ). Импульсы с выхода выпрямителя 28 поступают на первый вход элемента ЗАПРЕТ 30. 5 Входной сигнал дифференцируется дифференцирующей цепью 26 и поступает на прямой вход второго и инверсный вход третьего компараторов 21,22, на другие входы которых поступают опорные напряже- 0 ния Uon2, Uon3 (фиг.8 Б4),

На выходе третьего компаратора 22 формируются прямоугольные импульсы (фиг.8 Б6) и через элемент ИЛИ 29 поступают на второй вход элемента ЗАПРЕТ 30 и на 5 второй выход блока 12 {фиг.8 В - сигнал аварии). На выход элемента ЗАПРЕТ 30 проходят только те импульсы, поступающие на его первый вход, которые не совпадают с импульсами на втором входе (фиг.8 ГЗ - Сиг- 0 нал захвата)..

Работа блока 12 контроля при наличии на входе пилообразного сигнала со спадающей пологой частью показана на фиг.8 пунктирными линиями., Из временных диаг- 5 рамм видно, что работа блока не отличается от описанной выше.

При смене на входе блока сигнала пилообразной формы с размахом Un на сигнал пилообразной формы с размахом Uy прекращается формирование импульсов во всех

характерных точках (фиг. 10), На выхода первого компаратора 20 устанавливается по тенциал лог,1 (фиг, 10 51), а на выходе первой дифференцирующей цепи проходят импульсы с амплитудами, не достигающими пороговых значений (фиг. 10 54),

Работа блока 12 при наличии на входе пилообразного сигнала размахом Uy со спадающей пологой частью показана на фиг. 10 пунктирными линиями. Из временных диаграмм видно, что отличие состоит только в количестве импульсов, формируемых блоком после смены сигнала на входе блока, что не имеет существенного значения для работы устройства.

Блок 15 управления предназначен для формирования управляющих импульсов и работает следующим образом.

На вход положительного стаффинга, вход отрицательного стаффинга и вход запрета блока 15 поступают импульсы положительного стаффинга, отрицательного стаффинга и сигнала захвата соответственно. Названные импульсы объединяются элементом ИЛИ 31 и поступают на R-вход . RS-триггера 33, который устанавливается в состояние лог. О, открывая коммутатор 32 по второму входу и закрывая по первому и шестому входам. При этом на выход блока 15 проходят импульсы с его входов положЧ - тельного и отрицательного стаффинга и входа запрета.

Импульсы сигнала аварии, поступающие на информационный вход блока 15, устанавливают RS-триггер 33 в состояние лог.1, и открывая коммутатор 32 по первому и шестому входам и закрывая его по второму входу. При этом на выход блока 15 проходят импульсы с его информационного и управляющего входов.

Блок 16 формирования временных интервалов, предназначенный для формирования импульсов заданной длительности и с заданными временными сдвигами, работает следующим образом.

Первый ждущий мультивибратор 34 запускается положительным фронтом импульса, поступившего на вход блока 16, и формирует импульс заданной длительности. Задним фронтом этого импульса запускается второй ждущий мультивибратор 35 и формирует импульс, задним фронтом которого запускается третий ждущий мультивибратор 36. Этот мультивибратор формирует импульс, равный по длительности импульсу, формируемому первым ждущим мультивибратором 34, а временной сдвиг между ними определяется длительностью импульса, формируемого вторым ждущим мультивибратором 35. Четвертый

ждущий мультишибрггор 37 запускается задним фронтом импульса, сформированного третьим ждущим мультивибратором 36, и формирует импульс. Таким образом, в ответ 5 на каждый входной импульс блок 1 б формирует на своих выходах по одному импульсу определенной длительности и с определенными временными сдвигами.

Накопитель 17 предназначен для на0 копления зарядов, поступающих на его входы, и формирования управляющего сигнала и работает следующим образом,

На входы накопителяф 17 поступают импульсы заданной длительности с пере5 менной амплитудой и с заданным времен-. ным сдвигом. Под действием упомянутых импульсов заряжаются конденсаторы 43 и 45 накопительных RC-цепей, R 42, С 43 и R 44, С 45. Постоянная времени накопитель0 ных RC-цепей выбрана такой, чтобы за время импульса соответствующий конденсатор успел зарядиться до амплитудного значе-. ния импульса, Напряжение с конденсаторов 43, 45 через соответствующие повторители

5 напряжения 38, 39 поступают на делитель напряжения, состоящий из резисторов 40 и 41. На выходе делителя формируется потенциал, равный среднему арифметическому значению напряжений, поступающих на его

0 входы.

Блок 11 динамической памяти предназначен для переноса информационного сигнала с тактовой частоты записи f3 на тактовую частоту считывания fen путем иск5, лючения из него в процессе записи и считывания имеющихся в нем положительных и отрицательных вставок.

Блок 11 динамической памяти работает следующим образом.

0 На вход распределителя 46 записи поступает последовательность тактовых импульсов записи (f3). Из этой последовательности, исключены импульсы, соответствующие (совпадающие, по времени) импульсам положи5 тельных вставок.

В любом тактовом интервале формируется импульс только на одном из выходов распределителя 46 записи. В следующем

0 тактовом интервале импульс формируется на следующем выходе и т.д. до последнего выхода. В следующем тактовом интервале импульс формируется на первом выходе, и этот процесс повторяется. Во время паузы

5 в.последовательноети входных тактовых импульсов импульс, сформированный на одном из выходов, на следующий выход не продвигается. Дальнейшее продвижение импульсагпо выходам начинается после окончания паузы.

Аналогичным образом работает распределитель 47 считывания, так как на его вход поступает тактовая последовательность, из которой исключены импульсы, соответствующие (совпадающие по времени) отрицательным вставкам.

Импульсы, формируемые распределителем 46 записи, используются для управления процессом записи цифрового сигнала в ячейки памяти, который поступает на первые (информационные) входы элементов 50 памяти всех ячеек 48 памяти. Запись символов цифрового сигнала в ячейки 48 памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя 46 записи. Символы, совпадающие с паузами в тактовой последовательности записи, в ячейки памяти не записываются.

С выхода элемента памяти 50 символ цифрового сигнала поступает на вход элемента И 49; при поступлении на его второй вход импульса считывания названный символ проходит на его выход, т.е. на выход соответствующей ячейки 48 памяти.

Считывание символов цифрового сигнала из ячеек 48 памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя 47 считывания. При наличии паузы в тактовой последовательности считывания приостанавливается продвижение импульса по распределителю считывания, а на выходе блока 11 динамической памяти сохраняется предыдущий символ информационного сигнала.

Считываемые символы цифрового сигнала объединяются с помощью элемента ИЛИ 51 и поступают на выход блока 11 динамической памяти.

Коммутатор 13 предназначен для подключения входного аналогового сигнала к первому или второму выходам,

У коммутатора 13 первый вход является сигнальным, второй и третий входы - управляющими входами, а первый и второй выходы - сигнальными выходами коммутатора.

Под действием управляющего сигнала, поступающего на второй вход, коммутатор подключает входной сигнал к первому выходу, а под действием управляющего сигнала, поступающего на третий вход, - к второму выходу.

Временной детектор 4 предназначен для формирования импульсов, равных по длительности временному сдвигу между входными импульсами.,

. Импульсом, поступающим на S-вход, триггер устанавливается в состояние лог.1, поступающим на R-вход- в состояние лог,0н. Отсюда ясно,, что на выходе триггера формируются импульсы с длительностью, равной временному сдвигу входных .импульсов.

Буферный регистр 18 предназначен для хранения числа от одного управляющего импульса до следующего.

С помощью импульса, поступающего на (т+1)-й вход регистра 18, осуществляется запись числа, присутствующего на его m входах. Записанное число хранится в реги0 стре до следующего импульса на (т+1)-м входе, которым записывается следующее числб и хранится до следующего импульса и тзд. Отсюда ясно, что на выходах регистра 18 число меняет свое значение только в мо5 менты записи.

.Делитель 5 частоты предназначен для деления тактовой частоты считывания до значения, допустимого для аналого-цифро- вого преобразователя 19.

0 Делитель 5 частоты представляет собой n-разрядный счетчик импульсов, где п определяется ИЗ УСЛОВИЯ 2n f3/fmax АЦП, ГД6 fmax АЦП - максимально допустимая -тактовая частота аналого-цифрового преобразо5 вателя. Делитель 5 частоты осуществляет деление входной тактовой частоты на 2.

Устройство фазовой автоподстройки частоты работает при условии равенства номинальных значений тактовых частот

0 записи и считывания. Последовательность тактовых импульсов записи поступает на второй вход первого элемента И2, на первый вход которого поступают импульсы положительных вставок. Импульсы вставок

5 имеют длительность один тактовый интервал. Тактовые импульсы, совпадающие по времени с импульсами вставок, на выход элемента И2 не проходят. Таким путем образуются паузы в последовательности так0 товых импульсов записи. При этом на второй вход блока 11 динамической памяти поступает последовательность тактовых импульсов записи, содержащая только импульсы, совпадающие по времени с теми

5 символами цифрового сигнала, которые необходимо перенести на частоту считывания (например, с информационными символами, символами синхросигнала и т.д.), а импульсы, совпадающие с исключаемыми

0 символами цифрового сигнала (с символами положительных вставок), из тактовой последовательности исключены, т.е. образуется пауза.

На первый вход блока 11 динамической

5 памяти поступает информационный сигнал. Последовательность тактовых импульсов считывания с выхода генератора тактовых импульсов, поступает на второй вход второго элемента И 3, на первый вход которого поступают импульсы отрицательных

вставок, имеющих длительность один тактовый интервал. Тактовые импульсы, совпадающие по времени с импульсами вставок, на вход элемента И 3 не проходят. Таким путем образуется пауза в последовательности импульсов считывания. Эта последовательность поступает на третий вход блока 11 динамической памяти,.

Так как последовательности тактовых Импульсов записи и считывания не синхронизированы, то они имеют отличие по частоте в пределах заданного допуска. При этом временной интервал между моментами записи и считываний изменяется после каждого считывания на величину Дх Т3-ТСч,

где Т / fa , / fc4.

Рассмотрим работу устройства с момента включения, т.е. с режима поиска синхронизма.

В этом режиме временной интервал между моментами записи и считывания, изменяется по линейному закону в пределах отОдоиТсч, где L- количество ячеек памяти в блоке 11 динамической памяти. В тех же пределах изменяется длительность импульсов на выходе временного детектора 4, а усредненное значение напряжения изменяется от 0 до амплитудного значения этих импульсов Уимп, где Уимп (амплитуда HMJ пульсов на выходе временного детектора) спадает до нуля и снова нарастает и т.д., т.е. изменяется по пилообразному закону с периодом L/ Нз-Тсч (фиг.7 А). Напряжение на выходе второго фильтра 14 нижних частот изменяется также по пилообразному закону, с тем же периодом и размахом Un Уимп (фиг.7 Б) и поступает на входы блока 12 контроля и коммутатора 13. Блок 12 контроля формирует сигналы аварии (фиг.7 В) и захвата (фиг.7 В) и захвата (фиг.7 Г3.

На фиг.7 ГЗ сигнал захвата не показан, чтобы продемонстрировать режим поиска в полном объеме: режим прерывания поиска и переход в режим захвата показаны на фиг.9.

Сформированные блоком 15 управления управляющие импульсы (Д) поступают на вход блока Сформирования временных интервалов, который формирует управляющие импульсы для управления работой коммутатора 13 (фиг.7 Е, Ж) и. аналого-циф- рового преобразователя 19 (фиг.7 3). При наличии импульса (фиг.7 Е) коммутатор 13 передает входной сигнал на первый выход (фиг.7 И), а при наличии импульса (фиг.7 Ж) - на второй выход (фиг.7 К). В остальное время коммутатор 13 закрыт. Накопитель 17 формирует сигнал, равный по уровню среднему арифметическому (фиг,7 Л) амплитуд импульсов (фиг,7 И, К). Сигнал (фиг.7 Л) поступает на второй вход аналого-цифрового преобразователя 19, который под действием тактового сигнала, поступающего с дели- теля 5 частоты на третий вход, и управляющих импульсов (фиг.7 3), поступающих на первый вход, преобразует сигнал (фиг.7 Л) в цифровую форму (т-разрядное

число) (фиг.7 М). После окончания преобразования на (т+1)-м выходе аналого-цифрового преобразователя 19 формируется импульс Конец преобразования (П), которым число записывается в буферный ретистр 18 (фиг.7 М) и поступает на входы цифроаналогового преобразователя 6, Пре- образователь 6 преобразует число в аналоговый сигнал (фиг.7 О). Полученный сигнал поступает на второй вход сумматора 7. а на

первый его вход поступает управляющий сигнал с выхода второго фильтра 14 нижних частот, Коэффициент суммирования по первому входу значительно меньше, чем по второму (Ki«K2 1) и выбирается таким,

чтобы при наличии на первом входе сигнала с размахом Uy на выходе управляющий сигнал изменялся на величину одного уровня квантования Ди. Полученный сигнал с выхода сумматора 7 через первый фильтр 5

нижних частот поступает на вход генератора тактовых импульсов, состоящего из последовательно соединенных усилителя постоянного тока, управляемого синусоидального генератора и компаратора. Сину„соидальный сигнал с выхода управляемого генератора поступает на вход компаратора, который формирует прямоугольные импульсы той же частоты (fen) - тактовые импульсы. Под действием управляющего сигнала генератор тактовых импульсов перестраивается в сторону уменьшения расстройки.

Импульс Конец преобразования (П) через блок 15 управления поступает на вход блока 16 формирования временных интервалов и запускает его. С этого момента начинается следующий цикл работы блоков: блока 16 формирования временных интервалов, коммутатора 13, накопителя 17, аналого-цифрового преобразователя 19 и блока

15 управления, т.е. замыкается кольцо поиска (импульсы фиг.7 П, Д, 3). Длительность цикла в кольце поиска (период поиска Т) определяется временем задержки импульса (фиг.7 3) по отношению к импульсу (фиг.7

Д) ДТф и временем преобразования в ана- лого-цифровом преобразователе ДТдцпх хТп ДТф+ ДТдцп . Причем Тп ТСч«Тс, где Тс - период согласования частот (период следования вставок). При этом обеспечивается быстрая перестройка генератора тактовых импульсов, что уменьшает время поиска.

В режиме захвата при поступлении на вход положительного стаффинга или вход отрицательного стаффинга блока 15 управления импульса положительного или отрицательного стаффинга соответственно или на вход запрета импульса захвата (фиг.9 ГЗ) блок 15 управления переходит в режим за- хвата. При этом на выход блока проходит поступивший импульс, а кольцо поиска размыкается. Частота и фаза генератора тактовых импульсов подстраивается к установившимся значениям (фиг.9).

При этом уменьшаются величины изменения: временного интервала между моментами записи и считывания в блоке 11 динамической памяти, длительности импульсов на выходе временного детектора 4 и усредненного значения напряжения этих импульсов до величины Uy. Прекращается формирование импульсов аварии и захвата блоком 12 контроля (фиг.9 В, ГЗ), а управление осуществляется импульсами вставок (фиг.9, П, Г2). В промежутках времени между импулсами вставок (фиг.9, П, П2) управляющий сигнал остается неизменным. Значение управляющего сигнала изменяется только при поступлении вставки. В этом режиме подстройка генератора тактовых импульсов происходит медленнее, чем в режиме поиска. Временное положение (фаза) тактовых импульсов подстраивается к установившемуся значению. Далее значение уп- равляющего сигнала остается неизменным, что исключает временные флюктуации тактовых импульсов, и наступает установившийся режим.

Из изложенного выше видно, что управ- лающий сигнал имеет дискретные значения, а следовательно, и частота тактового генератора также имеет дискретные значения, что является причиной ухода временного положения тактовых импульсов от устано- вившегося значения при сверхнизких частотах следования вставок. Для устранения этого недостатка используется сумматор 7, в котором рассматриваемый управляющий сигнал складывается с ослабленным управ- ляющим сигналом, снимаемым с Выхода второго фильтра 14 нижних частот. С помощью последнего осуществляется-регулирование частоты генератора в промежутках

между дискретными значениями. .

. Так как управляющий сигнал на выходе второго фильтра 14 нижних частот имеет переменную составляющую (пилообразную), то и в суммарном управляющем сигнале присутствует переменная составляющая,

которая приводит к временным флюктуаци- ям тактовых импульсов.

При медленных изменениях фазы входного сигнала (тактовой последовательности), обусловленной нестабильностью тактовых генераторов записи и считывания на передающей стороне системы связи, устройство осуществляет подстройку фазы генератора тактовых импульсов, как это описано в режиме захвата.

Формула изобретения 1. Устройство фазовой автоподстройки частоты, содержащее первый инвертор, временной детектор, делитель частоты, цифроаналоговый преобразователь (ЦАП) и последовательно соединенные сумматор, первый фильтр нижних частот (ФНЧ) и генератор тактовых импульсов, отличающееся тем, что, с целью повышения степени ослабления временных флюктуации тактового сигнала путем выделения постоянной составляющей управляющего сигнала, введены буферный регистр, аналого-цифровой преобразователь (АЦП), накопитель, блок формирования временных интервалов, коммутатор, второй инвертор, первый и второй элементы И, блок контроля, блок управления, второй ФНЧ и блок динамической памяти, первый вход и первый выход которого являются соответственно информационным входом и информационным выходом устройства, при этом второй и третий выходы блока динамической памяти подключены соответственно к первому и второму входам временного детектора, выход которого через второй ФНЧ подключен к входу блока контроля, первому входу сумматора и первому входу коммутатора, первый и второй выходы которого подключены соответственно к первому и второму входам накопителя, причем первый вход блока управления является входом положительного стаффинга устройства и через первый инвертор подключен к первому входу первого элемента И, второй вход которого является тактовым входом устройства, а выход первого элемента И подключен к второму входу блока динамической памяти, к третьему входу которого подключен выход второго элемента И, при этом второй вход блока управления является входом отрицательного стаффинга и через второй инвертор подключен к первому входу второго элемента И, к второму входу которого и входу делителя частоты подключен выход генератора тактовых импульсов, а первый и второй выходы блока контроля подключены соответственно к входу запрета, а информационному .входу блока управления, выход которого подключен к входу блока формирования временных интервэпоа, первый, второй и третий выходы которого подключены соответственно к второму и третьему входам коммутатора и первому входу АЦП, к второму и третьему входам которого подключены выходы соответственно накопителя и делителя частоты, а т+1 выходов АЦП подключены к т+1 выходам буферного регистра, m выходов которого подключены к m входам ЦАП, выход которого подключен к второму входу сумматора причём (т+1)-й выход АЦП подключен к управляющему входу блока управления.

2. Устройство по п. 1,отличающее- с я тем, что блок контроля содержит первый, второй и третий источники опорных напряжений, первую и вторую дифференцирующие цепи, первый, второй и третий компараторы, элемент ИЛИ, выпрямитель и элемент ЗАПРЕТ, выход которого является первым выходом блока контроля, вторым выходом которого является выход элемента ИЛИ, подключенный к первому входу элемента ЗАПРЕТ, к второму входу которого подключен выход выпрямителя, при этом выходы первого и второго источников опорного напряжения подключены к инверсным входам соответственно первого и второго комрараторов, выходы которых подключены соответственно к входу второй дифференцирующей цепи и первому входу элемента ИЛИ, к второму входу которого подключен выход третьего компаратора, к прямому входу которого подключен выход третьего источника опорного напряжения, причем к прямому входу второго компаратора и инверсному входу третьего компаратора подключен выход первой дифференцирующей цепи, вход которой соединен с прямым входом первого компаратора и является входом блока контроля, а выход второй дифференцирующей цепи подключен к входу выпрямителя.

3. Устройство по п. 1, отл и ч а ю щ е.е- с я тем, что блок управления содержит элемент ИЛИ, RS-триггер и коммутатор, выход которого является выходом блока управления, входом положительного стаффинга,

входом отрицательного стаффинга и входом

.запрета которого являются соответственно

первый, второй и третий входы элемента

ИЛИ, выход которого подключен к второму

входу коммутатора и R-входу RS-триггера, S-вход которого соединен с первым входом коммутатора и является информационным входом блока управления, при этом прямой выход RS-триггера подключен к третьему и

четвертому входам коммутатора, а инверсный выход RS-триггера - к пятому входу коммутатора, шестой вход которого является управляющим входом блока управления.

4. Устройство по п. 1. о т л и ч а ю щ е е- с я тем, что блок формирования временных интервалов содержит последовательно соединенные по инверсным выходам первый, второй, третий и четвертый ждущие мультивибраторы, при этом прямые выходы первого, третьего и четвертого ждущего мультивибраторов являются соответственно первым, вторым и третьим выходами блока формирования временных интервалов, входом которого является вход первого жду- щего мультивибратора.

5. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что накопитель содержит первый и второй повторители напряжения, делитель напряжения, состоящий из первого и второго резисторов, первые выводы которых объединены и являются выходом накопителя, а вторые выводы первого и второго резисторов соединены с выходами соответственно первого и второго повторителей напряжёния, а также две накопительные цепи, каж- дая из которых состоит из резистора и

конденсатора, первый вывод которого соединен с общей шиной, при этом первые выводы резисторов первой и второй

накопительных цепей являются соответственно первым и вторым входами накопителя, при этом вторые выводы резисторов первой и второй накопительных цепей соединены с вторыми выводами конденсаторов

соответствующей накопительной цепи и входами соответственно первого и второго повторителей напряжения.

Фив. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

| Многоканальное устройство передачи и приема асинхронных цифровых сигналов | 1988 |

|

SU1555886A1 |

| Устройство для контроля многоканальной системы связи с временным разделением каналов | 1974 |

|

SU563734A1 |

| Устройство для контроля параметров электрических сигналов | 1983 |

|

SU1250971A1 |

| Устройство для передачи и приема цифровых сигналов с положительным стаффингом | 1975 |

|

SU657634A1 |

| Приемник команд стаффинга | 1982 |

|

SU1075433A1 |

| Передающее устройство телеизмерительной системы | 1986 |

|

SU1483476A1 |

Изобретение относится к электросвязи, а именно к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне. Цель изобретения - повышение степени ослабления временных флюктуации тактового сигнала путем выделения постоянной составляющей управляющего сигнала. Устройство содержит инвертор 1, элементы И 2, 3, временной детектор 4, делитель 5 частоты, цифроана- логовый преобразователь 6, сумматор 7, фильтр 8 нижних частот (ФНЧ), генератор 9 тактовых импульсов, инвертор 10, блок 11 динамической памяти, блок 12 контроля, коммутатор 13, ФНЧ 14, блок 15управле-. ния, блок 16 формирования временных интервалов, накопитель 17, буферный регистр 18, аналого-цифровой преобразователь 19. Сущность изобретения заключается в выделении постоянной составляющей спектра управляющего сигнала и использовании его -для управления генератором тактовых импульсов. 4 з.п. ф-лы, 10 ил. Ё

л

Ј

«ILL

з1И

w

м

мIXТП XТТХ X X Х-X X X У X XX X

//II I I И. I I 111 I II 111 III о I М- I I -M I 111 1 ГПТТ

Я II 88 II

Фиг. 7

s

C3

H. «C

«Xl

Г ft &

Я.

гз

Ill П И

.

Фиг. 10

| Левин Л.С., Плоткин М.А | |||

| Цифровые системы передачи информации | |||

| М.: Радио и связь | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-04-23—Публикация

1991-06-24—Подача