Изобретение относится к технике связи, преимущественно к системам автоматического вхождения в связь, и может использоваться для анализа команд управления, представляющих собой рекуррентные псевдослучайные последовательности.

Цель изобретения - повышение помехоустойчивости.

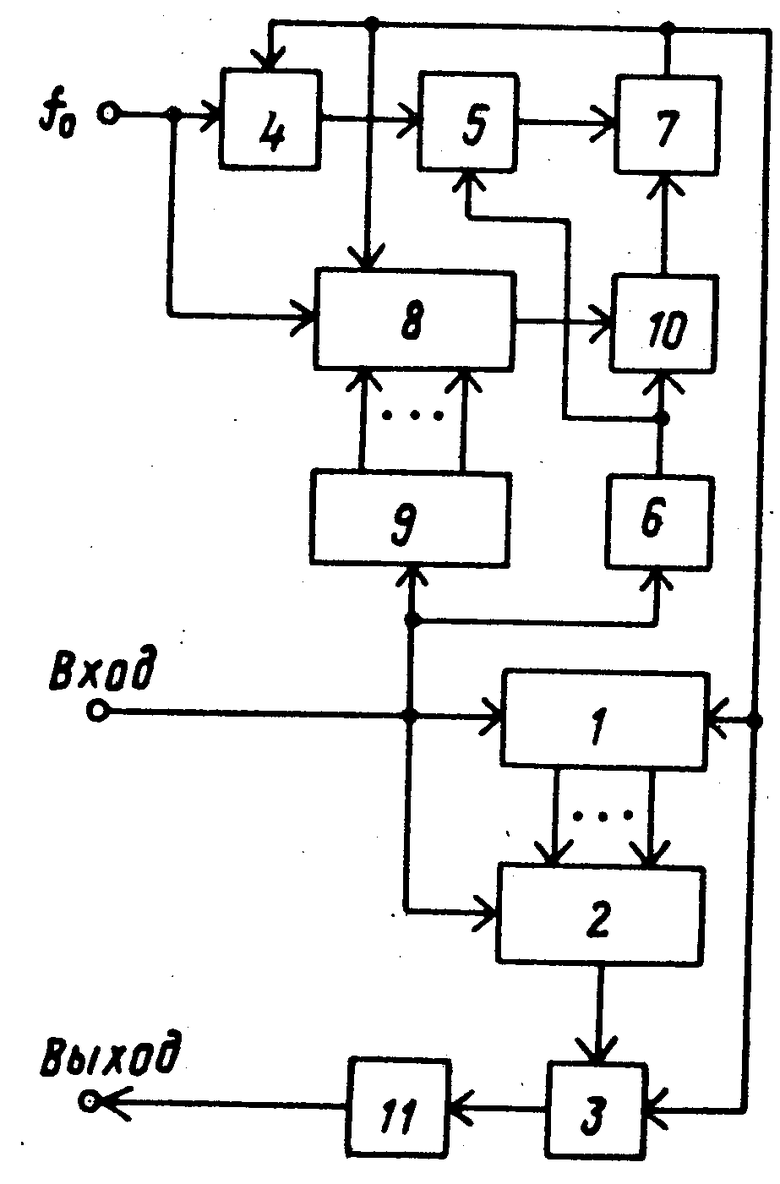

На чертеже приведена структурная схема анализатора последовательности посылок с переменным тактовым интервалом.

Анализатор последовательности посылок с переменным тактовым интервалом содержит регистр сдвига 1, сумматор 2, блок стробирования 3, ключ 4, делитель частоты 5, выпрямитель фронта импульса 6, триггер 7, делитель с переменным коэффициентом деления 8, блок установки 9, элемент ИЛИ 10, таймер 11.

Анализатор последовательности посылок с переменным тактовым интервалом работает следующим образом.

Входной сигнал поступает в сумматор 2, где он сравнивается с результатом суммирования соответствующих разрядов регистра сдвига 1, и, если результат сравнения положительный, то нулевой сигнал с выхода сумматора 2 через блок стробирования 3 поступает на установочный вход таймера 11, но установку не производит в силу своего нулевого значения. По истечении времени, необходимого для выработки синхронизирующего импульса, информация записывается в регистр сдвига 1 и процесс повторяется. Однако, если результат сравнения в сумматоре 2 будет отрицательным, т.е. единичным, то он сбрасывает таймер 11 в начальное состояние. Рассмотрим подробнее процесс формирования импульсов синхронизации. Очередная смена полярности элементов приходящей последовательности обеспечивает формирование импульса на выходе выделителя фронта импульса 6, который устанавливает делитель частоты 5 в нулевое состояние, а триггер 7 - в единичное, в результате чего открывается ключ 4 и делитель частоты 5 начинает счет. Досчитав до определенного времени, обеспечивающего окончание переходных процессов, делитель частоты 5 выдает сигнал и закрывает через триггер 7 ключ 4, тем самым прекращая счет. На блок стробирования 3 и делитель с переменным коэффициентом деления 8 поступает разрешающий сигнал. Делитель с переменным коэффициентом деления 8 начинает счет в соответствии с полярностью элемента последовательности, действующего на входе блока установки 9. Через некоторый интервал времени делитель с переменным коэффициентом деления 8 выдает сигнал, который устанавливает через элемента ИЛИ 10 триггер 7 в единичное состояние, обеспечивая тем самым открывание ключа 4, сброс делителя с переменным коэффициентом деления 8 и закрывание блока стробирования 3. Открывание ключа 4 обеспечивает возможность продолжения счета делителем частоты 5, который отсчитывает период и снова выдает передний фронт выходного импульса, который сбрасывает триггер 7 в нулевое состояние и весь цикл работы повторяется. Если в этот момент приходит смена полярности, то этим самым изменяются, коэффициент счета делителя с переменным коэффициентом деления 8 и делитель формируемого им интервала. Изменение длительностей интервалов, формируемых делителем с переменным коэффициентом деления 8, обеспечивает формирование в момент реальных или возможных смен полярностей элементов кода, одинаковых защитных интервалов, когда запрещено прохождение сигналов через блок стробирования 3. Остальное время предоставлено возможному прохождению сигналов с выхода сумматора 2. Импульсы разрешения, которые меняются в такт с приходящей информацией, обеспечивают адаптивное изменение длительности возможного действия помехи, что позволяет осуществлять прием сигналов с различными тактовыми интервалами при одинаковом времени интегрирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема рекуррентных кодовых последовательностей | 1984 |

|

SU1197127A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА АДРЕСНОЙ ПОСЫЛКИ | 1986 |

|

RU1391482C |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1986 |

|

SU1338102A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ДВОИЧНОЙ СИСТЕМЫ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ с ЧАСТОТНО- ВРЕМЕННЫМ КОДИРОВАНИЕМ | 1973 |

|

SU389632A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Система селективного вызова | 1985 |

|

SU1309330A1 |

| Устройство синхронизации с М-последовательностью | 1985 |

|

SU1312750A2 |

| Генератор квазирегулярных последовательностей импульсов | 1981 |

|

SU991589A2 |

Изобретение может быть использовано для анализа команд управления, представляющих собой рекурентные псевдослучайные последовательности. Цель изобретения - повышение помехоустойчивости. Устройство содержит регистр сдвига 1, сумматор 2, блок 3 стробирования, ключ 4, делитель 5 частоты, выделитель 6 фронта импульса. Вновь введены триггер 7, делитель 8 с переменным коэффициентом деления, блок 9 установки, элемент ИЛИ 10, таймер 11. Импульсы разрешения, которые меняются в такт с приходящей информацией, обеспечивают адаптивное изменение длительности возможного действия помехи, что позволяет принимать сигналы с различными тактовыми интервалами при одинаковом времени интегрирования. 1 ил.

АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОСТИ ПОСЫЛОК С ПЕРЕМЕННЫМ ТАКТОВЫМ ИНТЕРВАЛОМ, содержащий регистр сдвига, сумматор, блок стробирования, ключ, делитель частоты, выделитель фронта импульса, причем выходы регистра сдвига соединены соответственно с входами сумматора, дополнительный вход которого соединен с входом выделителя фронта импульса, выход которого соединен с первым входом делителя частоты, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены триггер, делитель с переменным коэффициентом деления, блок установки, элемент ИЛИ, таймер, вход которого соединен с выходом блока стробирования, первый вход которого соединен с выходом сумматора, второй вход блока стробирования соединен с первым входом регистра сдвига, первым входом ключа, первым входом делителя с переменным коэффициентом деления и выходом триггера, первый вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом выделителя фронта импульса, второй вход элемента ИЛИ соединен с выходом делителя с переменным коэффициентом деления, второй вход которого соединен с вторым входом ключа, третьи входы делителя с переменным коэффициентом деления соединены соответственно с выходами блока установки, вход которого соединен с входом выделителя фронта импульса и вторым входом регистра сдвига, второй вход делителя частоты соединен с выходом ключа.

| Авторское свидетельство СССР N 824485, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-01-27—Публикация

1985-10-14—Подача