Изобретение относится к области передачи неподвижных изображений, может быть использовано в системах синхронизации, и является усовершенствованием устройства по авт. св. № 1188903.

Цель изобретения - уменьшение времени обнаружения.

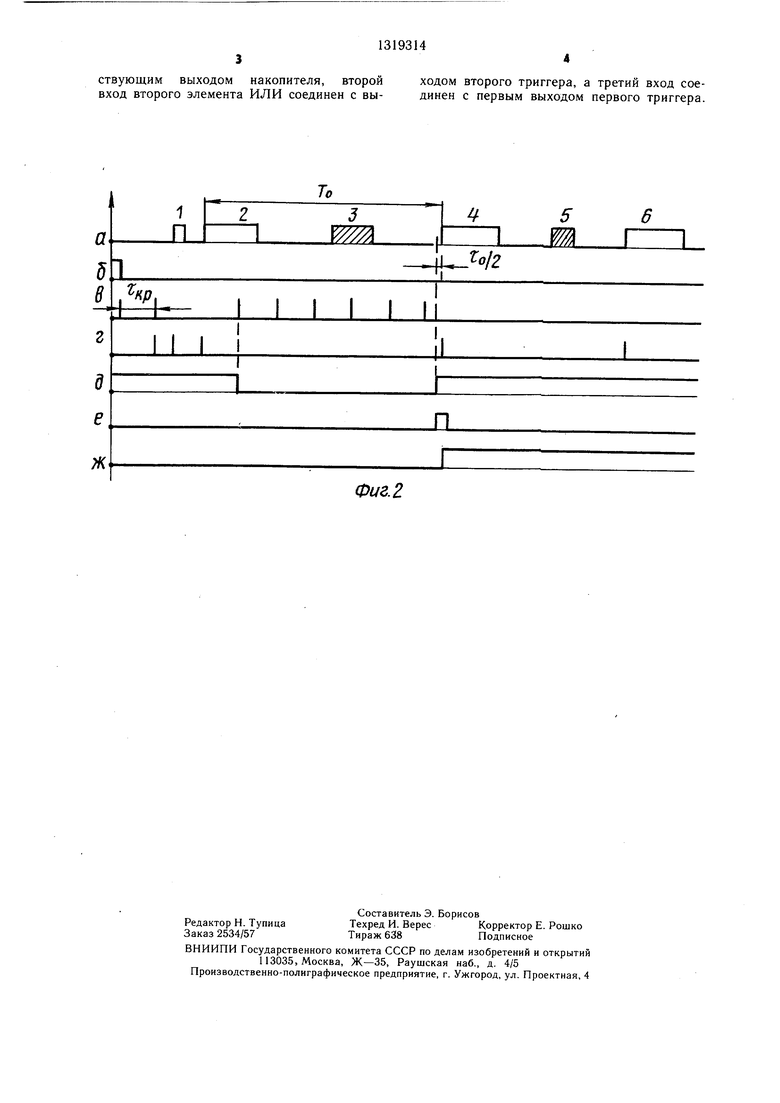

На фиг. 1 представлена электрическая структурная схема устройства обнаружения факсимильных фазовых импульсов; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство обнаружения факсимильных фазовых импульсов содержит формирователь 1 импульсов сброса, накопитель 2, первый 3 и второй 4 триггеры, первый 5 и второй 6 элементы И, коммутатор 7 импульсов, входную шину 8, выходную шину 9, установочную шину 10, первый элемент ИЛИ 11, инвертор 12, третий элемент И 13, второй элемент ИЛИ 14, третий триггер 15.

Коммутатор 7 импульсов содержит элемент ИЛИ 16, первый 17 и второй 18 элементы И, инвертор 19. Формирователь 1 импульсов сброса содержит элемент И 20, первый 21, второй 22 и третий 23 инверторы. Накопитель 2 выполнен в виде счетчика 24.

Устройство обнаружения факсимильных фазовых импульсов работает следующим образом.

После снятия сигнала начальной установки с установочной шины 10 на выходной шине 9 формируется уровень логического нуля (фиг. 2 б). Это связано с подачей уровня логического нуля с выхода первого триггера 3 на вход второго элемента И 6. Этот уровень существует до срабатывания первого триггера 3. До этого времени с выходов первого триггера 3 на управляющие входы коммутатора 7 импульсов поступают уровни логического нуля и логической единицы, разрешая прохождение через него на вход формирователя 1 импульсов сброса положительных импульсов с информационного входа.

Короткие положительные импульсы с выхода формирователя 1 подаются на вход накопителя 2, устанавливая его в нулевое состояние. Необходимые для счета импульсы с частотой „ подаются на счетный вход накопителя 2 (фиг. 2 г). Отсчеты интервалов времени с накопителя 2 поступают на первый элемент И 5, а отсчет, равный Тхр (положительный перепад), поступает на вход третьего элемента И 13. При отсутствии входных импульсов на входной шине 8 на других входах третьего элемента И 13 присутствует уровень логической единицы (фиг. 2 д). После отсчета накопителем 2 интервала tup положительный перепад подается на вход третьего элемента И 13 (фиг. 2 в) и с его выхода через элемент ИЛИ 16 коммутатора 7 поступает на вход формирователя 1. При этом накопитель 2

с сбрасывается и счет начинается заново, т.е. ведется поиск входных импульсов с длительностью больше Тхр . При этом входные импульсы короче «Скр меняют лишь начало отсчета в накопителе 2, но не влияют на состояние третьего триггера 15. Если

0 длительность входного импульса больше txp, то через интервал времени Сцр срабатывает третий триггер 15 за счет подачи на его входы уровня логической единицы и положительного перепада после отсчета

5 tup накопителем 2. С этого момента с его выхода подается запирающий потенциал на вход формирователя 1, блокируя сброс накопителя 2 от любых импульсов на время То /2, так как после этого осуществляется разблокировка формирователя

0 1 путем возврата третьего триггера 15 в исходное состояние (фиг. 2 ж). Происходит это от положительного импульса (фиг. 2 е), который появляется через интервал времени Т« ., /2, считая от переднего

5 фронта предполагаемого фазового импульса (фиг. 2 а, импульс 2). При этом, если в момент подачи этого импульса длительностью to на вход первого триггера 3 на его счетном входе появляется положительный перепад от входного импульса, то первый

0 триггер 3 срабатывает, с этого момента переводит устройство на выработку фазовой последовательности с периодом Т„ и смешением начальной фазы не более, чем на ± t./2. Входные импульсы из канала связи запираются коммутатором 7 за счет подачи

5 на его вход соответствующих логических сигналов.

Формула изобретения

Устройство обнаружения факсимильных фазовых импульсов по авт. св. № 1188903, отличающееся тем, что, с целью уменьшения времени обнаружения, введены последовательно соединенные первый элемент ИЛИ, первый вход которого соединен с вход5 ной щиной устройства обнаружения факсимильных фазовых импульсов, инвертор и третий элемент И, выход которого соединен с дополнительным входом коммутатора импульсов, а также последовательно соединенные второй элемент ИЛИ, первый вход ко0 торого соединен с установочной шиной устройства обнаружения факсимильных фазовых импульсов, и триггер, первый выход которого через второй вход первого элемента ИЛИ подключен к его второму входу,

г второй в ыход соединен с дополнительным входом формирователя импульсов сброса, а третий вход объединен с вторым входом третьего элемента И и соединен с соответ13193143

ствующим выходом накопителя, второйходом второго триггера, а третий вход соевход второго элемента ИЛИ соединен с вы- динен с первым выходом первого триггера.

Редактор Н. Тупица Заказ 2534/57

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

Составитель Э. Борисов

Техред И. ВересКорректор Е. Рошко

Тираж 638Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения факсимильных фазовых импульсов | 1984 |

|

SU1188903A1 |

| Устройство двухступенчатого автоматического фазирования факсимильного аппарата | 1984 |

|

SU1238265A2 |

| Устройство синхронизации | 1984 |

|

SU1241506A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Устройство для магнитной записи-воспроизведения речевых сигналов | 1990 |

|

SU1739384A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Формирователь импульсов | 1979 |

|

SU790186A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Цифровой усредняющий фазометр | 1983 |

|

SU1219982A1 |

Изобретение может использоваться в системах синхронизации при передаче неподвижных изображений и является усовершенствованием устр-ва по авт. св. № 1188903. Цель изобретения - уменьшение времени обнаружения. Устр-во содержит формирователь 1 импульсов сброса, накопитель 2, триггеры 3, 4, 15, элементы И 5, 6, 13, коммутатор 7 импульсов, элементы ИЛИ 11, 14,инвертор 12. Формирователь 1 состоит из элемента И 20 и инверторов 21-23. Коммутатор 7 состоит из элементов ИЛИ 16, И 17, 18 и инвертора 19. Отсчеты интервалов времени с накопителя 2 поступают на элементы И 5, а отсчет Ткр - на элемент И 13. При отсутствии импульсов на входной шине 8 на других входах элемента И 13 присутствуют «1. После отсчета интервала Скр импульс с элемента И 13 через элемент ИЛИ 16 поступает на формирователь 1, который формирует сигнал сброса накопителя 2. Т. обр. ведется поиск входных импульсов длительностью больше . Если длительность входного импульса больше Тхр , то через интервал Тцр сработает триггер 15 и его запирающий потенциал блокирует сброс накопителя 2 от любых и.мпульсов на определенное время. После окончания этого интервала на триггер 3 подается импульс длительностью Та , и если в этот момент на его счетном входе появится положит, перепад от входного импульса, то сработает триггер 3 и устр-во начнет формировать фазовую последовательность. Введены элементы 11 -15, 2 ил. (Л 00 со со м Физ. 1

| Устройство обнаружения факсимильных фазовых импульсов | 1984 |

|

SU1188903A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-02—Подача