, 1. .

Изобретение относится к вычислительной технике |i может быть использовано при построении запоминающих устройств .цифровых универса/ьных и спениализиро ванных машин.,

Известно запоминающее устройство, состоящее из блока управления, цешифратора кода ацреса, элементов И, формирователей ГОКОВ считьтакия и записи, фор- . мирователей токов запрета, накопителя с д пополнительным разрядом, усилителей воспроизведения, усилителёЯг стробирования, регистра числа и триггера Il.

Однако устройство не обеспечивает надежной работ,ы при несогласованных J5 между собой режимах записи и считывания.

Известно также буферное запоминающее устройство (БЗУ), состоящее из- четырехразрядных регистров сдвига, накопи-20 теля, устройства ввода, устройства вывода, элементов И, блока синхронизации, элементов ИЛИ, счетчика и генератора одиночных импульсов 12 J.

Основным недостатком данного устройства является невысокое быстро действие и большое время ожидания информация изкза последовательного действия БЗУ.

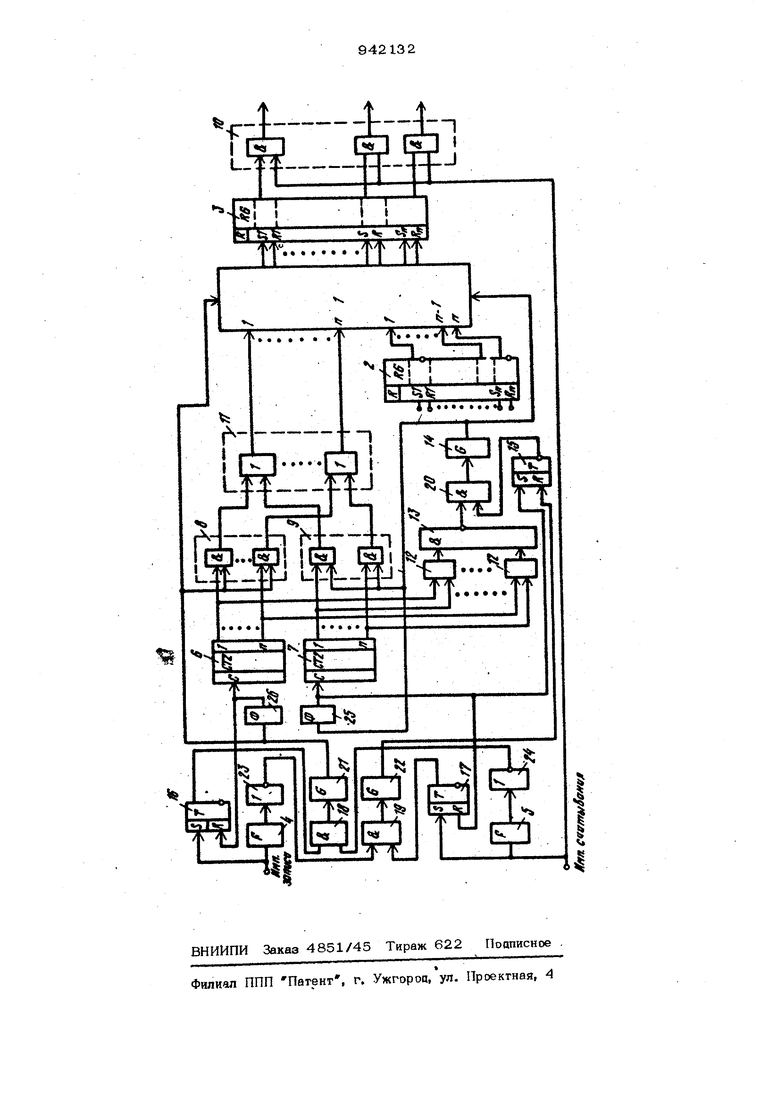

Наиболее близким к предлагаемому по теашической сущности является устройство, содержащее магнитный накотштель на сердечниках с ишнами адреснов и разря|гнсА записи, шкнами опроса и выхою, раа рядный и адресный счетчики, генераторы записи и опроса, схему контроля аапапие ния накопителя и схемы эадервкххи Оополнк тельный блок памяти на элементах со счн« тыванием без разрушения информации, генератор сброса и коммутатор опроса. Ши-; ны чтения (записи) элементов памяти дополнительного блока памяти соединевы последовательно с соответствующими пшнамя магнитного накопителя, шина опроса подключена к генератору опроса через коммутатор опроса, соединенный в свою очереда со схемой контроля заполнения накопителя. Шина сброса через генератор сброса подключена ко ВХОЕ записи магнитного нако пителя Гз. Недосгагками устройства являются сло жность и невысокое быстродействие в слу чае необхопимости совмещения режимов записи и считьюания. Цель изобретения - повышение бьгстродействия. Поставленная цель достигается тем, чт в известное буферное запоминающее устройство введены три группы элементо И, элементы равнозначности, элемент ИНЕ, К -S триггеры, формирователи импуль сов записи и. считьшания, инверторы, дополнительные генераторы одиночных Импульсов, элементы задержки, э кменты И, группа элэментов ИЛИ, шина считывания, вход формирователя импульсов записи подключен к шине записи и S -входу первого R -S триггера, единичный выход которог подключен к первому входу первого элемента И, а выход формирователя импульсе® записи подключен через первый инвертор к первому входу второго элемента И, второй вход первого элемента И соединен через второй инвертор .с выходом формирователя импульсов считывания, вхо которого подключен к шине считывания к 5 -входу второго R- 5 триггера, единичный выход которого подкл5очен ко второму входу второго элемента И, выходы элементе И подключены соответственно ко втюдам йоиолнительных генераторов одиночных импульсов, выход первого дополнительного генератора одиночных импульсов подключен ко входу записи накопителя, первым входам элементов И первой группы и через первый элемент задержки к счетному входу счетчика адреса записи и R - входу первого R -S триггера, выход второго дополнительного генератора оияночных импульсов подключен к 1 -входу третьего R- 5 триггера, 6-вход которого подключен к R-вхоцу второго R-Sтpиг , счетному входу счетчика адреса считьюания и выходу второго элемента задержки, вход второго элемента задержки подключен к выходу генератора одиночных импульсов, входу считывания накопителя и первым входам элементов И вторюй группы, вторые входы этих элементе подключены к.выходам сметчика адреса считывания и первым входам элементов равнозначности, вторые входы ко тфых соединены с соответствующими выходами счетчика адреса задаси и вторыми входами элементов И первой группы, выходы элементов равнозначности подключены к входам элэмента И-НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным вь1ходом третьего R- S триггера, а выход - с входом генератора одиночных импульсов, выходы элементов И первой и второй групп подключеты соответственно к первым и вторым входам элементов ИЛИ, выходы которых соединены с адресными входами накопителя, выходы выходного регистра подключены к первым входам элементов И третьей группы, выходы которых являются выходами устройства, а вторые входы элементов И третьей группы подключены к шине считывания. На чертеже представлена функциональная схема БЗУ. Устройство содержит накопитель 1, входной 2 и выходаой 3 регистры, формирователи 4 и 5 импульсов записи,и считывания, счетчики 6 записи и считывания 7, первую 8, вторую 9 и третью 10 группы логических элементов И группу 11 элементов ИЛИ, И логических элементов 12 равнозначности, И-входовой логический элемент И-НЕ 13, генератор 14 одиночных импульсов, R-S триггер 15 управления, R-S триггеры 16 записи и считывания 17, первый 18, второй 19 и третий 20 логические элементы И, первый 21 и второй 22 генераторы баийочного импульса, первый 23 и второй 24 инверторы, первый 25 и второй 26 элементы задержки. Информационные входы накопителя 1 соединены с выходами входного регистра 2, а информационные выходы накопителя через выходной регистр 3 подключены к первым входам э/вментов И третьей группы 10, выходы которых являются вьтодами устройства. Вторые входы элементов И 10 подключены к шине считывания устройства. Шина записи устройства подключена ко входу формирователя4 и S-входу триггера 16, а выход формирователя 4 через инвертор 23 подключен к первому входу второго элемента И 19. Единичный: выход триггера 16 пооключен к первому входу первого элемента И 18. Шина считывания подключена ко входу формирователя 5 и S -входу триггера 17. Выход формирователя 5 через инвертор 24 подключен ко второму входу элемента И 18, а единичный выход триггера 17 соединен со входом второго элемента И 19.

Выход элемента И 18 пооключен ко генератора 21 одиночных импульсов (ГОИ), выход которого соединен со входо элемента 25 задержки, первыми входами элементов И первой группы 8 и входом записи накопителя 1.

Выход элемента 25 задержки соединен с R-входом триггера 16 и счетным входом счетчика 6 адреса загаси, выходы которого подключены ко вторым входам грут пы 8 элементовИ и вторым входам элементов 12 равнозначности.

Выход элемента И 19 подключен ко вхопу ГС81 22, вькод которого подключен в R-BXoqy триггера 15, 5-вход которого подключен к R-BXooy триггера 17, счетному входу счетчика 7 адреса считьша- . ния и выходу элемента 26 ааоержки. Вход элемента 26 задержки подключен к выходу ГОИ 14, вхоцу. считывания накб- пителя 1 и первым группы 9 элементов И, вторые входы которых подсоединены к выходам счетчика 7 и первым входам элементов 12 равнозначнос ти. Выходы элементов 12 подключены ко входам схемы И-НЕ 13, выход которой подключен к первому входу элемента И 2О, а второй вход этого элемента соединен с инверсным вьссодом триггера 15,

Выход элемента И 20 соеоинен со входом ЮИ 14. Выходы группы 8 элементов И подключены к первым входам группы 11 элементов ИЛИ,, а вторые- входы этой группы элементов подсоединены к выходам группы 9 элементов И.

Выходы группы 11 элементов ИЛИ поключены к адресным входам накопителя t

Устройство работает следующим обрвгзом.

В ИСХОДНОМ состоянии счетчики 6 адресов записи и считывания 7, а также . триггеры 15-17 обнулены, на входах входного регистра ii и соответственно на информационных входах накопителя 1 содержится входная информация.

Работа БЗУ нач1шается с режим записи.

Импульс записи поступает на if-вход триггера 16 записи и переводит его в единичное состояние, открывая элемент И 18 по первому входу. В отсутствии импульса считывания на выходе 24 присутствует логическая единица, поэтому при включении триггера 16 записи на выходе элемента И 18 появляется положительный перепад напряжения, по которому ГОИ. 21 вырабатывает импульс записи. Этот импульс открывает логические эламенты И первой группы 8 и разрешает поступление кода с выходов счетчика 6 адреса записи на адресные входы накопителя 1. Кроме того, по этому импульсу происходит запись исходной информации в накопитель по адресу счетчика 6 адреса записи (в данном с;1учае по нулевому). По окончании цикла записи в накопитель этот же импульс записи, задержанный на элементе 25 задержки, сбра сывает триггер записи в О и увеличивает содержимое счетчика 6адреса записи на .

В ре льтате превышения содержимого счетчика 6 адреса записи над содержимым счетчика I адреса считывания на выходе элемента 12 разнозначности, соответствующего младшему разряду счетчиков 6 и 7, появляется отрицательный перепад, вызывающий появление положительного перепада напряжения Нессвпадениена выходе VI-входной схемы И-НЕ 13. В ре1 льтате совпадения перепадов напряжения Несовпадение и единичного cocTOstния инверсного плеча триггера 15 на выходе элемента И 2О возникает положительный перепад напряж«шя, по которому ЮИ 14 вырабатывает импульс Считьюание. Этот импульс открывает вторую группу 9 элементов И, подключив, выходы счетчика 7 адреса считывания через схемы И 9 и ИЛИ 11 к адресным входам накопителя 1,. врезультате чего и происходит считывание информации из накопителя в выходной регистр, затем этот импульс, задержанный на -э/вменте 26 задержки, подтверждает нулевое со-, стояние триггера 17 считывания, устанавливает триггер 15 в единичное состояние, запрещая прохождение потенциала Несовпадение через элэмент И 20, и увеличивает содерисимое счетчика 7 адреса считывания, го приводит к совпадению кодов в счетчиках 6 н 7. Слэдовательно, потенциал Несовпадение на выходе И-НЕ 13 исчезает. На этом заканчивается цикл записи-считывания первого информационного слова.

Аналогично, с приходом любого следующего импульса записи производится 3 пись в накопитель 1 второго и последукшхих информационных слов, а на выходе элемента И-НЕ 13 устанавливается потенциал Несовпадение. При этом в любом случае происходит только одно считывание, так как после первого считывания происходит установ в триггера 15 и блокировка элемента И 2О. 79 При считывании информации из выходного регистра на шину считывания поступает импульс считывания, который разрешает выцачу информации из выходного регистра через э/юменты И 10 на выход устройства. В то же время этот импульс устанавливает в триггер 17 считывания. Если при этом отсутствует импульс записи на шине записи, то на выхоре инвертора 23 присутствует логическая I и при совпадении положительных перепадов на входах элемента И 19 на вьссоде ГСЗИ 22 появляется импульс, кото рый устанавливает в 1 инверсный выхо триггера 15, разрешая прохождение потенциала Несовпадение на вход ГОИ 14 и прсдазводя считывание второго информационного слова .из накопителя в выходной регистр. Импульс с ГОИ 14 производит также сброс триггера 17 считывания, увеличение содержимого счетчика 7 на единицу и блокировку эл&к1ента И 2О путем установки в 1 триггера 15, Процесс считывания продолжается Йо тех пор, пока не происходит совпадения кодов в счетчиках 6 и 7 и сброс потенциала Несовпадение. На этом прадесс работ БЗУ заканчивается. Процесс записи-считывания В БЗУ происходит асинхронно, т.е. импульсы записи и считывания на шинах записи и сч1тывания появляются в любое емя, определяемое работой внешних управляющих устройств. Вслучае прихода импульса записи во Время считывания происходит блокир1 ка записи на длительность цикла считывания по второму входу элемента И 18, при этом длительность цикла считывания on ределяется длительностью импульса формирователя 5, который через инвертор 24 поступает на второй вход элемента И 18. Аналогично происходит бло1р1ровка считывания во время записи с помощью формирователя импульса цикла записи 4, инвертора 23 и первого входа элемента И 19. Вышеуказанные блокировки не приводят к потере информационных слов, а лишь производят задержку моментов записи и считывания относительно друг друга, не снижая быстродействия устройства. По сравнению с известным предлагаемое устройство обладает большим быстро действием вследствие возможности счнть вання с накопителя в моменты пауз между записями в накопитель. Считьюание из ЮУ по импульсу считывания имеет минимальную задержку, так как определяется лишь задержкой срабатывания одного элемента И. ормулаизобретени %ферное запоминающее устройство, содержащее накопитель, информационные входы которого соединены с соответствующими в ыходами входного регистра, а выходы подключены к входам выходного регистра, счетчики адреса записи и считывания, генератор одиночных импульсов и шину записи, отличающееся тем, что, с целью пшышения быстроцё1йствия устройства, в него введены три группы элементов И, элементы равнозначности, элемент И-НЕ, i -5; триггеры, формирователи импульсов записи и считываш1я, инверторы, дополните70: ные генераторы оянночн-чс импульсов, элементы задержки эпементы И, группа элементов ИЛИ, шина считывания, причем вход ффмирователя импульсов записи подключен к шяне записи и S -входу первого R - S триггера, единичный выход которого подключен к первому вхо- ау первого элемента И, а выход формирователя импульсов записи подключен через первый инвертер к первому входу второго элемента И, второй вход первого элемента И соединен через второй инвертор с выходом формирователя импульсов считыванвя, взюд которого подключен к шине считывания и S-BXotiy второго 5 - S . триггера, единичный выход которого поШЕЛючен: к второму входу второго элемента И, выходы элементов И подключены соответственно к входам дополнительньос генераторов одиночных импульсов, выход первого дополнительного генератора одиночных импульсов подключек к юсоду записи накопителя, первым входам элементов И первой группы и через первый элемент задержки - к счетному входу счетчика адреса записи и Rвходу первого R-S триггера, выход вторсго допошштального генератора одиночных импульсоз подключен к R-входу третьего R- S триггера, $-вход которого подключен к R-exotiy второго R- S триггера, счетному входу счетчика адреса считывания и вькоду второго элемента задержки, вход которого подключен к выхоцу генератора одиночных импульсов, воюду считьюания накопителя и первым входам элементов И второй группы, вторые входы которых гтосуспючены к выхоаам счетчика адреса считывания и первым входам элементов равнозначности, вторые входы которых соединены с соответствующими выходами счетчика адреса записи и вторыми входами элементов И первой rpyn-s пы, а выходы эпемштов равнозиачиосги подключены к входам элемента И-НЕ, которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом третьего to -R- 6 триггера, а выход - с входом генератсра одиночных импульсов, вьосоды элементов И первой и второй групп подключены соответственно к первым и вторым входам элементов ИЛИ, выводы которых сое-is динены с адресными входами накопителя, выходы выходного регистра подключены к

первым входам элементов И третьей груп пы, выходы которых $1ВЛ5потся выходами устройства, вторые входы эпементов И третьей группы подключены к шине считывания.

Источники информащш, принятые во внимание при экспертизе

1.Авторское свидетельство ССХЗР

N 487417, кл. Gr 11 С И/Об, 1975.

2.Авторское свидетельство СССР М 493805, кл. Q II С 7/00, 1975,

3.Авторское свидетельство СССР N 273284, кл. О II С 11/06,1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

Авторы

Даты

1982-07-07—Публикация

1978-10-30—Подача