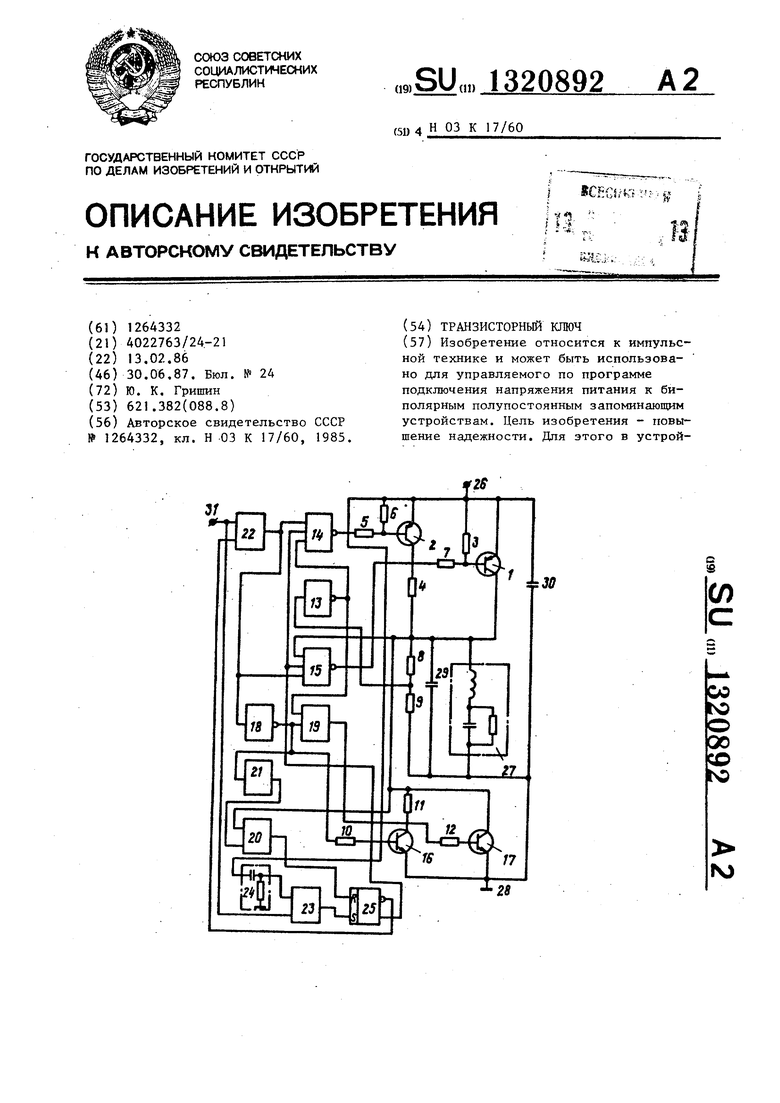

ство введены элемент 21 задержки, дифференцирующий элемент 24, два элемента ИЛИ 22, 23, RS-триггер 25, второй элемент И 20. Устройство содержит два транзистора 1, 2 одного типа проводимости, дна транзистора 16, 17 другого типа проводимости, десять резисторов 3-12, первый элемент И 19, два элемента И-НЕ 1А, 15, два инвертора 13, 8„ На чертеже

1

Изобретение относится к импульсной технике, может быть использовано для управляемого по программе подключения напряжения питания к биполярным полупостоянным запоминающим устройствам (ГШЗУ) и является усовершенствованием изобретения по авт. св №1264332.

Цель изобретения повьшгение надежности транзисторного ключа путем исключения перегрузок по мощности разрядного резистора при случайном подключении в цепь нагрузки встречного напряжения.

На чертеже представлена принципиальная электрическая схема транзисторного ключа.

Транзисторный ключ содержит первый 1 и второй 2 транзисторы одной структуры, десять резисторов 3-12, первый инвертор 13, первый 14 и второй 15 элементы И-НЕ,, третий 16 и четвертый 17 транзисторы другой структуры, второй инвертор 18, первый 19 и второй 20 элементы И, элемент 21 задержки, первый 22 и второй 23 элементы ИЛИ, дифференцирующий элемент 24 и RS-триггер 25. При этом эмиттер первого транзистора 1 подключен к шине 26 источника питания и первому вьгеоду первого резистора 3, второй вывод которого соединен с базой первого транзистора 1, коллектор которого через нагрузку 27 подключен к общей шине 28, коллектор второго транзистора 2 соединен с первым выводом второго резистора 4, а база подключена к первому выводу третьего резистора 5 и через четвертый резистор

20892

также показаны шина 26 источника питания, нагрузка 27, общая-шина 28, два конденсатора 28, 30, входная шина 31 устройства. Введение новых элементов с новыми связями позволяет исключить перегрузки по мощности разрядного резистора при случайном подключении в цепь нагрузки встречного напряжения, 1 ил.

6к шине 26 источника питания, второй вывод третьего резистора 5 соединен

с выходом первого элемента ИЛИ-НЕ 14, первый вход которого подключен к пер- вому входу второго элемента И-НЕ 15, выход которого через пятый резистор

7соединен с базой первого транзистора 1, эмиттер второго транзистора 2 подключен к шине 26 источника питания, второй вход первого элемента И-НЕ 14 соединен с выходом первого инвертора 13, вход которого подключен к первому выводу шестого резистора

8и через седьмой резистор 9 к общей шине 28, второй вход второго элемента И-НЕ 15 соединен с коллектором первого транзистора 1 и вторыми вы- водами второго 4 и шестого 8 резисторов, вход второго инвертора 18

подключен к первым входам элементов И-НЕ 14 и 15, а выход соединен с первым входом первого элемента И 19 и через восьмой резистор 10 с базой третьего транзистора 16, коллектор

которого через девятый резистор 11 соединен с коллекторами первого 1 и четвертого 17 транзисторов, база четвертого транзистора 17 через десятый резистор 12 соединена с выходом пер-.

вого элемента И 19, второй вход которого подключен к выходу первого инвертора 13, эмиттеры третьего 16 и четвертого 17 транзисторов объединены и подключены к общей шине 28,

первый вход второго элемента И 20. подключен к коллектору четвертого транзистора 17, а второй вход через элемент 21 задержки соединен с выходом второго инвертора 18, вход которого подключен к выходу первого элемента ИЛИ 22, первый вход которого соединен с инверсным выходом RS-триггера 25,-R-вход которого подключен к выходу второго элемента И 20, а S-вход соединен с выходом второго элемента ИЛИ 23, первый вход которого через дифференцирующий элемент 24 подключен к шине 26 источника питания, а второй вход объединен с вторым входом первого:. Элемента ИЛИ 22, прямой выход RS-триггера 25 подключен к третьим входам первого 14 и второго 15 элементов И-НЕ.

Кроме того, транзисторный ключ содержит первый 29 и второй 30 конденсаторы, первый вывод первого конденсатора 29 подключен к коллектору первого транзистора 1, а второй вывод соединен с общей шиной 28 и пер- вым вьгоодом второго конденсатора 30, второй вывод которого подключен к эмиттеру первого транзистора 1, объединенные вторые входы элементов ИЛИ 22 и 23.соединены с клеммой 31, которая является входом транзисторного ключа.

Транзисторный ключ работает следующим образом.

При включении питающего напряжения на шине 26 источника питания появляется нарастающее напряжение (передний фронт), при этом на выходе дифференцирующего элемента 24 появляется импульс короткой длительности который через первьй вход элемента ИЛИ 23 устанавливает RS-триггер 25 в единичное состояние, при котором с прямого выхода триггера 25 на третьи входы элементов И-НЕ 14 и 15 начинает поступать уровень 1, ас инверсного выхода триггера 25 на первый вход .элемента ИЛИ 22 - уровень О.

В исходном состоянии на входную клемму 31 подается уровень О, в результате чего на выходе элемента ИЛИ 22, а соответственно, и первых входах элементов И-НЕ 14 и 15 появляется уровень О, а на выходах элементов И -НЕ 14 и 15 устанавливается высокий уровень напряжения. При этом транзисторы 1 и 2 закрыты и, следовательно, нагрузка 27 отключена от шины 26 источника питания. При отсутствии напряжения на нагрузке 27 на втором входе элемента И-НЕ 15 и входе первого инвертора 13 устанавливается уровень О, а на выходе

, 208924

инвертора 13 - уровень 1, который поступает на второй вход элемента И- НЕ 14 и второй вход элемента И 19. Кроме того, в исходном состоянии О с выхода элемента ИЛИ 22 подается на

18, с выхода

fO

15

20

25

30

35

40

45

50

55

вход второго инвертора которого уровень 1 поступает на первый вход элемента И 19. При этом через резистор 10 в базу транзистора 16 протекает ток, открьтающий его. В это время одновременно на обоих входах элемента И 19 присутствуют уровни 1, в результате чего на выходе элемента И 19 устанавливается уровень 1 и через, резистор 12 в базу транзистора 17 протекает ток, обеспечивающий его открытое состояние. Открытый транзистор 17 полностью шунтируе нагрузку 27 и исключает появление на ней какого-либо напрякения, так как тепловые токи закрытых транзисторов 1 и 2 протекают через открытый транзистор 17. Уровни 1 с выхода инвертора 18 через элемент 21 задержки поступает на второй вход элемента И 20, на первом входе которого установлен уровень О (с отключенной нагрузки 27), поэтому на выходе элемента И 20 - уровень О, который не влияет на состояние триггера 25 (его единичное состояние сохраняется) .

При поступлении на входную клемму 31 уровня 1 на выходе элемента ИЛИ 22 появляется уровень 1, а на выходе инвертора 18 устанавливается О, который вык.пючает транзистор 16 и устанавливает на выходе элемента И 19 также уровень О, в результате чего ток в базу транзистора 17 пре- кращается и он выключается. Состояние триггера 25 при этом не изменяется (остается единичным). Наличие сигнала О на выходе элемента ИЛИ 22 приводит к тому, что на всех трех входах элемента И-НЕ 14 одновременно оказываются уровни 1, в результате чего на выходе элемента И-НЕ 14 устанавливается низкий уровень напряжения, а состояние элемента И-НЕ 15 не изменяется, так как на его втором входе сохраняется уровень О, поступающий с нагрузки 27. Появление на выходе элемента И-НЕ 14 низкого уровня напряжения приводит к включению транзистора 2, и через резистор 4 осуществляется предварительный заряд эквивалентной емкости

нагрузки 27, По мере роста налряже- ния на нагрузке 27 увеличивается и уровень напряжения на втором входе элемента И-НЕ 15. .Когда напряжение на втором входе элемента И-НЕ 15 достигает уровня напряжения, равного напряжению 1 на всех трех входах элемента И-НЕ 15 одновременно оказываются уровни 1, в результате чего на выходе элемента И-НЕ 15 появляется низкий уровень напряжения, который открьгаает транзистор 1, обеспе- чиваюгций дозаряд емкости нагрузки 27 и дальнейший рост напряжения на ней. После включения транзистора 1 напряжение в средней точке делителя напряжения, образованного резисторами 8 и 9, достигает такой величины, при которой на вход инвертора 13 на чинает поступать уровень 1, а с выхода инвертора 13 на второй вход элемента И-НЕ 14 - уровень О, в результате чего на выходе элемента И-НЕ 14 появляется высокий уровень напряжения, который включает транзистор 2. При этом состояние транзистора 1 не изменяется, он остается включенньм и обеспечивает подключение нагрузки 27 к шине 26 источника питания на все время, в течение которого на входной клемме 31 присутствует уровень

При поступлении на входную клемму 3.1 уровня О на выходе элемента ИЛИ 22 также появляется уровень O l, а на выходе элемента И-НЕ 15 устанавливается высокий уровень напряжения, в результате чего транзистор 1 выключается и отключает нагрузку 27 от шины 26 источника питания (транзистор 2 остается выключенным). Поступающий с выхода элемента ИЛИ 22 на вход инвертора 18 уровень О при приводит к появлению на выходе инвертора 18 1 и включению транзистора 16. Несмотря на то, что в это время на первом входе элемента И 19 присутствует уровень 1, элемент И 19 выключен (на его выходе уровень О), так как на его втором входе сохраняется уровень О с выхода инвертора 13, обусловленный тем, что на входе инвертора 13 присутствует высокий уровень напряжения от еще неразряженной емкости нагрузки 27. При этом транзистор 17 выключен. Включившийся транзистор 16 осуществляет предварительный разряд эквиваO

5

0

5

0

5

0

5

5

лентной емкости нагрузки 27 через резистор 11. По мере спада напряжения на нагрузке 27 уменьшается напряжение и в средней точке делителя напряжения,

п

образованного резисторами 8 и 9. Когда напряжение в средней точке делителя достигает уровня О, с выхода инвертора 13 на второй вход элемента И 19 начинает поступать уровень 1, С этого момента на обоих входах элемента И 19 одновременно оказываются уровни 1 в результате чего транзистор 17 переходит во включенное состояние и обеспечивает дозаряд емкости нагрузки 27 и в дальнейшем полное шунтирование нагрузки (шунтирование тепловых токов и токов утечки транзисторов 1 и 2). Таким образом, в первый момент выключения транзисторного ключа разряд эквивалентной емкости нагрузки 27 осуществляется через открытый транзистор 16 и резистор 11. Резистор 11 в ключе, выбираемый из условия максимально допустимого тока коллектора транзистора 16 и допустимой постоянной времени разряда эквивалентной емкости нагрузки, исключает перегрузку транзистора 16 по току при любом значении эквивалентной емкости нагрузки 27 (как правило, с целью симметрирования постоянных времени заряда и разряда эквивалентной емкости нагрузки 27 номиналы резисторов 4 и 11 следует выбирать равными). Через резистор 11 осуществляется : предварительный разряд емкости нагрузки до заданного напряжения, а окончательный ее разряд и полное шунтирование нагрузки осуществляются с помощью транзистора 17, в коллект.-, торной цепи которого отсутствуют ограничительные элементы тока (так как этот транзистор должен иметь минимальное остаточное напряжение между коллектором и эмиттером для более эффективного шунтирования нагрузки 27). I

0 Появившийся на выходе инвертора 18 уровень 1 (при выключении ключа через время задержки элемента 21 задержки поступает на второй вход элемента И 20. Время задержки элемента 21 задержки выбирают таким, чтобы оно превьш1ало время разряда эквивалентной емкости нагрузки 27, поэтому к моменту появления на втором входе элемента И 20 уровня 1 на его перBOM входе устанавливается уровень о в результате разряда эквивалентной емкости нагрузки 27. Поэтому через время задержки элемента 21 задержки состояние элемента И 20 не изменяется и на его выходе сохраняется уровень О, что сохраняет единичное состояние триггера 25.

При возникновении аварийной ситуации (например, при случайном попадании напряжения на отключенную от шины питания нагрузку) транзистор 17 автоматически переходит в выключенно состояние, так как при этом на входе

инвертора 13 мгновенно оказывается It 1 ti

уровень

а на его выходе - уро20

30

35

вень О , который выключает элемент И 19 по .его второму входу, а следовательно, и транзистор 17. В это вре- же время высокий Уровень напряжения с нагрузки 27 поступает на первый вход элемента И 20. С этого момента на обоих входах эл;емента И 20 одновременно устанавливаются уровни 1, поэтому и на выходе элемента И 20 появляется уровень 1, который воз-- действует на R-вход RS-триггера 25 (в это время на S-входе RS-триггера 25 - уровень о). RS-триггер 25 устанавливается в нулевое состояние, при котором с его инверсного выхода на первый вход элемента ИЛИ 22 начинает поступать уровень 1, приводящий к появлению уровня 1 на выходе элемента ИЛИ 22 (несмотря на то, что в это время на клемме 31 - уровень О). При этом на выходе интегратора 18 устанавливается уровень О, который выключает и транзистор 16. Одновременно уровень О с выхо- да инвертора 18 подтверждает по первому входу элемент И 19 его выключенное состояние (а соответственно, подтверждается и выключенное состояние транзистора 17). С этого момен- та оба транзистора 16 и 17 выключены и не потребляют тока от встречно включенного к нагрузке источника напряжения (через резистор 1I исключается протекание тока, и резистор 11 не рассеивает мощность).

В аварийном режиме уровень 1, поступающий на первые входы элементов И-НЕ 14 и 15 с выхода элемента ИЛИ 22, не приводит к включению этих элементов, так как переход триггера 25 в нулевое состояние при аварийном подключении к нагрузке встречного

25

40

55

50

3208928

напряжения обеспечивает уровень О на третьих входах элементов И-НЕ 14 и 15 (с прямого выхода триггера 25). Выключенное состояние элементов И- НЕ 14 и 15 обеспечивает выключенное состояние транзисторов I и 2.

Поступление на входную клемму 31 уровня 1 приводит к тому, что триггер 25 через элемент ИЛИ 23 устанавливается в единичное состояние, при котором на первый вход элемента ИЛИ 22 с инверсного выхода триггера 25 начинает поступать уровень О, а на третьи входы элементов И-НЕ 14 5 и 15 с прямого выхода триггера 25

W

начинает поступать уровень 1, что снимает блокировку с элементов И- НЕ 14 и 15. Элементы И-НЕ 14 и 15 включаются в соответствующей последовательности, что приводит к последующему подключению нагрузки 27 к шине 26 источника питания. При этом состояние инвертора 18 не изменяется (на его выходе сохраняется уровень о) и транзисторы 16 и 17 остаются выключенными.

При поступлении на входную клемму 31 уровня О нагрузка 27 отключается от шины 26 источника питания, а на выходе инвертора 18 устанавливается уровень 1, который включает транзистор 16. Если к этому времени не устранено аварийное подключение напряжения к нагрузке 27, то, несмотря на включенное состояние транзистора 16, спада напряжения на нагрузке 27 не происходит, поэтому в этом случае на втором входе элемента И 19 никогда не может появиться уровень 1 с выхода инвертора 13 (так как на его входе постоянно уровень l), что, в свою очередь, исключает возможность включения транзистора 17. Транзистор 16 остается во включенном состоянии до тех пор, пока через время задержки элемента 21 задержки на втором входе элемента И 20 не появится уровень 1 (на первом входе элемента И 20 уровень 1 присутствует постоянно, если к нагрузке 27 подключилось встречное напряжение). В результате на выходе элемента И 20 устанавливается уровень 1, который переводит RS-триггер 25 в нулевое состояние, обеспечивающее выключение транзистора 16 и прекращение тока через резистор 11. Вновь поступивший на входную 31 уровень 1

опять взводит в исходное состояние RS-триггер 25. Схема работает таким образом до тех пор, пока не будет установлено аварийное подключение к нагрузке встречного напряжения, после iero транзисторный ключ автоматически восстанавливает свою работу.

Конденсаторы 29 и 30 позволяют исключить броски напряжения на первом входе элемента И 20, втором входе элемента И-НЕ 15, входе инвертора 13 и транзисторе 1 за счет компенсации индуктивности проводников, соединяющих транзисторный ключ с нагрузкой 27 и шиной 26 источника питания.

Таким образом, в предлагаемом Транзисторном ключе при аварийном попадании на нагрузку встречного напряжения в вьпслюченное состояние переходит не только транзистор 17, но и транзистор 16, что исключает вьщег ленив значительной мощности на резисторе 11, определяющем время предварезко ограничены). Кроме того, при этом полностью исключается потребление энергии от случайно подключенно го к нагрузке источника напряжения.

Ю

Формула изобретения

Транзисторный ключ по авт. св. № 126А332, отличающийся тем, что, с целью повышения надежности в негб введены элемент задержки, дифференцирующий элемент, два элемен та ИЛИ, RS-триггер, второй элемент И первый вход которого подключен к кол

5 лектору четвертого транзистора, а второй вход через элемент задержки соединен с выходом второго инвертора вход которого подключен к выходу пер вого-элемента ИЛИ, первый вход котор

20 го соединен с инверсным выходом RS-триггера, R-вход которого подключен к выходу второго элемента И, а S-вход соединен с выходом второго элемента ИЛИ, первьй вход которого

рительного разряда эквивалентной ем- через дифференцирующий элемент подкости нагрузки. Это повышает надежность транзисторного ключа, особенно при выполнении его в виде гибридной интегральной микросхемы (когда геометрические размеры резистора 11

Составитель Г. Терешина Редактор А. Огар Техред В.Кадар Корректор Г. Решетник

Заказ .2667/56 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

1320892 -10

резко ограничены). Кроме того, при этом полностью исключается потребление энергии от случайно подключенного к нагрузке источника напряжения.

Формула изобретения

Транзисторный ключ по авт. св. № 126А332, отличающийся тем, что, с целью повышения надежности в негб введены элемент задержки, дифференцирующий элемент, два элемента ИЛИ, RS-триггер, второй элемент И, первый вход которого подключен к коллектору четвертого транзистора, а второй вход через элемент задержки соединен с выходом второго инвертора, вход которого подключен к выходу первого-элемента ИЛИ, первый вход которого соединен с инверсным выходом RS-триггера, R-вход которого подключен к выходу второго элемента И, а S-вход соединен с выходом второго элемента ИЛИ, первьй вход которого

30

,ключен к шине источника питания, а второй вход соединен с вторым входом первого элемента ИЛИ, прямой выход RS-триггера подключен к третьим входам первого и второго элементов И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный ключ | 1985 |

|

SU1336223A2 |

| Транзисторный ключ | 1985 |

|

SU1265992A2 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| Транзисторный ключ | 1986 |

|

SU1378040A1 |

| Оптоэлектронный переключатель | 1977 |

|

SU690628A2 |

| Транзисторный ключ | 1985 |

|

SU1264332A2 |

| Транзисторный ключ с защитой от перегрузки | 1988 |

|

SU1531203A1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| Транзисторный ключ | 1984 |

|

SU1211873A1 |

| Триггерное устройство | 1981 |

|

SU970649A1 |

Изобретение относится к импульсной технике и может быть использовано для управляемого по программе подключения напряжения питания к биполярным полупостоянным запоминающим устройствам. Цель изобретения - повышение надежности. Для этого в устрой(Л го

| Транзисторный ключ | 1985 |

|

SU1264332A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-30—Публикация

1986-02-13—Подача