Изобретение относится к импульсной технике, может быть использовано для управляемого по программе подключения напряжения питания к биполярным полупостоянным запоминающим устройствам (ППЗУ) и является усовершенствованием изобретения по авт. св. № 1265992.

Целью изобретения является повышение быстродействия транзисторного ключа путем сокраш.ения времени готовности его к работе после устранения аварийного состояния нагрузки.

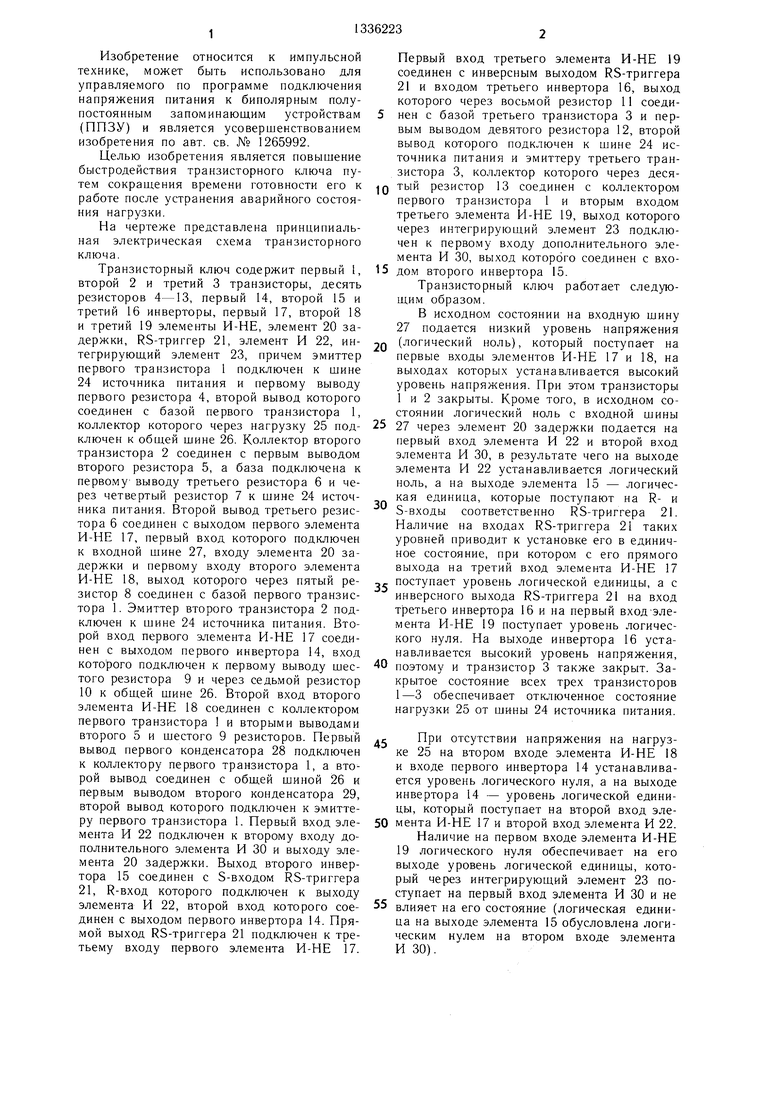

На чертеже представлена принципиальная электрическая схема транзисторного ключа.

Транзисторный ключ содержит первый 1, второй 2 и третий 3 транзисторы, десять резисторов 4-13, первый 14, второй 15 и третий 16 инверторы, первый 17, второй 18 и третий 19 элементы И-НЕ, элемент 20 задержки, RS-триггер 21, элемент И 22, интегрирующий элемент 23, причем эмиттер первого транзистора 1 подключен к шине 24 источника питания и первому выводу первого резистора 4, второй вывод которого соединен с базой первого транзистора 1, коллектор которого через нагрузку 25 подключен к общей шине 26. Коллектор второго транзистора 2 соединен с первым выводом второго резистора 5, а база подключена к первому выводу третьего резистора 6 и через четвертый резистор 7 к шине 24 источника питания. Второй вывод третьего резистора 6 соединен с выходом первого элемента И-НЕ 17, первый вход которого подключен к входной шине 27, входу элемента 20 задержки и первому входу второго элемента И-НЕ 18, выход которого через пятый резистор 8 соединен с базой первого транзистора 1. Эмиттер второго транзистора 2 подключен к шине 24 источника питания. Второй вход первого элемента И-НЕ 17 соединен с выходом первого инвертора 14, вход кото рого подключен к первому выводу шестого резистора 9 и через седьмой резистор 10 к общей шине 26. Второй вход второго элемента И-НЕ 18 соединен с коллектором первого транзистора 1 и вторыми выводами второго 5 и шестого 9 резисторов. Первый вывод первого конденсатора 28 подключен к коллектору первого транзистора 1, а второй вывод соединен с общей шиной 26 и первым выводом второго конденсатора 29, второй вывод которого подключен к эмиттеру первого транзистора 1. Первый вход элемента И 22 подключен к второму входу дополнительного элемента И 30 и выходу элемента 20 задержки. Выход второго инвертора 15 соединен с S-входом RS-триггера 21, R-вход которого подключен к выходу элемента И 22, второй вход которого соединен с выходом первого инвертора 14. Прямой выход RS-триггера 21 подключен к третьему входу первого элемента И-НЕ 17.

Первый вход третьего элемента И-НЕ 19 соединен с инверсным выходом RS-триггера 21 и входом третьего инвертора 16, выход которого через вось.мой резистор 11 соединен с базой третьего транзистора 3 и первым выводом девятого резистора 12, второй вывод которого подключен к шине 24 источника питания и эмиттеру третьего транзистора 3, коллектор которого через десяQ тый резистор 13 соединен с коллектором первого транзистора 1 и вторым входом третьего элемента И-НЕ 19, выход которого через интегрирующий элемент 23 подключен к первому входу дополнительного элемента И 30, выход которого соединен с вхо5 дом второго инвертора 15.

Транзисторный ключ работает следующим образом.

В исходном состоянии на входную шину 27 подается низкий уровень напряжения

Q (логический ноль), который поступает на первые входы элементов И-НЕ 17 и 18, на выходах которых устанавливается высокий уровень напряжения. При этом транзисторы 1 и 2 закрыты. Кроме того, в исходном состоянии логический ноль с входной шины

5 27 через элемент 20 задержки подается на первый вход элемента И 22 и второй вход элемента И 30, в результате чего на выходе эле.мента И 22 устанавливается логический ноль, а на выходе элемента 15 - логичес- кая единица, которые поступают на R- и S-входы соответственно RS-триггера 21. Наличие на входах RS-триггера 21 таких уровней приводит к установке его в единичное состояние, при котором с его прямого выхода на третий вход элемента И-НЕ 17

поступает уровень логической единицы, а с инверсного выхода RS-триггера 21 на вход третьего инвертора 16 и на первый вход-элемента И-НЕ 19 поступает уровень логического нуля. На выходе инвертора 16 устанавливается высокий уровень напряжения,

0 поэтому и транзистор 3 также закрыт. Закрытое состояние всех трех транзисторов 1-3 обеспечивает отключенное состояние нагрузки 25 от щины 24 источника питания.

с При отсутствии напряжения на нагрузке 25 на втором входе элемента И-НЕ 18 и входе первого инвертора 14 устанавливается уровень логического нуля, а на выходе инвертора 14 - уровень логической единицы, который поступает на второй вход эле0 мента И-НЕ 17 и второй вход элемента И 22. Наличие на первом входе элемента И-НЕ 19 логического нуля обеспечивает на его выходе уровень логической единицы, который через интегрирующий элемент 23 поступает на первый вход элемента И 30 и не

5 влияет на его состояние (логическая единица на выходе элемента 15 обусловлена логическим нулем на втором входе элемента И 30).

При поступлении на входную шину 27 высокого уровня напряжения на всех трех входах элемента И-НЕ 17 одновременно оказывается уровень логической единицы, в результате чего на его выходе устанавливается низкий уровень напряжения, а состояние элемента И-НЕ 18 не изменяется, так как на его втором входе сохраняется уровень логического нуля, поступающий с нагрузки 25. Появление на выходе элемента И-НЕ 17 низкого уровня напряжения приводит к включению транзистора 2 и через резистор 5 осуществляется предварительный заряд эквивалентной емкости нагрузки 25. По мере роста напряжения на нагрузке 25 увеличивается и уровень напряжения на втором входе элемента И-НЕ 18. Когда напряжение на втором входе элемента И-НЕ 18 достигнет уровня напряжения, равного напряжения, равного напряжению логической единицы, на обоих его входах 18 одновременно окажутся уровни логической -единицы, в результате чего на выходе появится низкий уровень напряжения, который открывает транзистор 1, обеспечивающий дозаряд емкости нагрузки и дальнейший рост напряжения на ней.

После включения транзистора 1 напряжение в средней точке делителя напряжения, образованного резисторами 9 и 10, достигает такой величины, при которой на вход инвертора 14 начинает поступать уровень логической единицы, а с выхода инвертора 14 на второй вход элемента И-НЕ 17 - уровень логического нуля, в результате чего на выходе элемента И-НЕ 17 появляется высокий уровень напряжения, который выключает транзистор 2. При этом состояние транзистора 1 не изменяется, он остается включенным и обеспечивает подключение нагрузки 25 к щине 24 источника питания на все время, в течение которого на входной шине 27 присутствует высокий уровень напряжения.

Появившийся на входной шине 27 высокий уровень напряжения через время задержки элемента 20 задержки поступает на первый вход элемента И 22 и второй вход элемента И 30. Время задержки элемента 20 задержки выбирается так, чтобы оно превышало время заряда эквивалентной емкости нагрузки 25, поэтому к моменту появления на первом входе элемента И 22 уровня логической е диницы на его втором входе устанавливается уровень логического нуля с выхода инвертора 14, так как к э.тому времени на входе последнего устанавливается уровень логической единицы в результате заряда эквивалентной е.мкости нагрузки 25. Поэтому , через время задержки элемента 20 задержки состояние элемента -И 22 не изменяется и на его выходе сохраняется уровень логического нуля. В это время на выходе элемента 15 тоже устанавливается

уровень логического нуля, так как на обоих входах элемента И 30 оказываются уровни логической единицы. Одновременное наличие на управляющих входах RS-триггера 21 уровней логического нуля не изменяет его состояния, поэтому на его прямом выходе сохраняется уровень логической единицы, исключающий блокировку элемента И-НЕ

17по третьему входу, а на инверсно.м вы- Q ходе RS-триггера 21 сохраняется уровень

логического нуля, обеспечивающий высокий уровень напряжения на выходе инвертора 16, который сохраняет выключенное состояние транзистора 3.

При возникновении аварийной ситуации 5 (например, при коротком замыкании в нагрузке 25) транзистор 1 автоматически переходит в выключенное состояние, так как при этом на втором входе элемента И-НЕ

18оказывается уровень логического нуля, 0 который выключает элемент И-НЕ 18 (устанавливает на его выходе высокий уровень напряжения), а следовательно, выключает и транзистор 1. В это же время на вход инвертора 14 воздействует уровень логического нуля, в результате чего на его выходе уста5 навливается уровень логической единицы, который поступает на второй вход элемента И 22. С этого момента времени на обоих входах элемента И 22 одновременно оказываются уровни логической единицы, поэтому

Q и на его выходе устанавливается уровень логической единицы, который воздействует на R-вход RS-триггера 21 (в это время на S-входе RS-триггера 21 уровень логического нуля). RS-триггер 21 устанавливается в нулевое состояние, при котором с его прямого

5 выхода на третий вход элемента И-НЕ 17 начинает поступать уровень логического нуля, приводящий к блокировке последнего по третьему входу и установке на выходе элемента И-НЕ 17 высокого уровня напряжения, в результате чего выключается и

0 транзистор 2, что исключает протекание тока через низкоомный резистор 5. Переход RS-триггера 21 в нулевое состояние приводит к появлению на его инверсном выходе уровня логической единицы, в результате

г чего на выходе инвертора 16 устанавливается низкий уровень напряжения, приводящий к включению транзистора 3 и появлению тока через резистор 13. Несмотря на включенное состояние транзистора 3 на втором входе элемента И-НЕ 19 сохраня0 ется уровень логического нуля (так как нагрузка 25 закорочена), а на выходе элемента И-НЕ 19 сохраняется уровень логической единицы.

Если теперь устранить аварийное состояние нагрузки 25 (устранить короткое замыкание в нагрузке 25), то ток, протекающий через открытый транзистор 3 и резистор 13, обеспечивает появление на нагрузке 25 (а

значит и на втором входе элемента И-НЕ 19) уровня логической единицы. С этого момента времени на обоих входах элемента И-НЕ 19 одновременно окажутся уровни логической единицы, что приводит к появлению на выходе элемента И-НЕ 19 уровня логического нуля. Через время интегрирования интегрирующего элемента 23 уровень логического нуля поступает на первый вход элемента И 30 и устанавливает на выходе 15 уровень логической единицы, который установит (взведет) RS-триггер 21 в исходное (единичное) состояние. Единичное состояние RS-триггера 21 обеспечит включение транзисторного ключа (если в это время на входной шине 27 продолжает сохраняться высокий уровень напряжения).

Схема транзисторного ключа может быть взведена в исходное состояние и при поступлении на входную шину 27 низкого уровня напряжения, так как при этом через время задержки элемента 20 задержки на первом входе элемента И 22 и втором входе элемента И 30 устанавливается уровень логического нуля, в результате чего на выходе элемента И 22 устанавливается логический ноль, а на выходе элемента 15 - логическая единица. Это также приводит к установке RS-триггера 21 в исходное (единичное) состояние, при котором с его прямого выхода на третий вход элемента И-НЕ 17 вновь начинает поступать уровень логической единицы, а с инверсного выхода RS-триг гера 21 - уровень логического нуля, приводящий к выключению транзистора 3.

Следует отметить, что номинал резистора 13 может выбираться в несколько раз (или на несколько порядков) больше номинала резистора 5, поэтому включенное состояние транзистора 3 при аварийном состоянии нагрузки не приводит к значительной мош,ности, рассеиваемой резистором 13. Интегрирующий элемент 23 предназначен для задержки разблокирования схемы транзисторного ключа от случайных («мерцающих) кратковременных обрывов нагрузки при ее восстановлении из аварийного состоя

ния, что повышает помехоустойчивость автоматического восстановления схемы транзисторного ключа.

Конденсаторы 28 и 29 позволяют исключить броски напряжения на втором входе элемента И-НЕ 18, входе инвертора 14, транзисторе 1 и втором входе элемента И-НЕ 19 за счет компенсации индуктивности проводников, соединяющих транзисторный ключ с нагрузкой 25 и тиной 24 источника питания.

Таким образом, предложенный транзисторный ключ по сравнению с известным обеспечивает автоматическое восстановление состояния сразу же посл е устранения аварийного состояния нагрузки и при этом не обязательна подача на входную шину ключа низкого уровня напряжения. Это обеспечивает повышение быстродействия ключа, так как после устранения короткого замыкания в нагрузке она сразу же оказывается под рабочим напряжением и может выполнять свою функцию.

Формула изобретения

Транзисторный ключ по авт. св. № 1265992, отличающийся тем, что, с целью повышения быстродействия, в него введены третий транзистор, три резистора, третий инвертор, интегрирующий элемент, дополнительный элемент И, третий элемент

И-НЕ, первый вход которого соединен с инверсным выходом RS-триггера и входом третьего инвертора, выход которого через восьмой резистор соединен с базой третьего транзистора и первым выводом девятого резистора, второй вывод которого подключен к щине источника питания и эмиттеру третьего транзистора, коллектор которого через десятый резистор соединен с коллектором первого транзистора и вторым входом третьего элемента И-НЕ, выход которого

через интегрирующий элемент подключен к первому входу дополнительного элемента И, второй вход которого соединен с выходом элемента задержки, а выход подключен к входу второго инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный ключ | 1985 |

|

SU1265992A2 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| Транзисторный ключ | 1986 |

|

SU1320892A1 |

| Триггерное устройство | 1981 |

|

SU970649A1 |

| Транзисторный ключ | 1985 |

|

SU1264332A2 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| Транзисторный ключ | 1984 |

|

SU1211873A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Устройство для управления лентопротяжным механизмом | 1987 |

|

SU1607006A1 |

Изобретение относится к импульсной технике и может быть использовано для управления программным подключением напряжения питания к биполярным полупостоянным запоминающим устройствам. Цель изобретения - повышение быстродействия транзисторного ключа - достигается путем сокраш.ения его времени готовности к работе после устранения аварийного состояния нагрузки. Для этого в устройство дополнительно введены третий транзистор 3, третий инвертор 16, интегрирующий элемент 23, элемент И 30. Устройство также содержит транзисторы 1 и 2, резисторы 4-13, инверторы 14 и 15, элементы И-НЕ 17, 18 и 19, элемент 20 задержки, RS-триг- гер 21, элемент И 22, шину 24 источника питания, нагрузку 25, общую тину 26, выходную шину 27, конденсаторы 28 и 29. Предложенный ключ по сравнению с прототипом обеспечивает автоматическое восстановление рабочего состояния сразу же после устранения аварийного режима нагрузки, что повышает его быстродействие. 1 ил. fsZfi (Л оо со 05 Ю Ю оо NJ

| Транзисторный ключ | 1985 |

|

SU1265992A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-19—Подача