Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, поступающей из каналов связи, удаленных от абонентов.

Целью изобретения является расширение функциональных возможностей устройства путем динамического изменения порядка выдачи сообщений в ЦВМ с учетом времени их поступления в сеть обмена.

Работа устройства основана на том, что при построении очереди на вьщачу сообщений для различных приоритетных групп оно обеспечивает вначале выделение и анализ кодов приоритета, времени поступления сообщения в сеть обмена, состояния очереди, а затем на основании этого производит динамическое упорядочение соединений.

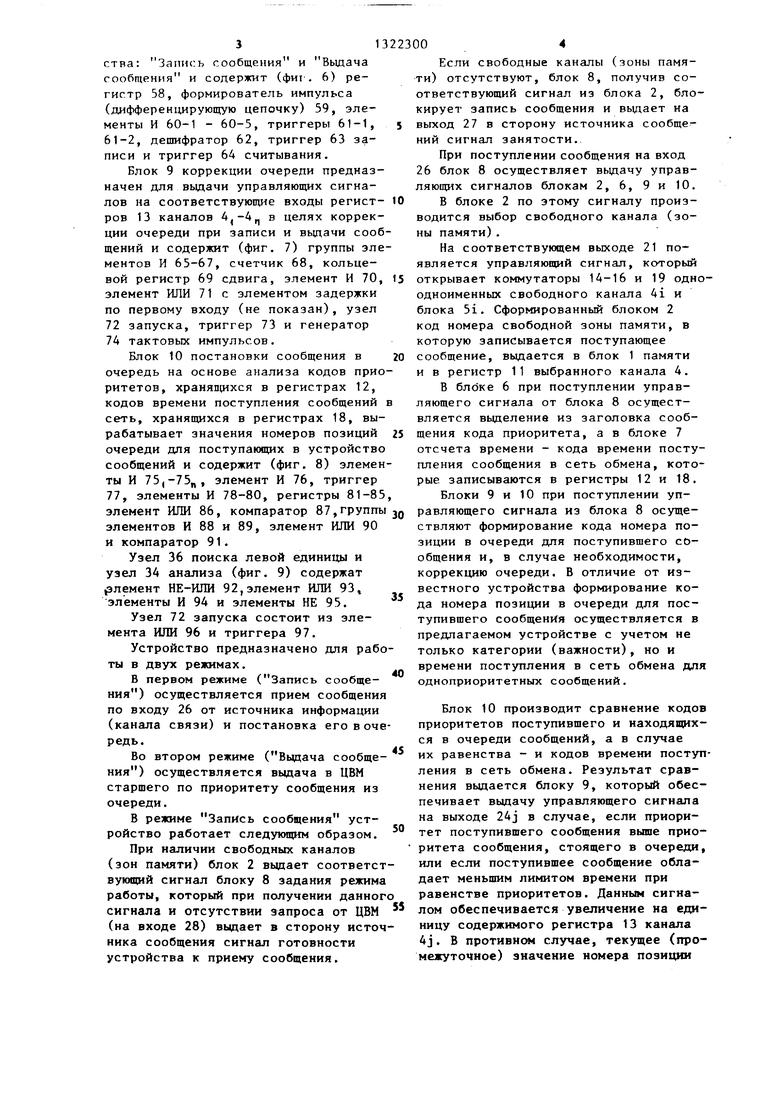

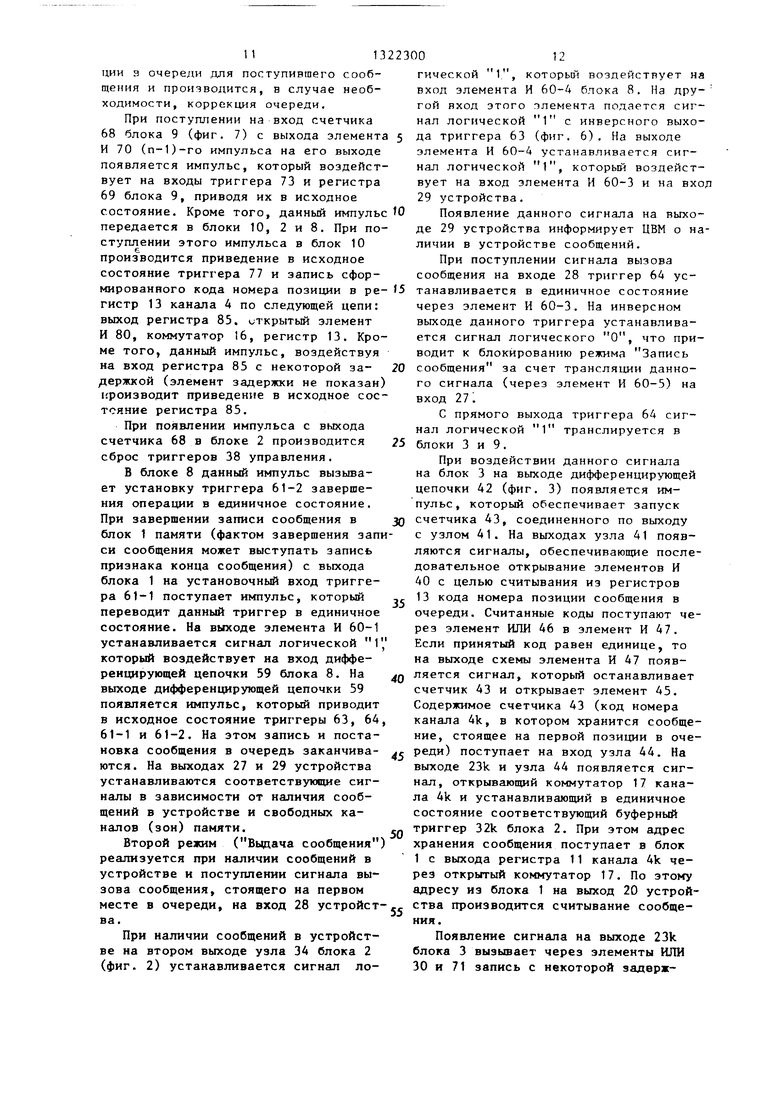

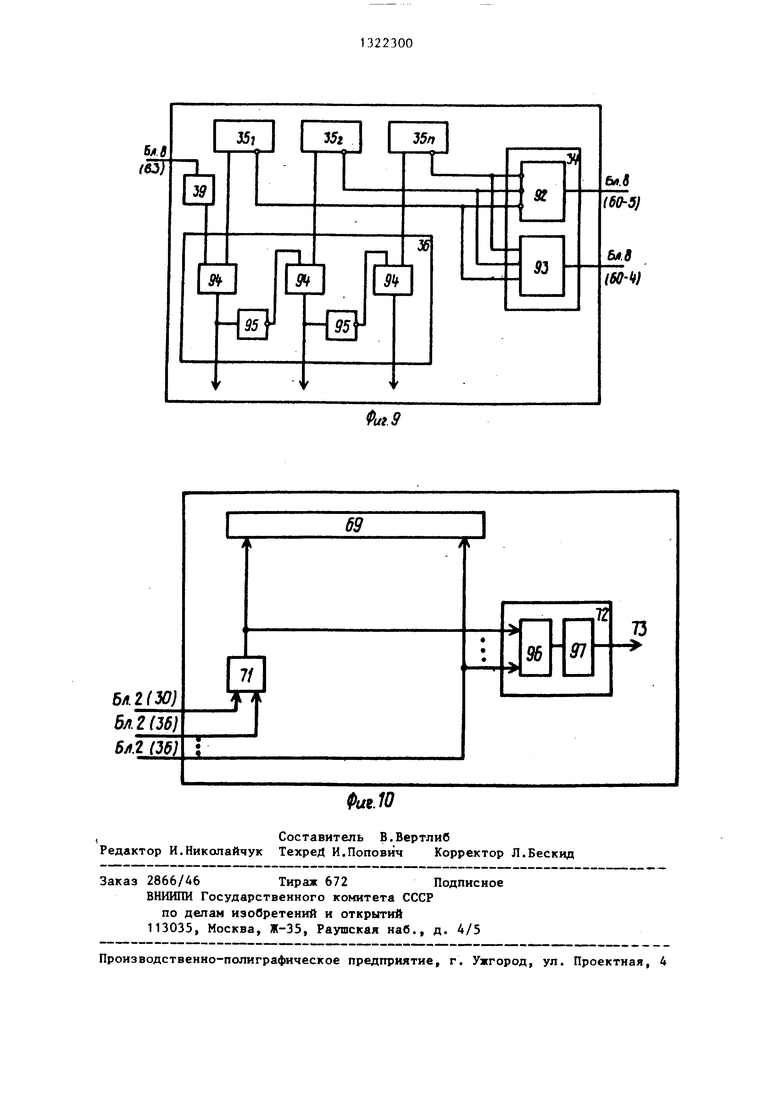

На фиг. 1 представлена блок-схема предлагаемого устройства( на фиг. 2 - 10 - функциональные схемы блока выбора канала, блока опроса каналов блоБлок 1 памяти вьтолняет функции оперативного запоминающего устройст для хранения поступающих сообщений. Блок 2 выбора канала предназначе

5 для выбора свободного канала и зоны памяти в блоке 1 и содержит (фиг. 2 злемент ИЛИ 30, элементы 31-1 и 31задержки, группу буферных триггеров 32, группу элементов И 33, узел 34

О анализа, группу триггеров 35 состоя ния каналов, узел 36 поиска левой единицы, узел 37 информации, группу триггеров 38 управления и формирова тель импульса (дифференцирующую це 5 почку) 39.

Блок 3 опроса каналов осуществля сравнение кодов, хранящихся в регис рах 13, и выдает сигнал на один из коммутаторов 17, включенный между о

20 ним из регистров 11 (тем, где храни ся признак сообщения, находящегося на первой позиции очереди) и блоком 1 памяти. В качестве признака сообщения выступает адрес (номер зоны п

ка формирования кода приоритета, бло-25 мяти), по которому хранится данное

ка отсчета времени, блока задания режима работы, блока коррекции очереди, блока постановки сообщения в очередь, узла поиска левой единицы

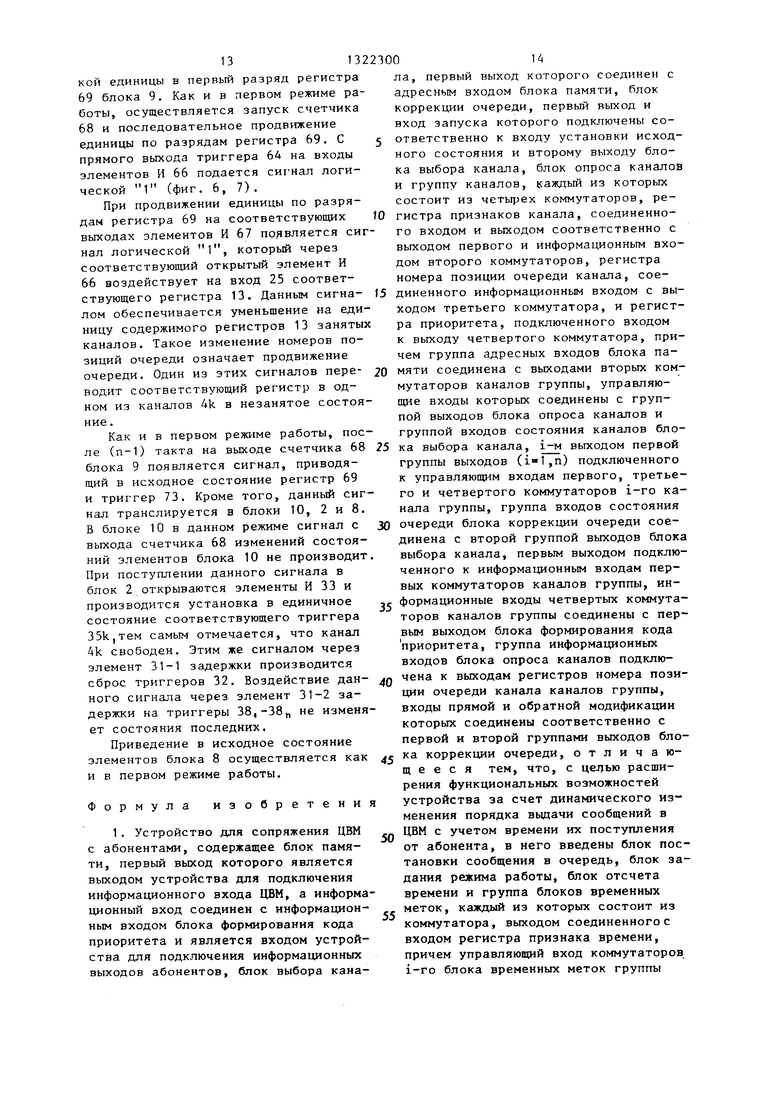

узла запуска блока коррекции очере-30 узлов элементов И 40, узел 41 дешиф35

и ди.

Устройство содержит (фиг. 1) блок 1 памяти, блок 2 выбора канала, блок 3 опроса каналов, каналы ,,, блоки 5,-5f, временных меток, блок 6 формирования кода приоритета, блок 7 отсчета времени, блок 8 задания режима работы, блок 9 коррекции очереди и блок 10 постановки сообщения в оче- редь.40

Каждый канал 4 содержит регистр 11 признака канала, регистр 12 приоритета, регистр 13 номера позиции канала.

рации, формирователь импульса (дифференцирующую цепочку) 42, счетчик 43 узел 44 дешифрации.группу элементов И 45, группу элемента ИЛИ 46 и элемент И 47.

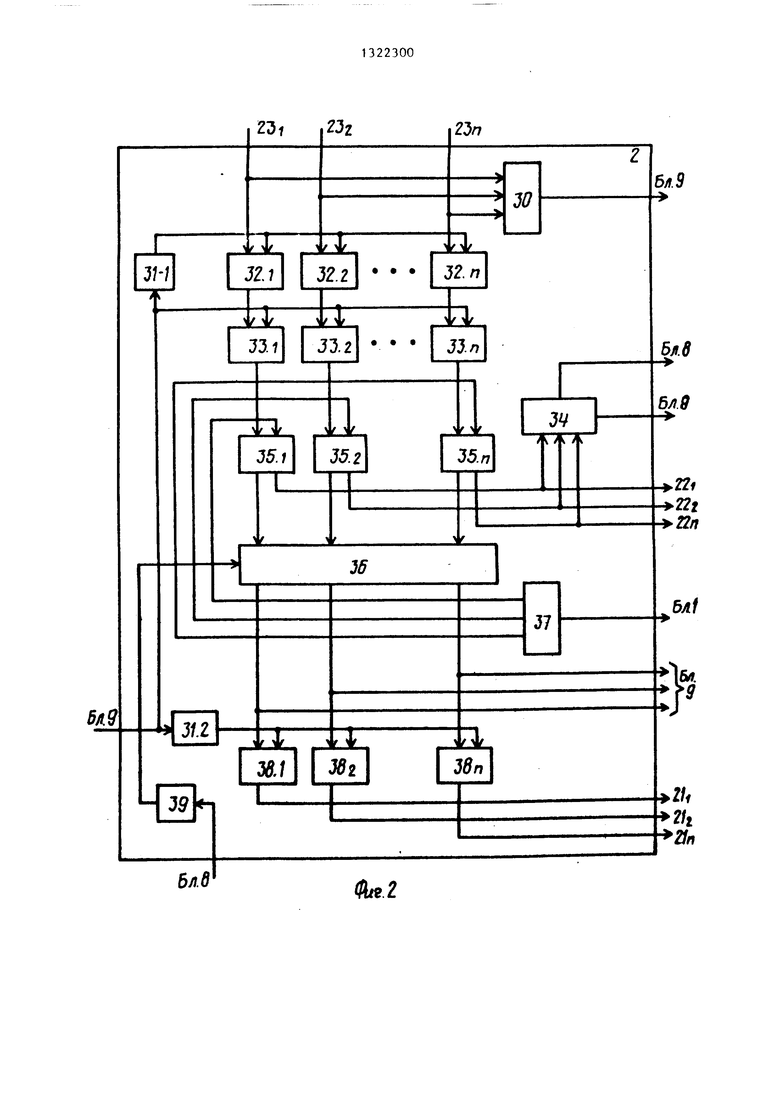

Блок 6 формирования кода приоритета обеспечивает выделение из заголовка сообщения кода приоритета, который хранится в соответствующем регистре 12, куда записывается с выхода блока 6 через соответствующие коммутаторы 15. Блок 6 (фиг. 4) содержит триггер 48, первую группу элементов И 49, регистр 50, вторую группу элементов

первый 14, четвертый 15, третий 16 и второй 17 коммутаторы.

I

Каждый блок 5 содержит регистр 18 признака времени и коммутатор 19.,

Устройство имеет информационный выход 20,блок 2 выбора канала - группу выходов 21, 22, блок 3 опроса канз лов - группу 23 выходовi блок 9 коррекции очереди - группу выходов 24 25. Кроме того, устройство имеет информационный вход 26, сигнальный выход 27 в сторону источника сообщений, управляющий вход 28 (от ЦВМ), сиг- нальньм выход 29 (в сторону ЦВМ).

Блок 1 памяти вьтолняет функции оперативного запоминающего устройства для хранения поступающих сообщений. Блок 2 выбора канала предназначен

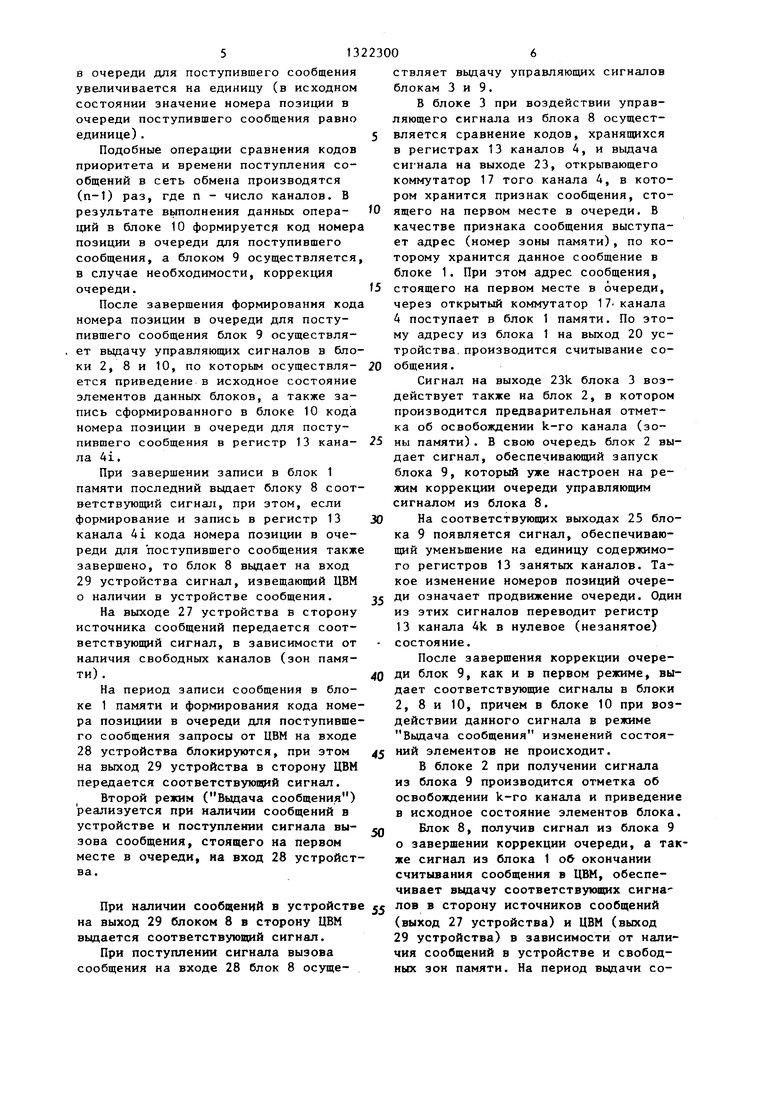

для выбора свободного канала и зоны памяти в блоке 1 и содержит (фиг. 2) злемент ИЛИ 30, элементы 31-1 и 312 задержки, группу буферных триггеров 32, группу элементов И 33, узел 34

анализа, группу триггеров 35 состояния каналов, узел 36 поиска левой единицы, узел 37 информации, группу триггеров 38 управления и формирователь импульса (дифференцирующую цепочку) 39.

Блок 3 опроса каналов осуществляет сравнение кодов, хранящихся в регистрах 13, и выдает сигнал на один из коммутаторов 17, включенный между одним из регистров 11 (тем, где хранится признак сообщения, находящегося на первой позиции очереди) и блоком 1 памяти. В качестве признака сообщения выступает адрес (номер зоны пасообщение в блоке 1. Признак сообщения записывается в регистр 11 через коммутаторы 14.

Блок 3 содержит (фиг. 3) группу

5

0

рации, формирователь импульса (дифференцирующую цепочку) 42, счетчик 43 узел 44 дешифрации.группу элементов И 45, группу элемента ИЛИ 46 и элемент И 47.

Блок 6 формирования кода приоритета обеспечивает выделение из заголовка сообщения кода приоритета, который хранится в соответствующем регистре 12, куда записывается с выхода блока 6 через соответствующие коммутаторы 15. Блок 6 (фиг. 4) содержит триггер 48, первую группу элементов И 49, регистр 50, вторую группу элементов

5 И 51 и счетчик 52.

Блок 7 отсчета времени обеспечивает выделение из заголовка сообщения кода времени в сеть обмена. Код времени поступления в сеть обмена сооб0 щения хранится в регистре 18 соответствующего блока 5, куда записьшается с выхода блока 7 через соответствующий коммутатор 19. Блок 7 содержит (фиг. 5) первую группу элементов И

5 53, триггер 54 запуска, регистр 55, счетчик 56 и вторую группу элемента И 57,.

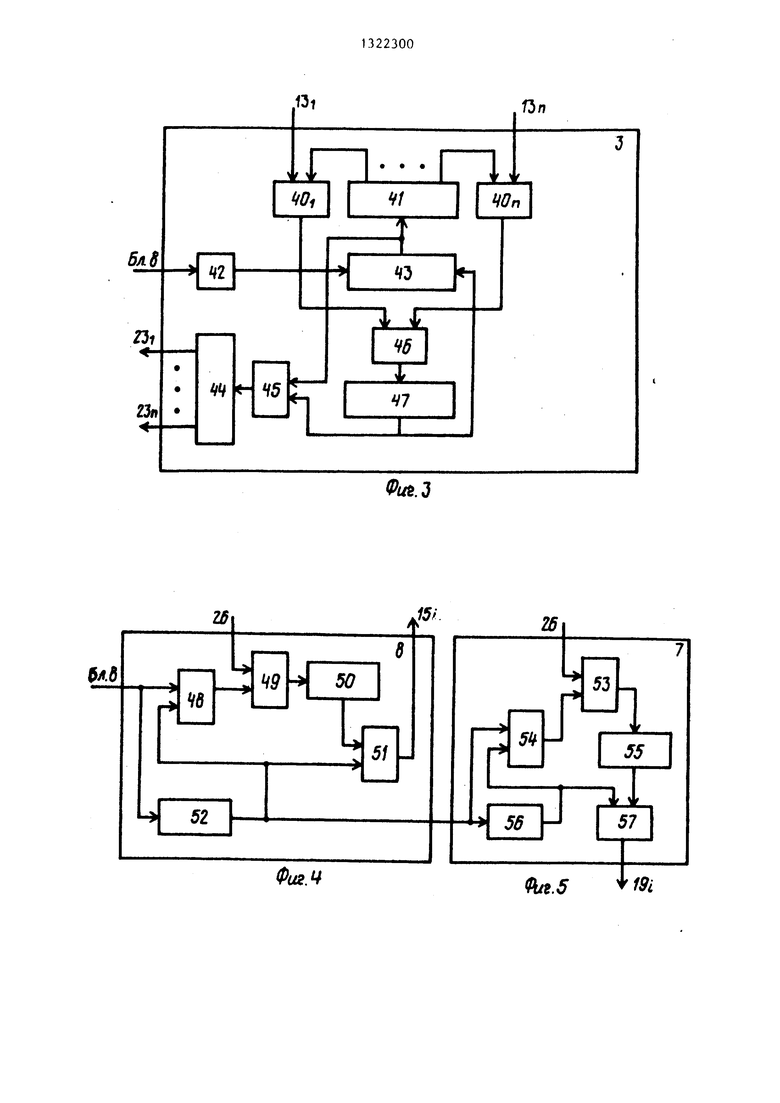

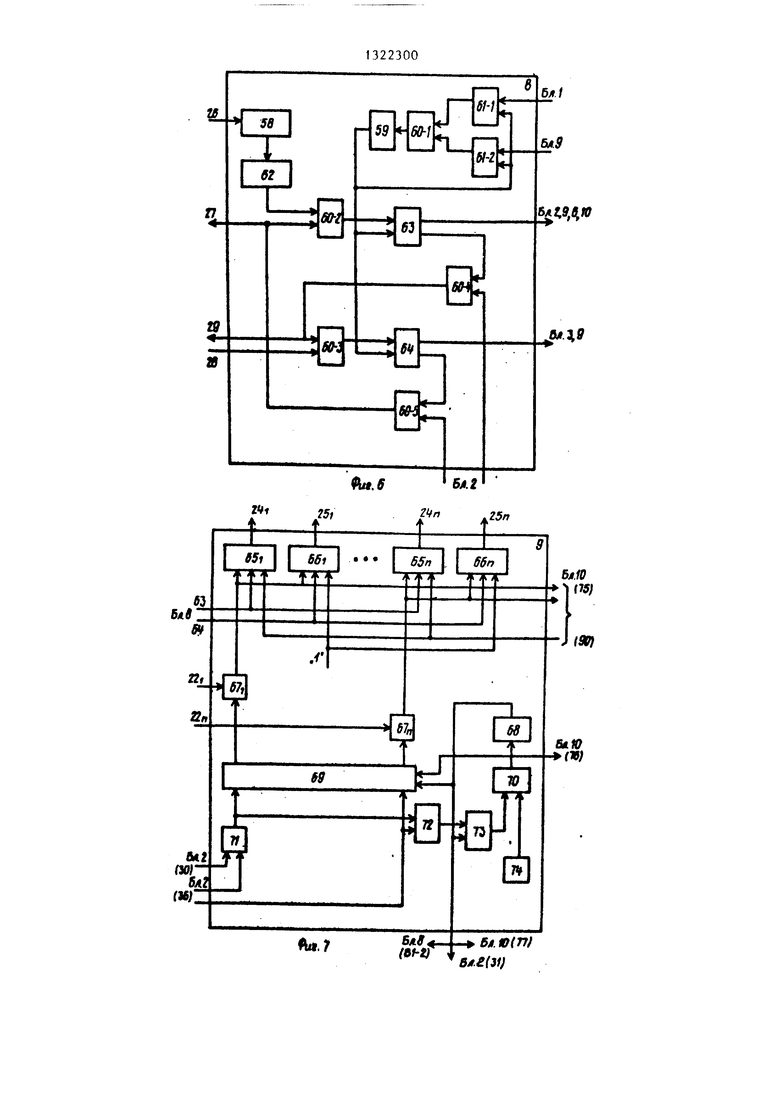

Блок 8 задания режима работы обеспечивает выбор режима работы устройства: Запись сообщения и Вьщача сообщения и содержит (фиг. 6) регистр 58, формирователь импульса (дифференцирующую цепочку) 59, элементы И 60-1 - 60-5, триггеры 61-1, 61-2, дешифратор 62, триггер 63 записи и триггер 64 считывания.

Блок 9 коррекции очереди предназначен для выдачи управляющих сигналов на соответствующие входы регист- ров 13 каналов 4,-4 в целях коррекции очереди при записи и вьщачи сообщений и содержит (фиг. 7) группы элементов И 65-67, счетчик 68, кольцевой регистр 69 сдвига, элемент И 70, элемент ИЛИ 71 с элементом задержки по первому входу (не показан), узел 72 запуска, триггер 73 и генератор 74 тактовых импульсов.

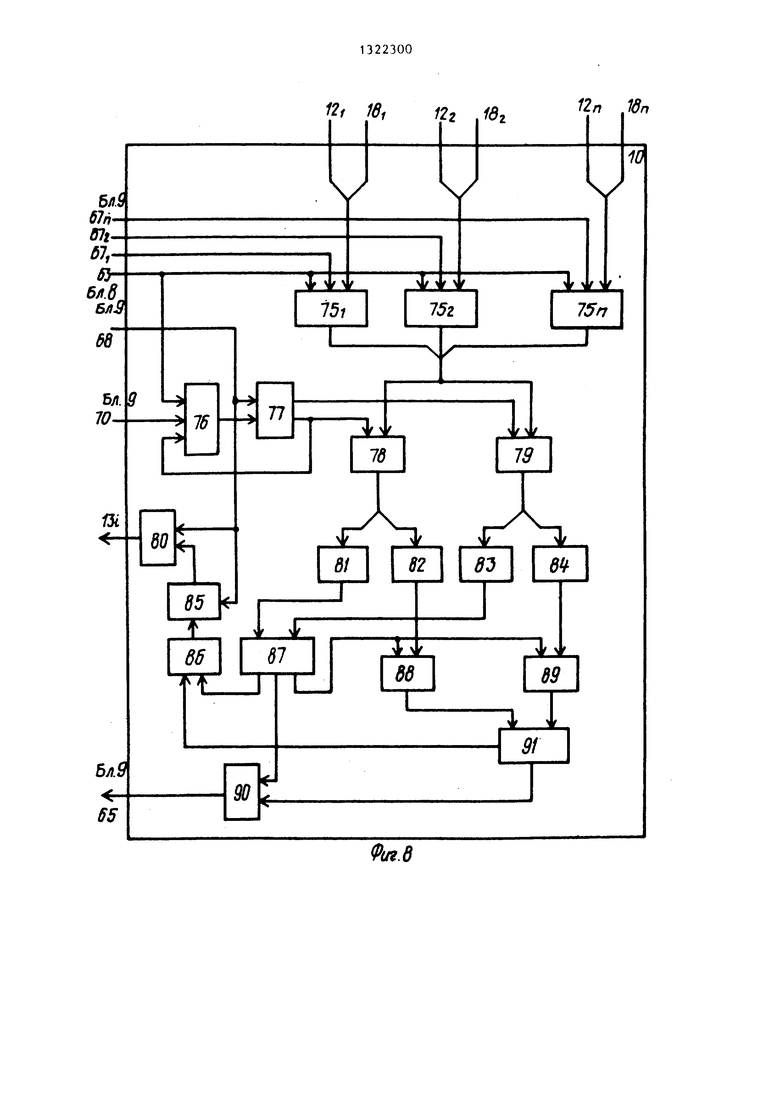

Блок 10 постановки сообщения в очередь на основе анализа кодов приоритетов, храняп хся в регистрах 12, кодов времени поступления сообщений сеть, хранящихся в регистрах 18, вырабатывает значения номеров позиций очереди для поступающих в устройство сообщений и содержит (фиг. 8) элементы И 75,-75„, элемент И 76, триггер 77, элементы И 78-80, регистры 81-85 элемент ИЛИ 86, компаратор 87,группы элементов И 88 и 89, элемент ИЛИ 90 и компаратор 91.

Узел 36 поиска левой единицы и узел 34 анализа (фиг. 9) содержат рлемент НЕ-ШШ 92, элемент ИЛИ 93, элементы И 94 и элементы НЕ 95.

Узел 72 запуска состоит из элемента ИЛИ 96 и триггера 97.

Устройство предназначено для работы в двух режимах.

В первом режиме (Запись сообщения) осуществляется прием сообщения по входу 26 от источника информации (канала связи) и постановка его в очередь.

Во втором режиме (Вьщача сообще- ния) осуществляется выдача в ЦВМ старшего по приоритету сообщения из очереди.

В режиме Запись сообщения устройство работает следующим образом.

При наличии свободных каналов (зон памяти) блок 2 вьщает соответствующий сигнал блоку 8 задания режима работы, который при получении данног сигнала и отсутствии запроса от ЦВМ (на входе 28) вьщает в сторону источника сообщения сигнал готовности устройства к приему сообщения.

s

o 5

0 5 Q

0

0

Если свободные каналы (зоны памяти) отсутствуют, блок 8, получив соответствующий сигнал из блока 2, блокирует запись сообщения и выдает на выход 27 в сторону источника сообщений сигнал занятости.

При поступлении сообщения на вход 26 блок 8 осуществляет выдачу управляющих сигналов блокам 2, 6, 9 и 10.

В блоке 2 по этому сигналу производится выбор свободного канала (зоны памяти).

На соответствующем выходе 21 появляется управляющий сигнал, который открывает коммутаторы 14-16 и 19 одно- одноименных свободного канала 41 и блока 51. Сформированный блоком 2 код номера свободной зоны памяти, в которую записывается поступающее сообщение, выдается в блок 1 памяти и в регистр 11 выбранного канала 4.

В блоке 6 при поступлении управляющего сигнала от блока 8 осуществляется вьщеленив из заголовка сообщения кода приоритета, а в блоке 7 отсчета времени - кода времени поступления сообщения в сеть обмена, которые записываются в регистры 12 и 18.

Блоки 9 и 10 при поступлении управляющего сигнала из блока 8 осуществляют формирование кода номера позиции в очереди для поступившего сообщения и, в случае необходимости, коррекцию очереди. В отличие от известного устройства формирование кода номера позиции в очереди для поступившего сообщения осуществляется в предлагаемом устройстве с учетом не только категории (важности), но и времени поступления в сеть обмена для одноприоритетных сообщений.

Блок 10 производит сравнение кодов приоритетов поступившего и находящихся в очереди сообщений, а в случае их равенства - и кодов времени поступления в сеть обмена. Результат сравнения выдается блоку 9, который обеспечивает выдачу управляющего сигнала на выходе 24j в случае, если приоритет поступившего сообщения выше приоритета сообщения, стоящего в очереди, или если поступившее сообщение обладает меньшим лимитом времени при равенстве приоритетов. Данным сигналом обеспечивается увеличение на единицу содержимого регистра 13 канала 4j. В противном случае, текущее (промежуточное) значение номера позиции

513

в очереди для поступившего сообщения увеличивается на единицу (в исходном состоянии значение номера позиции в очереди поступившего сообщения равно единице).

Подобные операции сравнения кодов приоритета и времени поступления сообщений в сеть обмена производятся (п-1) раз, где п - число каналов. В результате выполнения данных операций в блоке 10 формируется код номера позиции в очереди для поступившего сообщения, а блоком 9 осуществляется в случае необходимости, коррекция очереди.

После завершения формирования кода номера позиции в очереди для поступившего сообщения блок 9 осуществляет выдачу управляю1цих сигналов в блоки 2, 8 и 10, по которым осуществля- ется приведение в исходное состояние элементов данных блоков, а также запись сформированного в блоке 10 кода номера позиции в очереди для поступившего сообщения в регистр 13 канала 41,

При завершении записи в блок 1 памяти последний вьщает блоку 8 соответствующий сигнал, при этом, если формирование и запись в регистр 13 канала 41 кода номера позиции в очереди для поступившего сообщения также

завершено, то блок 8 выдает на вход 29 устройства сигнал, извещаюш 1й ЦВМ о наличии в устройстве сообщения.

На выходе 27 устройства в сторону источника сообщений передается соответствующий сигнал, в зависимости от наличия свободных каналов (зон памяти) .

На период записи сообщения в блоке 1 памяти и формирования кода номера позициии в очереди для поступившего сообщения запросы от ЦВМ на входе 28 устройства блокируются, при этом на выход 29 устройства в сторону ЦВМ передается соответствующий сигнал.

Второй режим (Выдача сообщения) реализуется при наличии сообщений в устройстве и поступлении сигнала вызова сообщения, стоящего на первом месте в очереди, на вход 28 устройства.

чивает вьщачу соответствующих сигнаПри наличии сообщений в устройстве лов в сторону источников сообщений на выход 29 блоком 8 в сторону ЦВМ (выход 27 устройства) и ЦВМ (выход выдается соответствующий сигнал. 29 устройства) в зависимости от напи- При поступлении сигнала вызова чия сообщений в устройстве и свобод- сообщения на входе 28 блок 8 осуще- ных зон памяти. На период ввдачи со

5

0

5

0

5

0

5

0

ствляет выдачу управляющих сигналов блокам 3 и 9.

В блоке 3 при воздействии управляющего сигнала из блока 8 осуществляется сравнение кодов, хранящихся в регистрах 13 каналов 4, и вьщача сигнала на выходе 23, открывающего коммутатор 17 того канала 4, в котором хранится признак сообщения, стоящего на первом месте в очереди. В качестве признака сообщения выступает адрес (номер зоны памяти), по которому хранится данное сообщение в блоке 1. При этом адрес сообщения, стоящего на первом месте в очереди, через открытый коммутатор 17 канала 4 поступает в блок 1 памяти. По этому адресу из блока 1 на вькод 20 устройства, производится считывание сообщения .

Сигнал на выходе 23k блока 3 воздействует также на блок 2, в котором производится предварительная отметка об освобождении k-ro канала (зоны памяти). В свою очередь блок 2 выдает сигнал, обеспечивающий запуск блока 9, который уже настроен на режим коррекции очереди управляющим сигналом из блока 8.

На соответствующих выходах 25 блока 9 появляется сигнал, обеспечивающий уменьшение на единицу содержимого регистров 13 занятых каналов. Такое изменение номеров позиций очереди означает продвижение очереди. Один из этих сигналов переводит регистр 13 канала 4k в нулевое (незанятое) состояние.

После завершения коррекции очереди блок 9, как и в первом режиме, выдает соответствующие сигналы в блоки 2, 8 и 10, причем в блоке 10 при воздействии данного сигнала в режиме Выдача сообщения изменений состояний элементов не происходит.

В блоке 2 при получении сигнала из блока 9 производится отметка об освобождении k-ro канала и приведение в исходное состояние элементов блока.

Блок 8, получив сигнал из блока 9 о завершении коррекции очереди, а также сигнал из блока 1 об окончании считывания сообщения в ЦВМ, обеспеобщений блок 8 блокирует поступление новых сообщений, при этом источнику сообщения передается соответствующий сигнал (выход 27) о занятости устройства ,

В режиме Запись обобщения при наличии хотя бы одного свободного канала на выходе элемента НЕ-ИЛИ 92 узла 34 (фиг. 9) устанавливается сигдействует на узел 37, на выходе которого появляется код номера выбранного канала 4 (зоны памяти). Кроме того, этим же импульсом обеспечивается опрокидывание соответствующего триггера 35 состояния канала, тем самым производится отметка о занятии данного канала, а также запись единицы в i-й разряд регистра 69 блока 9, Сигнал

нал логической 1, который воздейст-JO логической 1 на соответствующем вы- вует на вход элемента И 60-5 (фиг.6). В исходном состоянии (при отсутствии запросов от ЦВМ) с выхода триггера 64 на вход элемента И 60-5 подается сигнал логической 1, который с выхо- 15 бодной зоны памяти подается в блок да элемента И 60-5 воздействует на 1 памяти и на информационный вход

ходе 21 поступает на управляющие входы коммутаторов 14-16 и 19 выбранных канала 4 и блока 5 (фиг. 1,2). С выхода узла 37 блока 2 код номера свокоммутатора 14 канала 41. Поступающее сообщение записывается в свободную зону памяти, а номер данной зоны (адрес) - в регистр 11 выбранного канала 41.

вход элемента И 60-2 и на выход 27 устройства. Появление сигнала логической 1 на выходе 27 обеспечивает оповещание источника сообщений о готовности устройства к работе (к приему сообщения).

При записи в регистр 58 признака начала сообщения на выходе депшфрато- ра 62 появляется импульс, которьй через открытый элемент И 60-2 воздействует на установочный вход триггера 63, вызывая его опрокидывание.

На инверсном выходе триггера 63 устанавливается сигнал логического

кого II

О, который, воздействуя на вход элемента И 60-4, закрывает его.

На выходе 29 и входе элемента И 60-3 устанавливается сигнал логичес 0, тем самым производится извещение ЦВМ о занятости устройства и блокирование запросов от ЦВМ на период записи и постановки сообщения в очередь.

Если свободные каналы (зоны памя- ти) отсутствуют, то на выходе элемента И 60-5 устанавливается сигнал логического О, который выдается на выход 27 (в сторону источника сообщений) и на вход элемента И 60-2, тем самым производится блокирование записи сообщений.

На прямом выходе триггера 63 при наличии свободных каналов устанавли

вается сигнал логической 1, который Q сообщения в сеть на выходе счетчика транслируется в блоки 2, 6, 9 и 10. 56 появляется управляющими сигнал, В блоке 2 данный сигнал подается на дифференцирующую цепочку 39, на выходе которой появляется импульс, воздействующий на узел 36. (фиг. 2,9). « соответствующем выходе узла

На

36 появляется импульс, который устанавливает соответствующий триггер 38 в единичное состояние,а также возобеспечивающий сброс триггера 54 и пись кода времени поступления в регистр 18 блока 51 (фиг. 5,1). Цепь записи: регистр 55, элемент И 57, от крытый коммутатор 19 блока 5,регистр 18.

Появление импульса на соответству щем выходе узла 36 (фиг. 2) вызывает

действует на узел 37, на выходе которого появляется код номера выбранного канала 4 (зоны памяти). Кроме того, этим же импульсом обеспечивается опрокидывание соответствующего триггера 35 состояния канала, тем самым производится отметка о занятии данного канала, а также запись единицы в i-й разряд регистра 69 блока 9, Сигнал

логической 1 на соответствующем вы- бодной зоны памяти подается в блок 1 памяти и на информационный вход

ходе 21 поступает на управляющие входы коммутаторов 14-16 и 19 выбранных канала 4 и блока 5 (фиг. 1,2). С выхода узла 37 блока 2 код номера свологической 1 на соответствующем вы- бодной зоны памяти подается в блок 1 памяти и на информационный вход

коммутатора 14 канала 41. Поступающее сообщение записывается в свободную зону памяти, а номер данной зоны (адрес) - в регистр 11 выбранного канала 41.

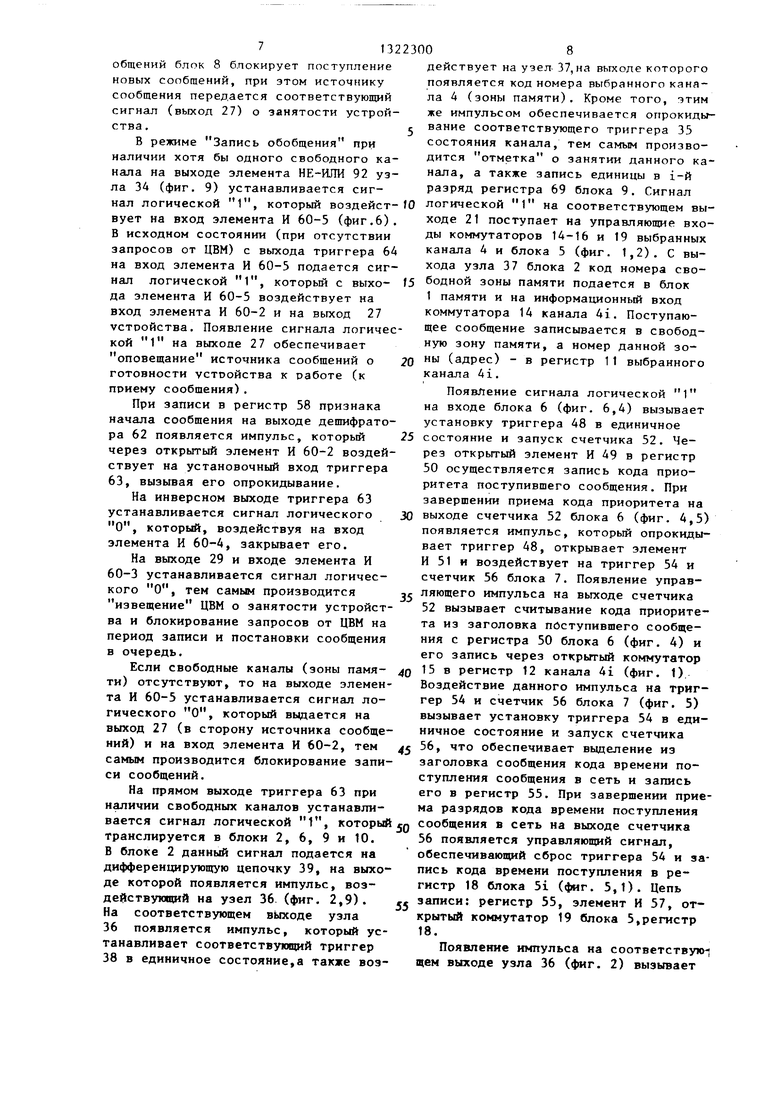

Появление сигнала логической 1 на входе блока 6 (фиг. 6,4) вызывает установку триггера 48 в единичное состояние и запуск счетчика 52. Через открытый элемент И 49 в регистр 50 осуществляется запись кода приоритета поступивщего сообщения. При завершении приема кода приоритета на выходе счетчика 52 блока 6 (фиг. 4,5) появляется импульс, который опрокидывает триггер 48, открывает элемент И 51 и воздействует на триггер 54 и счетчик 56 блока 7. Появление управ- ляющего импульса на выходе счетчика 52 вызывает считывание кода приоритета из заголовка поступившего сообщения с регистра 50 блока 6 (фиг. 4) и его запись через открытый коммутатор 15 в регистр 12 канала 41 (фиг. 1). Воздействие данного импульса на триггер 54 и счетчик 56 блока 7 (фиг. 5) вызывает установку триггера 54 в единичное состояние и запуск счетчика 56, что обеспечивает выделение из заголовка сообщения кода времени поступления сообщения в сеть и запись его в регистр 55. При завершении приема разрядов кода времени поступления

сообщения в сеть на выходе счетчика 56 появляется управляющими сигнал,

обеспечивающий сброс триггера 54 и запись кода времени поступления в регистр 18 блока 51 (фиг. 5,1). Цепь записи: регистр 55, элемент И 57, открытый коммутатор 19 блока 5,регистр 18.

Появление импульса на соответствующем выходе узла 36 (фиг. 2) вызывает

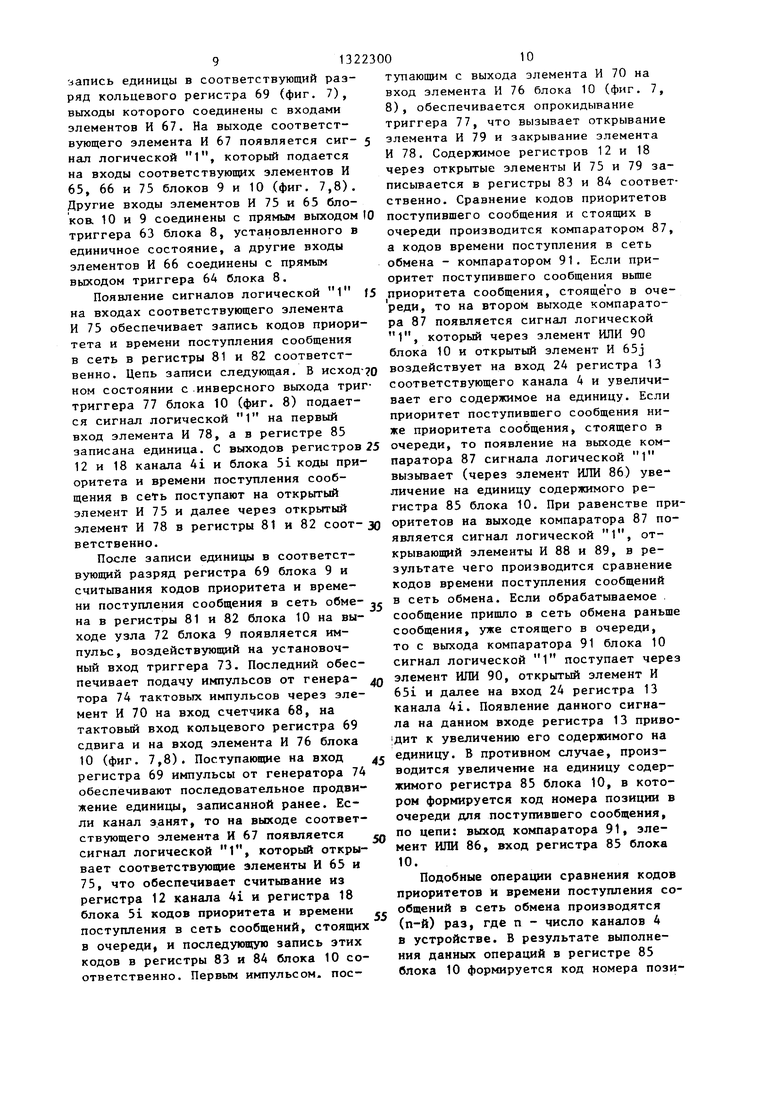

запись единицы в соответствующий разряд кольцевого регистра 69 (фиг. 7), выходы которого соединены с входами элементов И 67. На выходе соответствующего элемента И 67 появляется сиг- нал логической 1, который подается на входы соответствующих элементов И 65, 66 и 75 блоков 9 и 10 (фиг. 7,8). Другие входы элементов И 75 и 65 бло- коа 10 и 9 соединены с прямым выходом триггера 63 блока 8, установленного в единичное состояние, а другие входы элементов И 66 соединены с прямым выходом триггера 64 блока 8.

Появление сигналов логической 1 на входах соответствующего элемента И 75 обеспечивает эапись кодов приоритета и времени поступления сообщения в сеть в регистры 81 и 82 соответственно. Цепь записи следующая. В исход ном состоянии с инверсного выхода три триггера 77 блока 10 (фиг. 8) подается сигнал логической 1 на первый вход элемента И 78, а в регистре 85 записана единица. С выходов регистров 12 и 18 канала Ai и блока 5i коды приоритета и времени поступления сообщения в сеть поступают на открытый элемент И 75 и далее через открытый элемент И 78 в регистры 81 и 82 соответственио.

После записи единицы в соответствующий разряд регистра 69 блока 9 и считывания кодов приоритета и времени поступления сообщения в сеть обме- на в регистры 81 и 82 блока 10 на выходе узла 72 блока 9 появляется импульс, воздействующий на установочный вход триггера 73. Последний обеспечивает подачу импульсов от генера- тора 74 тактовых импульсов через элемент И 70 на вход счетчика 68, на тактовый вход кольцевого регистра 69 сдвига и на вход элемента И 76 блока 10 (фиг. 7,8). Поступающие на вход регистра 69 импульсы от генератора 74 обеспечивают последовательное продвижение единицы, записанной ранее. Если канал занят, то на выходе соответствующего элемента И 67 появляется сигнал логической 1, который открывает соответствую1цие элементы И 65 и 75, что обеспечивает считывание из регистра 12 канала 4i и регистра 18 блока 51 кодов приоритета и времени поступления в сеть сообщений, стоящих в очереди, и последующую запись этих кодов в регистры 83 и 84 блока 10 соответственно. Первым импульсом, поступающим с выхода элемента И 70 на вход элемента И 76 блока 10 (фиг. 7, 8), обеспечивается опрокидывание триггера 77, что вызывает открывание элемента И 79 и закрывание элемента И 78. Содержимое регистров 12 и 18 через открытые элементы И 75 и 79 записывается в регистры 83 и 84 соответственно. Сравнение кодов приоритетов поступившего сообщения и стоящих в очереди производится компаратором 87 а кодов времени поступления в сеть обмена - компаратором 91. Если приоритет поступившего сообщения вьппе приоритета сообщения, стояще го в оче- реди, то на втором выходе компаратора 87 появляется сигнал логической 1, который через элемент ИЛИ 90 блока 10 и открытый элемент И 65j воздействует на вход 24 регистра 13 соответствующего канала 4 и увеличивает его содержимое на единицу. Если приоритет поступившего сообщения ниже приоритета сообщения, стоящего в очереди, то появление на выходе компаратора 87 сигнала логической 1 вызывает (через элемент ИЛИ 86) увеличение на единицу содержимого регистра 85 блока 10. При равенстве приоритетов на выходе компаратора 87 появляется сигнал логической 1, открывающий элементы И 88 и 89, в результате чего производится сравнение кодов времени поступления сообщений в сеть обмена. Если обрабатываемое сообщение пришло в сеть обмена раньше сообщения, уже стоящего в очереди, то с выхода компаратора 91 блока 10 сигнал логической 1 поступает через элемент ИЛИ 90, открытый элемент И 651 и далее на вход 24 регистра 13 канала 41. Появление данного сигнала на данном входе регистра 13 приво- 1ДИТ к увеличению его содержимого на единицу. В противном случае, производится увеличение на единицу содержимого регистра 85 блока 10, в котором формируется код номера позиции в очереди для поступившего сообщения, по цепи: выход компаратора 91, элемент ИЛИ 86, вход регистра 85 блока 10.

Подобные операции сравнения кодов приоритетов и времени поступления сообщений в сеть обмена производятся (п-й) раз, где п - число каналов 4 в устройстве. В результате выполнения данных операций в регистре 85 блока 10 формируется код номера позиции 3 очереди для поступившего сообщения и производится, в случае необходимости, коррекция очереди.

При поступлении на вход счетчика

68блока 9 (фиг. 7) с выхода элемента И 70 (п-1)-го импульса на его выходе появляется импульс, который воздействует на входы триггера 73 и регистра

69блока 9, приводя их в исходное состояние. Кроме того, данный импульс передается в блоки 10, 2 и 8. При поступлении этого импульса в блок 10 производится приведение в исходное состояние триггера 77 и запись сформированного кода номера позиции в ре- гистр 13 канала 4 по следующей цепи: выход регистра 85. иткрытьй элемент

И 80, коммутатор 16, регистр 13, Кроме того, данный импульс, воздействуя на вход регистра 85 с некоторой за- /хержкой (элемент задержки не показан) 1ФОИЗВОДИТ приведение в исходное состояние регистра 85.

При появлении импульса с выхода счетчика 68 в блоке 2 производится сброс триггеров 38 управления,

В блоке 8 данный импульс вызывает установку триггера 61-2 завершения операции в единичное состояние. При завершении записи сообщения в блок 1 памяти (фактом завершения записи сообщения может выступать запись признака конца сообщения) с вьсхода блока 1 на установочный вход триггера 61-1 поступает импульс, который переводит данный триггер в единичное состояние. На выходе элемента И 60-1 устанавливается сигнал логической 1 который воздействует на вход дифференцирующей цепочки 59 блока 8. На выходе дифференцирующей цепочки 59 появляется импульс, который приводит в исходное состояние триггеры 63, 64 61-1 и 61-2. На этом запись и постановка сообщения в очередь заканчива- ются. На выходах 27 и 29 устройства устанавливаются соответствующие сигналы в зависимости от наличия сообщений в устройстве и свободных каналов (зон) памяти.

Второй режим (Ввдача сообщения) реализуется при наличии сообщений в устройстве и поступлении сигнала вызова сообщения, стоящего на первом месте в очереди, на вход 28 устройства.

При наличии сообщений в устройстве на втором выходе узла 34 блока 2 (фиг. 2) устанавливается сигнал логической 1, который воздействует на вход элемента И 60-4 блока 8, На другон вход этого элемента подается сигнал логической 1 с инверсного выхода триггера 63 (фиг, 6), На выходе элемента И 60-4 устанавливается сигнал логической 1, KOTopbDi воздействует на вход элемента И 60-3 и на вхо

29устройства.

Появление данного сигнала на выходе 29 устройства информирует ЦВМ о наличии в устройстве сообщений.

При поступлении сигнала вызова сообщения на входе 28 триггер 64 устанавливается в единичное состояние через элемент И 60-3, На инверсном выходе данного триггера устанавливается сигнал логического О, что приводит к блокированию режима Запись сообщения за счет трансляции данного сигнала (через элемент И 60-5) на вход 27

С прямого выхода триггера 64 сигнал логической 1 транслируется в блоки 3 и 9,

При воздействии данного сигнала на блок 3 на выходе дифференцирующей цепочки 42 (фиг, 3) появляется импульс, который обеспечивает запуск счетчика 43, соединенного по выходу с узлом 41. На выходах узла 41 появляются сигналы, обеспечивающие последовательное открывание элементов И 40 с целью считывания из регистров 13 кода номера позиции сообщения в очереди. Считанные коды поступают через элемент ИЛИ 46 в элемент И 47, Если принятый код равен единице, то на выходе схемы элемента И 47 появляется сигнал, который останавливает счетчик 43 и открывает элемент 45. Содержимое счетчика 43 (код номера канала 4k, в котором хранится сообщение, стоящее на первой позиции в очереди) поступает на вход узла 44. На выходе 23k и узла 44 появляется сигнал, открывающий коммутатор 17 канала 4k и устанавливающий в единичное состояние соответствующий буферный триггер 32k блока 2. При этом адрес хранения сообщения поступает в блок 1 с выхода регистра 11 канала 4k через открытый коммутатор 17. По этому адресу из блока 1 на выход 20 устройства производится считывание сообщения.

Появление сигнала на выходе 23k блока 3 вызывает через элементы ИЛИ

30и 71 запись с некоторой задержкой единицы в первый разряд регистра 69 блока 9. Как и в первом режиме работы, осуществляется запуск счетчика 68 и последовательное продвижение единицы по разрядам регистра 69. С прямого выхода триггера 64 на входы элементов И 66 подается сигнал логической 1 (фиг. 6, 7).

При продвижении единицы по разрядам регистра 69 на соответствующих выходах элементов И 67 появляется синал логической 1, который через соответствующий открытый элемент И 66 воздействует на вход 25 соответствующего регистра 13. Данным сигна- лом обеспечивается уменьщение на единицу содержимого регистров 13 заняты каналов. Такое изменение номеров позиций очереди означает продвижение очереди. Один из этих сигналов пере- водит соответствующий регистр в одном из каналов Ak в незанятое состояние .

Как и в первом режиме работы, после (п-1) такта на выходе счетчика 68 блока 9 появляется сигнал, приводящий в исходное состояние регистр 69 и триггер 73. Кроме того, данный сигнал транслируется в блоки 10, 2 и 8. В блоке 10 в данном режиме сигнал с выхода счетчика 68 изменений состояний элементов блока 10 не производит При поступлении данного сигнала в блок 2 открываются элементы И 33 и производится установка в единичное состояние соответствующего триггера 35k,тем самым отмечается, что канал 4k свободен. Этим же сигналом через элемент 31-1 задержки производится сброс триггеров 32. Воздействие дан- ного сигнала через элемент 31-2 задержки на триггеры 38,-38„ не изменяет состояния последних.

Приведение в исходное состояние элементов блока 8 осуществляется как и в первом режиме работы.

Формула изобретени

1. Устройство для сопряжения ЦВМ с абонентами, содержащее блок памяти, первый выход которого является вькодом устройства для подключения информационного входа ЦВМ, а информационный вход соединен с информационным входом блока формирования кода приоритета и является входом устройства для подключения информационных выходов абонентов, блок выбора кана

5 0

5 0 c Q

5

0

5

ла, первый выход которого соединен с адресным входом блока памяти, блок коррекции очереди, первый выход и вход запуска которого подключены соответственно к входу установки исходного состояния и второму выходу блока выбора канала, блок опроса каналов и группу каналов, каждый из которых состоит из четырех коммутаторов, регистра признаков канала, соединенного входом и выходом соответственно с выходом первого и информационным входом второго коммутаторов, регистра номера позиции очереди канала, соединенного информационным входом с выходом третьего коммутатора, и регистра приоритета, подключенного входом к выходу четвертого коммутатора, причем группа адресных входов блока памяти соединена с выходами вторых коммутаторов каналов группы, управляю- цие входы которых соединены с группой выходов блока опроса каналов и группой входов состояния каналов блока выбора канала, i-м выходом первой группы выходов (,n) подключенного к управляющим входам первого, третьего и четвертого коммутаторов i-ro канала группы, группа входов состояния очереди блока коррекции очереди соединена с второй группой выходов блока выбора канала, первым выходом подключенного к информационным входам первых коммутаторов каналов группы, информационные входы четвертых коммутаторов каналов группы соединены с первым выходом блока формирования кода приоритета, группа информационньтх входов блока опроса каналов подключена к выходам регистров номера позиции очереди канала каналов группы, входы прямой и обратной модификации которых соединены соответственно с первой и второй группами выходов блока коррекции очереди, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет динамического изменения порядка вьщачи сообщений в ЦВМ с учетом времени их поступления от абонента, в него введены блок постановки сообщения в очередь, блок задания режима работы, блок отсчета времени и группа блоков временных меток, каждый из которых состоит из коммутатора, выходом соединенного с входом регистра признака времени, причем управляющий вход коммутаторов i-ro блока временных меток группы

соединен с i-м выходом первой группы выходов блока выбора канала, а информационный вход - с выходом блока отсчета времени, синхронизирующий вход которого соединен с вторым выхо дом блока формирования кода приори- тета, а информационный вход соединен с входом устройства для подключения информационных выходов абонентов к информационным входам блока задания режима работы, первый выход и вход разрешения которого соединены соответственно с входами разрешения и третьим выходом блока выбора канала, второй выход блока задания режима работы является выходом устройства для подключения к синхронизирующим входам абонентов, а третий выход и вход запроса являются соответственно выходом и входом устройства для под- ключения синхронизирующих входа и выхода ЦВМ, вход установки исходного состояния и вход конца цикла обращеустановочным входом триггера, инверсный и прямой выходы которого подключены соответственно к управляющим входам элементов И первой и второй групп, информационными группами подключенных к выходам первого, второго и третьего узлов элементов И, входы первого и второго регистра соединены с выходами элементов И первой группы, входы третьего и четвертого регистров подключены к выходам элементов И второй группы, выходы элементов И третьей группы образуют первый выход блока, первый и второй выходы первого компаратора подключены соответственно к выходам первого и третьего регистров, а первый, второй и третий вьпсоды - соответственно к первым входам первого и второго элементов ИЛИ и к управляющим входам элементов И четвертой и пятой групп, информационные входы которых соединены соответственно с выходами второго и четвертого регистров, а выходы - соответственно с

ния к памяти блока задания режима работы соединены соответственно с пер- 5 первым и вторым входами второго ком- вым выходом блока коррекции очереди и паратора, первым и вторым выходами вторым выходом блока памяти, первый подключенного к вторым входам первого выход блока задания режима работы сое- и второго элементов ИЛИ, выходы кото- динен с входом разрешения блока формирования кода приоритета, с входами режима приема блока коррекции очереди и блока постановки сообщения в очередь, группа входов которого подключена к выходам регистров приоритета каналов группы и вьпсодам регистров узлов элементов И, второй вход элемен- признака времени блоков временных ме- та И, вход сброса пятого регистра, ток группы, информационные входы третьих коммутаторов каналов группы соединены с первым выходом блока постановки сообщения в очередь, второй вы- 40 вход блока,третий вход элемента И ход и управляющий вход которого сое- соединен с инверсным выходом триггера динены соответственно с синхронизирующим входом и вторым выходом блока коррекции очереди, входом режима вьщарых соединены соответственно с входом 30 модификации пятого регистра и вторым выходом блока, выход пятого регистра соединен с информационными входами элементов И третьей группы, вторые управляющие входы первого-третьего

соединенный с входом сброса триггера и управляющими входами элементов И третьей группы, образуют управляющий

3. Устрвйство по п. 1, отличающееся тем, что блок задания режима работы содержит регистр,

чи соединенного с четвертым выходом блока задания режима работы и управляющим входом блока опроса каналов. 2. Устройство по п. 1, отличающееся тем, что блок постановки сообщения в очередь содержит группу узлов элементов И, триггер, пять групп элементов И, пять регистров, два компаратора, два элемента ИЛИ и элемент И, причем информационные входы узлов элементов И группы об- установки в исходное состояние блока, разуют группу входов блока, первые а входы сброса соединены с входами управляющие входы соединены с входом сброса триггеров записи и считыва- режима приема блока и первым входом ния и через формирователь импульса с элемента И, выходом соединенного с выходом rtepBoro элемента И, первый

установочным входом триггера, инверсный и прямой выходы которого подключены соответственно к управляющим входам элементов И первой и второй групп, информационными группами подключенных к выходам первого, второго и третьего узлов элементов И, входы первого и второго регистра соединены с выходами элементов И первой группы, входы третьего и четвертого регистров подключены к выходам элементов И второй группы, выходы элементов И третьей группы образуют первый выход блока, первый и второй выходы первого компаратора подключены соответственно к выходам первого и третьего регистров, а первый, второй и третий вьпсоды - соответственно к первым входам первого и второго элементов ИЛИ и к управляющим входам элементов И четвертой и пятой групп, информационные входы которых соединены соответственно с выходами второго и четвертого регистров, а выходы - соответственно с

первым и вторым входами второго ком- паратора, первым и вторым выходами подключенного к вторым входам первого и второго элементов ИЛИ, выходы кото- узлов элементов И, второй вход элемен- та И, вход сброса пятого регистра, вход блока,третий вход элемента И соединен с инверсным выходом триггера

первым и вторым входами второго ком- паратора, первым и вторым выходами подключенного к вторым входам первого и второго элементов ИЛИ, выходы кото- узлов элементов И, второй вход элемен- та И, вход сброса пятого регистра, вход блока,третий вход элемента И соединен с инверсным выходом триггера рых соединены соответственно с входом модификации пятого регистра и вторым выходом блока, выход пятого регистра соединен с информационными входами элементов И третьей группы, вторые управляющие входы первого-третьего

первым и вторым входами второго ком- паратора, первым и вторым выходами подключенного к вторым входам первого и второго элементов ИЛИ, выходы кото- узлов элементов И, второй вход элемен та И, вход сброса пятого регистра, вход блока,третий вход элемента И соединен с инверсным выходом триггера

соединенный с входом сброса триггера и управляющими входами элементов И третьей группы, образуют управляющий

5 первым и вторым входами второго ком- паратора, первым и вторым выходами подключенного к вторым входам первого и второго элементов ИЛИ, выходы кото- узлов элементов И, второй вход элемен- та И, вход сброса пятого регистра, 40 вход блока,третий вход элемента И соединен с инверсным выходом триггера

3. Устрвйство по п. 1, отличающееся тем, что блок задания режима работы содержит регистр,

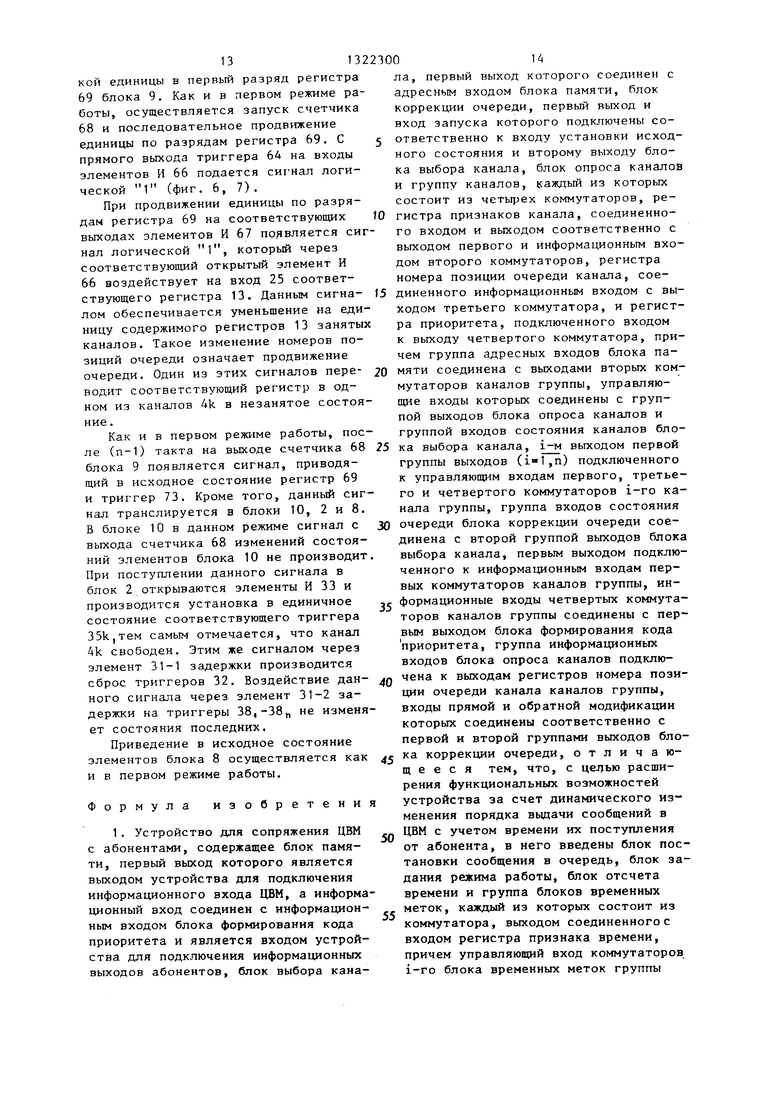

4 дешифратор, пять элементов И, формирователь импульса, триггер записи, триггер считывания и два триггера завершения операции, причем первый и {второй входы первого элемента И соееп динены соответственно с выходами первого и второго триггеров завершения операции, установочные входы которых являются соответственно входом конца цикла обращения к памяти и входом

17132230018

вход второго элемента И соединен через дешифратор с выходом регистра, вход которого является информационным входом блока, первый вход третьего элемента И является входом эапро- са блока, установочные входы триггеров записи и считывания соединены соответственно с выходами второго и третьего элементов И, а инверсные вЫходы.- соответственно с первыми входами О входами элементов И второй группы, четвертого и пятого элементов И, вто- выходы которых образуют первый выход рые входы которых образуют вход разрешения блока, а выходы соединены соответственно с вторыми входами третьего и второго элементов И и явля- 5 счетчика, входом соединенного с уста- ются третьим и вторым выходами- блока, новочным входом триггера и разрешаь- прямые выходы триггеров записи и счи- входом блока, выход счетчика сое- тывания являются соответственно первым и четвертым выходами блока.

4. Устройство поп. 1,отли- 20 чающееся тем, что блок отсчета времени содержит две группы элементов И, регистр, счетчик и триггер

6. Устройство по п. 1, отличающееся тем, что блок формирования кода приоритета содержит триггер, две группы элементов И и счетчик, причем информационные входы элементов И первой группы образуют информационный вход блока, а выходы соединены с входом регистра, выходы которого соединены с информационными

блока, управляющие входы элементов И первой и второй групп подключены соответственно к выходам триггера и

запуска, причем информационные входы

динен с входом сброса триггера и вторым выходом блока.

7, Устройство по п. 1, отличающееся тем, что блок коррекции очереди содержит три группы элементов И, кольцевой регистр сдвига, счетчик импульсов, элемент ИЛИ и эле- элементов И первой группы образуют 25 мент И, причем выходы элементов И информационный вход устройства, уп- первой и второй групп образуют соот- равляющий вход соединен с выходом ветственно первую и вторую группу вы- триггера, установочный вход которо- ходов блока, первые входы подключены го соединен с синхронизирующим входом соответственно к входу режима приема блока и через счетчик - с управляю- 30 и входу режима выдачи блока, вторые щим входом элементов И второй группы, входы элементов И первой и второй информационные входы которых соединены через регистр с выходами элементов И первой группы, а выходы образуют выход блока, вход сброса триггера за- j ды - с выходами соответствующих эле- пуска подключен к выходу счетчика. ментов И третьей группы, первые входы

5. Устройство по п. 1, отличающееся тем, что блок опроса каналов содержит два узла дешифрации,

группу узлов элементов И, группу эле- 40 гистра сдвига, вход первого разряда ментов ИЛИ, счетчик, элемент И и фор- которого соединен с выходом элемента мирователь импульса, причем информационные входы узлов элементов И группы образуют группу входов блока, а управляющие входы подключены к группе 5 ная с группой разрядных входов узла выходов первого узла дешифрации, вход запуска, и первый и второй входы эле- которого соединен с группой выходов счетчика и информационными входами элементов И группы, выходы которых через второй узел дешифрации соедине- 50 через счетчик с входами сброса коль- ны с группой выходов блока, а управ- цевого регистра сдвига и триггера, ляющие входы подключены к выходу эле- установленный вход и выход которого мента И и входу останова счетчика, подключены соответственно к выходу входом пуска соединенного через фор- узла запуска и первому входу элемен- мирователь импульса с управляющим вхо-55 i вторым входом соединенного с дом блока, входы элементов ИЛИ группы выходом генератора тактовых импуль- соединены с выходами соответствующих сов, выходы элементов И третьей груп- узлов элементов И группы, а выходы - пы и выходы элемента И и счетчика об- с группой входов элемента И. разуют второй выход блока.

групп соединены соответственно с входом синхронизации блока и шиной логической единицы блока, а третьи вхокоторых образуют группу входов состояния очереди, а вторые входы подключены к группе выходов кольцевого реИЛИ и первым разрядным входом узла запуска, группа разрядных входов кольцевого регистра сдвига, соединенмента ИЛИ образуют вход пуска блока, выход элемента И соединен с тактовым входом кольцевого регистра сдвига и

6. Устройство по п. 1, отличающееся тем, что блок формирования кода приоритета содержит триггер, две группы элементов И и счетчик, причем информационные входы элементов И первой группы образуют информационный вход блока, а выходы соединены с входом регистра, выходы которого соединены с информационными

входами элементов И второй группы, выходы которых образуют первый выход счетчика, входом соединенного с уста- новочным входом триггера и разрешаь- входом блока, выход счетчика сое-

блока, управляющие входы элементов И первой и второй групп подключены соответственно к выходам триггера и

7, Устройство по п. 1, отличающееся тем, что блок коррекции очереди содержит три группы элементов И, кольцевой регистр сдвига счетчик импульсов, элемент ИЛИ и эле- мент И, причем выходы элементов И первой и второй групп образуют соот- ветственно первую и вторую группу вы- ходов блока, первые входы подключены соответственно к входу режима приема и входу режима выдачи блока, вторые входы элементов И первой и второй ды - с выходами соответствующих эле- ментов И третьей группы, первые входы

групп соединены соответственно с входом синхронизации блока и шиной логической единицы блока, а третьи вхокоторых образуют группу входов состояния очереди, а вторые входы подключены к группе выходов кольцевого регистра сдвига, вход первого разряда которого соединен с выходом элемента ная с группой разрядных входов узла запуска, и первый и второй входы эле- через счетчик с входами сброса коль- цевого регистра сдвига и триггера, установленный вход и выход которого подключены соответственно к выходу узла запуска и первому входу элемен- i вторым входом соединенного с выходом генератора тактовых импуль- сов, выходы элементов И третьей груп- пы и выходы элемента И и счетчика об- разуют второй выход блока.

ИЛИ и первым разрядным входом узла запуска, группа разрядных входов кольцевого регистра сдвига, соединенгистра сдвига, вход первого разряда которого соединен с выходом элемента ная с группой разрядных входов узла запуска, и первый и второй входы эле- через счетчик с входами сброса коль- цевого регистра сдвига и триггера, установленный вход и выход которого подключены соответственно к выходу узла запуска и первому входу элемен- i вторым входом соединенного с выходом генератора тактовых импуль- сов, выходы элементов И третьей груп- пы и выходы элемента И и счетчика об- разуют второй выход блока.

мента ИЛИ образуют вход пуска блока, выход элемента И соединен с тактовым входом кольцевого регистра сдвига и

ФигМ

Фи.

Фиг.5 19i

16i122 1вг

(Ри.6

(60-5J

ISO-It)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналами связи | 1983 |

|

SU1160421A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ | 1979 |

|

SU826332A1 |

| Устройство для обмена информацией | 1981 |

|

SU962901A2 |

| Устройство для сопряжения источников сообщения с цифровой вычислительной машиной | 1984 |

|

SU1196880A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для обмена информации | 1979 |

|

SU962909A2 |

| Многоканальный коммутатор | 1983 |

|

SU1086447A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обработки информации, поступающей из каналов связи от удаленных абонентов. Целью изобретения является расширение функциональных возможностей устройства путем динамического изменения порядка вьщачи сообщений в ЦВМ с учетом времени их поступления в сеть обмена. Это позволяет повысить вероятность своевременной доставки сообщений в ЦВМ и обеспечивается за счет учета при построении очереди сообщений не только категории срочности, но и времени поступления сообщения в сеть обмена. Для достижения цели в устройство, содержащее блок 1 памяти, блок 2 выбора канала, блок 3 опроса каналов, группу каналов 4, блок 9 коррекции очереди, блок 6 формирования кода приоритета, введены блок 7 отсчета времени, блок 8 задания режима работы, группу блоков 5 временных меток, блок 10 постановки сообщения в очередь. 6 з.п.ф-лы, 10 ил. I k/) а, Пп PU9l

бл2(30}

6/1. г (36)

т

6/1.2 (36)

Фм.Ю

,Составитель В.Вертлиб

Редактор И.Николайчук ТехреД И.Попович Корректор Л.Бескид

Заказ 2866/46 Тираж 672 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для сопряжения источников случайных потоков сообщений с цифровой вычислительной машиной | 1972 |

|

SU489100A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-10-01—Подача