ции очереди со второго по К-й соединены с управляклцими входами третьих ключей в блоках фиксации очереди с первого по К-1-й соответственно, выходы регистров приоритета блоков фиксации очереди с первого по К-2-й соединены с информационными входами шестых ключей блокЬв фиксации очереди, выходы регистрЬв приоритета в -блоках фиксации очереди с второго по К-й соединены с управляющими входами., четвертых ключей в блоках фиксации очереди с первого по К-1-й соответственно, выход регистра признака К-го блока фиксации очереди соединен с информационным входом выходного ключа, а выход регистра признака К-1-го блока фиксации очереди соединен с информационным входом третьего ключа К-го блока фиксации очереди, выход регистра приоритета К-1-го блока фиксации очереди соединен с информационным входом четвертого ключа К-го блока фиксации очереди, при этом в каждом блоке фиксации очереди со второго по К-1-й выходы пятого и шестого ключей соединены с третьими входами первого и второго элементов ИЛИ соответственно, отличающеес я тем, что, с целью расширения функциональных возможностей за счет возможности изменения приоритета поступающего сообщения в зависимости от состояния очереди, в него введены блок анализа состояния очереди, блок восстановления очереди, группа элементов ИЛИ, при этом в каждый блок фиксации очереди введены регистр кода сообщения и третий элемент ИЛИ, в первьй К-й блок фиксации очереди введены пятьй и шестой ключи, в блоки фиксации очереди со второго по К-1-й введены седьмой, восьмой, .девятый : ключи, причем первый вход блока анализа состояния очереди подсоединен к информационной шине источников сообщения , первый выход блока анализа состояния очереди соединен с информационными входами пятых ключей в первом и К-ом блоках фиксацир очереди и седьмых ключей в блоках фиксации очереди с второго по К-1-й, выходы регистров кода сообщения К блоков фиксации очереди соединены с группой входов блока.анализа состояния очереди, второй выход которого с информационным входом блока формирования кода приоритета, информационный выход которого соединен с вторым входом блока анализа состояния очереди, третий выход которого соединен с информационными входами вторых ключей К блоков фиксации очереди и с третьим входом блока управления, третья группа выходов которого соединена с первыми входами элементов ИЛИ группы, группа выходов которых соединена с .управляющими входами пятого, шестого и восьмого ключей в блоках фиксации очереди с второго по К-1-fi и с управляющими входами третьего, четвертого и шестого ключей в К-м блоке фиксации очереди, четвертьй выход блока анализа состояния очереди соединен с запускающим входом блока восст.ановления очереди, группа информационных входов которого соединена с соответствующими выходами с первого по К-1-й из первой группы выходов блока управления, группа выходов блока восстановления очереди соединена с вторыми входами элементов ИЛИ группы, вьгходы регистров кода сообщения блоков фиксации очереди с третьего по К-й соединены с управляющими, входами девятых ключей блоков фиксации сообщения с второго по К-1-й соответственно, выход регистра кода сообщения второго блока ф)И ксации очереди соединен с управляющим входом шестого ключа первого блока фиксации очереди, выходы регистров кода сообщения блоков фиксации очереди с первого по К-2-й соединены с информационными входами восьмых ключей блоков фиксации очереди с второго по К-1-й соответственно, выход регистра кода сообщения К-1-го блока фиксации очереди соединен с информационным входом шестого ключа К-го блока фиксации очереди, при этом во всех блоках фиксации очереди выход третьего элемента ИЛИ соединен с входами регистра кода сообщения, в блоках фиксации очереди с второго по К-1-й информационный вход девятого ключа соединен с информационным входом третьего ключа, управляющий вход седьмого ключа соединен с управлякщим входом первого ключа, выходы седьмого, восьмого ..и девятого ключей соединены с первым, вторым и третьим входами Tpetbero элемента ИЛИ соответственно, в первом иК-м блоках фиксации очереди управляющий вход пятого ключа соединен с управляю1цим входом первого ключа, выходы пятого и шестого клю- .

чей соединены с первым и вторым входами третьего элемента ИЛИ соответственно, в первом блоке фиксации очереди информационньй вход шестого ключа соединен с информационным вхог дом третьего ключа, при это.м блок управления .содержит генератор тактовых импульсовj узел сравнения, дешифратор, два элемента И, два эле мента ИЛИ, два триггера, два узла распределения тактовых импульсов, группу элементов И и группу элементов ЗАПРЕТ, причем единичньш вход первого триггера является первым входом блока управления и соединен с его выходом, первый информационньй вход узла сравнения является вторым входом блока управления, второй информационньй вход узла сравнения является третьим входом блока управления, выходы элементов И группы соединены с группой входов первого элемента ИЛИ и образуют первую группу выходов блока управления, выходы элементов ЗАПРЕТ группы образуют вторую группу выходов блока управления, группа выходов первого узла распределения тактовых импульсов образует третью группу выходов блока управления, при этом в блоке управления выход первого элемента ИЛИ соединен с нулевым входом второго триггера, входом сброса второго узла распределения тактовых импульсов и управляющим входом узла сравнения, выход которого соединен с входом дешифратора, группа,выходов которого соединена с первыми входами элементов И группы и элементов ЗАПРЕТ группы и группой входов второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и первым входом второго элемента И; выход которого соединен с входом . запуска первого узла распределения тактовых импульсов, последний выход которого соединен с нулевым входом первого триггера, выход которого соединен с вторым входом второго элемента И, выход первого элемента И соединен с входом запуска второго узла распределения тактовых импульсов, группа выходов которого соединена с вторь1ми входами элементов И группы и элементов ЗАПРЕТ группы.

2.Устройство по п. 1, отличающееся тем, что блок анализа состояния очереди содержит буферный регистр, сумматор, память изменений приоритета, узел сравнения, память критических ситуаций, причем информационный вход буферного регистра является первым входом блока, группа информационных входов узла сравнения образует группу входов блока, информационный выход буферного регистра соединен с информационным входом памяти изменений приоритета и является первым и вторым выходами блока, первьй вход сумматора является вторым входом блока, а выход - третьим вь:ходом блока, первый выход узла сравнения является четвертым выходом блока, при этом в блоке анализа состояния очереди выход памяти критических ситуаций соединен с информационным входом узла -сравнения, второй выход которого соединен с адресным входом памяти изменений приоритета,выход которой соединен с вторым входомсумматора,

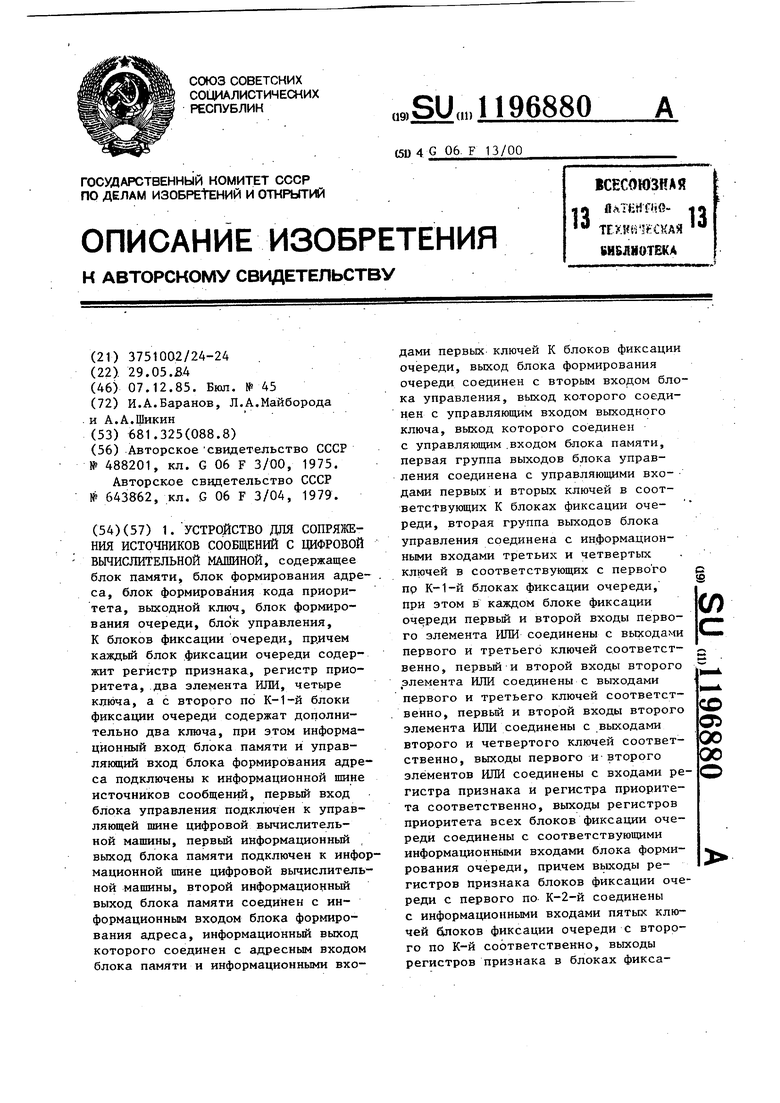

3.Устройство по п. 1, отличающееся тем, что блок восстановления очереди содержит триггер, буферный регистр, генератор

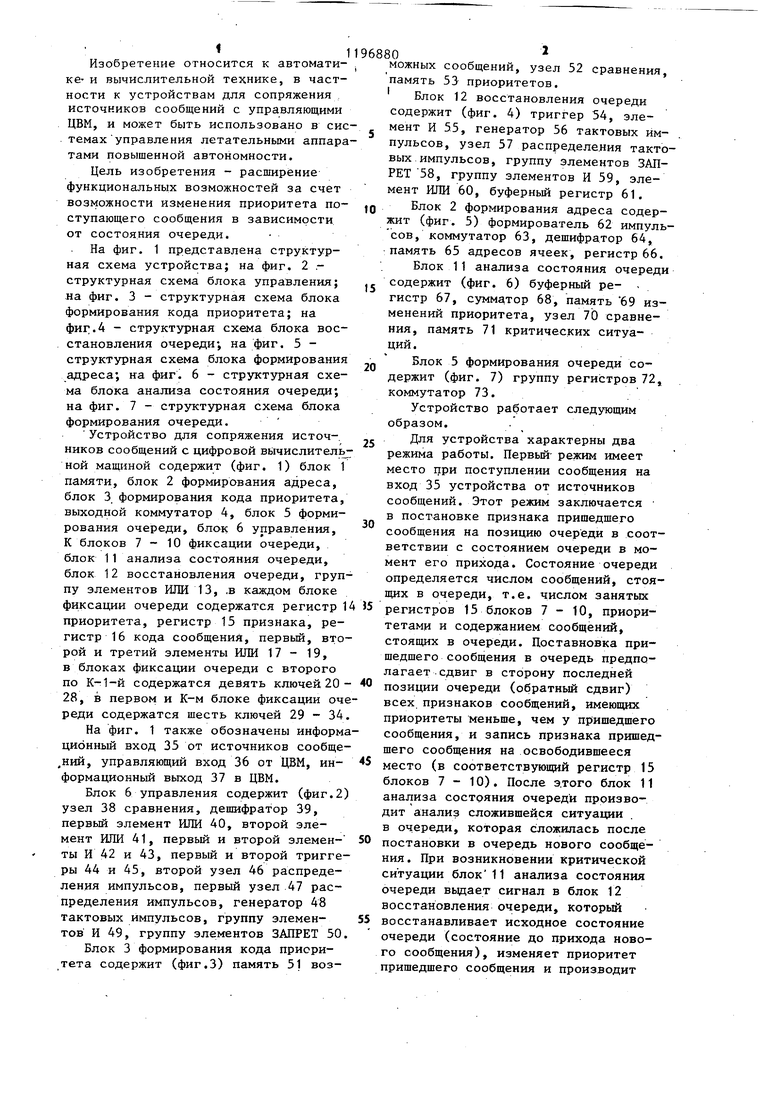

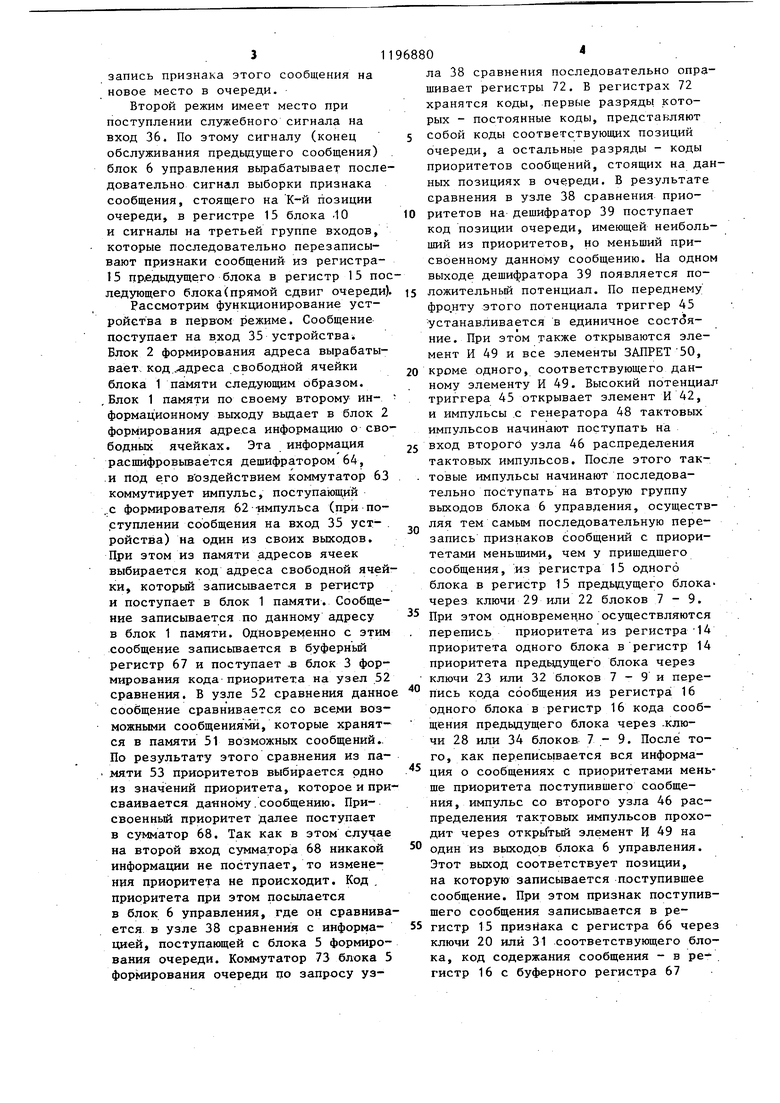

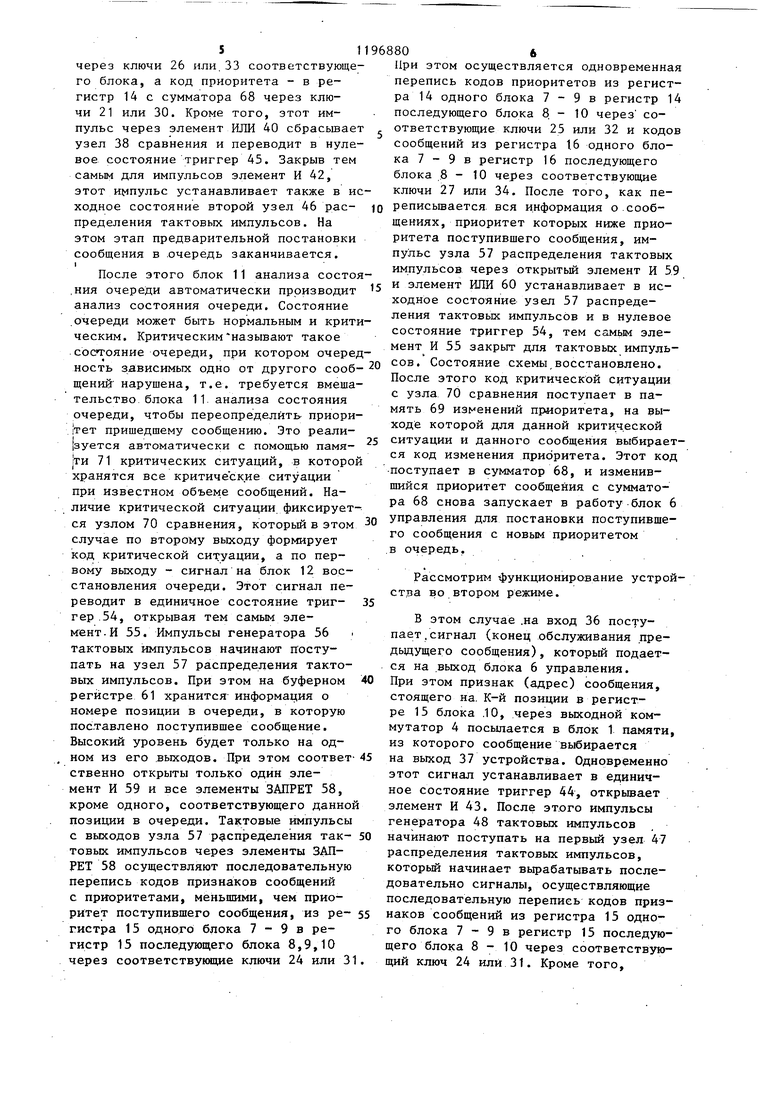

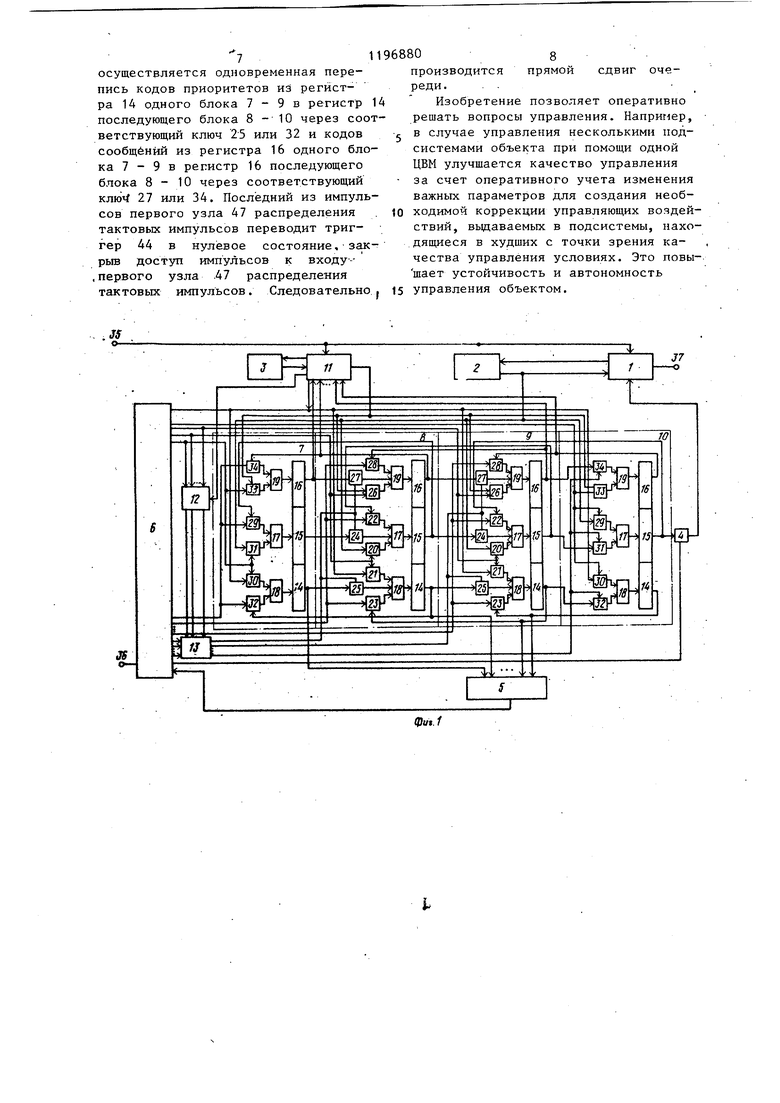

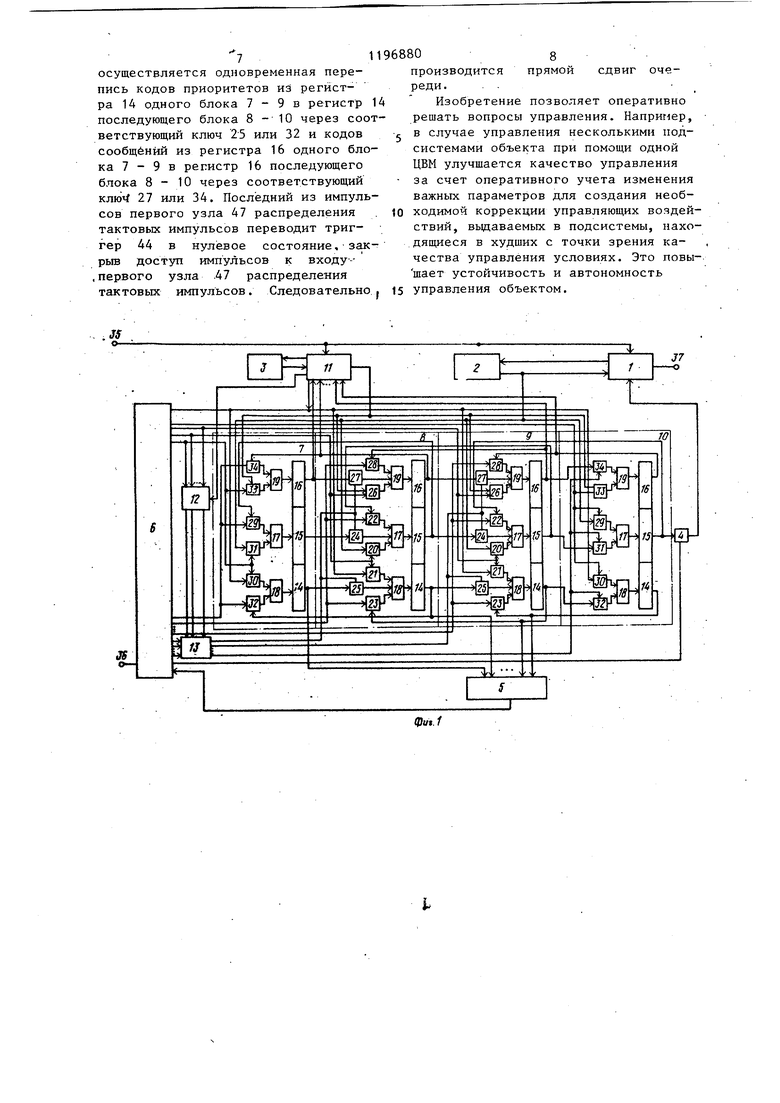

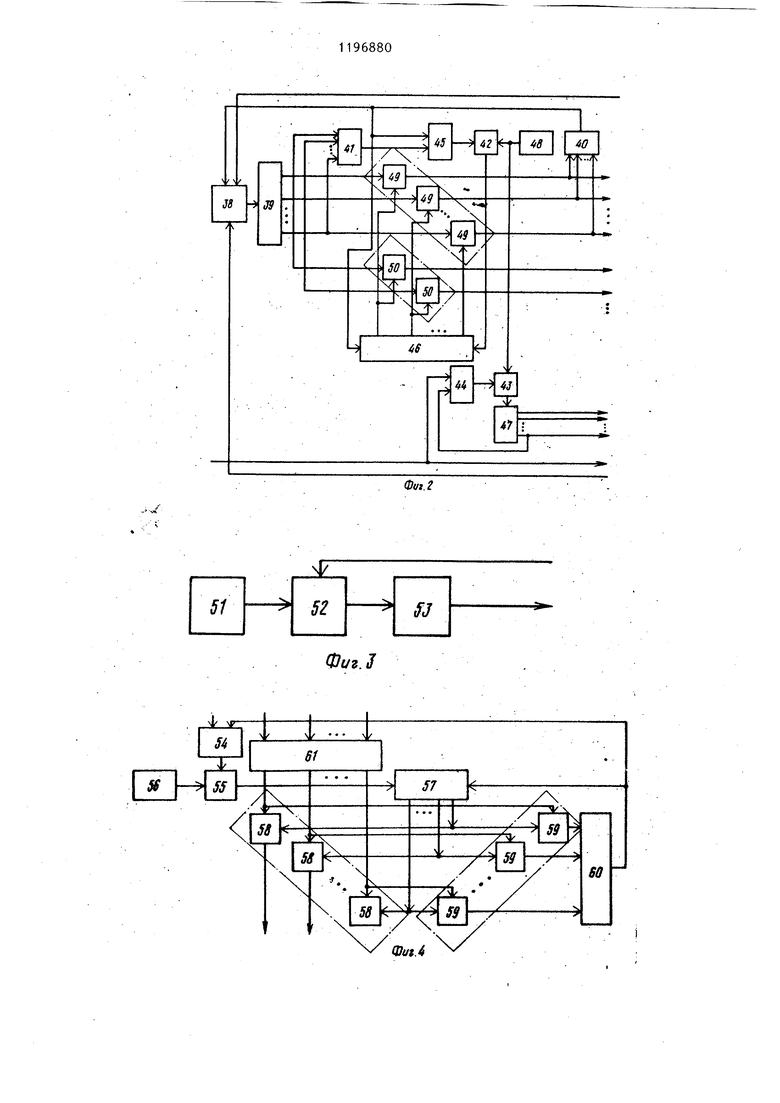

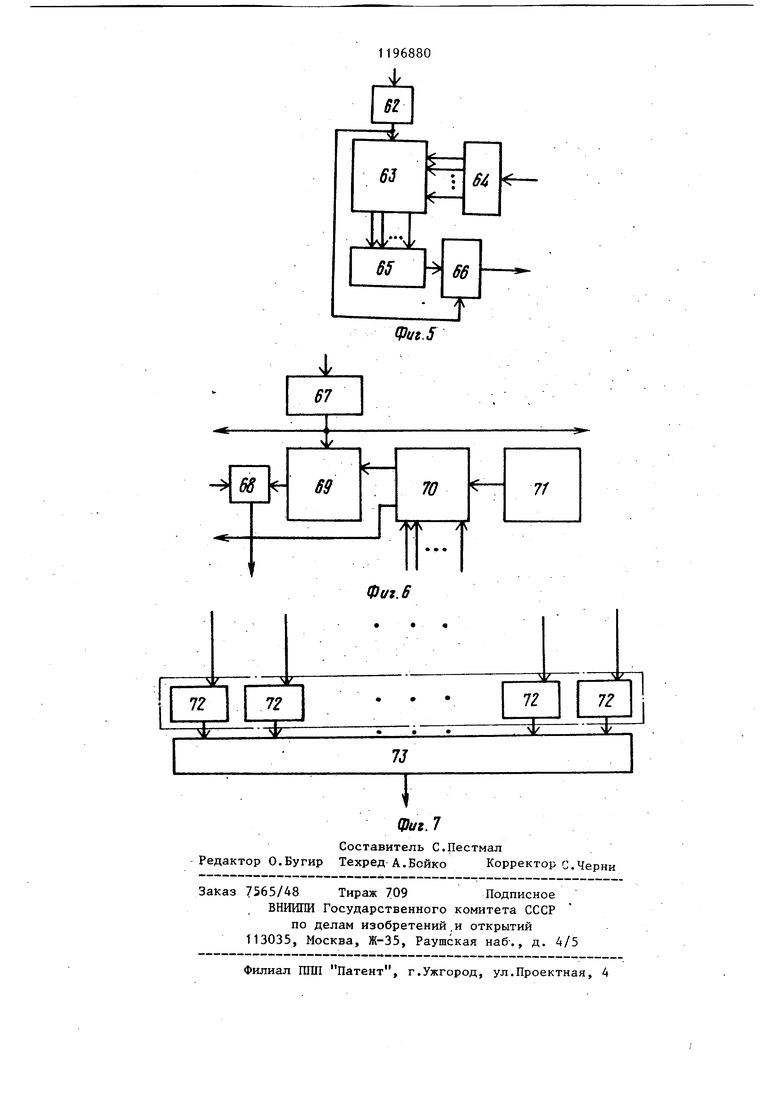

тактовых импульсов, узел распреде-ления тактовых импульсов, элемент И, элемент ИЛИ, группу элементов И, группу элементов ЗАПРЕТ, причем единичный вход триггера является запускающим ВХОДОМ блока, группа информационных входов буферного регистра образует группу информационных входов блока, выходы элементов И группы образуют группу выходов блока,при этом в блоке восстановления очереди группа выходов буферного регистра соединена с первыми входами элементов И группы и элементов ЗАПРЕТ группы, выходы которых соединены с группой входов элемента ИЛИ, выход которого соединен с входом сброса узла распределения тактовых импульсов и нулевым входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, а выход - с входом запуска узла распределения тактовых импульсов, группа йыходов которого соединена с вторыми входами элементов И группы и элементов ЗАПРЕТ группы. Изобретение относится к автоматике- и вычислительной технике, в частности к устройствам для сопряжения источников сообщений с управляющими ЦВМ, и может быть использовано в сис темахуправления летательными аппара тами повышенной автономности. Цель изобретения - расширение функциональных возможностей за счет возможности изменения приоритета поступающего сообщения в зависимости от состояния очереди. На фиг. 1 представлена структурная схема устройства; на фиг. 2 .структурная схема блока управления; на фиг. 3 - структурная схема блока формирования кода приоритета; на фиг.А - структурная схема блока восстановления очереди; на фиг. 5 структурная схема блока формирования адреса; на фиг. 6 - структурная схема блока анализа состояния очереди; на фиг. 7 - структурная схема блока формирования очереди. Устройство для сопряжения источников сообщений с цифровой вычислитель ной машиной содержит (фиг. 1) блок 1 памяти, блок 2 формирования адреса, блок 3 формирования кода приоритета, выходной коммутатор 4, блок 5 формирования очереди, блок 6 управления, К блоков 7-10 фиксации очереди, блок 11 анализа состояния очереди, блок 12 восстановления очереди, груп пу элементов ИЛИ 13, .в каждом блоке фиксации очереди содержатся регистр приоритета, регистр 15 признака, регистр 16 кода сообщения, первый, вто рой и третий элементы ИЛИ 17 - 19, в блоках фиксации очереди с второго по К-1-Й содержатся девять ключей, 20 28, в первом и К-м блоке фиксации оч реди содержатся шесть ключей 29 - 34 На фиг. 1 также обозначены информ ционный вход 35 от источников сообще ,ний, управляющий вход 36 от ЦВМ, информационный выход 37 в ЦВМ. Блок 6 управления содержит (фиг.2 узел 38 сравнения, дешифратор 39, первый элемент ИЛИ 40, второй элемент ИЛИ 41, первый и второй элементы И 42 и 43, первый и второй тригге ры 44 и 45, второй узел 46 распределения импульсов, первый узел 47 распределения импульсов, генератор 48 тактовых импульсов, группу элементов И 49, группу элементов ЗАПРЕТ 50 Блок 3 формирования кода приоритета содержит (фиг.З) память 51 воз0можных сообщений, узел 52 сравнения, память 53 приоритетов. Блок 12 восстановления очереди содержит (фиг. 4) триггер 54, элемент И 55, генератор 56 тактовых импульсов, узел 57 распределения тактовых импульсов, группу элементов ЗАПРЕТ 58, группу элементов И 59, элемент ШШ 60, буферньй регистр 61. Блок 2 формирования адреса содержит (фиг. 5) формирователь 62 импульсов, коммутатор 63, дешифратор 64, память 65 адресов ячеек, регистр 66. Блок 11 анализа состояния очереди содержит (фиг. 6) буферный ре- гистр 67, сумматор 68, память 69 изменений приоритета, узел 70 сравнения, память 71 критических ситуаций. Блок 5 формирования очереди содержит (фиг. 7) группу регистров 72, коммутатор 73. Устройство работает следующим образом. Для устройства характерны два режима работы. Первьй- режим имеет место при поступлении сообщения на вход 35 устройства от источников сообщений. Этот режим заключается в постановке признака прищедшего сообщения на позицию очереди в соответствии с состоянием очереди в момент его прихода. Состояние очереди определяется числом сообщений, стоящих в очереди, т.е. числом занятых регистров 15 блоков 7 - 10, приоритетами и содержанием сообщений, стоящих в очереди. Цоставновка пришедшего сообщения в очередь предполагает, сдвиг в сторону последней позиции очереди (обратный сдвиг) всех признаков сообщений, имеющих приоритеты меньше, чем у пришедшего сообщения, и запись признака пришедщего сообщения на освободившееся место (в соответствующий регистр 13 блоков 7 - 10). После э.того блок 11 анализа состояния очереди производит анализ сложившейся ситуации в очереди, которая сложилась после постановки в очередь нового сообщения . При возникновении критической ситуации блок11 анализа состояния очереди вьщает сигнал в блок 12 восстановления очереди, который восстанавливает исходное состояние очереди (состояние до прихода нового сообщения), изменяет приоритет пришедшего сообщения и производит

3 1

запись признака этого сообщения на новое место в очереди.

Второй режим имеет место при поступлении служебного сигнала на вход 36. По этому сигналу (конец обслуживания предыдущего сообщения) блок 6 управления вьфабатывает последовательно сигнал выборки признака сообщения, стоящего на К-й позиции очереди, в регистре 15 блока .10 и сигналы на третьей группе входов, которые последовательно перезаписывают признаки сообщений из регистра15 пр.едьщущего блока в регистр 15 последующего блока (прямой сдвиг очереди).

Рассмотрим функционирование устройства в первом режиме. Сообщение поступает на вход 35 устройства. Блок 2 формирования адреса вырабатывает. код.,адреса свободной ячейки блока 1 памяти следующим образом.

,Блок 1 памяти по своему второму информационному выходу выдает в блок 2 формирования адреса информацию о свободных ячейках. Эта информация расшифровьгоается дешифратором 64,

.и под его воздействием коммутатор 63 коммутирует импульс, поступающий

..с формирователя 62 -импульса (при поступлении сообщения на вход 35 уст- . ройства) на один из своих выходов. При этом из памяти адресов ячеек выбирается код адреса свободной ячейки, которьй записывается в регистр и поступает в блок 1 памяти. Сообщение записывается по данному адресу в блок 1 памяти. Одновременно с этим сообщение записьшается в буферньй регистр 67 и поступает JB блок 3 формирования кода-приоритета на узел 52 сравнения. В узле 52 сравнения данное сообщение сравнивается со всеми возможными сообщениями, которые хранятся в памяти 51 возможньк сообщений.. По результату этого сравнения из памятн 53 приоритетов выбирается одно из значений приоритета, которое и присваивается данному.сообщению. Присвоенный приоритет далее поступает в сумматор 68, Так как в этом случае на второй вход сумматора 68 никакой информации не поступает, то изменения приоритета не происходит. Код . приоритета при этом посылается в блок 6 управления, где он сравнивается в узле 38 сравнения с информацией, поступающей с блока 5 формирования очереди. Коммутатор 73 блока 5 формирования очереди по запросу уз6880

ла 38 сравнения последовательно опращивает регистры 72. В регистрах 72 хранятся коды, первые разряды которых - постоянные коды, представляют

5 собой коды соответствующих позиций очереди, а остальные разряды - коды приоритетов сообщений, стоящих на данных позициях в очереди. В результате сравнения в узле 38 сравнения приоритетов на дешифратор 39 поступает код позиции очереди, имеющей неибольший из приоритетов, но меньший присвоенному данному сообщению. На одном выходе дешифратора 39 появляется положительный потенциал. По переднему фро.нту этого потенциала триггер 45 устанавливается в единичное состояние. При этом также открываются элемент И 49 и все элементы ЗАПРЕТ50,

20 кроме одного, соответствующего данному элементу И 49. Высокий потенциал триггера 45 открывает элемент И 42, и импульсы .с генератора 48 тактовых импульсов начинают поступать на

25 вход второго узла 46 распредел-ения

тактовых импульсов. После этого так. товые импульсы начинают последовательно поступать на вторую группу выходов блока 6 управления, осуществ, ляя тем самым последовательную перезапись признаков сообщений с приоритетами меньшими, чем у пришедшего сообщения, из регистра 15 одного блока в регистр 15 предьщущего блокачерез ключи 29 или 22 блоков 7 - 9.

5 При этом одновременно осуществляются перепись приоритета из регистра14 приоритета одного блока врегистр 14 приоритета предыдущего блока через ключи 23 или 32 блоков 7 - 9 и перепись кода сообщения из регистра1 1 б одного блока в регистр 16 кода сообщения предыдущего блока через .ключи 28 или 34 блоков 7 - 9. После того, как переписывается вся информа45ция о сообщениях с приоритетами меньше приоритета поступившего сообщения, импульс со второго узла 46 распределения тактовых импульсов проходит через открьГтый элемент И 49 на

50 один из выходов блока 6 управления. Этот выход соответствует позиции, на которую записывается поступившее сообщение. При этом признак поступившего сообщения записьгоается в регистр 15 признака с регистра 66 через ключи 20 или 31 соответствующего блока, код содержания сообщения - в регистр 16 с буферного регистра 67

через ключи 26 или.33 соответствующего блока, а код приоритета - в регистр 14 с сумматора 68 через ключи 21 или 30. Кроме того, этот импульс через элемент ИЛИ 40 сбрасьтает узел 38 сравнения и переводит в нулевое состояние триггер 45. Закрыв тем самым для импульсов элемент И 42, этот импульс устанавливает также в исходное состояние второй узел 46 распределения тактовых импульсов. На этом этап предварительной постановки

сообщения в .очередь заканчивается. I

После этого блок 11 анализа состоя,ния очереди автоматически производит анализ состояния очереди. Состояние .очереди может быть нормальным и критическим. Критическим называют такое состояние очереди, при котором очередность зависимых одно от другого сообщений нарушена, т.е. требуется вмешательство блока 11 анализа состояния очереди, чтобы переопределить приори|тет пришедшему сообщению. Это реали,|зуется автоматически с помощью памяти 71 критических ситуаций, в которой хранятся все критические ситуации при известном объеме сообщений. Наличие критической ситуации фиксируется узлом 70 сравнения, которьш в этом случае по второму выходу формирует код критической ситуации, а по первому выходу - сигнал на блок 12 восстановления очереди. Этот сигнал переводит в единичное состояние триггер.54, открывая тем самым элемент. И 55. Импульсы генератора 56 тактовых импульсов начинают п оступать на узел 57 распределения тактовых импульсов. При этом на буферном регистре 61 хранится информация о номере позиции в очереди, в которую поставлено поступившее сообщение. Высокий уровень будет только на одном из его .выходов. При этом соответственно открыты только один элемент И 59 и все элементы ЗАПРЕТ 58, кроме одного, соответствующего данной позиции в очереди. Тактовые импульсы с выходов узла 57 распределения тактовых импульсов через элементы З.АПРЕТ 58 осуществляют последовательную перепись кодов признаков сообщений с приоритетами, меньшими, чем приоритет поступившего сообщения, из регистра 15 одного блока 7 - 9 в регистр 15 последующего блока 8,9,10 через соответствующие ключи 24 или 31

При этом осуществляется одновременная перепись кодов приоритетов из регистра 14 одного блока 7 - 9 в регистр 14 последующего блока 8. - 10 через соответствующие ключи 25 или 32 и кодов сообщений из регистра 1.6 одного блока 7 - 9 в регистр 16 последующего блока 8 - 10 через соответствующие ключи 27 или 34. После того, как переписьшается вся информация о сообщениях, приоритет которых ниже приоритета поступившего сообщения, импульс узла 57 распределения тактовых импульсов через открытый элемент И 59 и элемент ШТИ 60 устанавливает в исходное состояние узел 57 распределения тактовых импульсов и в нулевое состояние триггер 54, тем самьм элемент И 55 закрыт для тактовых импульсов. Состояние схемы,восстановлено. После этого код критической ситуации с узла 70 сравнения поступает в память 69 изменений приоритета, на выходе которой для данной критической ситуации и данного сообщения выбирается код изменения приоритета. Этот код поступает в сумматор 68, и изменившийся приоритет сообщения с сумматора 68 снова запускает в работу блок 6 управления для постановки поступившего сообщения с новым приоритетом .в очередь.

Рассмотрим -функционирование устройст.ва во втором режиме.

В этом случае .на вход 36 поступает, сигнал (конец обслуживания .предьщущего сообщения), который подается на .выход блока 6 управления. При этом признак (адрес) сообщения, стоящего на. К-й позиции в регистре 15 блока .10, через выходной коммутатор 4 посылается в блок 1 памяти, из которого сообщение выбирается на выход 37 устройства. Одновременно этот сигнал устанавливает в единичное состояние триггер 44, открывает элемент И 43. После этого импульсы генератора 48 тактовых импульсов начинают поступать на первый узел 47 распределения тактовых импульсов, которьй начинает вырабатывать последовательно сигналы, осуществляющие последовательную перепись кодов признаков сообщений из регистра 15 одного блока 7 - 9 в регистр 15 последующего блока 8-10 через соответствующий ключ 24 или 31. Кроме того. осуществляется одновременная перепись кодов приоритетов из регистра 14 одного блока 7 - 9 в регистр последующего блока 8 - 10 через соо ветствующий ключ 25 или 32 и кодов сообщений из регистра 16 одного бло ка 7 - 9 в регистр 16 последующего блока 8-10 через соответствующий клю 27 или 34. Последний из импуль сов первого узла 47 распределения тактовых импульсов переводит триггер 44 в нулевое состояние,зак рыв достзш импульсов к входу-.первого узла .47 распределения тактовых импульсов. Следовательно 08 производится прямой сдвиг очереди. . . Изобретение позволяет оперативно решать вопросы управления. Наприг1ер, в случае управления несколькими подсистемами объекта при помощи одной ЦВМ улучщается качество управления за счет оперативного учета изменения важных параметров для создания необходимой коррекции управляющих воздействий, выдаваемых в подсистемы, находящиеся в худщих с точки зрения качества управления условиях. Это повышает устойчивость и автономность управления объектом.

л

/

50

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

| Устройство маршрутизации | 1988 |

|

SU1695329A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКОВ СООБЩЕНИЙ С ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ, содержащее блок памяти, блок формирования адреса, блок формирования кода приоритета, выходной ключ, блок формирования очереди, блок управления, К блоков фиксации очереди, причем каждьш блок фиксации очереди содержит регистр признака, регистр прио ритета,.два элемента ИЛИ, четыре ключа, а с второго по К-1-й блоки фиксации очереди содержат дополнительно два ключа, при этом информационный вход блока памяти и управляющий вход блока формирования адреса подключены к информационной шине источников сообщений, первый вход блока управления подключен к управ ляющей шине цифровой вычислительной машины, первьш информационный выход блока памяти подключен к информационной шине цифровой вычислительной машины, второй информационный выход блока памяти соединен с информационным входом блока формирования адреса, информационный выход которого соединен с адресным входом блока памяти и информационными входами первых ключей К блоков фиксации очереди, выход блока формирования очереди соединен с вторым входом блока управления, выход которого соединен с управляющим входом выходного ключа, выход которого соединен с управляющим .входом блока памяти, первая группа выходов блока управления соединена с управляющими входами первых и вторых ключей в соответствующих К блоках фиксации очереди, вторая группа выходов блока управления соединена с информационными входами третьих и четвертых ключей в соответствующих с первого i пр К-1-й блоках фиксации очереди, (Л при этом в каждом блоке фиксации очереди первьш и второй входы первого элемента ИЛИ соединены с выходами первого и третьего ключей соответственно, первьй и второй входы второго элемента ИЛИ соединены с выходами первого и третьего ключей соответст х венно, первьй и второй входы второго оь элемента ИЛИ соединены с выходами 00 второго и четвертого ключей соответ00 ственно, выходы первого и-второго элементов ИЛИ соединены с входами регистра признака и регистра приоритета соответственно, выходы регистров приоритета всех блоков фиксации очереди соединены с соответствующими информационными входа т блока формирования очереди, причем вькоды регистров признака блоков фиксации очереди с первого по К-2-Й соединены с информационными входами пятых ключей б локов фиксации очереди с второго по К-й соответственно, выходы регистров признака в блоках фикса

Фиг.З

-

44

43

1196880 Ф

Г;

6

S

66

Фиг.5

Фиг. 6

| Устройство для сопряжения источников случайных потоков сообщений с цифровой вычислительной машиной | 1972 |

|

SU488201A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU643862A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-05-29—Подача