Изобретение относится к промыш-: ленности средств связи и может быть использовано при построении устройс сопряжения скорости развертки малокадровых телевизионных систем с тел визионными системами, скорость развертки которых близка или равна вещательному стандарту, а также при построении устройств вывода информации из ЭВМ для получения на экране вещательного видеоконтрольного устройства изображения объекта, исследу емого при помощи радиолокатора или , гидроакустических устройств. Известен преобразователь телевизи онного стандарта, содержащий первый счетчик, синхровход которого соедине с синхровходом второго счетчика, к «ыходу которого подключен первый гру повой вход коммутатора, третий счетчик, первый групповой выход которого соединен с вторым групповым входом коммутатора, групповой выход которого через блок памяти подключен к групповому входу цифро-аналогового преобразователя, аналого-цифровой преобразователь, а также блок управления, групповой выход которого соединен с вторым групповым входом блока памяти, третий групповой вход .которого подключен к второму групповому выходу третьего счетчика и к групповому входу блока управления fl Недостатком известного преобразователя телевизионного стандарта является низкая точность преобразования видеосигнала при произвольно меняющихся частотах разложения входной и выходной развертки. Этот недостаток обусловлен тем, что непосредственное соединение выхода умно- жителя частоты с счетным входом первого счетчика не может обеспечить переключение первого и второго счетчика, осуществляющих адресацию запо.минающего устройства, при записи син сронно с периодом фо;рмирования им- пульсов управления блока памяти, так как импульсы управления блока памяти формируются по кодовым комбинациям сигнала третьего счетчика, моменты переключения которого определяются частотой задающего генератора. В результате этого нарушаются требуемые временные соотношения сигналов на входах запоминающего блока памяти, что приводит к записи в блок памяти ложной информации, в результате чего появляются ошибки в процессе преобра зования. Цель изобретения - повышение точ ности преобразования при произвольно меняющихся частотах входной и выход ной разверток. Указанная цель достигается тем, что в известный преобразов&тель телевизионного стандарта, содержащий первый счетчик, синхровход которого соединен с синхровходом второго сче чика, к выходу которого подключен первый групповой вход коммутатора,, третий счетчик, первый групповой выход которого соединен с вторым групповым входом коммутатора, групповой выход которого через блок памяти подключен к групповому входу цифроаналогового преобразователя, аналого-цифровой преобразователь, а также блок управления, групповой выход которого соединен с вторым групповым входом блока памяти, третий групповой вход которого подключен к второму групповому выходу третьего счетчика и к групповому входу блока управления, введены два триггера, регистр сдвига, элемент И и регистр, при этом группочой выход аналого-цифровйго преобразователя через последовательно соединенные регистр сдвига и регистр подключен к четвертому групповому входу блока памяти, выход первого счетчика соединен с первым входом первого триггера и с соответствующим входом регистра, выход первого триггера через элемент И соединен с пепвым входом второго триггера, выход которого подключен к управляющему входу блока управления, к управляющему входу коммутатора и к управляющему входу второго счетчика, причем первый выход блока управления соединен с вторым входом второго триггера, второй выход блока управления соединен с вторым- входом элемента И и с соответствующим входом блока памяти, третий выход бло- , ка управления соединен с вторым входом первого триггера, а тактовый вход первого счетчика соединен с тактовым входом регистра сдвига. Блок управления содержит два блока совпадения, три ждущих мультивибратора, элемент ИЛИ и -триггер, причем выход первого бло:са совпадения соединен с первым входом элемента ИЛИ, выход которого через последо вательно соединенные первый и второй, Лйущие мультивибраторы подключен к первому входу Д-триггера, второй вход которого соединен с входом третьего ждущего мультивибратора, выход которого подключен к второму входу элемента ИЛИ, а выход первого ждущего мультивибратора соединён с третьим входом } триггера, ири этрМ групповые входы первого и второго блоков совпадения являются групповым входом блока управления, вход третьего ждущего мультивибратора является управляющим входом блока управления, .выход первого блока совпадения является первым выходом блока управления, выход второго блока совпадения является вторим выходом блока управления, выход третьего ждущего мультивибратора и триггера явля ются групповым выходом блока управления.

Регистр сдвига предназначен для непрерывной записи входного видеосигнала. Регистр предназначен для хранения значений входного видеосигнала с момента полного заполнения регистра сдвига до ближайшего цикла записи. Выход первого счетчика соединен с тактовым входом регистра и первого триггера, 4fTO обеспечивает одновременно перезапись сигнала с регистра сдвига в регистр и срабатывание первого триггера. Первый триггер предназначен для формирования сигнала заполнения регистра , ;м. сдвига..

Блок управления предназначен для фop 0Ipoвaния сигналов управления, необходимы}; для работы блока; памяти в режш4е записи и в режиме считывания а также для формирования сигналов г определяющих начало циклов считывания и начало возможных циклов записи. Элемент И, включенный между выходом первого триггера и входом установки второго триггерау предназначен для переключения второго триггера в состояние, соответствующее режиму записи, в момент времени , определяемые блоком управления Второй триггер Предназначен для переключения преобразователя телевизионного стандарта режим считывания ив режим записи. Выход второго триггера соединен с вторым входом , устройства управления, с входом управления коммутатор а и с счетным входом и торого счетчика, что обеспечив ет переключение второго счетчика Синхронно с работой коммутатора и синхронно с переходом преобразователя телевизионного, стандарта с режима записи в режим считывания. Таким образем, обеспечивается формирова1Ние сигналов На входг х управ/ления и на адресных входах блока па мятй синхронно с частотой элементов разложения выходной развертки; как в режиме считывания, так ив режиме записи, что с беспечивает четкое р зграничение времени записи н считывания. . . - . - :

. того, при переходе преобразователя телевизионного стандарта с режима считывания в режим записи обеспечивается начало ф ормированиясигналов на входах управления и адресных входах, блокапамяти сразу после установки кода сигнала на информационном входе блока памяти, что исключает возможность изменения сигнала на каком-либо входе блока памяти, в процессе записи. Этим исключа ются ошибки преобразования видеосигнала, а следовательно, повышается точность преобразования видеосигнала при произвольном изменении и соотношении частот входной и выходной разверток. Произвольное изменение частот входной и выходной разверток

означает изменение частот элементов, разложения входной и выходной разверток по любому независимому закону в пределах соответствующих рабочих диапазонов, при этом верхняя и нижняя граница рабочего диапазона частот выходной развертки определяется блочком памяти, а верхняя и нижняя гpaни цы рабочего диапазона частот входной развертки равны соотв.етственно

мгновенной частоте выходной развертки и частоте, близкой Нулю. Произвольное соотношение частот входной и выходной развертки означает возможность выборка любого значения час7ОТ разложения входной и выходной развертки в пределах соответствующих рабочих диапазонов и независимо друг от друга.. . .

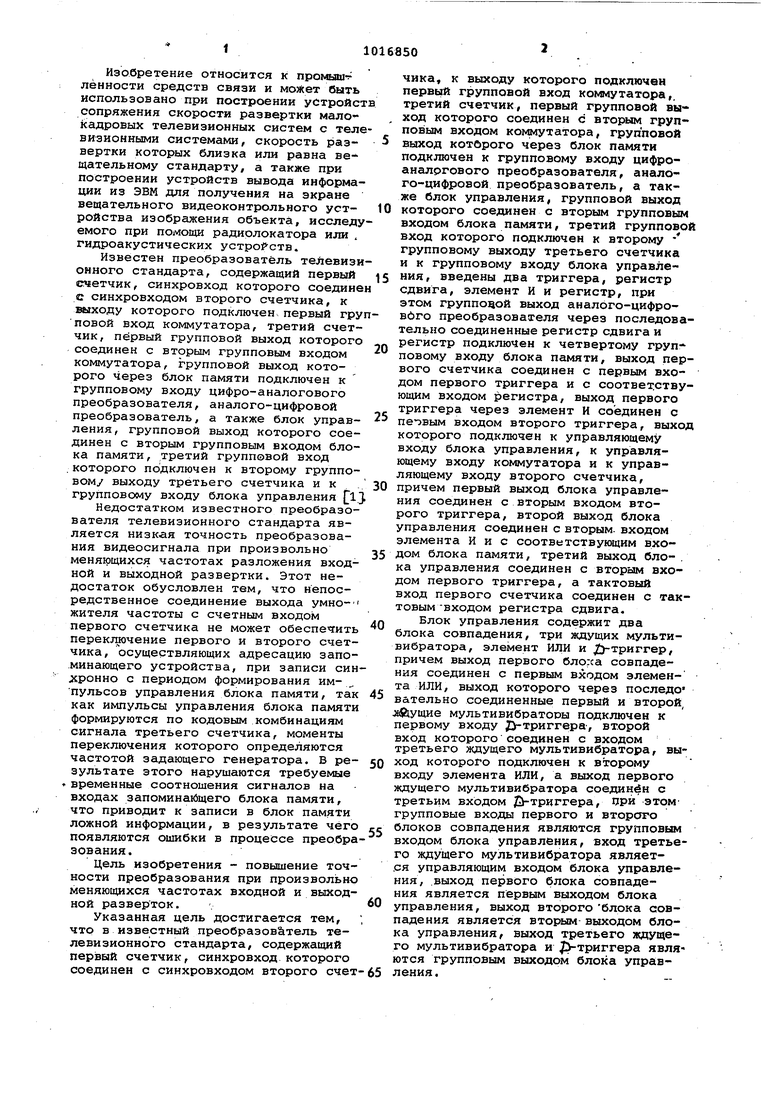

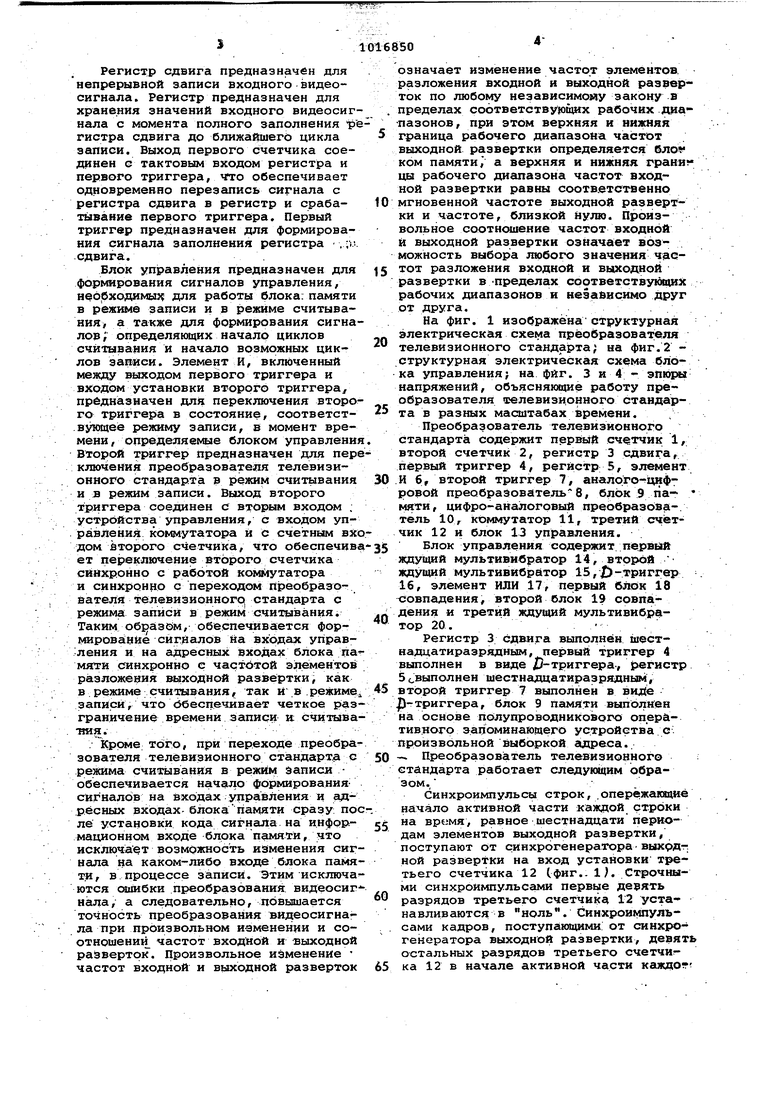

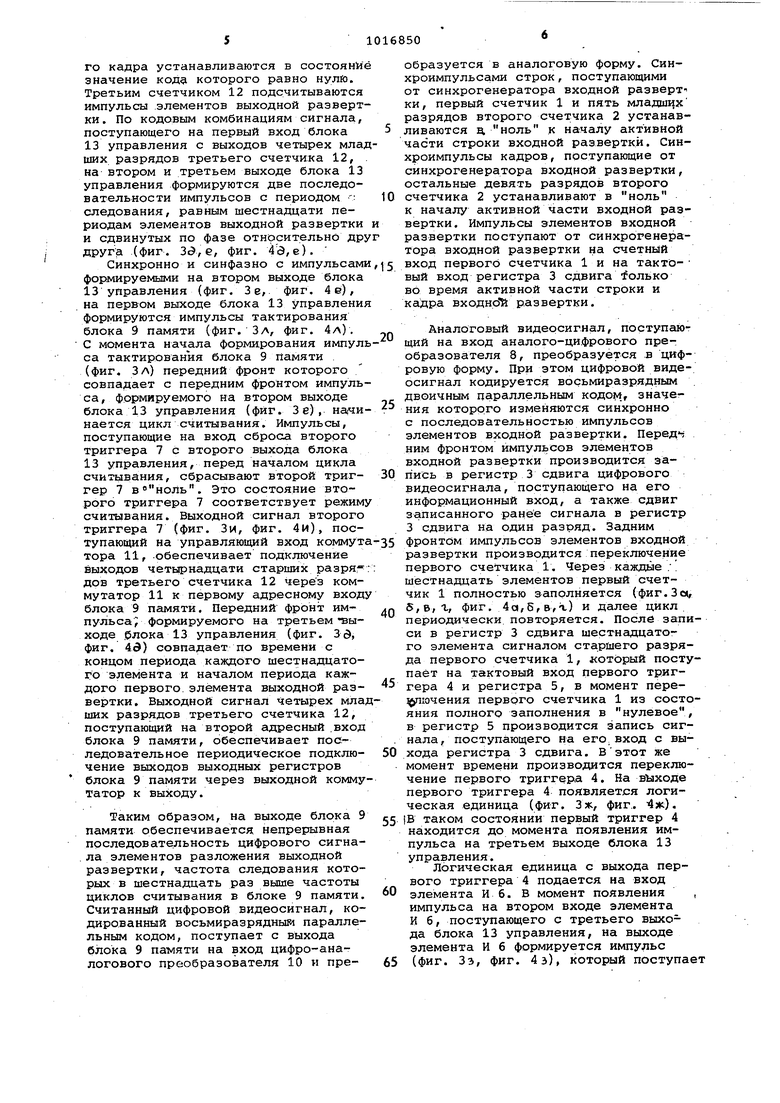

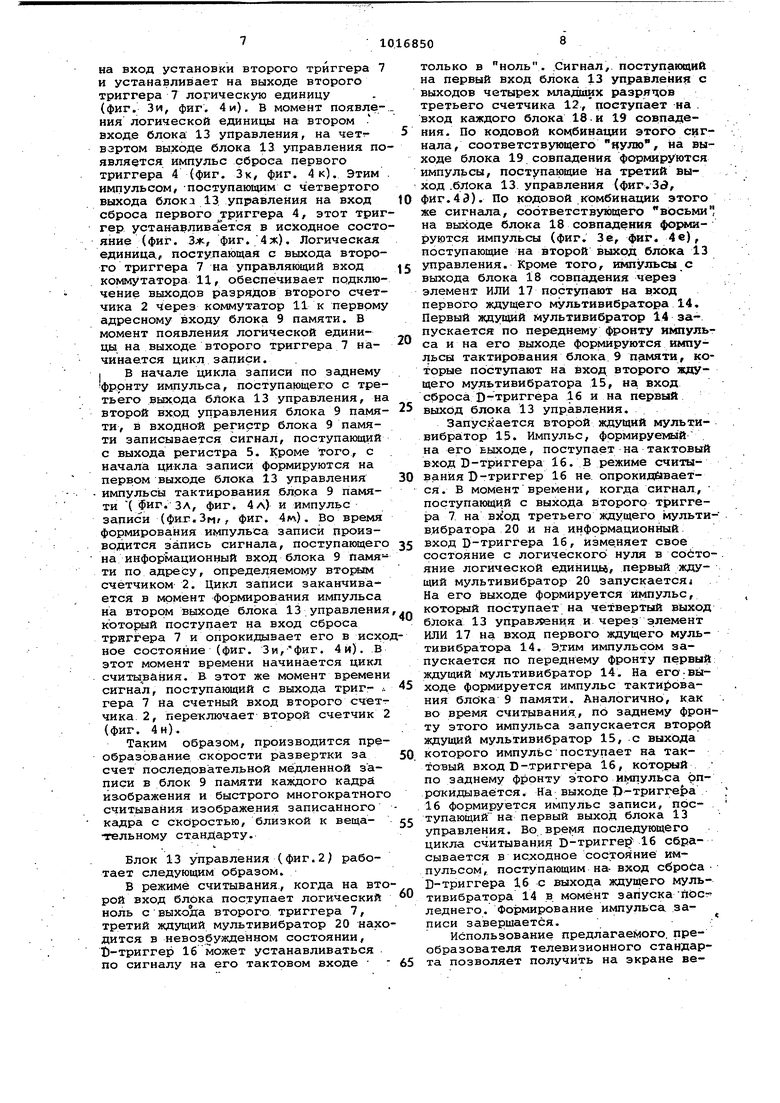

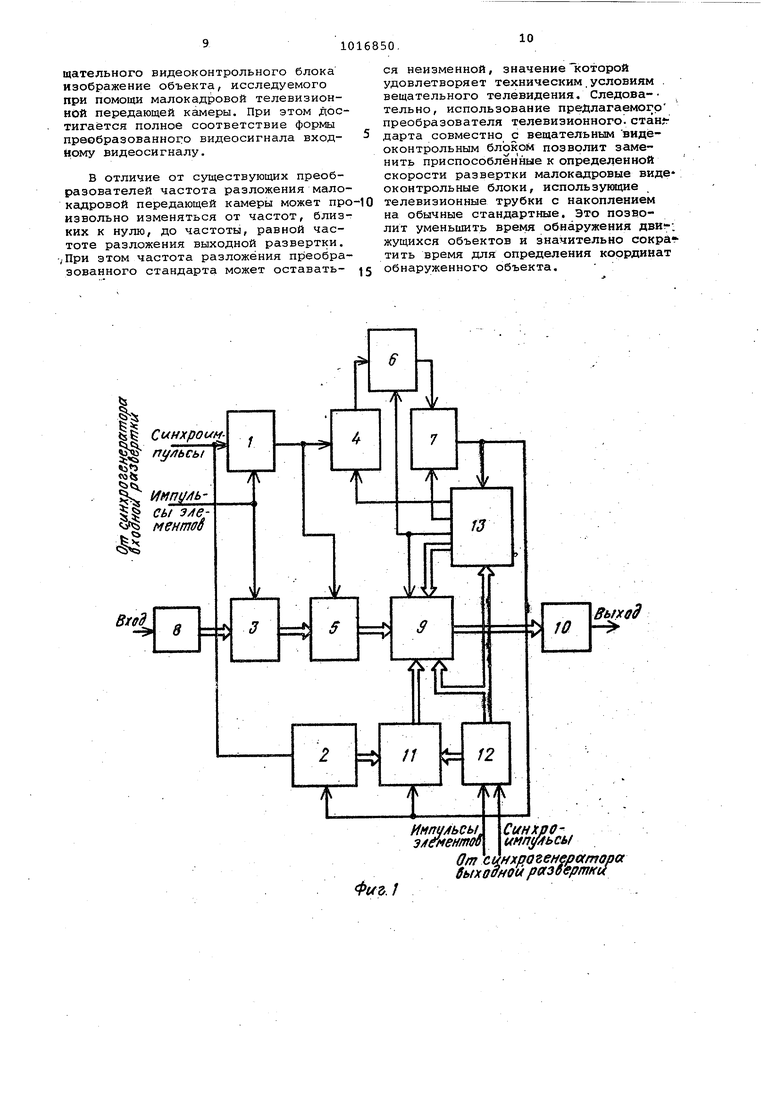

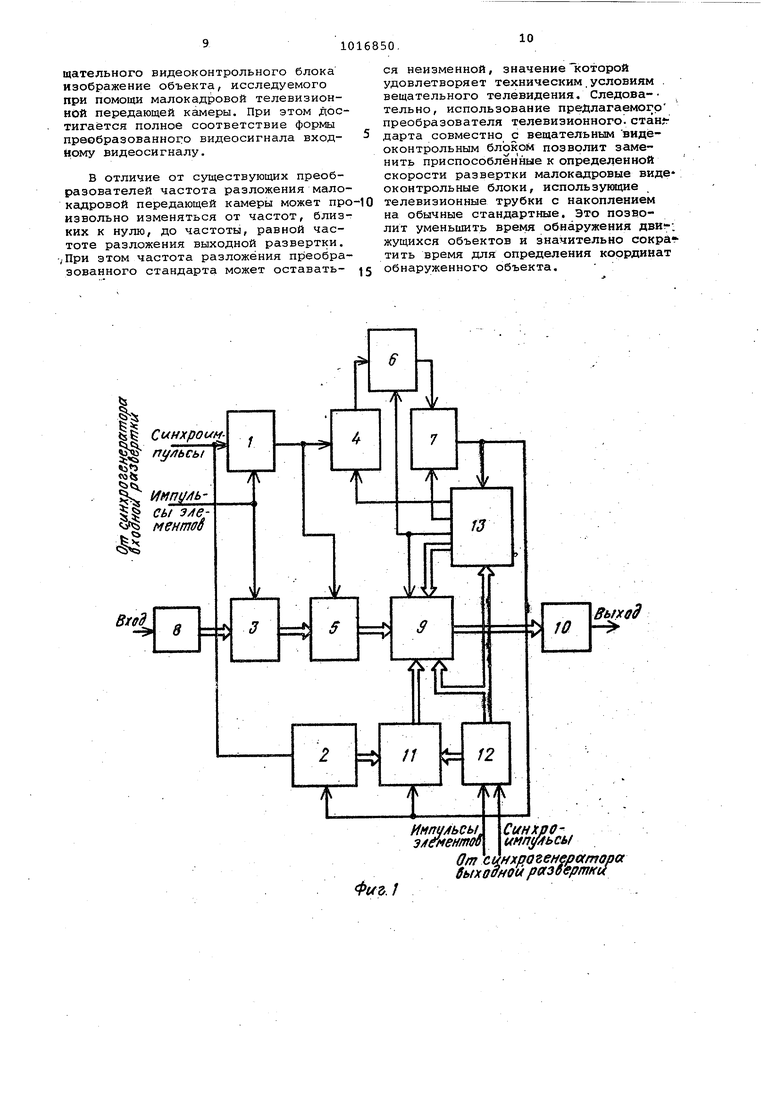

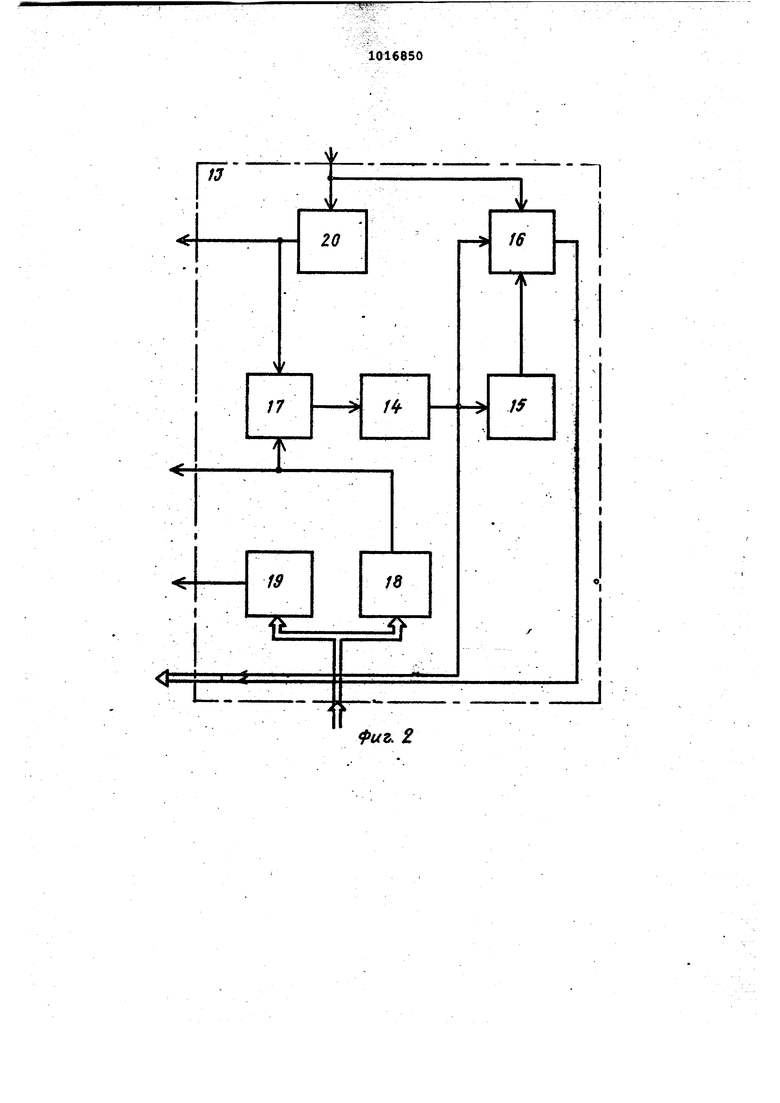

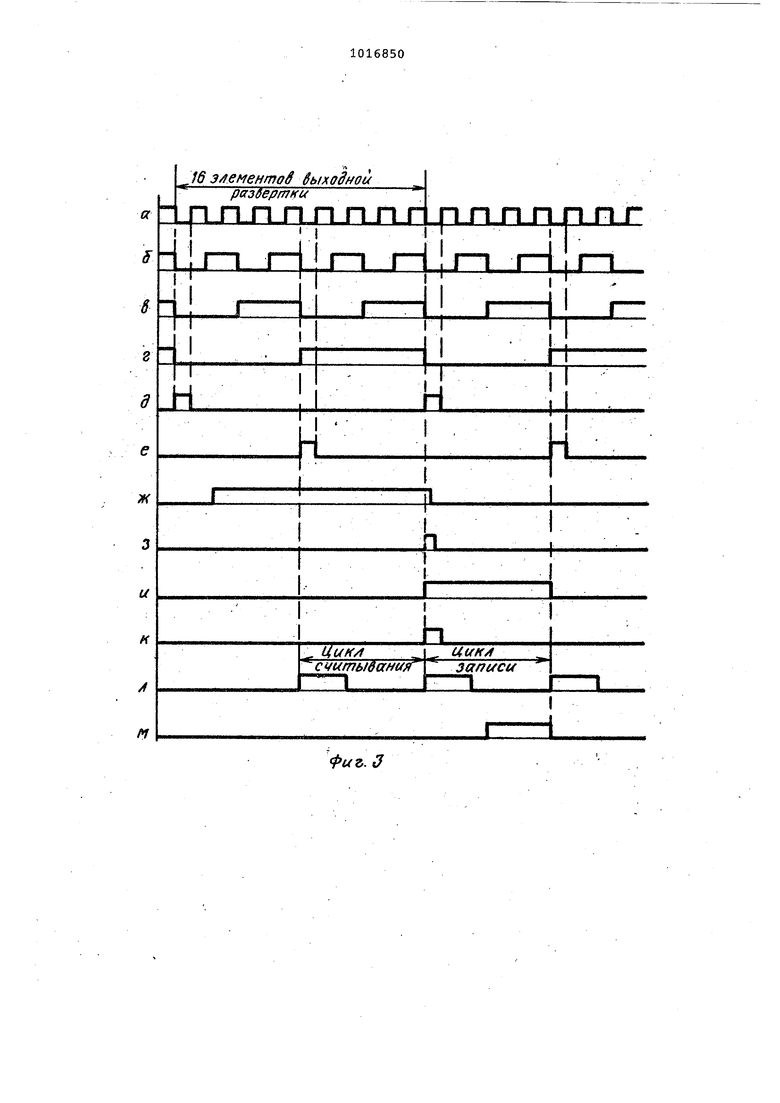

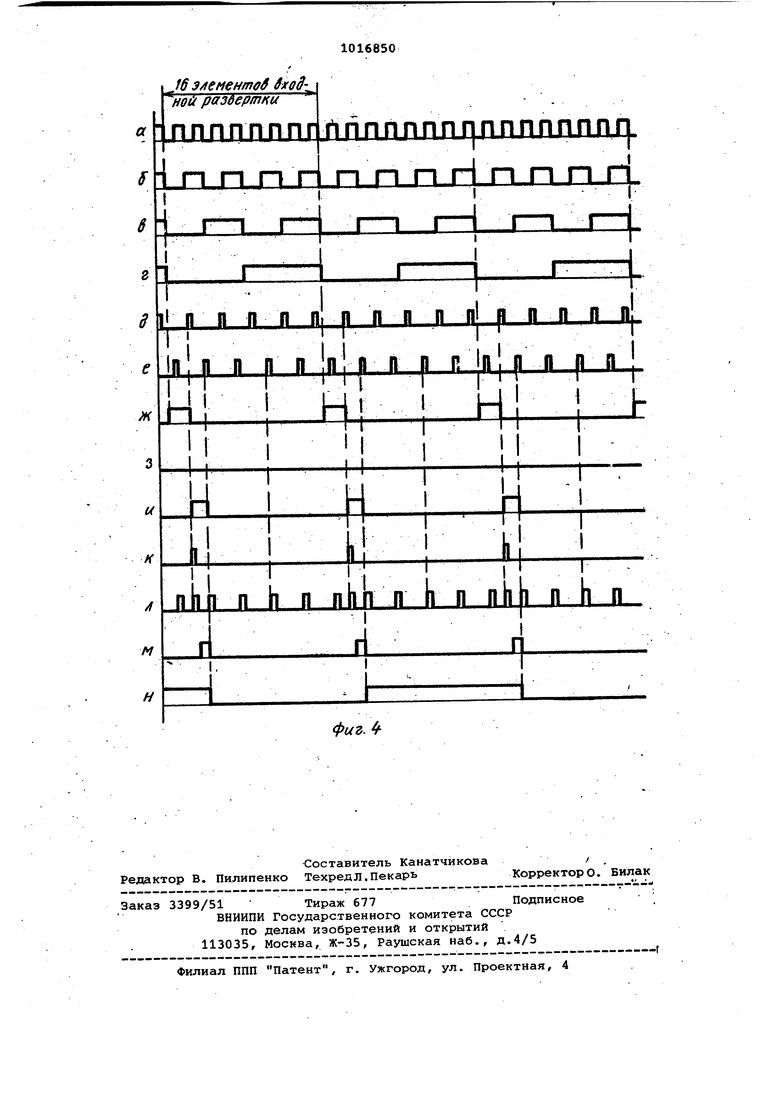

На фиг. 1 изображена структурная электрическая схема преобразователя телевизионного стандарта; на фиг.2 структурная электрическая схема блока управления; на фиг. 3 и 4 - эпюры напряжений, объясняющие работу преобразователя телевизионного стандё рта в разных масштабах Времени.

Преобразователь телевизионного стандарта содержит первый счетчик 1, второй счетчик 2, регистр 3 сдвига, первый триггер 4, регистр 5, элемент

И 6, второй триггер 7, aнaлpгo- цифровой преобразователь 8, блок 9 riа- мяти, цифро-аналоговый преобразЬва-. тель 10, коммутатор 11, третий счетчик 12 и блок 13 управления.

Блок управления содержит первый ждущий мультивибратор 14, второй ждущий мультивибратор 15,X)-триггер 16, элемент ИЛИ 17, первый блок 18 совпадения, второй блок 19 совпадения и третий ждущий мультивибратор 20.

Регистр 3 сдвига выполнен шестнадцатиразрядным, первый триггер 4 выполнен в виде /3-триггера, регистр 5(,выполнен шестнадцатиразрядным,

второй триггер 7 выполнен в виЛе р-триггера, блок 9 Памяти выполнен на основе полупроводникового оп еративного зацоминающего устройства c произвольной Выборкой адреса..

- Преобразователь телевизионного стандарта работает следукщим образом.,

Синхроимпульсы строк,.опережающие начало активной части каждой ртроки

на вр«мя, равное шестнадцати периодам элементов выходной развертки, поступают от сйнхрогенератора выхрдт. ной развертки на вход установки третьего счетчика 12 (фиг.. 1К Строчными синхроимпульсами первые девять

разрядов третьего счетчика 12 устанавливаются в ноль. Синхроимпульсами кадров, поступающими от сйнхрогенератора выходной развертки, девять остальных разрядов третьего счетчи ка 12 в начале активной части каждо г го кадра устанавливаются в состояни значение кода которого равно нули. Третьим счетчиком 12 подсчитываются импульсы элементов выходной разверт ки. По кодовым комбинациям сигнала, поступающего на первый вход блока 13 управления с выходов четырех мла ших разрядов третьего счетчика 12, на втором и третьем выходе блока 13 управления формируются две последовательности импульсов с периодом : следования, равным шестнадцати периодам элементов выходной развертки и сдвинутых по фазе относительно др друга (фиг. ЗЭ,е, фиг. 4Э,е). Синхронно и синфазно с импульсам формируемыми на втором выходе блока 13 управления (фиг. Зе, фиг. 4 е), на первом выходе блока 13 управлени формируются импульсы тактирования блока 9 памяти (фиг. 3л, фиг. 4л). С момента начала формирования импул са тактирования блока 9 памяти (фиг. 3л) передний фронт которого совпадает с передним фронтом импуль са, формируемого на втором выходе блока 13 управления (фиг. 3е), накк наётся цикл считывания. Импульсы, поступающие на вход сброса второго триггера 7 с второго выхода блока 13 управления, перед началом цикла считывания, сбрасывают второй триггер 7 в ноль. Это состояние второго триггера 7 соответствует режим считывания. Выходной сигнал второго триггера 7 (фиг. Зи, фиг. 4и), поступающий на управляющий вход коммут тора 11, .обеспечивает подключение выходов четьфнадцати старших разряд лов третьего счетчика 12 через коммутатор 11 к первому адресному вход блока 9 памяти. Передний фронт импульса; формируемого на третьем выходе .блока 13 управления (фиг. 3d, фиг. 4д) совпадает по времени с концом периода каждого шестнадцатого элемента и началом периода каждого первого, элемента выходной развертки. Выходной сигнал четырех мла ших разрядов третьего счетчика 12, поступающий на второй адресный .вход блока 9 памяти, обеспечивает пос.ледовательное периодическое подключение выходов выходных регистров блока 9 памяти через выходной комму татор к выходу. Таким образом, на выходе блока 9 памяти обеспечивается непрерывная последовате.льность цифрового сигна.ла элементов разложения выходной развертки, частота следования которых в шестнадцать раз выше частоты циклов считывания в блоке 9 памяти. Считанный цифровой видеосигнал, кодированный восьмиразрядный параллельным кодом, поступает с выхода блока 9 памяти на вход ци.фро-аналогового преобразователя 10 и преобразуется в аналоговую форму. Синхроимпульсами строк, поступающими от синхрогенератора входной разверт ки, первый счетчик 1 и пять младших разрядов второго счетчика 2 устанавливаются д ноль к началу активной части строки входной развертки. Синхроимпульсы кадров, поступакзщие от синхрогенератора входной развертки, остальные девять разрядов второго счетчика 2 устанавливают в ноль к началу активной части входной развертки. Импульсы элементов входной развертки поступают от синхрогенератора входной развертки на счетный вход первого счетчика 1 и на такто- вый вход регистра 3 сдвига только во время активной части строки и кадра входнрЙ развертки. Аналоговый видеосигнал, поступающий на вход аналого-ци.фрового преобразователя 8, преобразуется в цифровую форму. При этом цифровой видеосигнал кодируется восьмиразрядным двоичным параллельным кодом, значения которого изменяются синхронно с последовательностью импульсов элементов входной развертки. Передт ним фронтом импульсов элементов входной развертки производится запись в регистр 3 сдвига цифрового видеосигнала, поступающего на его информационный вход, а также сдвиг записанного ранее сигнала в регистр 3 сдвига на один разряд. Задним фронтом импульсов элементов входной развертки производится переключение первого счетгчика 1. Через каждые . . шестнадцать элементов первый счетчик 1 полностью заполняется (фиг. Зек, 5, в, г, фиг. 4о|,Б,в,т.) и далее цикл . периодически повторяется. После записи в регистр 3 сдвига шестнсщцатого элемента сигналом старшего разряда первого счетчика 1, который поступает на тактовый вход первого триггера 4 и регистра 5, в момент пере ючения первого счетчика 1 из состояния полного заполнения в нулевое, в регистр 5 производится запись сигнала , поступающего на его.вход с выхода регистра 3 сдвига. Вэтот же момент времени производится переключение первого триггер1а 4. На вЪлходе первого триггера 4 поя:вляется логическая единица (фит. Зж, фиг.. 4ж). В таком состоянии первый триггер 4 находится до момента появления импульса на третьем выходе блока 13 управления. Логическая единица с выхода первого триггера 4 подается на вход элемента И б. В момент появления , импульса на втором входе элемента И 6, поступающего с третьего выхода блока 13 управления, на выходе элемента И б формируется импульс (фиг. Зэ, фиг. 4э), который поступает на вход установки второго триггера 7 и устанавливает на выходе второго триггера 7 логическую единицу (фиг. Зи, фиг, 4и), в момент появлеВИЯ логической единицы на втором входе блока 13 управления, на чет вэртом выходе блока 13 управления по является импульс сброса первого триггера 4 (фиг. Зк, фиг. 4 к). Этим импульсом, поступающим с четвертого выхода блока 13 управления на вход сброса первого триггера 4, этот триг гер устанавливаетЪя в исходное состо яние (фиг. Зж, фиг, 4ж). Логическая единица, поступающая с выхода второго триггера 7 на управляющий вход коммутатора 11, обеспечивает подклю чение выходов разрядов второго счетчика 2 через коммутатор 11 к первому адресному входу блока 9 памяти. В момент появления логической единицы, на выходе второго триггера 7 начинается цикл записи. I В начале цикла записи по заднему фррнту импульса, поступающего с третьего выхода блока 13 управления, н второй вход управления блока 9 памя ти, в входной регистр блока 9 памяти записывается сигнал, поступающрш с выхода регистра 5. Кроме того, с начала цикла записи формируются на первом выходе блока 13 управления импульсы тактирования блока 9 памяти Ч фиг.3л, фиг. 4л) и импульс записи (фи.г.3м,, фиг. ). Во время формирования импульса записи производится запись сигнала, поступающего на информационный вход блока 9 памя-ти по адресу, определяемому вторьш счетчиком 2. Цикл записи заканчивается в момент формирования импульса на втором выходе блока 13 управления который поступает на вход сброса триггера 7 и опрокидывает его в исхо ное состояние (фиг. Зи,-фиг. 4 и). В этот момент времени начинается цикл считывания. В этот же момент времени сигнал, поступающий с выхода триг- л гера 7 на счетный вход второго счетт чика. 2, переключает второй счетчик (фиг. 4н). Таким образом, производится преобразование скорости развертки за счет последовательной медленной записи в блок 9 памяти каждого кадрй изображения и быстрого многократного считывания изображения записанного кадра с скоростью, близкой к вещательному стандарту. Блок 13 управления (фиг.2) работает следующим образом. В режиме считывания., когда на вто рой вход блока поступает логический ноль с выхода второго триггера 7, третий ждущий мультивибратор 20 нахо дится в невозбужденном состоянии, й-триггер 16 может устанавливаться по сигналу на его тактовом входе только в ноль. Сигнал, поступающий на первый вход блока 13 управления с выходов четырех младших разрядов третьего счетчика 12, поступает на . вход каждого блока 18-и 19 совпадения. По кодовой комбинации этого сигнала, соответствующего 1улю, на выходе блока 19 совпадения формируются импульсы, поступающие на третий выход .блока 13 управления (фиг., ФИГ.4Э). По кодовой комбинации этого же сигнала, соответствующего восьми на выходе блока 18 совпадения фО1 4Ируются импульсы (фиг. Зё, фиг. 4е), поступающие на второй выход блока 13 управления. Кроме того, импульсы с выхода блока 18 совпадения череэ элемент ИЛИ 17 поступают на в.ход первого ждущего мультивибратора 14, Первый ждущий мультивибратор 14 эапускается по переднему фронту импульса и на его выходе формируются импульсы тактирования блока 9 памяти, которые поступают на вход второго ждущего мультивибратора 15, на вход сброса В-триггера 16 и на первый выход блока 13 управления. Запускается второй ждущий мультивибра;тор 15. Импульс, формируемый . на его выходе, поступает на тактовый вход D-триггера 16. В режиме считывания D -триггер 16 не. опрокидЁ вается. В моментвремени, когда сигнал, поступающий с выхода второго триггера 7 на вхоД третьего ждущего мультив.ибратора 20 и на информационный. вход D-триггера 16, йзме.няет свое состояние с логического нуля в состо- . логической единицц, первый ждущий мультивибратор 20 запускается На его выходе формируется импульс, который поступает на четвертый выход блока 13 управления и через элемент ИЛИ 17 на вход первого ждущего мультивибратора 14. Э.ТИМ импульсом запускается по переднему фронту первый ждущий мультивибратор 14. На его;выходе формируется импульс тактирования блока 9 памяти. Аналогично, как во время считывания., по заднему фронту этого импульса запускается второй ждуидай мультивибратор 15, с выхода которого импульс поступает на тактовый вход D-триггера 16, который по заднему фронту этого импульса рпрокидываётся. На выходе р-триггера 16 формируется импульс записи, поступающий на первый выход блока 13 управления. Во.время последующего цикла считывания О-триггер 16 сбрасывается в исходное состояние кы пульсом, поступающим на- вход сброса D-триггера 16 с выхода ждущего мультивибратора 14 .в момент запуска Пйсг леднего. Формирование импульса записи завершается.; Использование предлагаемого, преобразователя телевизионного стандарта позволяет получить на экране нещательного видеоконтрольного блока изображение объекта, исследуемого при помощи малокадровой телевизионной передающей камеры. При этом достигается полное соответствие формы преобразованного видеосигнала входному видеосигналу.

В отличие от существующих преобразователей частота разложения малокадровой передающей камеры может про извольно изменяться от частот, близких к нулю, до частоты, равной частоте разложения выходной развертки. ,-При этом частота разложения преобразован ного стандарта может оставаться неизменной, значение которой удовлетворяет техническим.условиям . вещательного телевидения. Следова- тельно, использование предлагаемого преобразователя телевизионного.станг дарта совместно с вещательным видеоконтрольным позволит заменить приспособленные к определенной скорости развертки малокадровые виде оконтрольные блоки, использующие телевизионные трубки с накоплением на обычные стандартные. Это позволит уменьшить время обнаружения жущихся объектов и значительно сократить время для определения координат обнаруженного объекта. ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Преобразователь телевизионного стандарта | 1987 |

|

SU1415467A1 |

| Устройство для коррекции апертурных искажений электронно-лучевой трубки | 1986 |

|

SU1334394A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| СПОСОБ ШИФРАЦИИ И ДЕШИФРАЦИИ ТЕЛЕВИЗИОННЫХ СИГНАЛОВ И СИСТЕМА ШИФРАЦИИ ТЕЛЕВИЗИОННОГО СИГНАЛА | 1990 |

|

RU2106760C1 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

1. ПРЕОБРАЗОВАТЕЛЬ ТЕЛЕВИЗИОННОГО СТАНДАРТА, додержавши первый счетчик, синхровход которого соединен с синхровходом второго счетчика, к выходу которого подключен первый групповой вход колмутатора, трет й счетчик, первый групповой выход которого соединен с вторым группо1вым входом коммутатора, групповой выход которого через блок памяти подключен к групповому . входу циф о« аналогового преобразователя, аналогоцифровой преобразователь, а также блок управления, групповой выход которого соединен с вторым групповым входом блока памяти, третий групповой вход которого подключен к второму групповому выходу третьего счетчика и к групповому входу блока управления, отличаю тем, что, с целью повышения точности преобразования при произвольно меняющихся частотах входной и выходной разверток, в него введены два триггера, регистр сдвига, элемент И и регистр, при .этом групповой выход аналого-цифрового преобразователя через последовательно соединенные ре- гистр сдвига и регистр подключен к четвертому групповому входу блока памяти, выход .первого счетчика соеди- нен с первым входом первого триггера и с сЬответств1ую1цим входом регистра, выход первого триггера через элемент И соединен с первым входом второго триггера, выход которого подключен к управляющему входу блока управления, к управляющему входу коммутатора и к управляющему входу второго счетчика, причем первый выход блока управления соединен с вторым входом второго триггера, второй выход блока управления соединен с вторам .входом элемента И и соответствующим : V входом блока памяти, третий выход блока управления соединен с вторым входом первого триггера, а тakтoвaй вход первого счетчика соединен с тактовым входом регистра сдвига.. 2. Устройство по п. 1, о т л и -. чающееся тем, что блок, уп равления содержит два блока совпадения, три ждущих муль.тивибратора, элемент ИЛИ и D-триггер причем | выход первого блока совпадения сое(Л динен с первым входом элемента ИЛИ, выход которого через последоват.ельно соединенные первый и второй ждущие мультивибраторы подключен к перврму входу -триггера, второй вход i которого соединен с входом третьего ждущего мультивибратора, выход которого подключен к второму входу эJieмeн.та ИЛИ,а выход первого ждущего муль- тивибратора соединен с третьим вхоCD Эб дом D -триггера, при этом групповые входы первого и второго блоков сов-падения являются групповым входом :л блока управления, вход третьего жду щего мультивибратора является ynjiaBо ляюидам входом блока управления, вы:ход первого блока совпадения- является первым вь1ходом блока управле- ния, выход второго блока сю падения является вторым выходом блока управления, выход третьего ждущего мультиI вибратора является третьим выходом блока управления, а выходы первого ждущего мультивибратора и -триггера являются групповым выходом блока .управления.

§i Ct HxpouM§;§ П(//}ьсы §5 ИМП( сь/ э/ie ментоб Фиъ. Выход Синхроимпу ьсь..нхрогенерехтара 8ь(хоаио1( развертки

фиг. 2 цементов ёыходноиI 16 элементов pc(3Sepmifu 1 гтл п ё Г1 л ГТПГГГ н

г д е ж

н

tfUff/l

ci umbteaHu

фиъ. 3

иикл

записи

фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Зажим для канатной тяги | 1919 |

|

SU358A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-05-07—Публикация

1981-04-24—Подача