Изобретение относится к импульсной технике и может быть использовано в системах автоматики и вычислительной техники для генерирования программируемой импульсной последовательности с широким диапазоном изменения импульсов и пауз.

Целью изобретения является расширение функциональных возможностей генератора за счет увеличения диапазона изменения длительностей формируемых импульсов и пауз последовательности.

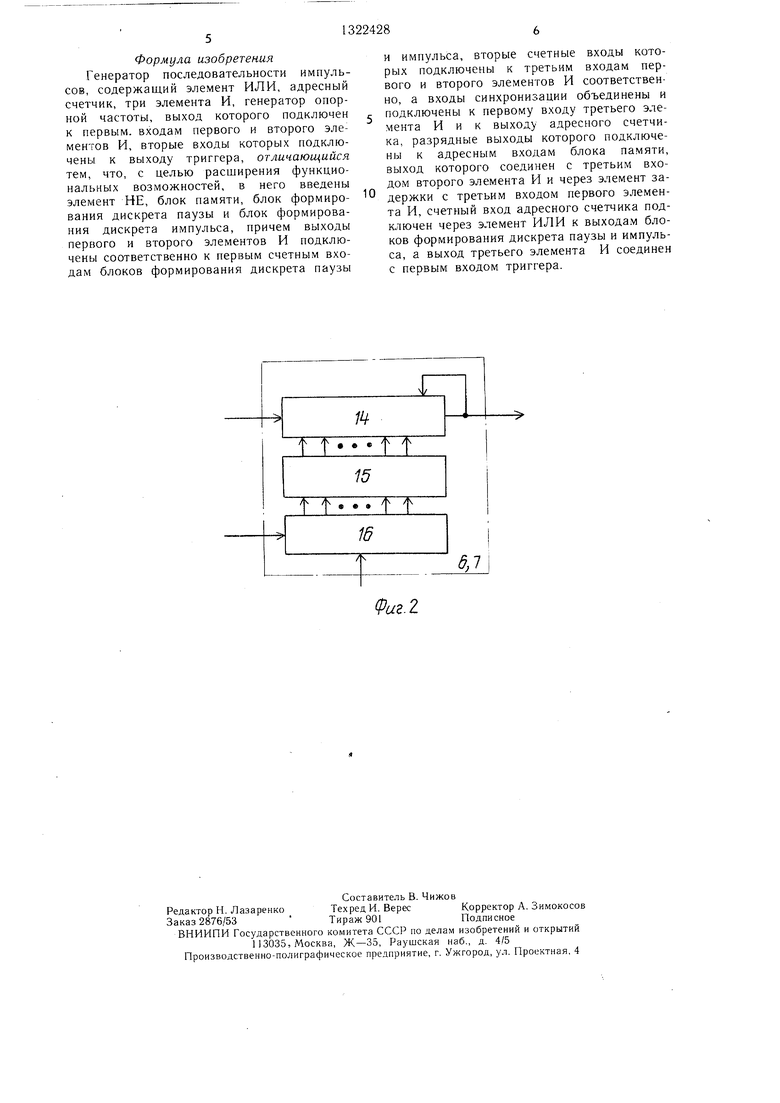

На фиг. 1 представлена структурная схема генератора последовательности импульсов; на фиг. 2 - структурная схема блока формирования дискрета (импульса или паузы).

Генератор последовательности импульсов содержит (фиг. 1) генератор 1 опорной частоты, элементы И 2-4, триггер 5, блок 6 формирования дискрета паузы, блок 7 формирования дискрета импульса, элеВ режиме внешней синхронизации генератор работает следующим образом.

В исходном состоянии устройства на выходе блока 10 наблюдается низкий уровень 5 напряжения, на шине 13 устройства - высокий уровень, открываюший элемент И 2, на выходе триггера 5 - низкий уровень напряжения, блокирующий прохождение опорных импульсов генератора 1 через элементы И 3 и 4, в ДПКД 14 блока 7 формирования дискрета импульса записан код N41, пропорциональный одному дискрету первого формируемого импульса последовательности, т. е. код, определяющий продолжительность удержания адресов ячеек бло- 5 ка 10 памяти, с которых считываются единичные символы для формирования первого импульса.

10

В ДПКД 14 блока 6 формирования дискрета паузы записан код N«i, пропормент НЕ 8, адресный счетчик 9, блок 10 20 циональный одному дискрету первой форми- памяти, элемент ИЛИ 11, входные шиныруемой паузы последовательности, т. е. код,

определяющий время удержания адресов ячеек блока 10 памяти, с которых считываются нулевые символы для формирования

12 и 13, причем выход генератора 1 подключен к первым входам элементов И 3 и 4, вторые входы которых подключены к выходу триггера 5, третий вход первого элемента . первой паузы последовательности. В блоках

И 3 подключен к выходу элемента НЕ 8 с .. -7 ж„

и к второму счетному входу блока 6, вход синхронизации которого подключен к первому входу третьего элемента И, к выходу

адресного счетчика 9 и к входу синхро15 памяти блоков 6 и 7 формирования дискретов импульсов и пауз записана соответственно информация о длительностях дискретов формирования каждого из импульсов и каждой паузы последовательности. В блонизации блока 7, первый счетный вход зо ° виде нулей и единиц записа- которого подключен к выходу второго эле-на информация о структуре формируемой

мента И 4, третий вход которого соеди-последовательности. Длительности нулевых и

нен с втррым счетным в.ходом блока 7, сединичных символов задаются соответствуювходом элемента НЕ 8 и выходом блока 10,щими блоками 6 и 7 формирования дискреадресные входы которого соединены с раз-тов в зависимости от порядкового норядными выходами адресного счетчика 9, 35 мера формируемого импульса или паузы.

счетный вход которого через элемент ИЛИ 11

С приходом по шине 12 устройства внешнего синхронизирующего импульса триггер 5 переводится в другое устойчивое состояние, при котором на выходе этого Пример выполнения блоков б и 7 фор- 0 триггера 5 формируегся высокий уровень мирования дискрета паузы и импульсанапряжения. Элемент И 4 закрыт низким

представлен на фиг. 2, каждый из которыхуровнем напряжения с выхода блока 10,

содержит делитель 14 с переменным коэф- опорная частота с генератора 1 через нефициентом деления СДПКД),блок 15 памя- ° проходит. Элемент И 3 положити и адресный счетчик 16, причем выходы дс тельным перепадом напряжения с триггел лt .г - ллтл. лд1 гл/ т: 1гсч| т71пг ii dtr игт г

делителя 14 и адресного счетчика 16 подключены к входам блока 15 памяти.

Адресный счетчик 16 производит отсчет по входу 15 перепадов напряжения типа 1-0.

соединен с выходами блоков 6 и 7, при этом выход третьего элемента И 2 подключен к первому входу триггера 5.

ра 5 и высоким уровнем напряжения с выхода элемента НЕ 8 открывается для прохождения импульсов опорной частоты на блок 6 формирования дискрета паузы, т. е. на ДПКД 14 этого блока. Импульсами опор- Генератор последовательности импульсов 50 ° частоты уменьшается до нуля код N,, может работать в двух режимах; в режимев ДПКД 14, пропорциональный одному дискрету первой формируемой паузы. Когда код в ДПКД 14 уменьшится до нуля, на его выходе формируется короткий импульс, конепрерывной генерации, т. е. формируемая структура последовательности многократно тиражируется с периодом, равным длительности этой структуры, и в режиме внешторый передним фронтом через элемент ИЛИ

ней синхронизации, т. е. по каждому 55 11 увеличивает на единицу первоначальный внешнему импульсу синхронизации генера-код адресного счетчика 9. По новому адретор однократно формирует структуру заданной последовательности.

су к выходу блока 10 подключается новая соответствующая ячейка памяти.

В режиме внешней синхронизации генератор работает следующим образом.

В исходном состоянии устройства на выходе блока 10 наблюдается низкий уровень напряжения, на шине 13 устройства - высокий уровень, открываюший элемент И 2, на выходе триггера 5 - низкий уровень напряжения, блокирующий прохождение опорных импульсов генератора 1 через элементы И 3 и 4, в ДПКД 14 блока 7 формирования дискрета импульса записан код N41, пропорциональный одному дискрету первого формируемого импульса последовательности, т. е. код, определяющий продолжительность удержания адресов ячеек бло- ка 10 памяти, с которых считываются единичные символы для формирования первого импульса.

ваются нулевые символы для формирования

первой паузы последовательности. В блоках

торый передним фронтом через элемент ИЛИ

11 увеличивает на единицу первоначальный код адресного счетчика 9. По новому адресу к выходу блока 10 подключается новая соответствующая ячейка памяти.

Если в этой ячейке записан нуль, то на выходе блока 10 остается низкий уровень напряжения, что свидетельствует о продолжении формирования первой паузы. Задним фронтом короткого импульса с выхода блока 6 формирования дискрета паузы в ДПКД 14 этого блока записывается из блока 15 памяти опять код N„1, пропорциональный одному дискрету первой формируемой паузы. Элемент И 3 остается открытым, и импульсы опорной частоты продолжают поступать на блок 6 формирования дискрета паузы, уменьшая в его ДПКД 4 код до нуля.

При нулевом коде ДПКД 14 опять на выходе блока 6 формируется второй короткий импульс, который передним фронтом через элемент ИЛИ 11 увеличивает на единицу код адресного счетчика 9. По новому адресу к выходу блока 10 памяти подключается ячейка памяти. Если в этой ячейке записана единица, на вы.ходе блока 10 памяти формируется высокий уровень напряжения, что свидетельствует об окончании формирования первой паузы, состоящей из двух нулевых символов, и о начале формирования первого импульса последовательности. Высоким уровнем напряжения с выхода блока 10 памяти открывается элемент И 4 и через элемент НЕ 8 закрывается элемент И 3.

Перепад напряжения на выходе элемента НЕ 8 поступает также на блок 6 формирования дискрета паузы, вход адресного счетчика 16. Отрицательный перепад напряжения изменяет первоначальный код адресного счетчика 16 на единицу. По новому адресу на выходе блока 15 памяти сформируется код , пропорциональный дискрету второй паузы формируемой последовательности. Этот код N„2 записывается в ДПКД 14 задним фронтом второго короткого импульса с выхода блока 6 формирования дискрета паузы. Таким образом, блок 6 формирования дискрета паузы подготовлен к формированию второй паузы с дискретностью, пропорциональной коду N„2, а импульсы опорной частоты начинают поступать на вход блока 7 формирования дискрета импульса т. е. на его ДПКД 14. Записанный в ДПКД 14. код N„1 уменьшается до нуля. При обнулении ДПКД 14 на выходе блока 7 формирования дискрета импульса формируется короткий импульс, который передним фронтом через элемент ИЛИ 11 увеличивает на единицу код адресного счетчика 9. По новому адресу к выходу блока 10 памяти подключается новая ячейка памяти. Если в этой ячейке записан нуль, на выходе блока 10 памяти формируется низкий уровень напряжения, который отключает канал формирования единичного дискрета (элементы 4 и 7) и включает канал формирования нулевого дискрета (элементы 3 и 6). Отрицательный перепад напряжения на входе блока 7 формирования дискрета импульса изменяет первоначальный код адресного счетчика 16 на единицу. По новому адресу на выходе бло5 ка 15 памяти формируется код N„2, пропорциональный дискрету второго импульса формируе.мой последовательности. Этот код N„2 записывается в ДПКД 14 задним фронтом короткого импульса с выхода блоQ ка 7 формирования дискрета импульса. Таким образом, фор.мируется пауза, состоящая из двух нулевых си.мволов длительностью по Ni,,-To каждый, и импульс, состоящий из одного единичного символа длительностью Nn-T(j, где То - период следова5 ния импульсов опорной частоты генератора . Далее процесс формирования пос- , ледовательностн импульсов к пауз происходит аналогично. Осуществив перебор всех адресов, по которым в ячейках блока 10 памяти записывается информация о структуре формируемой последовательности, адресный, счетчик 9 формирует короткий по длительности импульс переполнения, поступающий через открытый элемент И 2 на триггер 5 и устанавливающий его в исход5 ное состояние, что свидетельствует об окончании формирования заданной последовательности. С прнходо.м -следующего импульса синхронизации процесс формирования заданной последовательности повторяется.

0 Для перевода устройства в режим непрерывной генерации необходимо подключить 1лину 13 к источнику низкого уровня напряжения. Устройство начинает работать с поступление.- на щину 12 короткого пускового импульса, который устанавли5 вает на выходе триггера 5 высокий уровень напряжения. Это приводит к тому, что элемент И 2 закрывается и импульс переполнения, сформированный адресным счетчиком 9 после опроса все.х ячеек блока 10 па мяти, не устанавливает триггер 5 в исходное состояние. После переполнения адресный счетчик 9 снова начинает перебирать адреса ячеек б.юка 10 памяти с первой до последней, т. е. до переполнения. Импульс переполнения адресного счет5 чика 9 устанавливает в исходное состояние и адресные счетчики 19 блоков формирования дискретов импульса 7 и паузы 6. При этом в ДПКД 4 блока 7 формирования дискрета импульса записывается код Nni, пропорциональный одному дискре0 ту первого формируемого импульса последовательности. В ДПКД 14 блока 6 формирования дискрета паузы записывается код N,, , пропорциональный одному дискрету первой формируемой паузы последовательности.

5

Далее процесс формирования последовательности импульсов л пауз многократно повторяется.

Формула изобретения Генератор последовательности импульсов, содержащий элемент ИЛИ, адресный счетчик, три элемента И, генератор опорной частоты, выход которого подключен к первым, входам первого и второго элементов И, вторые входы которых подключены к выходу триггера, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены элемент НЕ, блок памяти, блок формирования дискрета паузы и блок формирования дискрета импульса, причем выходы первого и второго элементов И подключены соответственно к первым счетным входам блоков формирования дискрета паузы

и импульса, вторые счетные входы которых подключены к третьим входам первого и второго элементов И соответственно, а входы синхронизации объединены и подключены к первому входу третьего элемента И и к выходу адресного счетчика, разрядные выходы которого подключены к адресным входам блока памяти, выход которого соединен с третьим входом второго элемента И и через элемент задержки с третьим входом первого элемента И, счетный вход адресного счетчика подключен через элемент ИЛИ к выходам блоков формирования дискрета паузы и импульса, а выход третьего элемента И соединен с первым входом триггера.

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсной последовательности | 1988 |

|

SU1529421A1 |

| Устройство для формирования пачек импульсов | 1987 |

|

SU1451834A1 |

| Устройство для формирования сигналов алфавитно-цифровых и графических изображений | 1982 |

|

SU1083406A1 |

| Генератор случайного импульсного процесса (его варианты) | 1983 |

|

SU1107121A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Устройство для формирования символов | 1983 |

|

SU1088060A1 |

| Устройство управления электродвигателем | 1985 |

|

SU1328919A1 |

| Устройство для формирования символов | 1983 |

|

SU1113840A1 |

| Генератор случайного импульсного процесса | 1982 |

|

SU1094032A1 |

| Устройство для формирования импульсных последовательностей | 1986 |

|

SU1374412A2 |

Изобретение может быть использовано в системах автоматики и вычислительной техники. Цель изобретения - расширение функциональных возможностей устройства. Генератор содержит элементы И 2...4, триггер 5, генератор 1 опорной частоты, адресный счетчик 9 и элемент ИЛИ 11. Введение элемента НЕ 8, блока 10 памяти и блоков 6 и 7 формирования дискрета паузы и импульса соответственно увеличивает диапазон изменения длительности формируемых импульсов и пауз последовательности. 2 ил. S / - СО ю кэ 00 Л N 10 (Pu2.1

| Генератор последовательности импульсов | 1980 |

|

SU949786A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-25—Подача