Изобретение относится к импульсной технике и предназначено для использования в корреляционной и измерительной технике.

Целью изобретения является расширение функциональных возможностей за счет формирования информационного сигнала о длительности задержки и упрощение перестройки времени задержки.

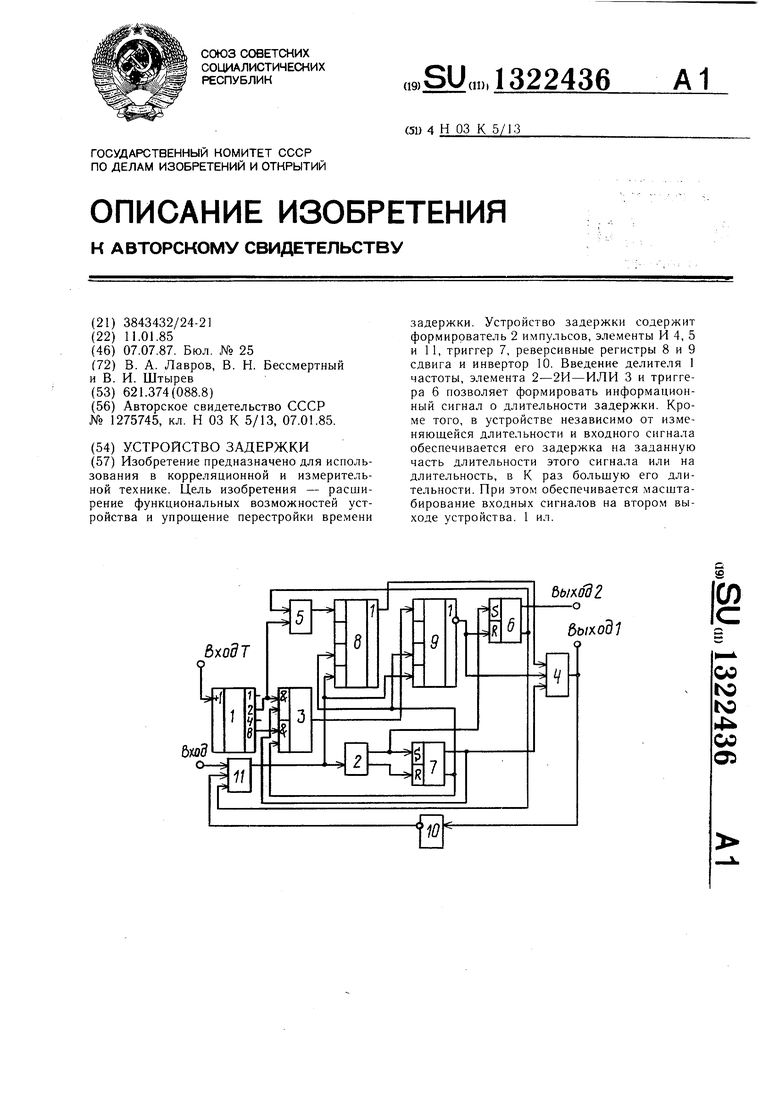

На чертеже представлена структурная схема устройства задержки.

Устройство содержит делитель 1 частоты, формирователь 2 импульсов., элемент 2- 2И-ИЛИ 3, элементы И 4 и 5, триггеры 6 и 7, реверсивные регтетры 8 и 9 сдвига, инвертор 10 и элемент И 11.

Источник входной импульсной последовательности подключен к первому входу элемента И 11, выход которого подключен к входу формирователя 2 импульсов и к первым входам реверсивных регистров 8 и 9 сдвига, выходы которых подключены соответственно к первому и второму входам элемента И 4, выход которого является выходом устройства и через инвертор 10 подключен к второму входу элемента И 11. Источник тактовых импульсов подключен к входу делителя 1 частоты, первый выход которого подключен к первым входам элемента И 5 и элемента 2-2И-ИЛИ 3, выходы которых подключены к вторым входам соответственно реверсивных регистров 8 и 9 сдвига. Выход реверсивного регистра 9 сдвига подключен к первому входу триггера 6, первый выход которого подключен к третьему входу элемента И 1 1 и к второму входу элемента И 5. Первый выход формирователя 2 импульсов подключен к первому входу триггера 7 и к второму входу триггера 6, второй выход которого является дополнительным выходом устройства. Второй выход формирователя 2 импульсов подключен к второму входу триггера 7, первый выход которого подключен к третьим входам реверсивных регистров 8 и 9 сдвига и к второму входу элемента 2-2И- ИЛИ 3. Второй выход триггера 7 подключен к третьим входам элемента И 4 и элемента 2-2И-ИЛИ 3, к четвертому входу которого подключен второй выход делителя 1 частоты.

Формирователь 2 импульсов выполнен по известной схеме.

Устройство работает следующим образом.

В исходном положении триггеры 6 и 7 установлены в нулевое состояние, при этом элемент И 5 открыт по одному из своих входов, а на регистры 8 и 9 подаются разрешающие потенциалы для сдвига информации, например, вправо. Элемент 2-2И ИЛИ 3 открыт единичным потенциалом с выхода триггера 7 таким образом, что на его выходе, например, присутствует пониженная частота импульсов с выхода делителя 1. Таким образом, на регистр 8 с выхода элемента И 5 поступают импульсы средней частоты от источника тактовых импульсов, а на регистр 9 с выхода элемента 2-2И-ИЛИ 3 - импульсы пониженной частоты тактовых импульсов на соответствующий коэффициент деления делителя 1.

Импульс, поступающий на вход устройства через открытый элемент И 11, поступает на вход формирователя 2, на втором выходе которого по фронту входного им пульса формируется короткий импульс, подтверждающий исходное состояние триггера 7. Одновременно входной импульс поступает в регистры 8 и 9 на первые входы, например информационные, и производится за5 пись потенциала логической единицы тактовыми импульсами в ячейках регистров в течение в.ремени следования входного импульса.

По спаду входного импульса на втором выходе формирователя 2 выделяется импульс

0 который опрокидывает триггеры 6 и 7, при этом элементы И 5 и 11 закрывается. Соответствующий потенциал с выхода триггера 7 открывает элемент 2-2И-ИЛИ 3 по другому входу, и импульсы средней тактовой

частоты поступают в регистр 9, включенный этим же потенциалом триггера 7 на сдвиг информации в противоположную сторону. На втором выходе, например прямом, триггера 6 формируется выходной сигнал, крат- ный.входному, который оканчивается при опQ рокидывании триггера 6.

Регистр 9 осуществляет задержку формирования выходного сигнала на время, меньшее его длительности во столько раз, во сколько низкая частота записи меньще средней частоты считывания. По оконча5 НИИ времени задержки, т.е. с появлением единичного потенциала на инверсном выходе первой ячейки регистра 9, триггер 6 опрокидывается в исходное положение, при этом открывается элемент И 5 и тактовые импульсы средней частоты с первого выхода

0 делителя 1 поступают в регистр 8, включенный потенциалом с триггера 7 на сдвиг информации в противоположную записи сторону. И с выхода первой ячейки регистра 8 через элемент И 4 на выходе устс ройства формируется выходной задержанный импульс, длительность которого равна длительности входного, так как его запись-считывание в регистр 8 производится на одной средней частоте.

0 В устройстве, независимо от изменяющейся длительности входного сигнала, обеспечивается его задержка на заданную часть длительности этого сигнала или на длительность, в К раз больщую его длительности, а также масштабирование вход5 ных сигналов на втором выходе устройства.

Изменение коэффициента К реализуется переключением только одного соответствующего вывода делителя частоть к четвертому входу элемента 2-2И-ИЛИ.

Формула изобретения

Устройство задержки, содержащее два регистра сдвига, инвертор, формирователь импульсов, триггер и три элемента И, при этом первый вход первого элемента И является входом устройства, второй его вход через- инвертор подключен к первому выходу устройства и выходу второго элемента И, первый и второй входы подключены соответственно к выходам первого и второго регистров сдвига, первый вход первого регистра сдвига подключен к выходу третьего элемента И, выход первого элемента И подключен к второму входу первого регистра сдвига и входу формирователя импульсов, выходы которого подключены соответственно к первому и второму входам триггера, первый выход которого подключен к третьим входам регистров сд.вига, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования информационного сигнала о дли0

5

0

тельности задержки и упрош.ения перестройки времени задержки, в него введен делитель частоты, второй триггер и элемент 2-2И-ИЛИ, причем вход делителя частоты является тактовым входом устройства, его первый выход подключен к первым входам третьего элемента И и элемента 2-2И- ИЛИ, второй вход которого подключен к второму выходу первого триггера и треьс- му входу второго элемента И, второй выход делителя частоты подключен к третьему входу элемента 2-2И-ИЛИ, четвертый вход которого подключен к первому выходу первого триггера, выход элемента 2-2И- ИЛИ подключен к первому входу второго регистра сдвига, второй вход которого подключен к выходу первого элемента И, выход второго регистра сдвига подключен к первому входу второго триггера, второй вход которого подключен к второму выходу формирователя импульсов, а первый выход подключен к третьему входу первого элемента И и к второму входу третьего элемента И, а второй выход является вторым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1985 |

|

SU1275745A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для сравнения фаз | 1984 |

|

SU1282254A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Устройство для управления следящим приводом | 1986 |

|

SU1416939A1 |

| Делитель частоты с переменным коэффициентом деления | 1980 |

|

SU1075413A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

Изобретение предназначено для использования в корреляционной и измерительной технике. Цель изобретения - расширение функциональных возможностей устройства и упрощение перестройки вре.мени ОХ бхоЗ задержки. Устройство задержки содержит формирователь 2 импульсов, элементы И 4, 5 и 11, триггер 7, реверсивные регистры 8 и 9 сдвига и инвертор 10. Введение делителя 1 частоты, элемента 2-2И-ИЛИ 3 и триггера 6 позволяет формировать информационный сигнал о длительности задержки. Кроме того, в устройстве независимо от изменяющейся длительности и входного сигнала обеспечивается его задержка на заданную часть длительности этого сигнала или на длительность, в К раз больщую его длительности. При этом обеспечивается масштабирование входных сигналов на втором выходе устройства. 1 ил. бь/хоЭ7 OQ ю to со О5

| Устройство задержки | 1985 |

|

SU1275745A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1985-01-11—Подача