появляются сигналы единичного уровня, этот сигнал, поступая на тактовые входы триггеров 11 и 12, фиксирует в них состояние старших разрядов счетчиков 13 и 14 и через интервал времени, определяемый элементом задержки 10, устанавливает в исходное состояние счетчики 13 и 14. При увеличении (уменьшении) частоты сравниваемых сигналов уменьшается (уве1

Изобретение относится к электротехнике и может применяться в цифровых комплексах релейной защиты и автоматики энергосистем, в которых установки измерительных органов ав- томатически изменяются при изменении режима работы энергосистемы или за- даются оператором с пульта ЭВМ.

Целью изобретения является повы

шение точности сравнения фаэ путем исключения погрешности при изменении частоты входных сигналов.

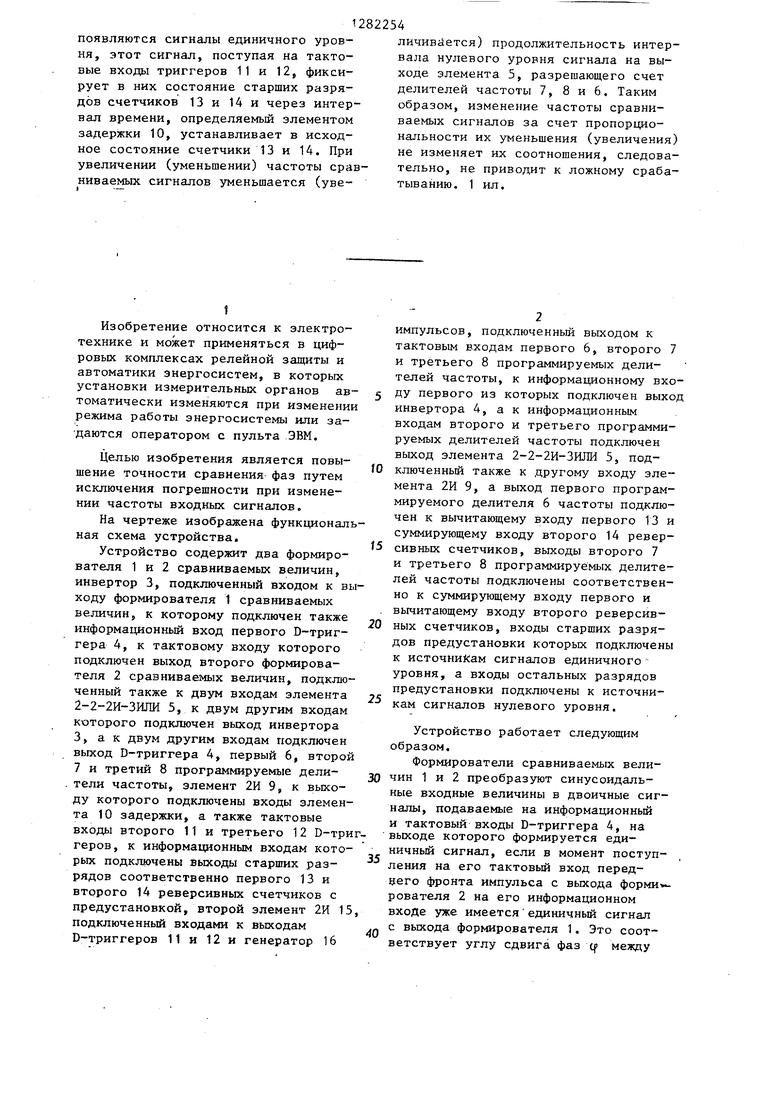

На чертеже изображена функциональная схема устройства.

Устройство содержит два формирователя 1 и 2 сравниваемых величин, инвертор 3, подключенный входом к выходу формирователя 1 сравниваемых величин, к которому подключен также информационный вход первого D-триг- гера 4, к тактовому входу которого подключен выход второго формирователя 2 сравниваемых величин, подключенный также к двум входам элемента 2-2-2И-ЗИЛИ 5, к двум другим входам которого подключен выход инвертора 3, а к двум другим входам подключен выход D-триггера 4, первый 6, второй 7 и третий 8 программируемые дели- тели частоты, элемент 2И 9, к выходу которого подключены входы элемента 10 задержки, а также тактовые входы второго 11 и третьего 12 D-три геров, к информационным входам которых подключены выходы старших разрядов соответственно первого 13 и второго 14 реверсивных счетчиков с предустановкой, второй элемент 2И 15 подключенный входами к выходам D-триггеров 11 и 12 и генератор 16

личивается) продолжительность интервала нулевого уровня сигнала на выходе элемента 5, разрешающего счет делителей частоты 7, 8 и 6, Таким образом, изменение частоты сравниваемых сигналов за счет пропорциональности их уменьшения (увеличения) не изменяет их соотношения, следовательно, не приводит к ложному срабатыванию. 1 ил.

импульсов, подключенный выходом к тактовым входам первого 6, второго 7 и третьего 8 программируемых делителей частоты, к информационному входу первого из которых подключен выход инвертора 4, а к информационным входам второго и третьего программируемых делителей частоты подключен выход элемента 2-2-2И-ЗШ1И 5, под- ключенньй также к другому входу элемента 2И 9, а выход первого программируемого делителя 6 частоты подключен к вычитающему входу первого 13 и суммирующему входу второго 14 реверсивных счетчиков, выходы второго 7 и третьего 8 программируемых делителей частоты подключены соответственно к суммирующему входу первого и вычитающему входу второго реверсивных счетчиков, входы старших разрядов предустановки которых подключены к источникам сигналов единичного уровня, а входы остальных разрядов предустановки подключены к источникам сигналов нулевого уровня.

Устройство работает следующим образом.

Формирователи сравниваемых величин 1 и 2 преобразуют синусоидальные входные величины в двоичные сигналы, подаваемые на информационный

и тактовый входы D-триггера 4, на выходе которого формируется единичный сигнал, если в момент поступления на его тактовый вход переднего фронта импульса с выхода форми - рователя 2 на его информационном входе уже имеется единичный сигнал с выхода формирователя 1. Это соответствует углу сдвига фаз if между

сравниваемыми сигналами, удовлетворяющему условию О и i 180°. При угле сдвига фаз 180 q 360 в момен поступления переднего фронта импульса на тактовый вход} на информационном входе будет сигнал нулевого уровня и D-триггер 4 установится в нулевое состояние, D-триггер 4 управляет элементом 2-2-2И-ЗИЛИ 5,который формирует сигнал нулевого уровня, по продолжительности равный времени между передними фронтами импульсов с выходов формирователей 1 и 2, т.е. сигнал, продолжительность которого пропорциональна углу сдв ига фаз. Сформированный таким образом сигнал на выходе элемента 5 сравнивается с продолжительностью полупериода сигнала на входе формирователя 1 при помощи делителе 6-8 частоты и реверсивных счетчиков 13 и 14. Для задания зоны срабатывания устройства на входы установки коэффициентов деления делителей 6-8 частоты подаются в двоичном виде числа а , а , b соответственно. Причем число с выбирается исходя из требуемой разрядности п представления граничных углов зоны срабатывания по формуле

С 2

«-1

а числа а

и Ь, определяО J гллО

ются из соотношений Qimln с

b о

Ч max с округлением до ближайшего целого значения. При частоте сравниваемых сигналов f(j. продолжительность их полупериода будет .1 2f

Тогда при частоте импульсов

f генератора 16 с выхода делителя 6 частоты за период сравниваемых сипналов поступит N

2f.

импульсов. При сдвиге фаз сравниваемых сигналов (f продолжительность интервала нулевого уровня на выходе эле1 Ч

мента 5 будет --- . тг-о, Тогда с вы- /.LC loU

ода делителей 7 и 8 частоты за период сравниваемых сигналов посту1 Ч- 2f

k L b 2f р Т5о

угла сдвига фаз Cf в задаваемый уставкамиCfinlpиср д интервал, будет выполняться условие Ng г Nj i Ng.

пит соответственно N -

Си

а

; тво

и N.

т.е, попадании

нерка выполнения этого условия осуществляется реверсивными счетчиками 13 и 14 причем счетчик 13 предназначен для проверки условия N ь а счетчик 14 - условия N i N

NC,

.Оба

0

5

fO

15

счетчика предварительно устанавливаются в исходное состояние с единицей в старшем разряде и нулями в остальных. Если за время счета число импульсов, поступающих на сум- мирутоЕций вход, равно или больше числа импульсов, поступающих на вычитающий вход, то состояние старшего разряда остается единичным, В противном случае, после окончания счета старший разряд будет иметь нулевое состояние.

Таким образом, счетчик 13, подключенный суммирующим входом к выходу делителя 7 и вычитающим входом к выходу делителя 6, будет к моменту окончания счета иметь единицу в старшем разряде, если ср 1|, а счетчик 14, связанный суммирующим входом с выходом делителя 6 и вычитающим входом с выходом делителя 8, будет иметь единицу в старшем разряде если Ч -Ртох вьщеления момента окончания счета предназначен элемент 2И

0 9, который формирует на своем выходе единичный сигнал в случае, если на входах разрешения счета делителей частоты 6, 7 и 8 появляются сигналы единичного уровня, прекращающие счет.

Единичный сигнал с выхода элемента 2И, 9, поступая на тактовые входы D-триггера 11 и 12, фиксирует в них состояние старших разрядов счетчиков 13 и 14 и через интервал времени,

0 определяемый элементом 10 задержки, устанавливает в исходное состояние счетчики 13 и 14,

Следовательно, D-триггеры 11 и 12 устанавливаются в единичные, состоя5 ния; если выполняется условие (f Выходные сигналы D-тригге- ров 11 и 12 объединяются по функции 2И элементом 15, таким образом, при

4 m;n Q 4 ma)t Р нахождении уг- 0. ла сдвига фаз в зоне срабатывания, на выходе элемента 2И 15 формируется единичный сигнал.

При увеличении (уменьшении) частоты сравниваемых сигналов уменьшает- 5 ся (увеличивается) продолжительность интервала нулевого уровня сигнала на выходе элемента 5, разрешающего счет делителей частоты 7 и 8, следовательно, число импульсов Ng, подаваемых

с выхода делителя 7 частоты на суммирующий вход счетчика 13 и число импульсов Ng, подаваемых с выхода делителя 8 частоты на вычитающий вход счетчика 14. Вместе с уменьшением (увеличением) интервала нулевого уровня с выхода элемента 5 будет пропорционально уменьшаться (увеличиваться ) продолжительность интервала нулевого уровня сигнала на выхо- W ход первого D-триггера, выход инверде инвертора 3, разрешающего счет делителя 6 частоты, следовательно, число импульсов Ыд, подаваемых с выхода делителя 6 частоты на вычитаю15

щий вход счетчика 13 и суммирующий вход счетчика 14. Таким образом, изменение частоты сравниваемых сигналов хоти и приводит к изменению чисел Ng, N,, Np, но за счет пропорциональности их уменьшения (увеличения) не изменяет их соотношения в неравенстве N Ь N Nj, следовательно, не приводит к ложному срабатыванию предлагаемого устройства. Этим обеспечивается повышение точности сравнения фаз при изменяющейся частоте сравниваемых сигналов.

Формула изобретения

Устройство для сравнения фаз, содержащее два формирователя сравниваемых величин, выход первого из которых подключен ко входу инвертора,генератор импульсов, элемент задержки, три триггера и элемент 2И, выход которого является выходом устройства, отличающееся тем, что, с целью повьш1ения точности сравнения фаз путем исключения погрешности при изменении частоты входных сигналов, дополнительно введены элемент 2-2- -2И-ЗИЛИ, три программируемых делителя частоты, элемент 2И и два реверсивных счетчика с предустановкой, а упомянутые триггеры выполнены в виде D-триггеров, при этом выход первого формирователя сравниваемых ве20

25

тора подключен к одному из входов вновь введенного элемента 2И, а также к разрешающему входу первого программируемого делителя частоты, к тактовому входу которого подключен выход генератора импульсов, подключенный также к тактовым входам второго и третьего программируемых делителей частоты, к информационным входам которых, а также к другому входу вновь введенного элемента 2И подключен выход элемента 2-2-2И-ЗИЛИ а выход первого программируемого делителя частоты подключен к вычитающему входу первого и суммирующему входу второго реверсивного счетчиков, выходы второго и третьего программируемых делителей частоты подключены соответственно к сумми30 рующему входу первого и вычитающему входу второго реверсивных счетчиков, входы старших разрядов предустановки которых подключены к источникам сигналов единичного уровня а входы остальных разрядов предустановки подключены к источникам сигналов нулевого уровня, входы разрешения записи реверсивных счетчиков подключены через элемент задержки к выходу вновь введенного элемента 2И, который подключен также к тактовым входам второго и третьего В-триг геров, к информационным входам которых подключены выходы старших разря дов соответственно первого и второго реверсивных счетчиков, а выходы второго и третьего D-триггеров подключены к входам элемента 2И.

35

40

Составитель Т. Щеголькова Редактор С. Патрушева Техред Л.Кравчук Корректоре. Шекмар

Заказ 7280/54 Тираж 619Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

личин подключен также к информационному входу первого D-триггера, к тактовому входу которого подключен выход второго формирователя сравниваемых величин, подключенный также к двум соответствующим входам элемента 2-2-2И-ЗИЛИ, к двум другим входам которого подключен выход инвертора, а к третьим двум входам подключен РЫ

тора подключен к одному из входов вновь введенного элемента 2И, а также к разрешающему входу первого программируемого делителя частоты, к тактовому входу которого подключен выход генератора импульсов, подключенный также к тактовым входам второго и третьего программируемых делителей частоты, к информационным входам которых, а также к другому входу вновь введенного элемента 2И подключен выход элемента 2-2-2И-ЗИЛИ а выход первого программируемого делителя частоты подключен к вычитающему входу первого и суммирующему входу второго реверсивного счетчиков, выходы второго и третьего программируемых делителей частоты подключены соответственно к суммирующему входу первого и вычитающему входу второго реверсивных счетчиков, входы старших разрядов предустановки которых подключены к источникам сигналов единичного уровня а входы остальных разрядов предустановки подключены к источникам сигналов нулевого уровня, входы разрешения записи реверсивных счетчиков подключены через элемент задержки к выходу вновь введенного элемента 2И, который подключен также к тактовым входам второго и третьего В-триг геров, к информационным входам которых подключены выходы старших разрядов соответственно первого и второго реверсивных счетчиков, а выходы второго и третьего D-триггеров подключены к входам элемента 2И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Устройство для управления разгоном и торможением исполнительного двигателя станка | 1981 |

|

SU1062646A1 |

| Функциональный преобразователь полинома третьей степени | 1988 |

|

SU1562907A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровой фазометр | 1989 |

|

SU1688189A1 |

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1599793A1 |

| Устройство для измерения скорости движения воздуха | 1989 |

|

SU1679392A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2444123C1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

Изобретение относится к электротехнике, в частности j релейной защите. Цель изобретения - повышение точности сравнения фаз путем ис ключения погрешности при изменения частоты входных сигналов. Формирователи сравниваемых величин 1 и 2 преобразуют синусоидальные вход- ные величины в двойные сигналы, подаваемые на D-триггер 4, которьш управляет элементом 2-2-2И-3 ИЛИ 5, формирующим сигнал нулевого уровня. Сигнал на выходе элемента 5 сравнивается с продолжительностью полупериода сигнала на входе формирователя 1 при помощи делителей частоты 6, 7 и 8 и реверсивных счетчиков 13, 14. Счетчик 13 подключен суммирующим входом к выходу делителя 7 и вычитающим входом к выходу делителя 6, а счетчик 14 - к выходам делителей 6 и 8. Для выделения момента окончания счета предназначек элемент 2И 9, формирующий единичный сигнал. Если на входах разрешения счета делителей частоты 6, 7 и 8 (Л Ъ I-J& j tC 30 N: to ел

| Устройство для сравнения фаз двух электрических величин | 1979 |

|

SU790061A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сравнения фаз | 1983 |

|

SU1125696A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-01-07—Публикация

1984-06-14—Подача