Изобретение относится к радиотехнике и связи, в частности к телефо-- нии, и может быть использовано для управления коммутационным оборудованием . электронных АТС.Цель изобретани - повьпиение помехоустойчивости и упрощение устройства путем умень цения количества каналов обработки сигналов.

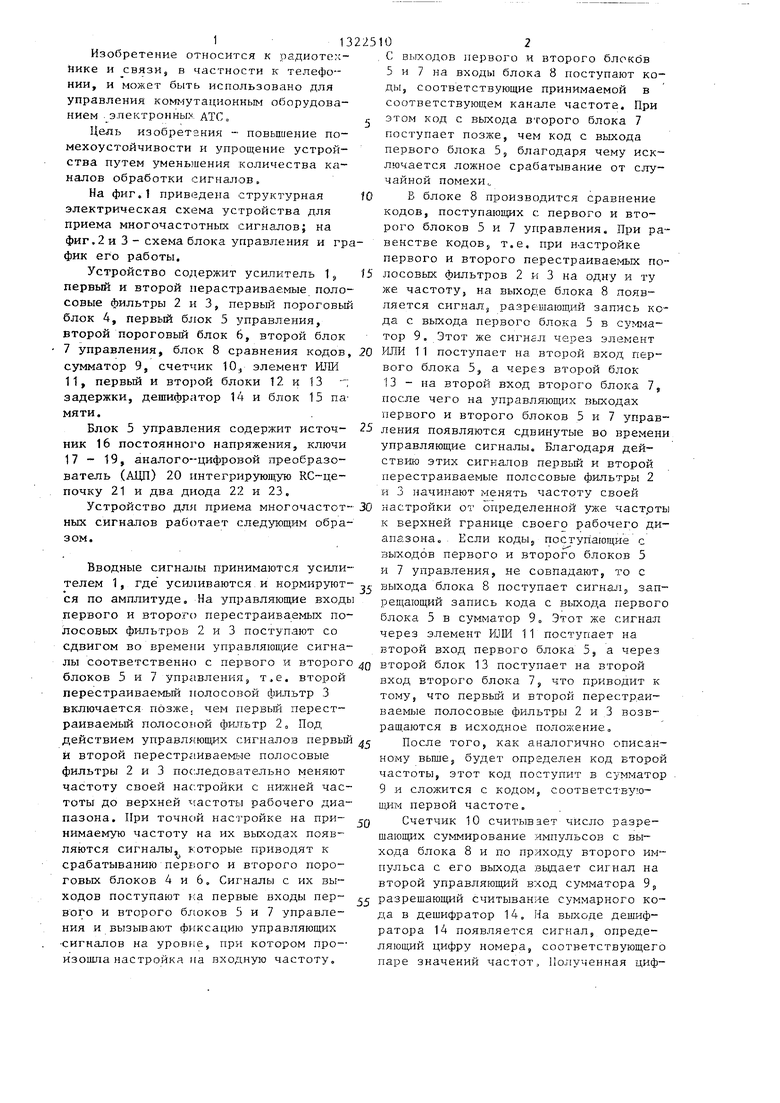

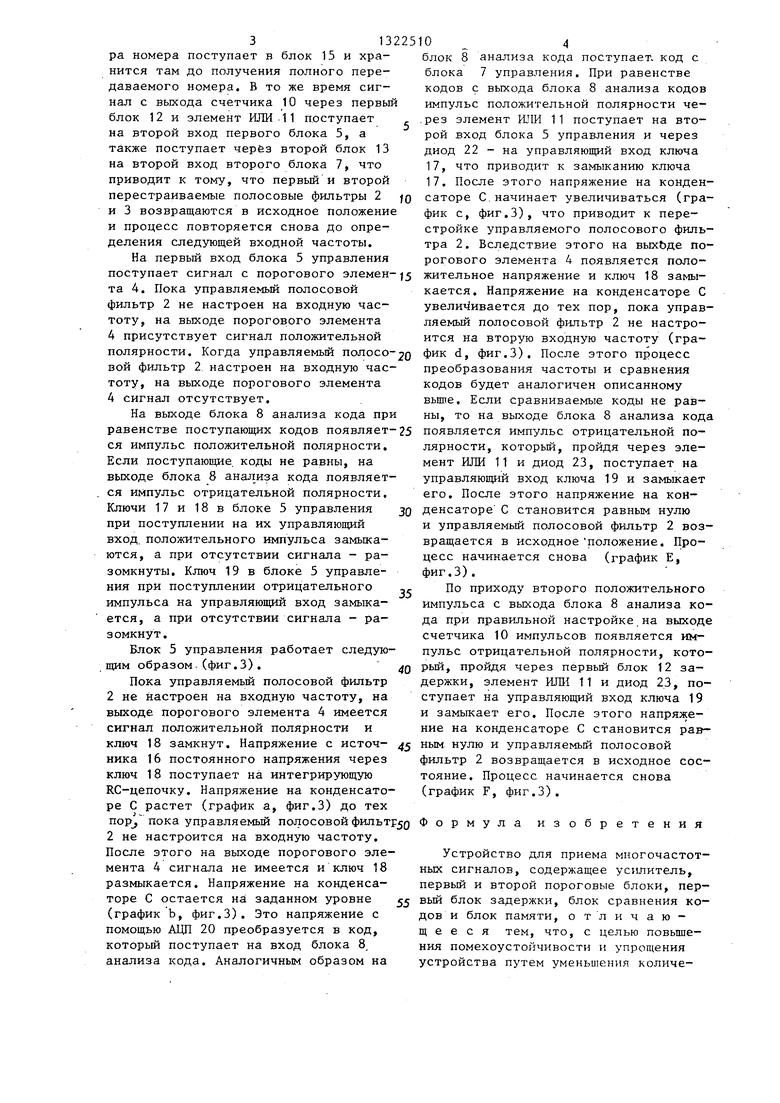

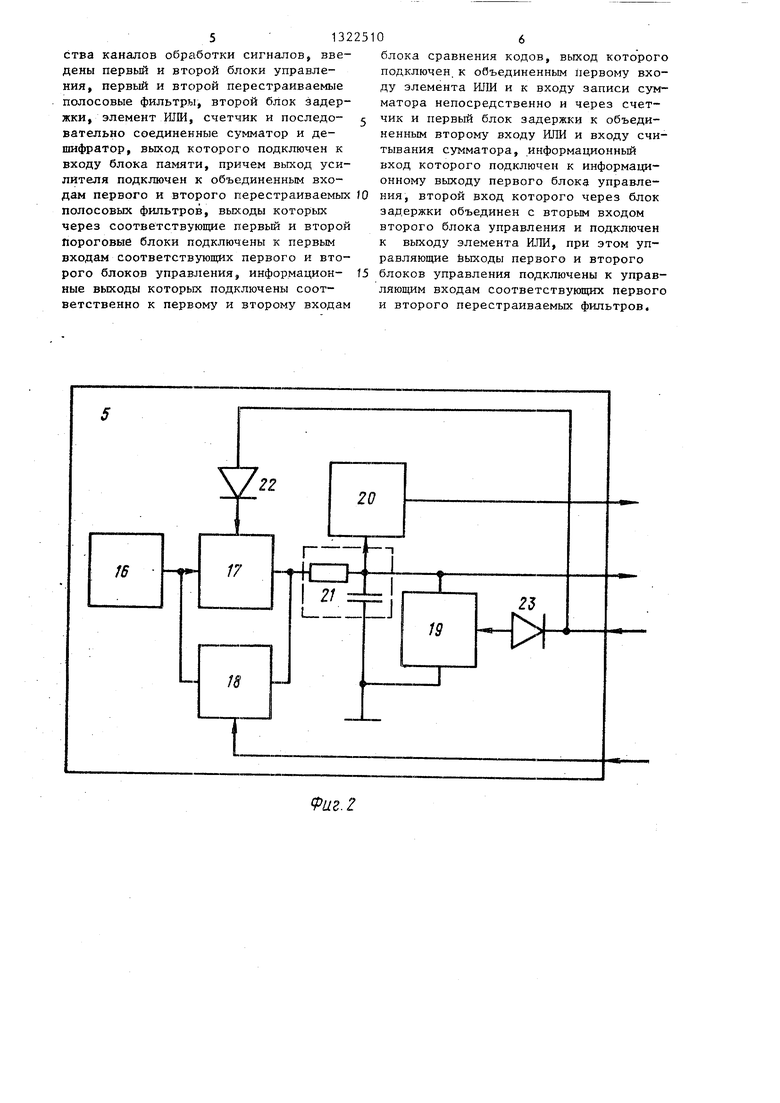

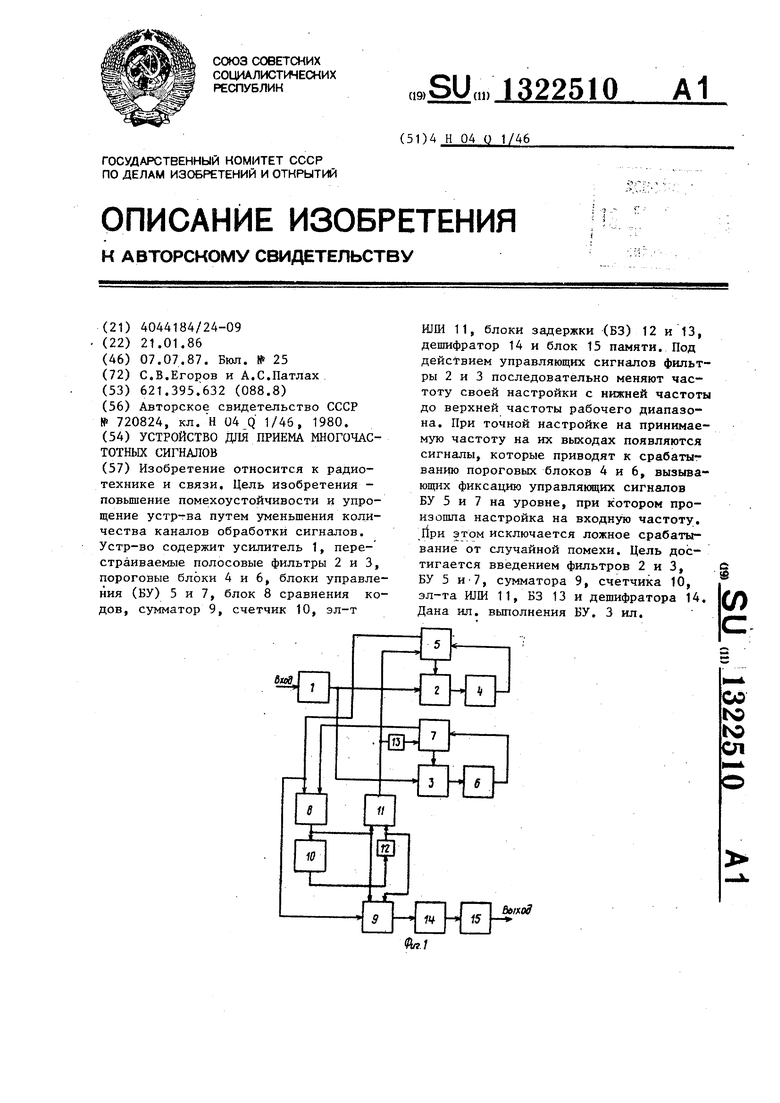

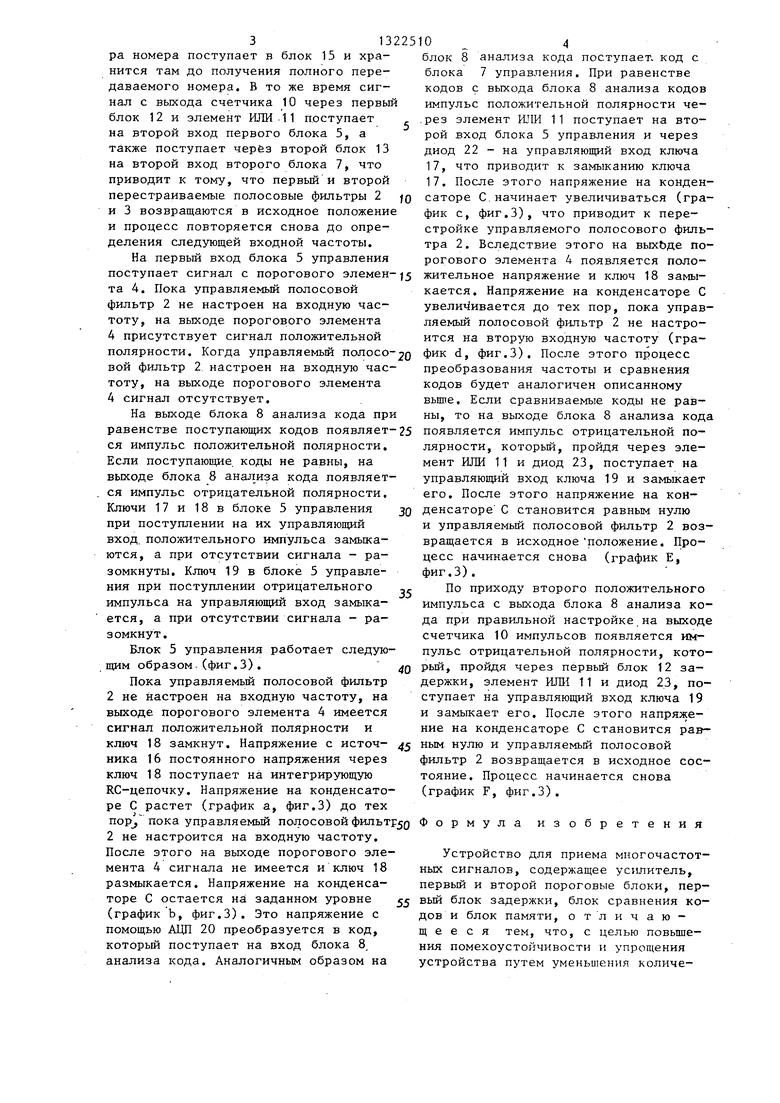

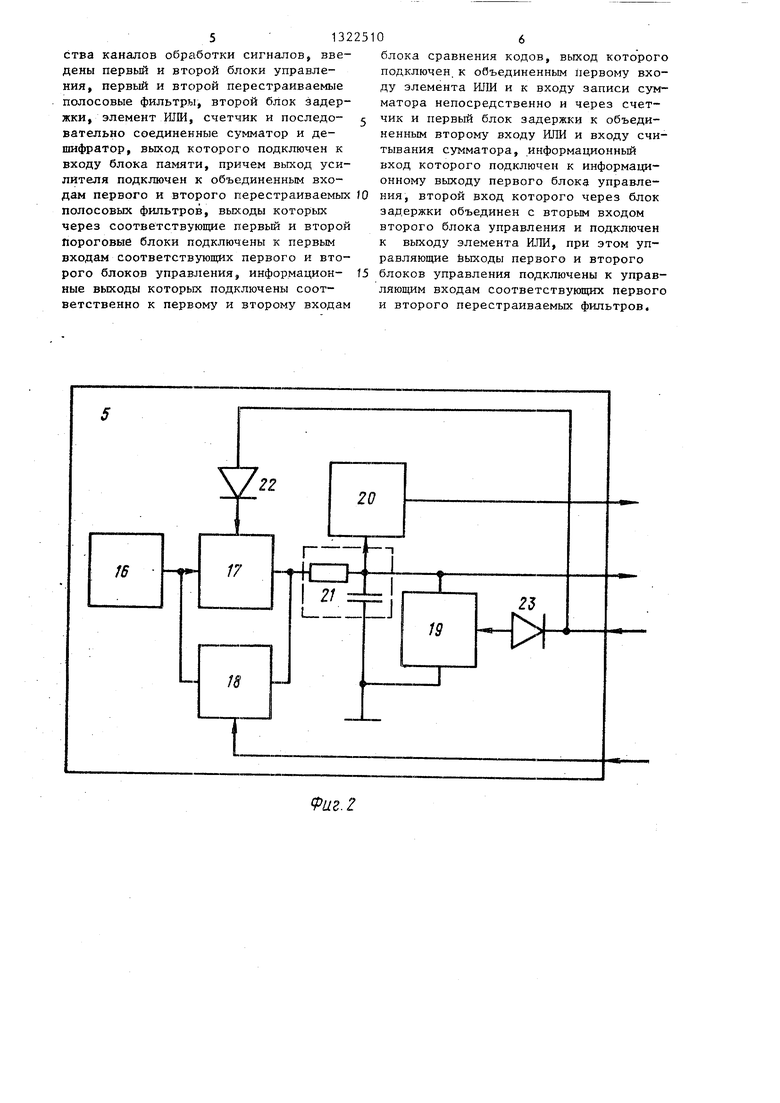

На фиг,1 приведена структурная электрическая схема устройства для приема многочастотных сигналов; на фиг,2 и 3 - схема блока управления и график его работы,

Устройство содержит усилитель 1, первый и второй перастраиваемые полосовые фильтры 2 и 3j первый пороговый блок 4, первый блок 5 управления, второй пороговый блок 6, второй блок 7 управления, блок 8 сравнения кодов, сумматор 9, счетчик 10,, элемент ИЛИ 11, первый и второй блоки 12 к 13 - задержки, дешифратор 14 и блок 15 памяти.

Блок 5 управления содержит источ- ник 16 постоянного напряжения, ключи 17 - 19, аналого-цифровой преобразователь (АЦП) 20 интегрирутощуто КС-цепочку 21 и два диода 22 и 23,

Устройство для приема многочастот- ных сигналов работает следующим образом.

Вводные сигналы принимаются усилителем 1, где усиливаются, и нормируют- ся по амплитуде. На управляющие входы первого и второго перестраиваемых полосовых фильтров 2 и 3 поступают со сдвигом во времени управля1ош;ие сигналы соответственно с первого и второго блоков 5 и 7 управленияэ т.е, второй перестраиваемый полосовой фильтр 3 включается позже, чем первый: перест раиваемый полосоной фильтр 2„ Под действием управляющих сигналов первый и второй перестре иваем ые полосовые фильтры 2 и 3 пос-ледовательно меняют частоту своей настройки с нижней частоты до верхней частоты рабочего диапазона. При точной настройке на при- нимаемую частоту на их выходах появляются сигналы, которые приводят к срабатыванию nepiioro и второго пороговых блоков 4 и 6. Сигналы с их выходов поступают на первые входы пер- вого и второго блоков 5 и 7 управления и вызывают фиксацию управляющих сигналов на ypoBfse, при котором про-- изошла настройка на входную частоту.

С выходов первого и второго блоков 5 и 7 на входы блока 8 поступают коды, соответствующие принимаемой в соответствующем кан;1ле частоте. При этом код с выхода второго блока 7 поступает позже, чем код с выхода первого блока 5, благодаря чему исключается ложное срабатывание от случайной помехи

В блоке 8 производится сравнение кодов, поступаю1цих с первого и второго блоков 5 и 7 управления. При равенстве кодов, т,е, при н-астройке первого и второго перестраивае1У1ых полосовых фильтров 2 и 3 на одну и ту же частоту, на выходе блока 8 появляется сигнаЛд разреаиающий запись кода с выхода первого блока 5 в сум1-ш тор 9, Этот же сигнал через элемент РШИ 11 поступает на второй вход первого блока 5, а через второй блок 13 - на второй вход второго блока 7, после чего на заправляющих выходах первого и второго блоков 5 и 7 управления появляются сдвинутые во времени управляющие сигналы. Благодаря действию этих сигналов первый и второй перестраиваемые полосовые фильтрь 2 и 3 начинают менять частоту своей настройки от определенной уже частрты к верхней границе своего рабочего диапазона. Если кодыд поступающие с выходов первого и второго блоков 5 и 7 управления, не совпадают, то с выхода блока В поступает сигнал запрещающий запись кода с выхода первого блока 5 в сумматор 9, Этот же сигнал через элемент ЮШ 11 поступает на второй вход первого блока З, а через второй блок 13 поступает на второй вход второго блока 7, что приводит к тому, что первый и второй перестраи- полосовые фильтры 2 и 3 возв- раш.аются в исходное положение.

После того, как аналогично описанному вьше, будет определен код второй частоты, этот код поступит в сумматор 9 и сложится с кодом, соответствую- первой частоте,

Счетчик 10 считывает число разрешающих суммирование импульсов с выхода блока 8 и до приходу второго импульса с его выхода выдает сигнал на второй управляющий вход сумматора 9 разрешающий считывание суммарного кода в дешифратор 14, На выходе дешифратора 14 появляется сигнал, определяющий цифру номера, соответствующего паре значений частот. Полученная циф313

pa номера поступает в блок 15 и хранится там до получения полного передаваемого номера. В то же время сигнал с выхода счетчика 10 через первый блок 12 и элемент ИЛИ 11 Поступает на второй вход первого блока 5, а также поступает через второй блок 13 на второй вход второго блока 7, что приводит к тому, что первый и второй перестраиваемые полосовые фильтры 2 и 3 возвращаются в исходное положение и процесс повторяется снова до определения следующей входной частоты.

На первый вход блока 5 управления поступает сигнал с порогового элемента 4. Пока управляемьш полосовой фильтр 2 не настроен на входную частоту, на выходе порогового элемента 4 присутствует сигнал положительной полярности. Когда управляемьй полосовой фильтр 2 настроен на входную частоту, на выходе порогового элемента 4 сигнал отсутствует.

На выходе блока 8 анализа кода при равенстве поступающих кодов появляется импульс положительной полярности. Если поступающие, коды не равны, на выходе блока 8 анализа кода появляется импульс отрицательной полярности. Ключи 17 и 18 в блоке 5 управления при поступлении на их управляющий вход, положительного импульса замыкаются, а при отсутствии сигнала - разомкнуты. Ключ 19 в блоке 5 управления при поступлении отрицательного импульса на управляющий вход замыкается, а при отсутствии сигнала - разомкнут.

Блок 5 управления работает следующим образом (фиг.3).

Пока управляемьй полосовой фильтр 2 не настроен на входную частоту, на выходе порогового элемента 4 имеется сигнал положительной полярности и ключ 18 замкнут. Напряжение с источ- ника 16 постоянного напряжения через ключ 18 поступает на интегрирующую RC-депочку. Напряжение на конденсаторе С растет (график а, фиг.З) до тех пор, пока управляемьш полосовой фильт 2 не настроится на входную частоту. После этого на выходе порогового элемента 4 сигнала не имеется и ключ 18 размыкается. Напряжение на конденсаторе С остается на заданном уровне (график Ь, фиг.З). Это напряжение с помощью АЦП 20 преобразуется в код, который поступает на вход блока 8 анализа кода. Аналогичным образом на

10 4

блок 8 анализа кода поступает, код с блока 7 управления. При равенстве кодов с выхода блока 8 анализа кодов импульс положительной полярности че- .рез элемент ИЛИ 11 поступает на второй вход блока 5 управления и через диод 22 - на управляющий вход ключа 17, что приводит к замыканию ключа 17. После этого напряжение на конденсаторе С.начинает увеличиваться (график с, фиг.З), что приводит к перестройке управляемого полосового фильтра 2. Вследствие этого на вых&де порогового элемента 4 появляется положительное напряжение и ключ 18 замыкается. Напряжение на конденсаторе С увели ивается до тех пор, пока управляемый полосовой фильтр 2 не настроится на вторую входную частоту (график d, фиг.З). После этого процесс преобразования частоты и сравнения кодов будет аналогичен описанному выше. Если сравниваемые коды не равны, то на выходе блока 8 анализа кода появляется импульс отрицательной полярности, которьй, пройдя через элемент ИЛИ 11 и диод 23, поступает на управляющий вход ключа 19 и замыкает его. После этого напряжение на конденсаторе С становится равным нулю и управляемьй полосовой фильтр 2 возвращается в исходное положение. Процесс начинается снова (график Е, фиг.З).

По приходу второго положительного импульса с выхода блока 8 анализа кода при правильной настройке на выходе счетчика 10 импульсов появляется импульс отрицательной полярности, который, пройдя через первьй блок 12 задержки, элемент ИЛИ 11 и диод 23, поступает на управляющий вход ключа 19 и замыкает его. После этого напряжение на конденсаторе С становится равным нулю и управляемьй полосовой фильтр 2 возвращается в исходное состояние. Процесс начинается снова (график F, фиг.З).

Формула изобретения

Устройство для приема многочастот- ных сигналов, содержащее усилитель, первьй и второй пороговые блоки, первый блок задержки, блок сравнения кодов и блок памяти, отличающееся тем, что, с целью повьше- ния помехоустойчивости и упрощения устройства путем уменьшения количе5 132 ства каналов обработки сих налов, введены первый и второй блоки управления, первый и второй перестраиваемые полосовые фильтры, второй блок задержки, элемент И1Ш, счетчик и последо- вательно соединенные сумматор и дешифратор, выход которого подключен к входу блока памяти, причем выход усилителя подключен к объединенным входам первого и второго перестраиваемых полосовых фильтров, вькоды которых через соответствующие первый и второй пороговые блоки подключены к первым входам соответствующих первого и второго блоков управления, информацион- ные выходы которых подключены соответственно к первому и второму входам

06

блока сравнения кодов, выход которого подключен, к объединенным первому входу элемента ШШ и к входу записи сумматора непосредственно и через счетчик и первый блок задержки к объединенным второму входу ИЛИ и входу считывания сумматора, информационный вход которого подключен к информационному выходу первого блока управления, второй вход которого через блок задержки объединен с вторым входом второго блока управления и подключен к выходу элемента И.11И, при этом управляющие Ёыходы первого и второго блоков управления подключены к управляющим входам соответствующих первого и второго перестраиваемых фильтров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема многочастотных сигналов | 1989 |

|

SU1646076A1 |

| Следящий фильтр | 1986 |

|

SU1390779A1 |

| АНАЛИЗАТОР СПЕКТРА | 1989 |

|

RU2007692C1 |

| Установка для акустико-эмиссионного контроля | 1986 |

|

SU1452316A1 |

| Устройство радиоимпульсной автоматической подстройки частоты | 1981 |

|

SU1146799A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для спектрально-временного анализа сигналов | 1989 |

|

SU1711109A1 |

| Ультразвуковой адаптивный дефектоскоп | 1989 |

|

SU1702294A1 |

| Система дистанционного контроля поставки материальных и технических ресурсов для восстановления объектов инфраструктуры | 2020 |

|

RU2734064C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - повьшение помехоустойчивости и упрощение устр-ва путем уменьшения количества каналов обработки сигналов. Устр-во содержит усилитель 1, перестраиваемые полосовые фильтры 2 и 3, пороговые блоки 4 и 6, блоки управления (БУ) 5 и 7, блок 8 сравнения кодов, сумматор 9, счетчик 10, эл-т ШШ 11, блоки задержки (БЗ) 12 и 13, дешифратор 14 и блок 15 памяти. Под действием управляющих сигналов фильтры 2 и 3 последовательно меняют частоту своей настройки с нижней частоты до верхней частоты рабочего диапазона. При точной настройке на принимаемую частоту на их выходах появляются сигналы, которые приводят к срабатыванию пороговых блоков 4 и 6, вызывающих фиксацию управлякщих сигналов БУ 5 и 7 на уровне, при котором произошла настройка на входную частоту. Йри этом исключается ложное срабатывание от случайной помехи. Цель достигается введением фильтров 2 и 3, БУ 5 и-7, сумматора 9, счетчика 10, эл-та ШШ 11, БЗ 13 и дешифратора 14. Дана ил. выполнения БУ. 3 ил. СЛ СО to ю СП Bofxoff

9иг.2

Фиг.

Редактор Е.Папп

Составитель В.Шевцов

Техред л.Олийнык Корректор Л.Пилнпенко

Заказ 2880/57Тираж 638 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для приема многочастотных сигналов | 1978 |

|

SU720824A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-07—Публикация

1986-01-21—Подача