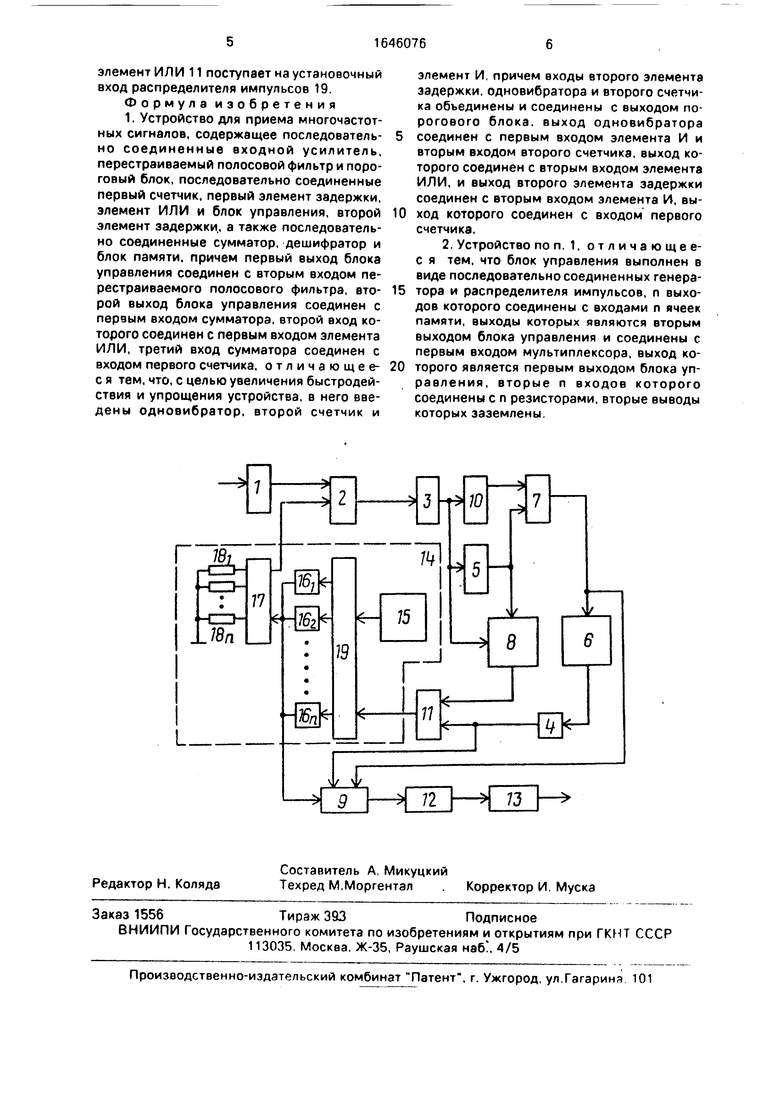

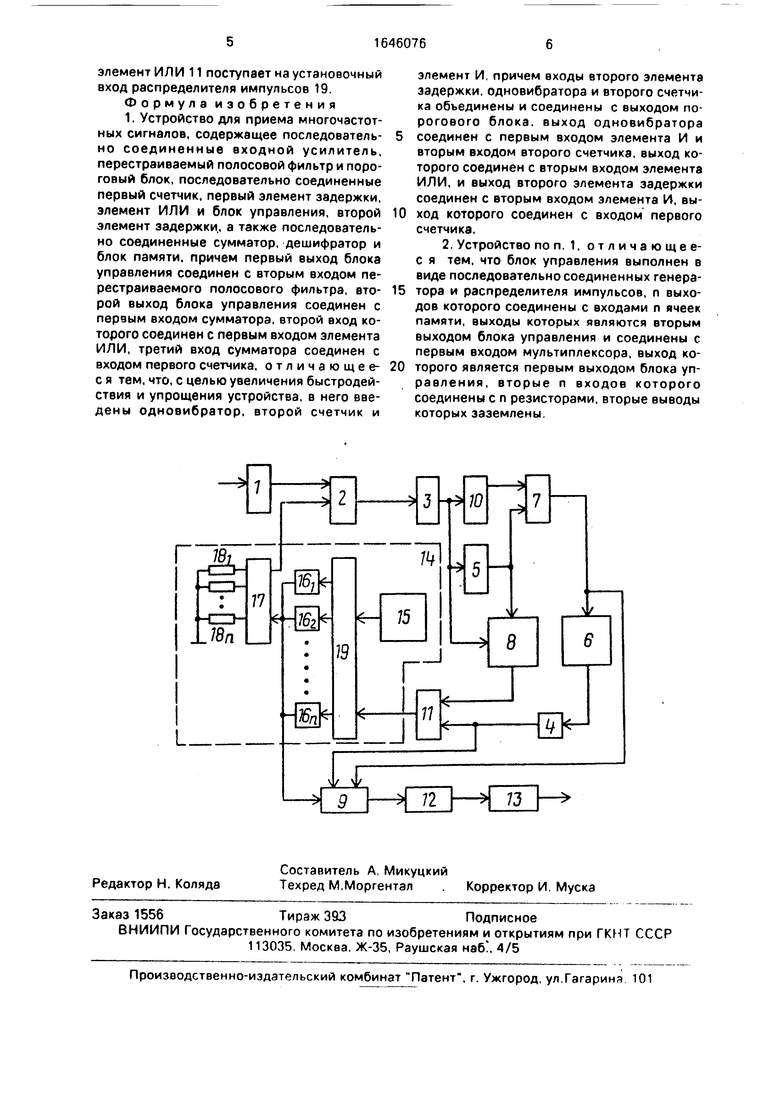

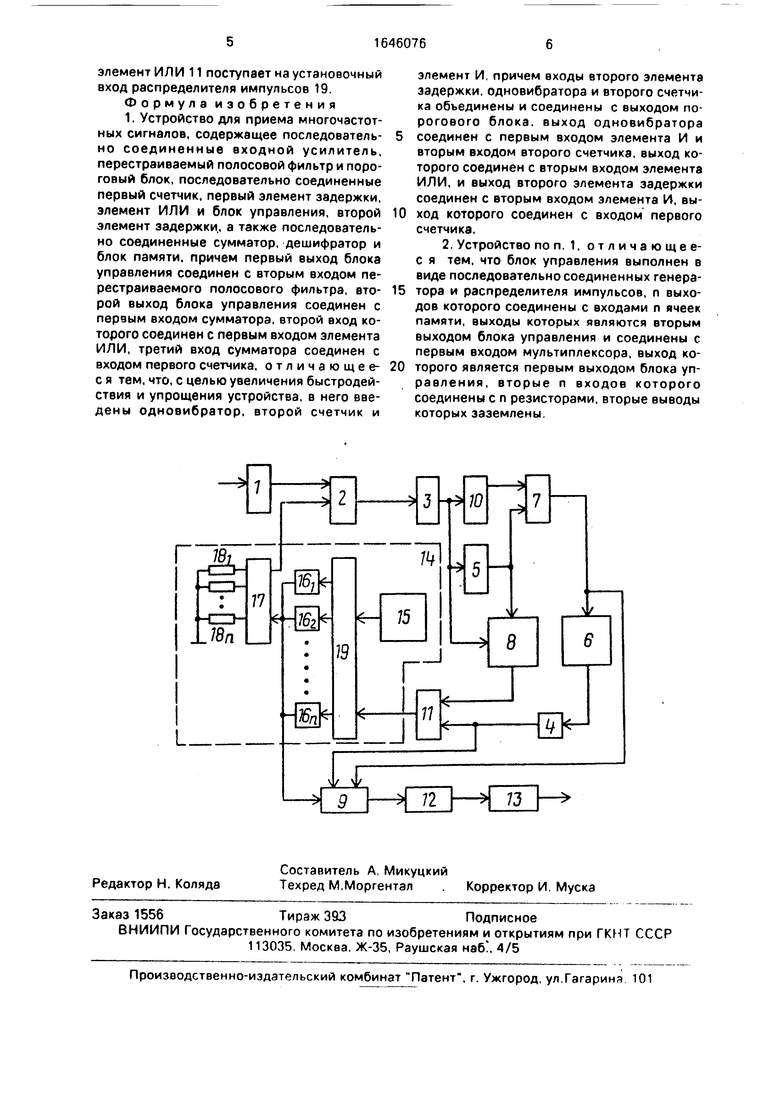

19. Длительность сигнала с выхода генератора 15 равна 1,5 периода нижней входной частоты из ряда частот, принимаемых устройством. Под действием этих сигналов на выходах распределителя импульсов 19 поочередно появляются сигналы на время, рав- ное 1.5 периода нижней частоты, принимаемой устройством, и поочередно поступают на входы разрешения считывания ячеек памяти 16i,..16n, благодаря чему на выходах ячеек 16i...16n поочередно появляются кодовые сигналы, соответствующие дискретному ряду частот, принимаемых устройством. При поступлении сигнала на ус- тановочный вход распределителя импульсов он устанавливается о начальное состояние. Ко до оме сииплы нп выходах ячеек памяти 16i...16n дискретно появляются в возрастающем порядке, т. е. от значения кодового сигнала, соответствующего нижней частоте, принимаемой устройством, к значению кодового сигнала, соответствующего верхней частоте, принимаемой устройством. Кодовые сигналы с ячеек памяти 16i...16n дискретно поступают на управляющий вход мультиплексора 17. Под действием этих сигналов выход мультиплексора 17 поочередно подключается к резисторам 18i...18n. Благодаря этому будет меняться частота пропускания перестраиваемого полосового фильтра 2. Частота пропускания фильтра 2 будет меняться дискретно, в возрастающем порядке, т. е. от нижней частоты, принимаемой устройством, к верхней частоте, принимаемой устройством.

При совпадении резонансной частоты фильтра 2 и входной частоты на выходе фильтра 2 появляется сигнал, который приводит к срабатыванию порогового блока 3. Сигнал с выхода порогового блока 3, который будет присутствовать в течение времени, равного (1.5...1) периода нижней частоты, поступает на информационный вход второго счетчика 8, через второй блок задержки 10 на первый вход элемента И 7 и запускает одновибратор 5. Время задержки второго блока задержки 10 равно времени срабатывания одновибратора 5. Одновибратор 5 формирует инверсный по отношению к выходному сигналу порогового блока 3 импульс, длительность которого равна 0,5 периода нижней частоты, принимаемой устройством. Одновибратор 5 и второй счетчик 8 служат для защиты устройства от действия импульсных помех. Предположим, что одиночный импульс вызовет срабатывание порогового блока 3, после чего произойдет запуск одновибратора 5. Импульс с выхода одновибратора 5 поступает нэ второй вход элемента И 7 и на время, равное

0,5 периода нижней частоты, блокирует дальнейшее прохождение сигнала с выхода порогового блока 3 через элемент Ц7. После окончания действия импульса с вывода одновибратора 5 на выходе порогового блока 3 сигнала, вызванного одиночным импульсом, уже не будет, а значит, не будет сигнала на выходе элемента И 7, и ложная информация не поступит на выход устройства.

0 Предположим, что помеха состоит из нескольких импульсов, и поэтому на выходе порогового блока 3 сигнал будет появляться столько раз, сколько импульсов в помехе. Второй счетчик 8 считает число импульсов с

5 выхода порогового блока 3 и после прихода второго импульса выдает сигнал, который, пройдя через элемент ИЛИ 11, поступает на установочный вход распределителя импульсов 19, устанавливая его в начальное поло0 жение, и процесс поиска входной частоты начинается сначала. Таким образом, действия импульсных помех не вызывают ложного срабатывания устройства.

Если на вход устройства поступает ра5 бочая частота, то после окончания действия импульса с выхода одновибратора 5 на выходе порогового блока 3 еще будет присутствовать сигнал, который через элемент И 7 поступает на вход разрешения записи сум0 мэтора 9, и в сумматоре 9 из соответствующей ячейки памяти 16i...16n записывается кодовый сигнал, соответствующий входной частоте. Передним фронтом с выхода одно- вибратора 5 производится установка второ5 го счетчика 8 в начальное состояние. Это необходимо для того, чтобы второй счетчик 8 не сработал при приеме второй рабочей частоты.

После того как аналогично описанному

0 выше произойдет настройка на вторую частоту, кодовый сигнал, соответствующий второй частоте, поступит в сумматор 9 и сложится с кодовым сигналом, соответствующим первой принятой частоте.

5 Первый счетчик 6 считает число разрешающих суммирование импульсов с выхода элемента И 7 и по приходу второго импульса с выхода элемента И 7 выдает сигнал, который через первый блок задержки 4 поступа0 ет на вход разрешения считывания сумматора 9, разрешая считывания суммарного кодового сигнала в дешифратор 12. На выходе дешифратора 13 появляется сигнал, определяющий цифру передаваемого номе5 ра, соответствующую паре принятых входных частот. Полученная цифра номера поступает в блок памяти 13 и хранится там до получения полного передаваемого номера. В то же время сигнал с выхода первого счетчика 6 через первый блок задержки 4 и

элемент ИЛИ 11 поступает на установочный вход распределителя импульсов 19. Формула изобретения 1. Устройство для приема многочастотных сигналов, содержащее последовательно соединенные входной усилитель, перестраиваемый полосовой фильтр и пороговый блок, последовательно соединенные первый счетчик, первый элемент задержки, элемент ИЛИ и блок управления, второй элемент задержки., а также последовательно соединенные сумматор, дешифратор и блок памяти, причем первый выход блока управления соединен с вторым входом перестраиваемого полосового фильтра, второй выход блока управления соединен с первым входом сумматора, второй вход которого соединен с первым входом элемента ИЛИ, третий вход сумматора соединен с входом первого счетчика, отличающее- с я тем, что, с целью увеличения быстродействия и упрощения устройства, в него введены одновибратор, второй счетчик и

элемент И, причем входы второго элемента задержки, одновибратора и второго счетчика объединены и соединены с выходом порогового блока, выход одновибратора

соединен с первым входом элемента И и вторым входом второго счетчика, выход которого соединен с вторым входом элемента ИЛИ, и выход второго элемента задержки соединен с вторым входом элемента И, выход которого соединен с входом первого счетчика.

2. Устройство по п. 1. отличающее- с я тем. что блок управления выполнен в виде последовательно соединенных генератора и распределителя импульсов, п выходов которого соединены с входами п ячеек памяти, выходы которых являются вторым выходом блока управления и соединены с первым входом мультиплексора, выход которого является первым выходом блока управления, вторые п входов которого соединены с п резисторами, вторые выводы которых заземлены.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема многочастотных сигналов | 1989 |

|

SU1601782A1 |

| Устройство для приема многочастотных сигналов | 1986 |

|

SU1322510A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Устройство для автоматической компенсации погрешности измерительного канала | 1989 |

|

SU1675853A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

Авторы

Даты

1991-04-30—Публикация

1989-02-27—Подача