Изобретение относится к вычислительной технике.

Цель изобретения - расширение диапазона области применения за счет увеличения диапазона разности сравниваемых чисел.

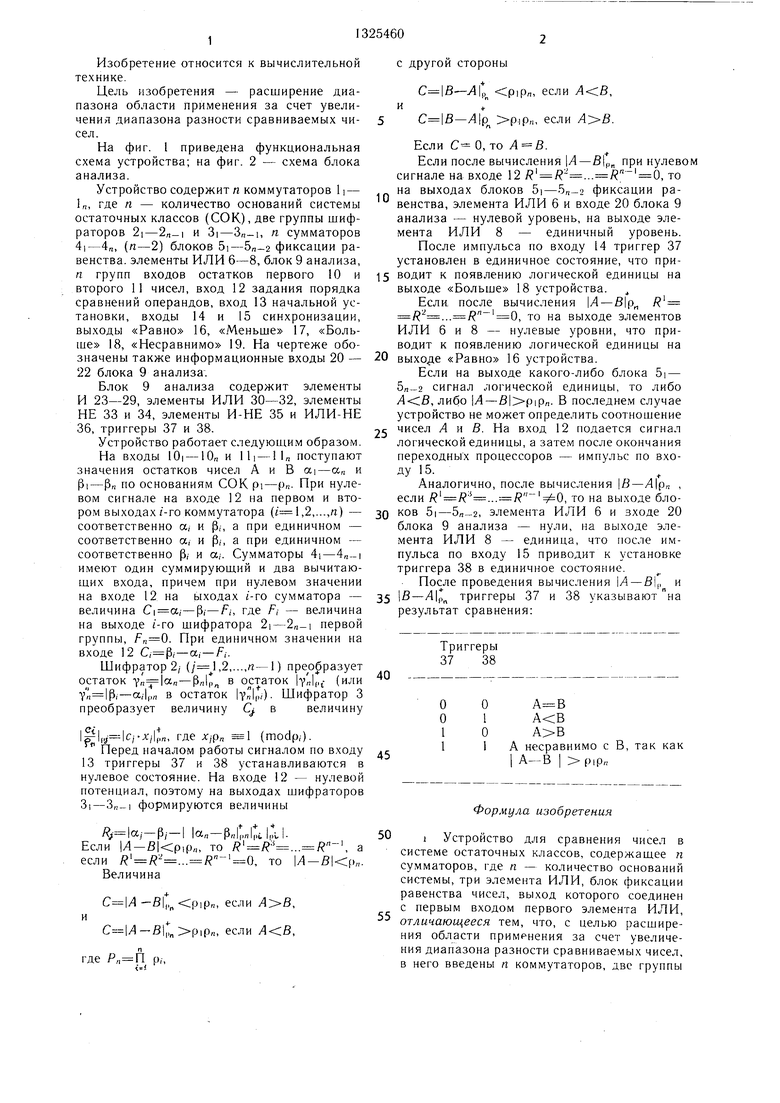

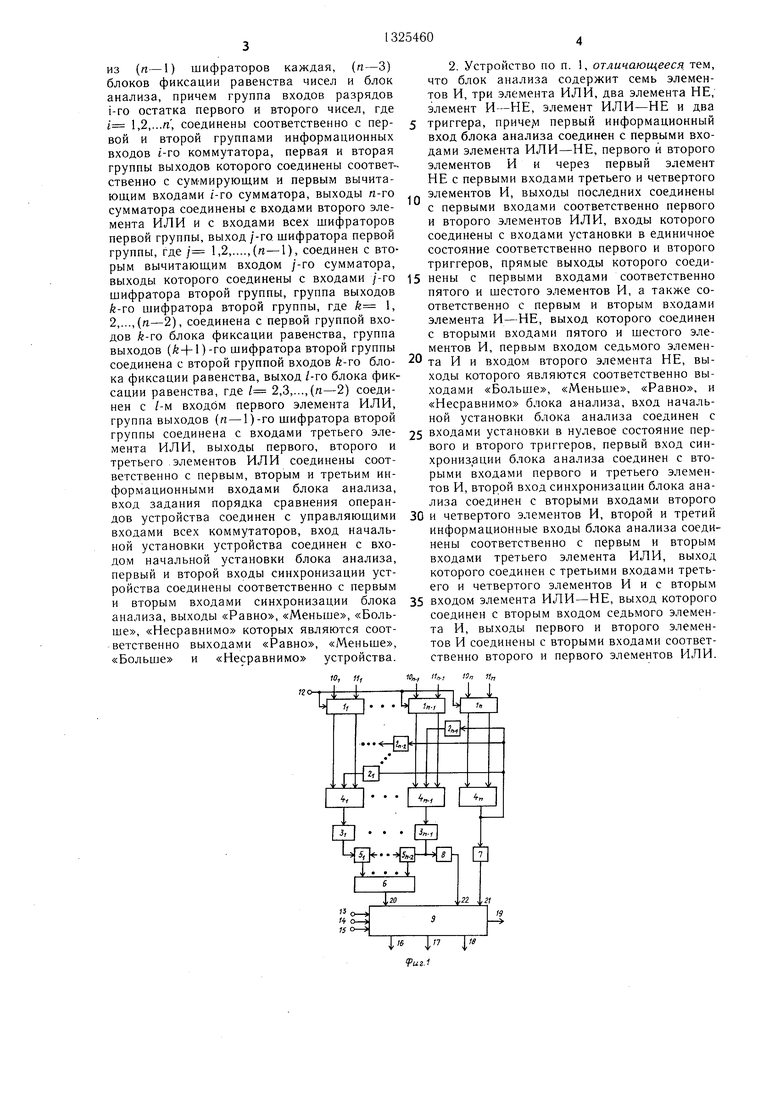

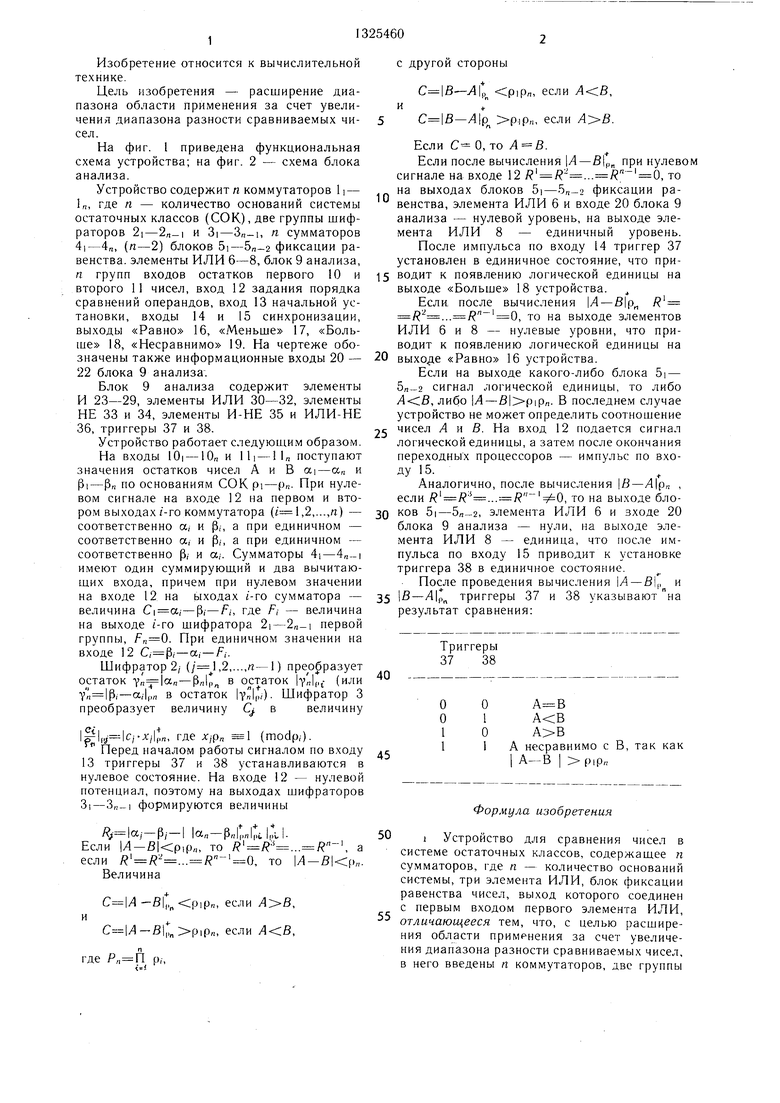

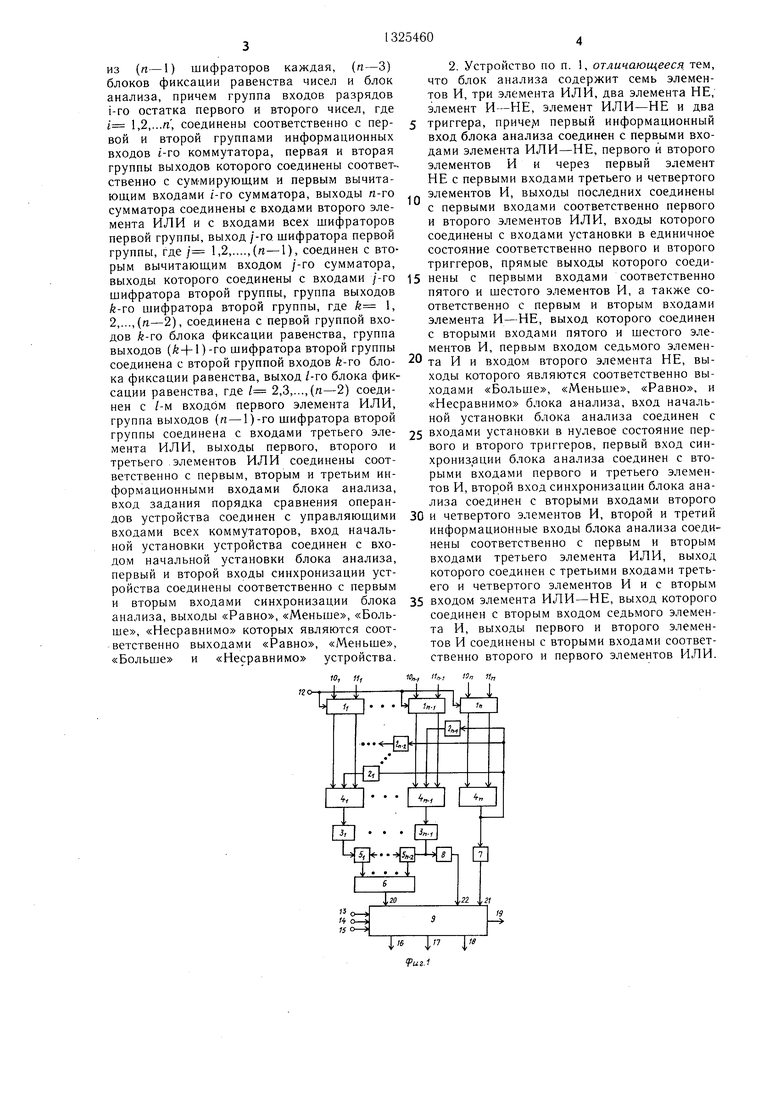

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема блока анализа.

Устройство содержит п коммутаторов 11 - п, где п - количество оснований системы остаточных классов (СОК), две группы шифраторов 2i-2n-i и 3|-3„ 1, п сумматоров 4i-4„, (п-2) блоков 5i-5п-2 фиксации равенства, элементы ИЛИ 6-8, блок 9 анализа, п групп входов остатков первого 10 и второго 11 чисел, вход 12 задания порядка сравнений операндов, вход 13 начальной установки, входы 14 и 15 синхронизации, выходы «Равно 16, «Меньше 17, «Больше 18, «Несравнимо 19. На чертеже обозначены также информационные входы 20 - 22 блока 9 анализа.

Блок 9 анализа содержит элементы И 23-29, элементы ИЛИ 30-32, элементы НЕ 33 и 34, элементы И-НЕ 35 и ИЛИ-НЕ 36, триггеры 37 и 38.

Устройство работает следующим образом.

На входы 10| -10п и lli -11„ поступают значения остатков чисел А и В oci-а„ и р|-РП по основаниям СОК pi-р«. При нулевом сигнале на входе 12 на первом и втором выходах :-го коммутатора (г 1,2,...,п) - соответственно а, и р,, а при единичном - соответственно а, и р/, а при единичном - соответственно р/ и а/. Сумматоры 4i-4„.| имеют один суммируюший и два вычитающих входа, причем при нулевом значении на входе 12 на ыходах г -го сумматора - величина ,--р,-f/, где f,- - величина на выходе г -го шифратора 2i-2„ 1 первой группы, . При единичном значении на входе 12 С,р,-а,-f,-.

Шифратор 2/ (,2,...,п-1) преобразует остаток ,г -pnlj в остаток Iv ilpt (или .-a;l(,/i в остаток ). Шифратор 3 преобразует величину Q в величину

(.}- Cj-Xjln, где 1 (modp,-).

Перед началом работы сигналом по входу 13 триггеры 37 и 38 устанавливаются в нулевое состояние. На входе 12 - нулевой потенциал, поэтому на ВЕЯходах шифраторов 3|-3„ | формируются величины

,- | |а„-р„|р„|рс1е1 Если ,р,„ то ..., а если ..., то .

Величина

, если , и

, если ,

П

где р,-.

с другой стороны

pipn, если , и

С |В-Л|р р|р,ь если .

Если С О, то Л Б.

Если после вычисления А-B,„ при нулевом сигнале на входе 12 ... 0, то на выходах блоков 5i-5„-2 фиксации равенства, элемента ИЛИ 6 и входе 20 блока 9 анализа - нулевой уровень, на выходе элемента ИЛИ 8 - единичный уровень.

После импульса по входу 14 триггер 37 установлен в единичное состояние, что при- 5 водит к появлению логической единицы на выходе «Больще 18 устройства. ,

Если, после вычисления А-Б|р„ /..., то на выходе элементов ИЛИ 6 и 8 - нулевые уровни, что приводит к появлению логической единицы на 0 выходе «Равно 16 устройства.

Если на выходе какого-либо блока 5i - 5л--2 сигнал логической единицы, то либо , либо . В последнем случае устройство не .может определить соотношение чисел А и В. На вход 12 подается сигнал логической единицы, а затем после окончания переходных процессоров - импульс по входу 15.

Аналогично, после вычисления |В-Л|р , если ..., то на выходе блоков 5|-5п-2, элемента ИЛИ 6 и входе 20 блока 9 анализа - нули, на выходе элемента ИЛИ 8 - единица, что после импульса по входу 15 приводит к установке триггера 38 в единичное состояние.

После проведения вычисления И -В,, и 5 IB-/1|р триггеры 37 и 38 указывают на результат сравнения:

5

0

Триггеры 37 38

О О 1 1

О 1 О

А несравнимо с В, так как 1 А-В I pip,,

Формула изобретения

I Устройство для сравнения чисел в системе остаточных классов, содержащее п сумматоров, где п - количество оснований системы, три элемента ИЛИ, блок фиксации равенства чисел, выход которого соединен с первым входом первого элемента ИЛИ, тличающееся тем, что, с целью расширения области применения за счет увеличения диапазона разности сравниваемых чисел, в него введены п коммутаторов, две группы

из (п-1) шифраторов каждая, (п-3) блоков фиксации равенства чисел и блок анализа, причем группа входов разрядов i-ro остатка первого и второго чисел, где i 1,2,...« , соединены соответственно с первой и второй группами информационных входов t-ro коммутатора, первая и вторая группы выходов которого соединены соответственно с суМ Мирующим и первым вычитающим входами /-ГО сумматора, выходы п-го сумматора соединены с входами второго элемента ИЛИ и с входами всех шифраторов первой группы, выход/-го шифратора первой группы, где / 1,2,(п-1), соединен с вторым вычитающим входом /-го сумматора, выходы которого соединены с входами /-го шифратора второй группы, группа выходов k-ro шифратора второй группы, где k 1, 2,..., (п.-2), соединена с первой группой входов -го блока фиксации равенства, группа выходов ()-ro шифратора второй группы соединена с второй группой входов fe-ro блока фиксации равенства, выход 1-го блока фиксации равенства, где / 2,3,...,(п-2) соединен с /-М входом первого элемента ИЛИ, группа выходов (п-1)-го шифратора второй группы соединена с входами третьего элемента ИЛИ, выходы первого, второго и третьего элементов ИЛИ соединены соответственно с первым, вторым и третьим информационными входами блока анализа, вход задания порядка сравнения операндов устройства соединен с управляющими входами всех коммутаторов, вход начальной установки устройства соединен с входом начальной установки блока анализа, первый и второй входы синхронизации устройства соединены соответственно с первым и вторым входами синхронизации блока анализа, выходы «Равно, «Меньше, «Больше, «Несравнимо которых являются соответственно выходами «Равно, «Меньше, «Больше и «Несравнимо устройства.

0

2. Устройство по п. , отличающееся тем, что блок анализа содержит семь элементов И, три элемента ИЛИ, два элемента НЕ, элемент И-НЕ, элемент ИЛИ-НЕ и два триггера, приче и первый информационный вход блока анализа соединен с первыми входами элемента ИЛИ-НЕ, первого и второго элементов И и через первый элемент НЕ с первыми входами третьего и четвертого элементов И, выходы последних соединены с первыми входами соответственно первого и второго элементов ИЛИ, входы которого соединены с входами установки в единичное состояние соответственно первого и второго триггеров, прямые выходы которого соеди5 нены с первыми входами соответственно пятого и шестого элементов И, а также соответственно с первым и вторым входами элемента И-НЕ, выход которого соединен с вторыми входами пятого и шестого элементов И, первым входом седьмого элемен0 та И и входом второго элемента НЕ, выходы которого являются соответственно выходами «Больше, «Меньше, «Равно, и «Несравнимо блока анализа, вход начальной установки блока анализа соединен с

5 входами установки в нулевое состояние первого и второго триггеров, первый вход синхронизации блока анализа соединен с вторыми входами первого и третьего элементов И, второй вход синхронизации блока анализа соединен с вторыми входами второго

0 и четвертого элементов И, второй и третий информационные входы блока анализа соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с третьими входами третьего и четвертого элементов И и с вторым

5 входом элемента ИЛИ-НЕ, выход которого соединен с вторым входом седьмого элемента И, выходы первого и второго элементов И соединены с вторыми входами соответственно второго и первого элементов ИЛИ.

10, п,

/го

i « I -f 1

fu2.

Фиг. г

1 W

jvi

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для выбора упорядоченной последовательности данных | 1984 |

|

SU1218381A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1737441A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1394214A1 |

| Арифметическое устройство вычислительной машины для расчета ткани | 1974 |

|

SU518767A1 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

Изобретение относится к вычислительной тетхнике. Цель изобретения - расширение диапазона возможной разности сравниваемых чисел. Устройство содержит п (по числу оснований системы остаточных классов) коммутаторов и сумматоров, 2п-2 шифраторов, (п-2) блоков фиксации равенства, элементы ИЛИ и блок анализа, содержащий триггеры, элементы И, ИЛИ, НЕ, ИЛИ-НЕ, И-НЕ. Остатки «i-а„ и PI-рп сравниваемых чисел А и В поступают на входы устройства, затем последовательно вычисляются разности |А-В| в СОК {pi, рг р„-.} и |В-AIX- Блок анализа фиксирует случаи , , либо случаи, когда устройство не может сравнивать А и В, поскольку |А-В| р1р„. 1 з.п.ф-лы, 2 ил. (Л 00 N5 СЛ 4 О5

| Устройство для сравнения чисел, выраженных в системе остаточных классов | 1976 |

|

SU608155A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Акушский И | |||

| Я., Бурцев В | |||

| М., Пак И | |||

| Т | |||

| О новой позиционной характеристике непозиционного кода и ее применении-В кн.: Теория кодирования и оптимизация сложных систем.-Алма-Ата: Наука, с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1979 |

|

SU873237A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-03—Подача