дов схемы сравнения, первый и второй выходы которой соединены соответственно с нулевым входом последнего триггера группы и вторым входом второго элемента ИЛИ блока управления, вторые входы элементов И первой группы которого соединены соответственно с выходами схем сравнения группы, кроме первой, выходы

позиционного сумматора соединены с второй группой входов схемы сравнения, управляющие входы схемы сравнения, позиционного сумматора и схем сравнения группы соединены с входом Режим преобразователя, выходы сумматоров по модулю группы являются выходом кода системы остаточных классов преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь чисел из модулярного кода в позиционный код | 1987 |

|

SU1481898A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1981 |

|

SU991410A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

ОБРАТИМЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ КОДОВ В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ, содержащий группу сумматоров по модулю, позиционный сумматор, группу .схем сравнения и блок управления, содержащий группу триггеров, первую группу элементов И и первый элемент ИЛИ, причем единичные выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, выход последнего из которых соединен с первым входом первого элемента ШШ, выходы сумматоров по модулю группы соединены с первыми группами входов соответствующих схем сравнения группы, вторые группы входов которых являются входами остатков по модулям преобразователя, выход позиционного сумматора является выходом двоичного кода преобразователя, выход первой схемы сра&нения группы соединен с единичным входом первого триггера группы блока управл1ения, отличающийс я тем, что, с целью повышения быстродействия, в него введены шифратор и схема сравнения, а блок управления содержит вторую группу элементов И, группу элементов задержки, триггер, элемент И и второй элемент ИЛИ, причем нулевые выходы триггеров группы соединены через соответствующие элементы задержки группы с первыми входами соответствующих элементов И второй группы, вторые входы которых соединены с нулевым входом последнего триггера группы, нулевые входы триггеров группЫ; кроме последнего, соединены соответственно с выходами элементов И второй группы, кроме первого, выход которого соединен с вторым входом первого элемента сл ИЛИ, выход которого соединен с нулевым входом триггера, выход которого соединен с первым входом элемента И. второй вход которого соединен с вы ходом второго элемента ИЛИ, выходы . элементов И, кроме последнего, первой группы соединены соответственно с единичными входами триггеров группы, кроме первого, входы Пуск, Режим и тактовый вход преобразователя соесо динены соответственно с единичным входом триггера, первым входом втоэо рого элемента ИЛИ и третьим входом элемента И блока управления, выходы элемента И и триггеров группы которого соединены соответственно с тактовыми входами сумматоров по модулю группы и позиционного сумматора и соответствующими входами шифратора, выходы которого подключены соответ-. ственно к информационным входам сумматоров по модулю группы, позиционного сумматора и первой группе вхо

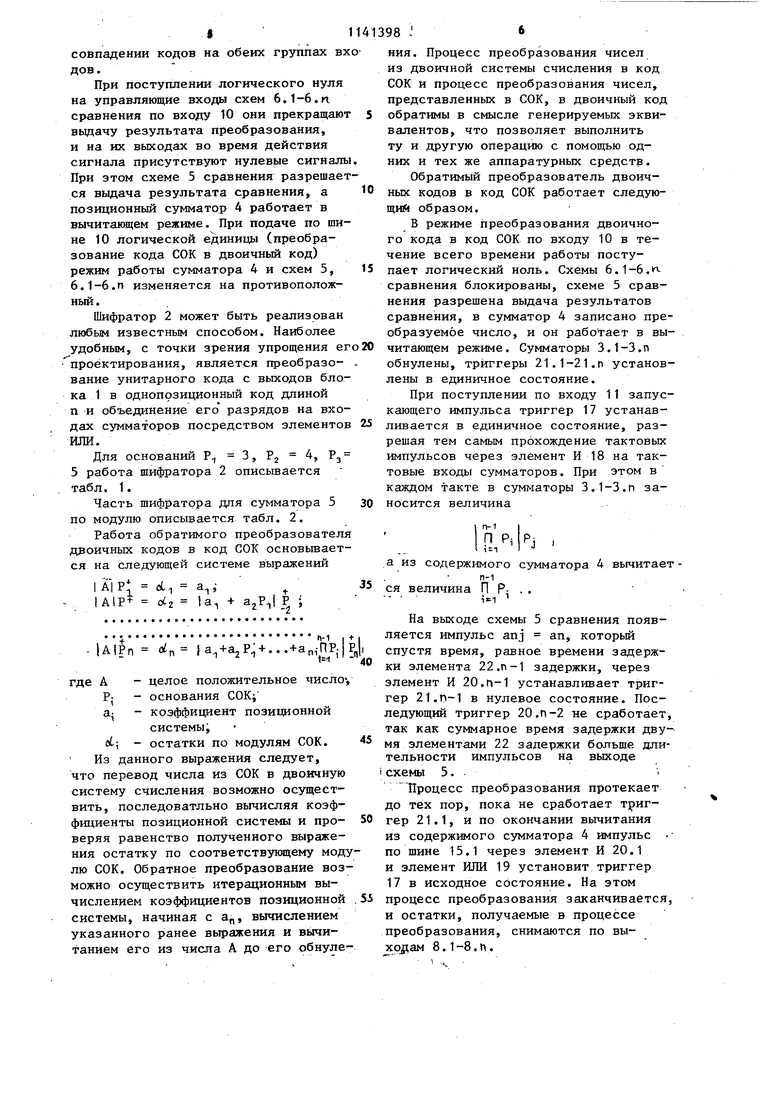

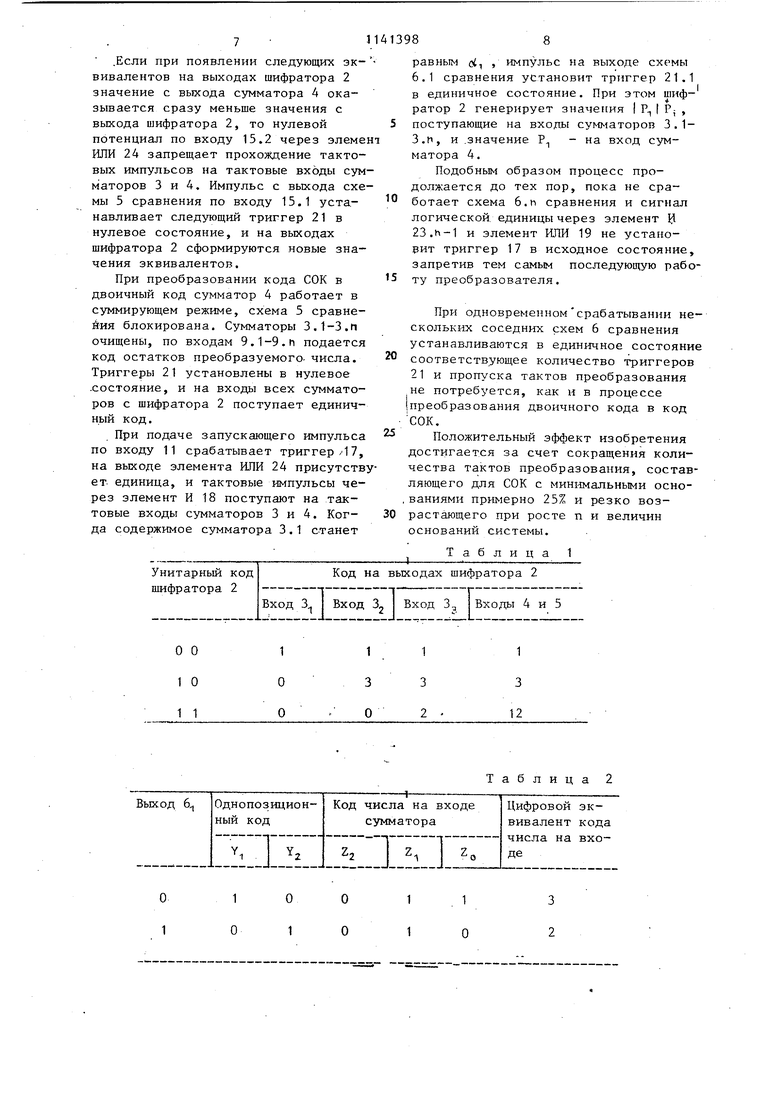

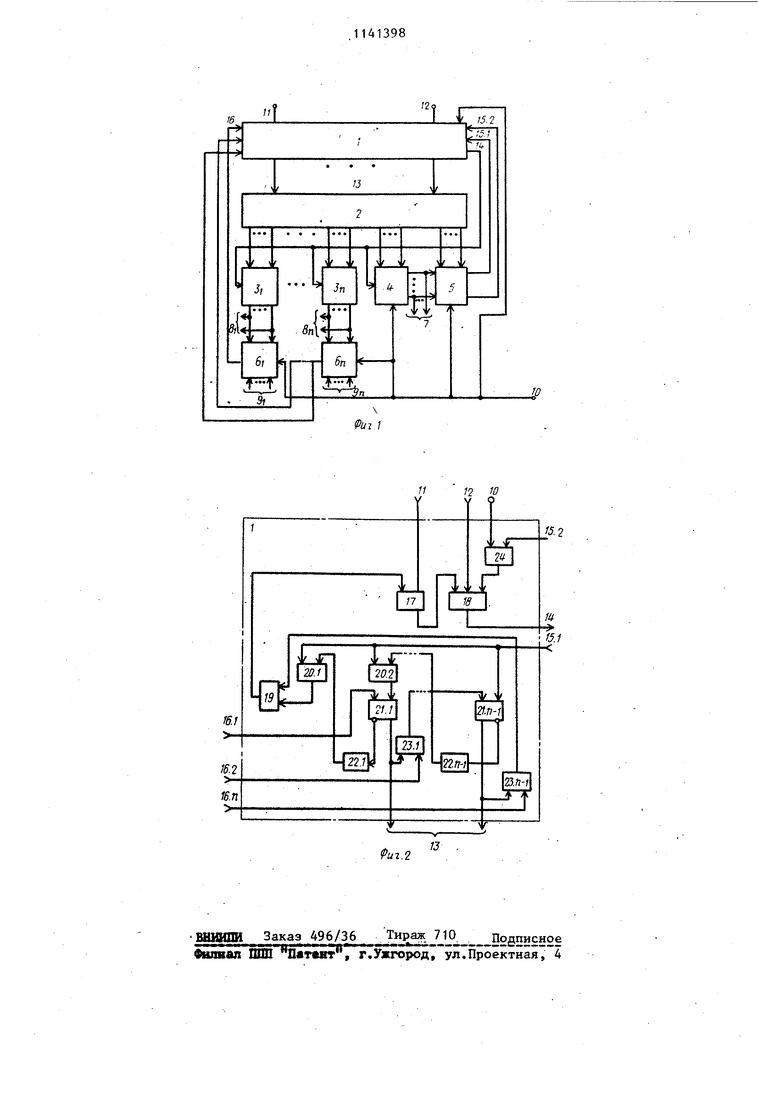

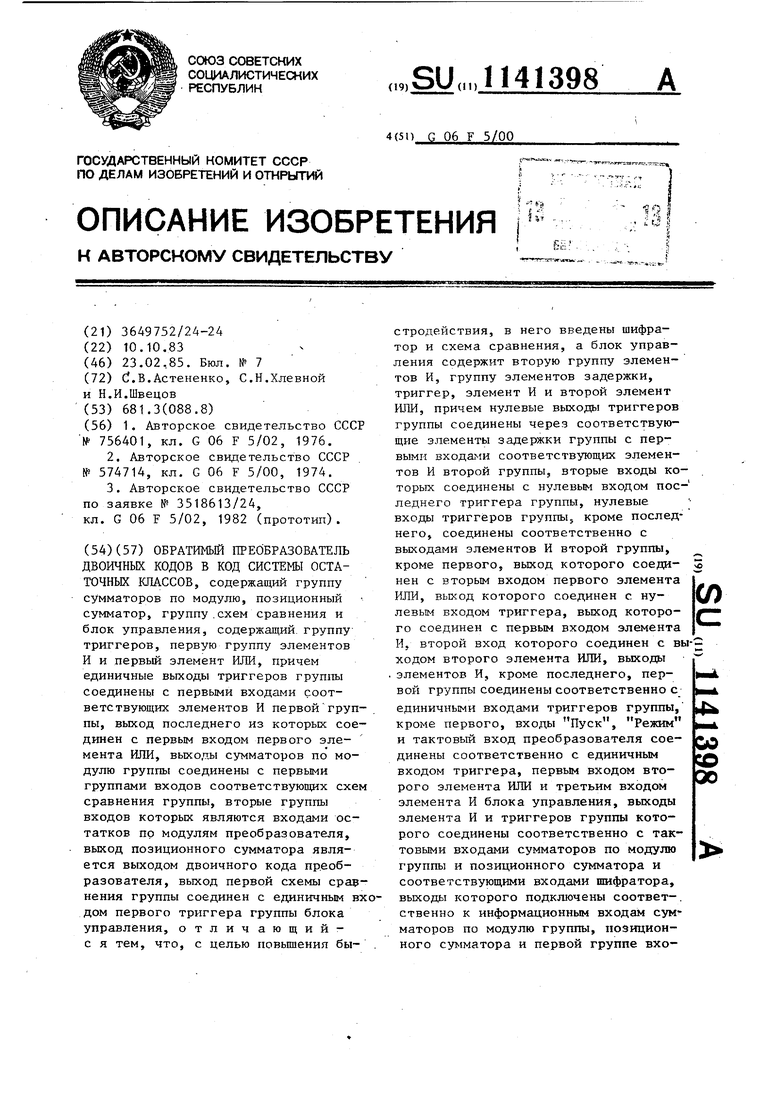

, 1 Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вывода цифровых вычислительных машин, систем телекодовой связи, в цифровых измерительных устрйоствах, функционирующих в системе остаточных классов (СОК)-. Известно устройство дпя прямого и обратного преобразования чисел кода СОК в двоичный код, содержащее реверсивные счетчики, дешифраторы нуля переключатель, триггер и элементы И СП. Недостатком данного устройства является низкое быстродействие. Известно также устройство для прямого и обратного преобразования чисел из кода СОК в двоичный код, содержащее ( h + 1) счетчиков (и - число оснований системы остаточных клас сов), выходы которьк со.единены с пер вьми входами (п + 1) элементов сравнения, другие входы которых подключе ны к выходам (h+ 1) регистров, выход первого элемента сравнения - к одному входу переключателя, другой вход, -которого подключен к выходу мно говходовЬго элемента И, входы которо го подключены к выходам других элементов сравнения, входы счетчиков подключены к выходу другого элемента И, входы которого соединены с тактовой шиной и выходом триггера, входы которого подключены к шине пуска и выходу переключателя {.21. Недостатком указанного устройства является низкое быстродействие. Наиболее близким по технической сущности к изобретению является преобразователь, содержащий группу входных регистров, группу элементов сравнения, группу элементов И, группу счетчиков по модулю, позиционный сумматор, коммутатор, группу триггеров, элемент ИЛИ, причем входы счетчиков группы соединены соответственно с выходами элементов И, первые входы которых соединены с тактовым входом преобразователя, информационные входы которого соединены.с входами регистров группы, выходы которых соединены с первыми входами соответствующих элементов сравнения группы., вторые входы которьк соединены с выходами соответствующих счетчиков по модулю группы, выходы позиционного сумматора являются выходами преобразователя, вхрды констант эквивалентов которого соединены с информационными входами коммутатора, выходы которого соединены с информационными входами позиционного сумматора, управляющий вход . которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы, вторые входы которых соединены с выходами соответствующих триггеров группы и управляющими входами коммутатора, выход |с-го элемента сравнения группы (Х 1-п где п- число оснований) соединен с нулевым входом 1с-го и единичным входом ( In + 1)-го тоигге- . ра группы, единичный вход первого триггера является входом пуска преобразователя Сз. Недостатки известного преобразователя - низкое быстродействие, а также невозможность выполнения преобразования из позиционного код СОК. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем что в обратимый преобразователь двоичных кодов в код системы остаточных классов, содержащий группу сумматоров- по модулю, позиционный сумматор, группу схем сравнения и блок управления, содержащий группу триггеров, первую группу элементов И, первый элемент ИЛИ, причем единичные выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, выход последнего из которых соединен с первым входом первого элемента ИЛИ, выходы сумматоров по модулю группы с первыми группами входов соответствующих схем сравнения группы, вторые группы входов которых являются входами остатков по модулям преобразователя, выход позиционного сумматора - выходом двоичного кода преобразователя, выход первой схемы срарнения группы соединен с единичным входом первого триггера группы блока уп равления, введены шифратор и схема сравнения, а блок управления содержи вторую группу элементов И, группу элементов задержки, триггер, элемент И и второй элемент ИДИ, причем нулевые выходы.триггеров группы соединен через соответствующие элементы задержки 1руппы с первыми входами срответствующих элементов И второй груп-/ пы, вторые входы.которых соединены с нулевым входом последнего триггера группы, нулевые входы триггеров груп пы, кроме последнего,- соответственно с вбкодами элементов И второй гру пы, кроме первого, выход которого соединен с вторым входом первого эле мента ИЛИ, выход которого соединен с нулевым входом триггера, вькод которого соединен с первым входом элемента И, второй вход которого сЬединен с выходом второго элемента ИЛИ, выходы элементов И, кроме последнего первой группы - соответственно с еди ничными входами триггеров группы, кроме первого, входа Пуск, Режик и .тактовый вход преобразователя соответственно с единичным входом триггера, первым входом второго элемента ИДИ и третьим входом элемента И блока управления, выходы элемента И и триггеров группы которого соединены соответственно с тактовыми вхол дами сумматоров по модулю группы и J позиционного сумматора и соответствующими входами шифратора, выходы которого подключены соответственно к информационным входам сумматоров по модулю группы, позиционного сумматора и первой группе входов схемы сравнения, первый и второй выходы которой соединены соответственно с нулевым входом последнего триггера группы и вторым входом второго элемента ИЛИ блока управления, вторые входы элементов И первой группы которого соединены соответственно с выходами элементов сравнения группы, кроме первого, выходы позиционного сумматора - с второй группой входов схемы сравнения, управляющие входы схемы сравнения, позиционного сумматора и схем сравнения группы - с входом Режим преобразователя, выходы сумматоров по модулю группы являются выходом кода СОК преобразователя. На фиг. 1 представлен обратимьш .преобразователь двоичных кодов в код СОК; на фиг. 2 - блок управления. Обратимый преобразователь двоичных кодов в код СОК содержит блок 1 управления, шифратор 2, сумматоры 3.1-З.п группы по модулям (оснований СОК), позиционньш сумматор 4, схему 5 сравнения, схемы 6.1-б.п сравнения группы., выход 7 двоичных кодов,выходы 8.1-8.П кода СОК,входы 9.19.П остатков по модулям, вход 10 Режим, вход 11 Пуск, вход 12 тактовьк импульсов, выходы 13 и 14 блока управления, входы 15 и 16 блока 1 управления. Блок 1 управления содержит триггер 17, элемент И 18, элемент ИЛИ 19, группу элементов И 20.120.п, группу триггеров 21.1-21.n-1, группу элементов 22.1-22.n-1 задержки, группу элементов И 23.1-23.n-1, элемент ИЛИ 24. Схема 5 сравнения при значении, поступающем с выходов сумматора 4, меньшем, чем значение, поступающее с выхода шифратора 2, формирует короткий импульс, поступающий по входу 15.1 на вход блока 1. Причем импульс на шине 15.1 появляется в момент появления тактового импульса по входу 12, выход 15.2 схемы 5 сравнения асинхронный, инверсный и потенциальный. Схемы сравнения 6.1-б.п имеют потенциальные асинхронные выходы, на которых сигнал логической единицы формируется при совпадении кодов на обеих группах вх При поступлении логического нуля на управляющие входы схем 6.1-6,п сравнения по входу 10 они прекращают выдачу результата преобразования, и на их выходах во время действия сигнала присутствуют нулевые сигналы При этом схеме 5 сравнения разрешает ся вьщача результата сравнения, а позиционный сумматор 4 работает в вычитающем режиме. При подаче по шине 10 логической единицы (преобразование кода СОК в двоичный код) режим работы сумматора 4 и схем 5, 6.1-6.П изменяется на противоположный. Шифратор 2 может быть реализован любым известным способом. Наиболее удобным, с точки зрения упрощения ег проектирования, является преобразование унитарного кода с выходов блока 1 в однопозиционный код длиной п и объединение его разрядов на входах сумматоров посредством элементов ИЛИ. Для оснований Р 3, Pj 4, РЗ 5 работа щифратора 2 описывается табл. 1. Часть шифратора для сумматора 5 по модулю описывается табл. 2. Работа обратимого преобразователя двоичных кодов в код соте основывается на следующей системе выражений h-1 1 + - lAIPn oin И-,+а2Р; + ...+а„,-ПР.|Р -целое положительное число-, -основания СОК; -коэффициент позиционной системы; -остатки по модулям сок. Из данного выражения следует, что перевод числа из СОК в двоичную систему счисления возможно осуществить, последоватльно вычисляя коэффициенты позиционной системы и проверяя равенство полученного выражения остатку по соответствзпощему моду лю СОК. Обратное преобразование возможно осуществить итерационным вычислением коэффициентов позиционной .55

системы, начиная с а„, вычислением указанного ранее выражения и вычитанием его из числа А до его обнулеи остатки, получаемые в процессе преобразования, снимаются по выxpjiaM 8.1-8.п. ния. Процесс преобразования чисел из двоичной системы счисления в код СОК и процесс преобразования чисел, представленных в СОК, в двоичный код обратимы в смысле генерируемых эквивалентов, что позволяет выполнить ту и другую операцию с помощью одних и тех же аппаратурных средств. Обратимый преобразователь двоичных кодов в код СОК работает следующий образом. В режиме преобразования двоичного кода в код СОК по входу 10 в течение всего времени работы поступает логический ноль. Схемы 6.1-6. сравнения блокированы, схеме 5 сравнения разрешена выдача результатов сравнения, в сумматор 4 записано преобразуемое число, и он работает в вычитающем режиме. Сумматоры 3.1-З.п обнулены, триггеры 21.1-21.п установлены в единичное состояние. При поступлении по входу 11 запускающего импульса триггер 17 устанавливается в единичное состояние, разрешая тем самьм прохождение тактовых импульсов через элемент И 18 на тактовые входы сумматоров. При этом в каждом такте в сумматоры 3.1-З.п заносится величина а из содержимого сумматора 4 вычитает п-1 ся величина П Р- . . - На выходе схемы 5 сравнения появляется импульс anj an, который спустя время, равное времени задержки элемента 22 .п-1 задержки, через элемент И 20.п-1 устанавливает триггер 21.п-1 в нулевое состояние. Последующий триггер 20.п-2 не сработает, так как суммарное время задержки двумя элементами 22 задержки больше длительности импульсов на выходе схемы 5. Процесс преобразования протекает до тех пор, пока не сработает триггер 21.1, и по окончании вычитания из содержимого сумматора 4 импульс по щине 15.1 через элемент И 20.1 и элемент ИЛИ 19 установит триггер 17 в исходное состояние. На этом процесс преобразования заканчивается,

.Если при появлении следующих экБивалентов на выходах шифратора 2 значение с выхода сумматора 4 оказывается сразу меньше значения с выхода шифратора 2, то нулевой потенциал по входу 15.2 через элеме ИЛИ 24 запрещает прохозкдение тактовых импульсов на тактовые входы сумматоров 3 и 4. Импульс с выхода схемы 5 сравнения по входу 15.1 устанавливает следующий триггер 21 в нулевое состояние, и на выходах шифратора 2 сформируются новые значения эквивалентов.

При преобразовании кода СОК в двоичный код сумматор 4 работает в суммирующем режиме, схема 5 сравнейия блокирована. Сумматоры 3.1-З.п очищены, по входам 9.1-9.h подается код остатков преобразуемого- числа. Триггеры 21 установлены в нулевое .состояние, и на входы всех сумматоров с шифратора 2 поступает единичный код.

При подаче запускающего импульса по входу 11 срабатывает триггер/17, на выходе элемента ИЛИ 24 присутствет единица, и тактовые импульсы через элемент И 18 поступают на тактовые входы сумматоров 3 и 4. Когда содержимое сумматора 3.1 станет

О

1

О

1

равным oi, , импульс на выходе схемы 6.1 сравнения установит триггер 21.1 в единичное состояние. При этом шифратор 2 генерирует значения | Р., | Р; , поступающие на входы сумматоров 3,1З.п, и .значение Р - на вход сумматора 4.

Подобным образом процесс продолжается до тех пор, пока не сработает схема 6.П сравнения и сигнал логической единицы через элемент II 23.h-1 и элемент ИЛИ 19 не установит триггер 17 в исходное состояние, запретив тем самым последующую работу преобразователя.

При одновременномсрабатывании нескольких соседних схем 6 сравнения устанавливаются в единичное состояни соответствующее количество триггеров 21 и пропуска тактов преобразования не потребуется, как и в процессе (преобразования двоичного кода в код

сок.

Положительный эффект изобретения достигается за счет сокращения количества тактов преобразования, составляющего для СОК с минимальными осно,ваниями примерно 25% и резко возрастающего при росте п и величин оснований системы.

Таблица 1

Таблица 2

3 2

о о

1 о

Риг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 756401, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-23—Публикация

1983-10-10—Подача