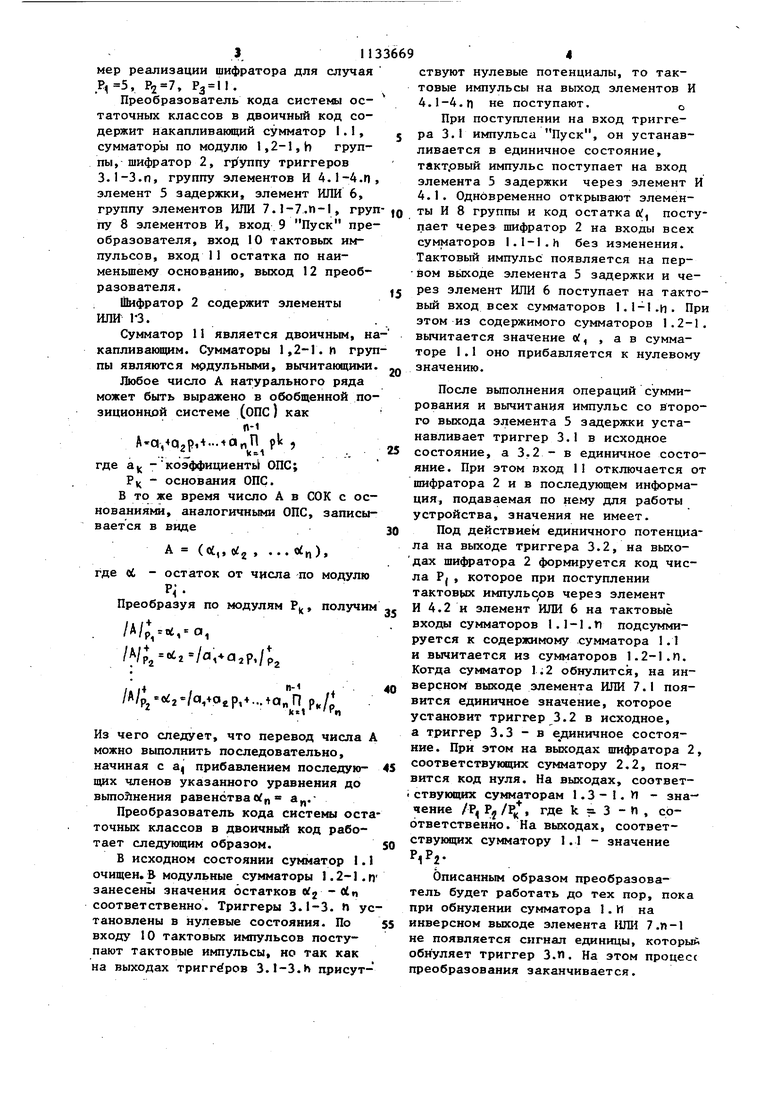

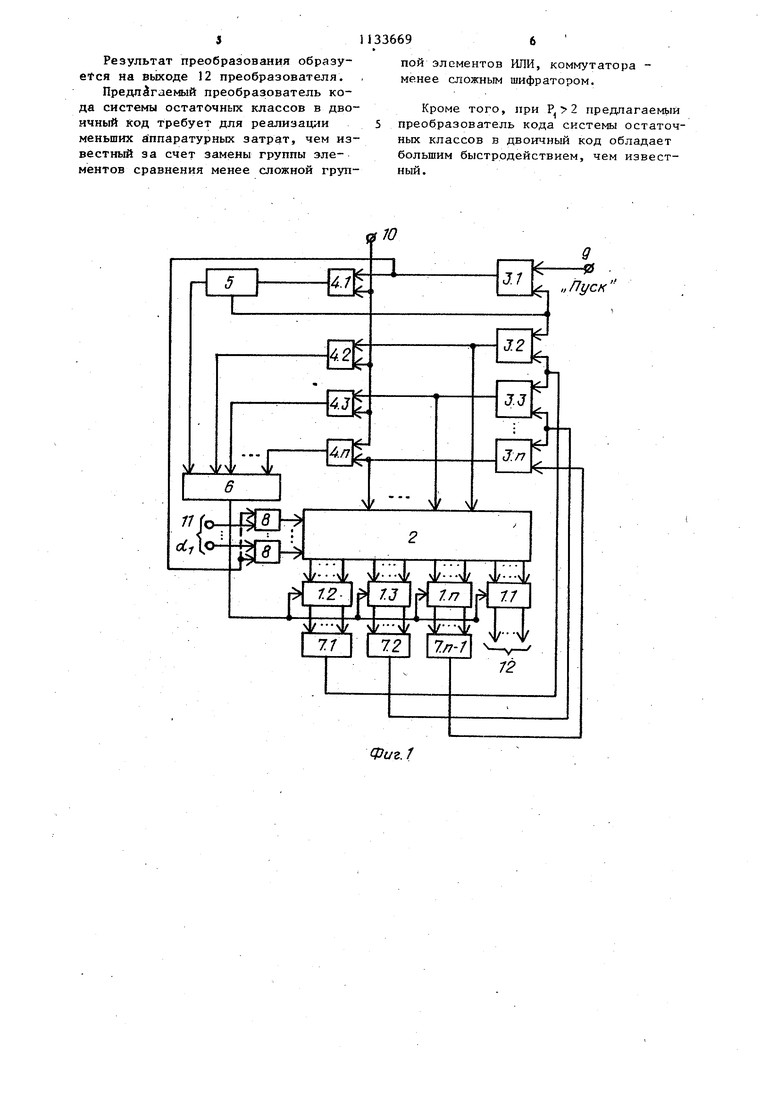

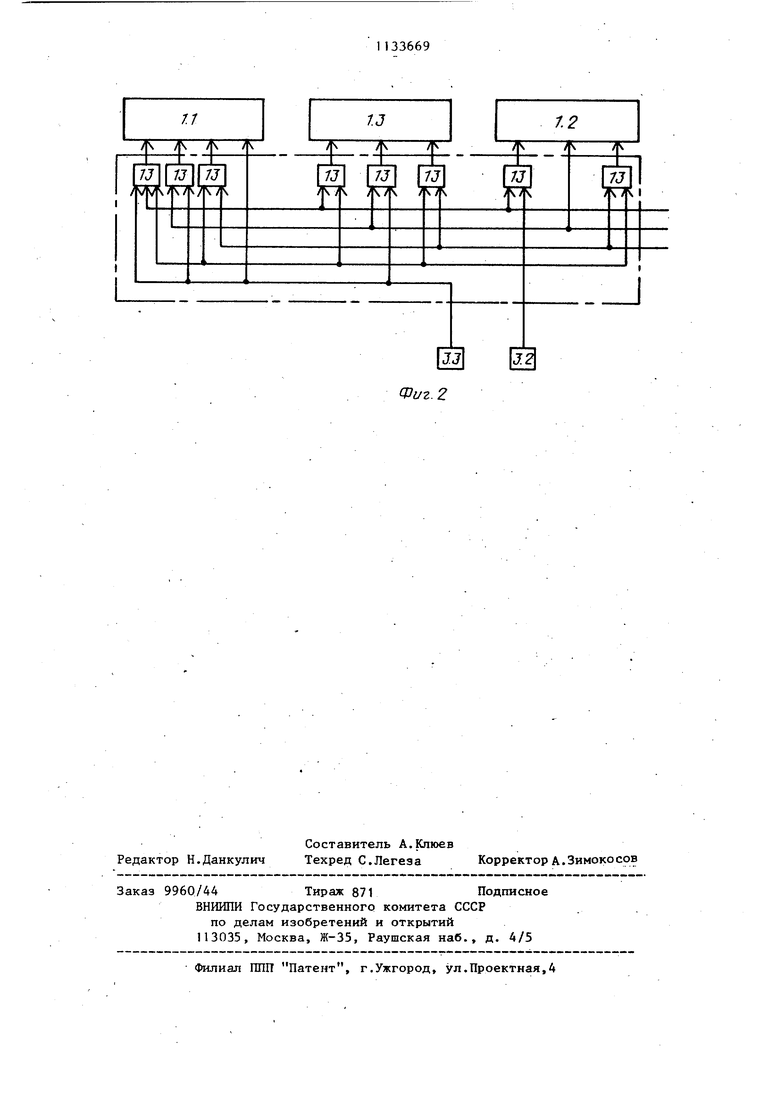

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в СОК, а также в аппаратуре передачи данных, использующей коды СОК. Известно устройство для преобразования чисел из СОК в позиционный код, содержащее суммирующие счетчики входные регистры, элементы сравнения по основаниям СОК, двоичный накапливающий счетчик, выходы которого являются выходом устройства, первый триггер, первьй и второй элемент И у Однако данное устройство требует значительных аппаратурных затрат и обладает недостаточным быстродействием,что снижает эффективность вьшислительных ус тройств, функционирующих в СО Наиболее близким к изобретению по сущности технического решения является преобразователь непозиционног кода в двоичный код, содержащий груп пу входных регистров, группу элементов сравнения, группу элементов И, группу счетчиков по модулю, накапливающий сумматор, коммутатор, элемент ИЛИ, группу триггеров, причем входы счетчиков по модулю группы соединены соответственно с выходами элементов И, первые входы которых соединены с тактовым входом преобразователя, информационные входы которого соединены с входами регистров группы, выходы которых соединены с первыми входами соответствующих элементов сравнения группы, вторые входы которых соединены с выходами соответствующих счетчиков по модулю группы, выходы накапливающего сумматора являются выходами преобразователя входы констант эквивалентов которого соединены с информационными входами коммутатора, выходы которого соединены с информационными входами накапливающего сумматора, управлякиций .вход которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы, вторые входы которых соединены с вы ходами соответствующих триггеров группы и с управляющими входами коммутатора, выход k -го элемента сравнения труппы (, где И число оснований) соединен с нулевым входом| го и единичным входом ( триггера группы, единичный вход пер вого триггера группы является входом пуска преобразователя 2 . Недостатком известного устройства являются значительные аппаратурные затраты. Цель изобретения - сокращение ко личества оборудования. Поставленная цель достигается тем, что преобразователь кода системы остаточных классов в двоичный код, содержащий группу сумматоров по модулю, накапливающий сумматор, группу триггеров, первую группу элементов И и элемент ИЛИ, причем выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с тактовым входом преобразователя, выходы элементов И, кроме первого, первой группы подключены к соответствующим входам элемента ИЛИ, выход которого соединен с тактовым входом накапливакмцего сумматора, выход которого является выходом преобразователя, единичный вход первого триггера группы соединен с входом Пуск преобразователя, нулевой вход k-го триггера группы соединен с единичным входом (k+l)-ro триггера группы ((и-1), где п - число оснований,содержит шифратор, группу элементов ИЛИ, элемент задержки и вторую группу элементов И, причем вход остатка по наименьшему основанию преобразователя соединен с первыми входами элементов И второй группы, выходы которых соединены с первой группой входов шифратора, вторая группа входов которого соединена свыходами триггеров с второй по м-и группы, выходы шифратора соединены соответственно с информационными входами накапливающего сумматора и сумматоров группы, выходы сумматоров группы соединены с входами соответствующих элементов ШШ группы, инверсные выходы которых подключены к нулевым входам триггеров с второй по П-и группы выход первого триггера группы соединен с вторыми входами элементов И второй группы, выход первого элемента И первой группы через элемент задержки соединен с нулевым входом первого триггера группы и п м входом элемента ИЛИ, выход которого соединен с тактовыми входами сумматоров группы. На фиг,1 представлен преобразователь кода системы остаточных классов в двоичный код; на фиг.2 - пример реализации шифратора для случая Р, 5, , РЗ И. Преобразователь кода системы остаточных классов в двоичный код содержит накапливающий сумматор 1.1, сумматоры по модулю l,2-l,h группы, шифратор 2, ri ynrry триггеров 3.1-З.п, группу элементов И А.1-4.П элемент 5 задержки, элемент ИЛИ 6, группу элементов ИЛИ 7.1-7.П-1, груп пу 8 элементов И, вход 9 Пуск преобразователя, вход 10 тактовых импульсов, вход 11 остатка по наименьшему основанию, выход 12 преобразователя. Шифратор 2 содержит элементы ИЛИ 1-3. Сумматор 11 является двоичным, н капливающим. Сумматоры 1,2-1. и гру пы являются мрдульными, вычитающими Любое число А натурального ряда может быть выражено в обобщенной по зиционной системе (ОПС) как П-1 А-а, р1 где a(j -коэффициенть ОПС; Р, - основания ОПС. В то же время число А в СОК с ос нованиями, аналогичными ОПС, записы вается в виде А (ot,, , ... ), где ot - остаток от числа по модулю Р Преобразуя по модулям Р,, получи , a, ,a2p,/p2 /A/J ,+aep,+-.+a«n pJ .k 11 ( Из чего следует, что перевод числа можно выполнить последовательно, начиная с & прибавлением последующих членов указанного уравнения до вьто нения равенства п Преобразователь кода системы ост точных классов в двоичный код работает следующим образом. В исходном состоянии сумматор 1. очищен. В модульные сумматоры 1.2-l. занесены значения остатков of2 п соответственно. Триггеры 3.1-3. h у тановлены в нулевые состояния. По входу 10 тактовых импульсов поступают тактовые импульсы, но так как на выходах триггеров 3.1-3.h дрисут ствуют нулевые потенциалы, то тактовые импульсы на выход элементов И 4.1-4.П не поступают.о При поступлении на вход триггера 3.1 импульса Пуск, он устанавливается в единичное состояние, тактрвый импульс поступает на вход элемента 5 задержки через элемент И 4.1. Одновременно открывают элементы И 8 группы и код остатка tf, поступает через шифратор 2 на входы всех сумматоров l.l-l.h без изменения. Тактовый импульс появляется на первом выходе элемента 5 задержки и через элемент ИЛИ 6 поступает на тактовый вход всех сумматоров 1.1-1.ц . При этом из содержимого сумматоров 1.2-1. вычитается значение (У, , а в сумматоре 1.1 оно прибавляется к нулевому значению. После вьшолнения операций суммирования и вычитания импульс со второго выхода элемента 5 задержки устанавливает триггер 3.1 в исходное состояние, а 3.2 - в единичное состояние. При этом вход I1 отключается от шифратора 2 и в последующем информация, подаваемая по нему для работы устройства, значения не имеет. Под действием единичного потенциала на выходе триггера 3.2, на выходах шифратора 2 формируется код числа PJ , которое при поступлении тактовых импульс ов через элемент И 4.2 и элемент ИЛИ 6 на тактовые входы сумматоров 1.1-1.И подсуммируется к содержимому сумматора 1.1 и вычитается из сумматоров 1.2-1.П. Когда сумматор 1;2 обнулится, на инвареном выходе элемента ШШ 7.1 появится единичное значение, которое установит триггер 3.2 в исходное, а триггер 3.3 - в единичное состояние. При этом на выходах шифратора 2, соответствующих сумматору 2.2, появится код нуля. На выходах, соответствующих сумматорам 1.3 - 1. И - значение /Р PJ /Р, где k 5S. 3 - И , соответственно. На выходах, соответствующих сумматору 1.1 - значение . Описанным образом преобразователь будет работать до тех пор, пока при обнулении сумматора 1.И на инверсном выходе элемента ИЛИ 7.П-1 не появляется сигнал единицы, который обнуляет триггер З.п. На этом процесс преобразования заканчивается.

Результат преобразования образуetcH на вьЬсоде 12 преобразователя.

Предлагаемый преобразователь кода системы остаточных классов в двоичный Код требует для реализации меньших аппаратурных затрат, чем известный за счет замены группы элементов сравнения менее сложной группой элементов ИЛИ, коммутатора менее сложным шифратором.

Кроме того, при Р 2 предпагаемь1й преобразователь кода системы остаточных классов в двоичный код обладает большим быстродействием, чем известный.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1983 |

|

SU1181140A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1989 |

|

SU1742997A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ Б ДВОИЧНЫЙ КОД, содержащий группу сумматоров по модулю, накапливающий сумматор, группу триггеров, первую группу элементов И и элемент ИЛИ, причем выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с тактовым ВХОДОМ преобразователя, ВЫХОДЫ элементов И, кроме первого, первой группы подключены к соответствующим входам элемента ИЛИ, ВЫХОД которого соединен с тактовым ВХОДОМ накапливающего сумматора, выход которого является ВЫХОДОМ преобразователя, единичный ВХОД первого, триггера группы соединен с входом Пуск преобразователя, нулевой вход k-ro триггера группы соединен с единичным ВХОДОМ (k+l)ro триггера группы (k . . . (п-1 ), где П - число оснований, отличающийся, тем, что, с целью сокращения количества оборудования, он содержит шифратор, группу элементов ИЛИ, элемент задержки и вторую группу элементов И, причем ВХОД остатка по наименьшему основанию преобразователя соединен с первыми входами элементов И.второй группы, ВЫХОДЫ которых соединены с первой группой входов шифратора, вторая группа входов которого соединена с выходами триггеров с второй по И-и группы, ВЫХОДЫ шифратора g соединены соответственно с информационными входами накапливающего cyvr (Л матора и сумматоров группы, выходы сумматоров группы соединены с входами соответствующих элементов ИЛИ группы, инверсные выходы которых подключены соответственно к.нулевым входам триггеров с второй по И-и группы, ВЫХОД первого триггера группы соединен с вторыми входами элеменСАд тов И второй группы, ВЫХОД первого :с элемента И первой группы через эле9) 35 мент задержки соединен с нулевым входом первого триггера группы и П-м CD ВХОДОМ элемента ИЛИ, выход которого соединен с тактовыми входами сумматоров группы.

:i

- ч|/

„ Пуск

Sf--- /

|jj| IJ;

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1981 |

|

SU991410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3518613/18-24, 1982 (прототип). | |||

Авторы

Даты

1985-01-07—Публикация

1983-10-10—Подача