1

Изобретение относится к автоматике и вычислительной технике, в частности к информационно-измерительной технике, и может быть использовано для обрабЬт-j ки данных в информационно-измеритель- , ных системах и в цифровых вычислительных машинах, работающих в системе остаточных классов и реализующих допусковый контроль.IQ

Известно устройство для сравнения чисел в системе остаточных классов, содержащее сумматоры, элементы И и НЕ регистры и узлы анализа Cl.

Недостатком известного устройства является невозможность сравнения чи- «5 сел с заранее заданной погрешностью.

Наиболее близким техническим решени м к предложенному является устройство, содержащее узлы деления, регистры, сумматоры, блок сравнения на ра- венство, блок сравнения и два коммутатора, причем выходы регистров первого и второго блоков преобразования соединены соответственно со входами „ первого и второго коммутаторов, в1ыхот ды которых подключены ко входам блр- ка сравнения на равенство, один из выходов которого соединен с первым входом блока сравнения, а другой выход - с первым входом второго эле- 30

мента ИЛИ, выход которого соединен со вторым входом блока сравнения, третий и четвертый входы которого подключены соответственно к выходам, элементов И группы первого и второ- . го блоков преобразования, а выходы блока сравнения, служат выходами устройства 23.

Недостатками этого устройства являются невозможность сравнения чисел с заданной погрешностью,.невысокое быстродействие, обусловленное наличием узлов деления, а также большая сложность,

Цель изобретения - расширение функциональных возможностей, за счет сравнения с заданной погрешностью, повышение быстродействия.

Эта цель достигается тем, что в устройство для сравнения чисел в системе остаточных классов, содержащее первый и второй регистры, п, ячеек анализа, триггер, элементы И, ИЛИ, схему сравнения на равенство, причем каждые -i -ые группы входов первого и второго регистров, где л -1,2,... п, соединены с информационными входами первой.и второй .группы входов соответственно л -ой ячейки анализа, каждая из которых состоит из

групп элементов И, элементов ИЛИ и сумматора, а информационные входы первой группы входов каждой ячейки анализа соединены с информационными входами элементов И первой и второй групп, а информационные входы второй группы входов каждой ячейки анализа подключены к информационным входам элементов И третьей и четвертой .групп, первый управляющий вход каждой ячейки анализа соединен с управляющими входами элементов И второй и четвертой групп, а второй управляющий вход каждой ячейки анализа подключен к управляющим входам элементов И первой и третьей групп, выходы элементов И первой и четвертой групп каждой ячейки coeдинeн iI со входами элементов ИЛИ первой группы, выходы которых подключены к первым входам сумматора, выходы элементов И второй и третьей групп соединены со входами элементов ИЛИ второй группы, выходы которых подключены ко вторым входам сумматора, вьаходы которого соединены с выходами ячейки анализа, введен регистр уставок и схема сравнения: .с уставками, а вход запуска устройства соединен с первым входом первого элемента ИЛИ, выход которого подключен ко входу установки в единичное состояние триггера, а инверсный и прмой выходы которого соединены с первыми и вторыми входами управления соответственно всех ячеек анализа, выход каждой ч-ой ячейки анализа подключены к L-ым входам схемы сравнения на равенство и второго элемента. ИЛИ, выход которого соединен с информационным входом элемента И, выход которого подключен к первому входу схемы сравнения с уставками, второй вхо которой соединен свыходом регистра уставок, первый выход схемы сравнения на равенство подключен к управляющему входу элемента И и ко вторрму входу первого элемента ИЛИ, а второй выход схемы сравнения на равенство соединен со входом установки в нулевое состояние триггера.

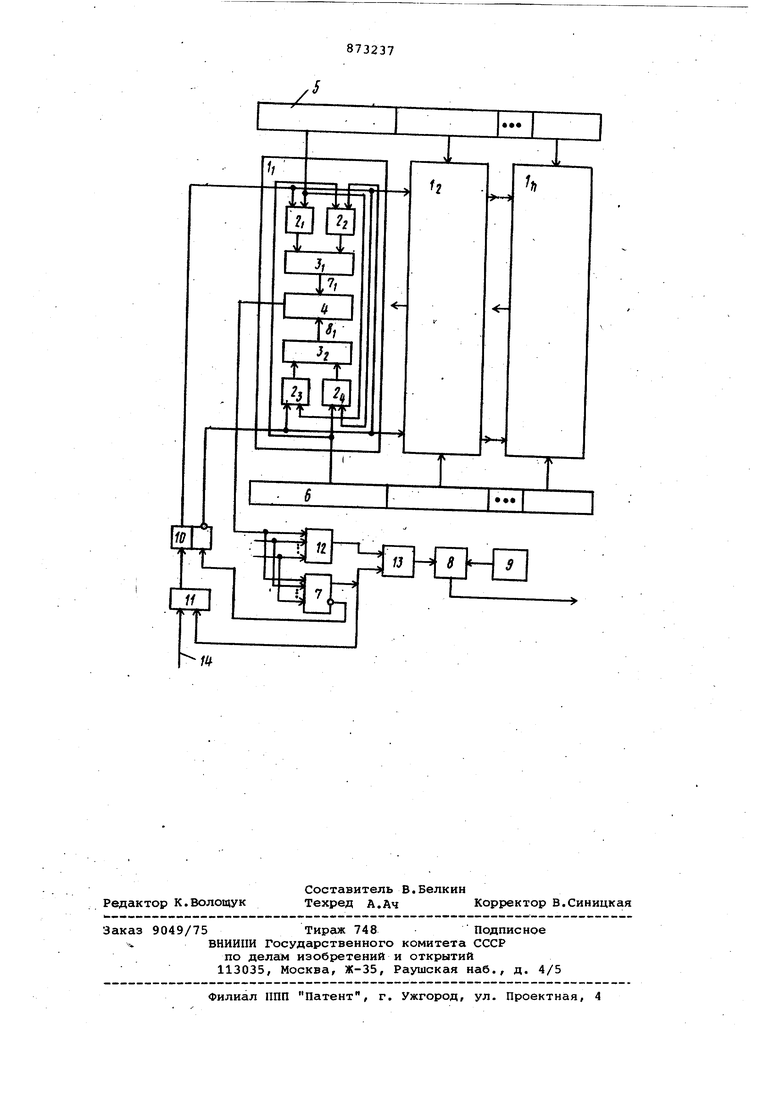

На чертеже представлена функциональная схема устройства.

Устройство содержит ячейки анализа Ijf, ±2 V) каждая из которых .состоит из групп элементов И 2jf 22, ....24, групп элементов ИЛИ 3j) , 3;, и сумматора 4 , регистры 5 и 6, схемы сравнения на равенство 7, схема 8 сравнения с уставками, 9 регистр уставок, триггер 10, элементы ИЛИ 11 и 12, элемент И 13 и вход запуска 14.

Устройство работает следующим образом.

К моменту начала сравнения в регистрах 5 и 6 записаны сравниваемые два числа (А и В соответственно}, а в регистре 9 уставки записана требуемая уставка.

После подачи сигнала на шину запуска 14 через элемент ИЛИ 11 триггер 10 устанавливается в единичное состояние. Тем самым разрешается .прохождение информации через элементы И группы 2.f и 2 каждой ячейки анализа. В результате через элементы ИЛИ на суммирующие входы сумматоров 4 ячеек анализа подается код из регистра 5 а на вычитающие входы - кdfд из регистра 6. Таким образом вычисляется разность А - В параллельно во всех модулях системы остаточных классов, т.е. определяются числа

--а--ъ,, ...,и

где

А mod У

Ь HBiMod Г - i - модуль системы остаточных

классов.

Дальнейшая работа устройства определяется работой блока сравнения на равенство 7. Если блок сравнения на равенство 7 зафиксировал равенство всех чисел d между собой, то он через элемент И 13 разрешает прохождение любого из чисел выхода элемента ИЛИ 12 на один из входов схемы 8 сравнения с уставкой. Схема 8 сравнения с уставкой осуществляет сравнение (по принципу больше-меньше величины поступившего числа со значением уставки, записанном в регистре 9 уставок. Указанное сравнение производится в обычном позиционном коде. Сигнал сравнения на выходе схемы 8 сравнения с уставкой является выходным сигналом всего устройства. Одновременно с указанными действиями схема сравнения на равенство 7 через второй вход элемента ИЛИ 11 подтверждает состояние триггера 10. Если блок сравнения на равенство 4 не зафиксировал равенство всех чисел d между собой, в этом случае числа на вход элемента И 13 не попадают и работа схемы 8 сравнения с уставкой блокируется. Одновременно сигнал с инверсного выхода схемы сравнения на равенство 4 изменяет состояние триггера 10 на противоположное. Этим разрешается прохождение информации через элементы И группы 2, 2 каждой ячейки анализа. Теперь через группы элементов ИЛИ 3 на вычитающие входы сумматоров 4 подается код регистра 5 , а на суммирующие входы код из регистра 6. Таким образом вычисляется разность А - В параллельно во всех модулях системы остаточных классов, т.е. теперь определяютс числа

. Дальнейшая работа устройства совпадает с описанной во всем, за исключением того, что теперь в блоке сравнения на равенство 4 и в блоке сравнения с уставкой 5 анализируются не числа ,a числа Таким образом, предлагаемое устройство позволяет получить выигрыш в быстродействии в .И/2 раз по срав нению с известным устройством У1 - число модулей в системе остаточ. ных классов за счет распараллеливания процесса сравнения двух чисел по всем модулям системы остаточ1аах классов. Кроме того, реализация срав нения двух чисел с заданной пограаностью позволяет реализовать системы допускового контроля и. системы тревожной сигнализации, работающие полностью в системе остаточных классов. Формула изобретения Устройство для сравнения чисел в системе остаточных классов, содер Жсцдее первый и второй регистры Yt яче ек анализа, триггер, элементы И, ИЛИ схему.сравнения на равенство, причем каждые -ые группы выходов первого и- второго регистров, где ,2,.. .п соединены с информационными входами первой и второй группы входов соответственно -oй ячейки анализа, ка |дая из которых состоит из групп элеJMeHTOB И, элементов ИЛИ и сумматора, а информационные входы первой группы входов каждой ячейки анализа соединены с информационными входами элементов И первой и второй групп, а информационные входы второй группы входов каждой ячейки анализа подключены к информационным входам элементов И третьей и четвертой груп первый управляющий вход каждой ячейки анализа соединен с управляющими входами элементов И второй и четвертой групп, а второй управляющий вход каждой ячейки анализа подключен к управляющим входам элементов И первой и третьей групп, выходы элементов И первой и четвертой групп каждой ячейки соединены со входами элементов ИЛИ первой группы, вькоды которых подключены к первым входам сумматора, выходы элементов И второй и третьей групп соединены со входами элементов ИЛИ второй группы, выходы которлх подключены ко вторым входам сумматора, выходы которого соединены с выходами ячейки анализа, отличающееся тем, что, с целью расширения функциональных возможностей за счет сравнения с заданной погрешностью и повышения быстродействия, в него введен регистр уставок и схема сравнения с уставками, а вход запуска устройства соединен с первым входом первого элемента ИЛИ, выход которого подключен ко входу установки в единичное состояние триггера, а инверсный и прямой выходы которого соединены с первыми и вторг лк входами управления соответственно всех ячеек анализа, выход каждой i- -ой ячейки анализа подключен к н-ым. ВХОДС1М схемы сравнения на равенство и второго элемента ИЛИ, выход которого соединен с информационным входом элемента И, выход которого подключен к первому входу схемы сравнения с уставками, второй вход которой соединен с выходом регистра уставок, первый выход схемы сравнения на равенство подключен к управляющему входу элемента И и ко второму входу первого элемента ИЛИ, а второй выход схемы сравнения на равенство соединен со входом установки в нулевое состояние триггера. Источники информации ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 618739, кл. g 06 F 7/04, 1976. 2.Авторское свидетельство СССР €08155, кл. G06 F 7/04, 1976 . (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сравнения чисел, представленных в системе остаточных классов | 2020 |

|

RU2751992C1 |

| Устройство для сортировки | 1988 |

|

SU1569821A1 |

| Устройство для сравнения чисел | 1985 |

|

SU1287142A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Устройство автоматического регулирования частоты и перетоков активной мощности в энергосистеме | 1982 |

|

SU1089698A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1986 |

|

SU1325460A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

Авторы

Даты

1981-10-15—Публикация

1979-12-21—Подача