Изобретение относится к вычислительной технике, в частности к системам распределенной обработки информации, и может быть использовано для построения вычислительных сетей с локально распределенными ресурсами.

Цель изобретения - расширение клас-г са решаемых задач за счет функций моделирования распределенных систем, в частности транспортных потоков на участках железных дорог.

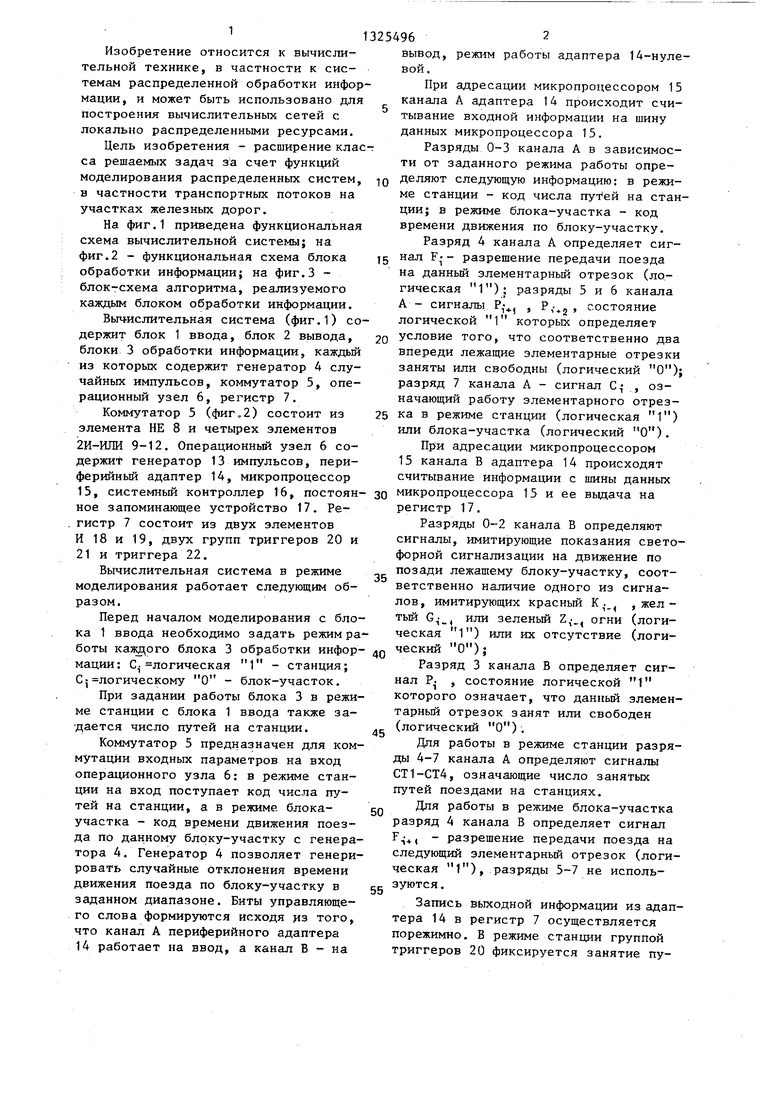

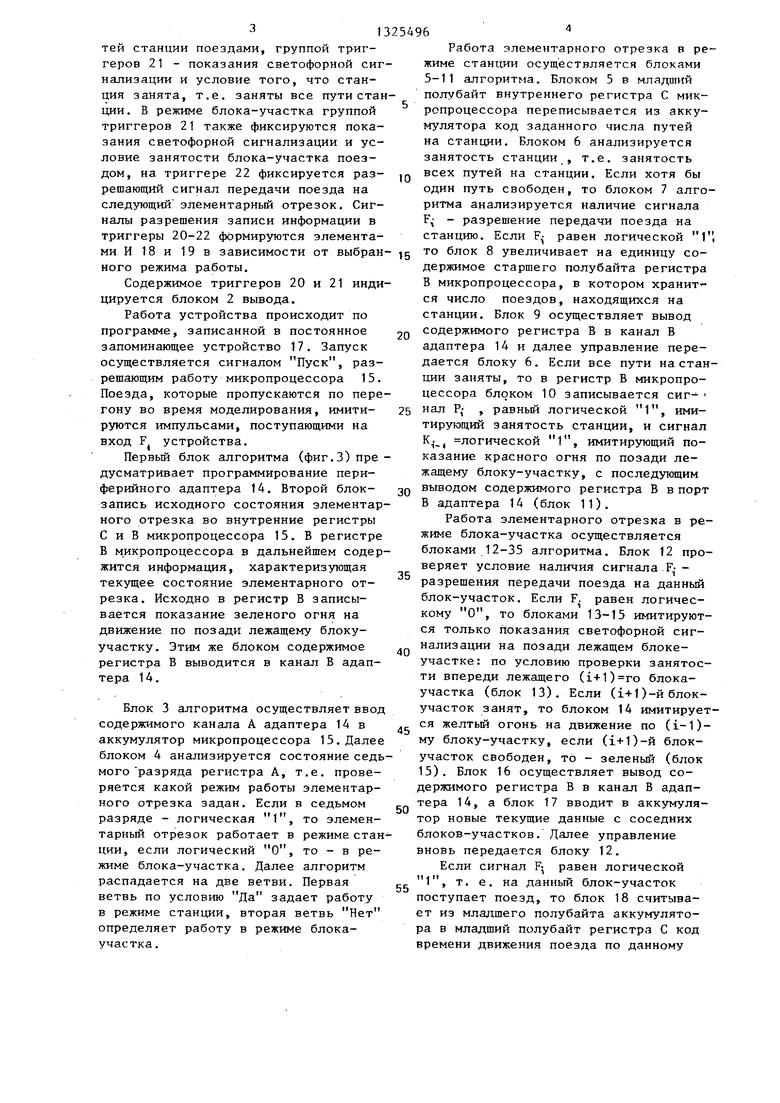

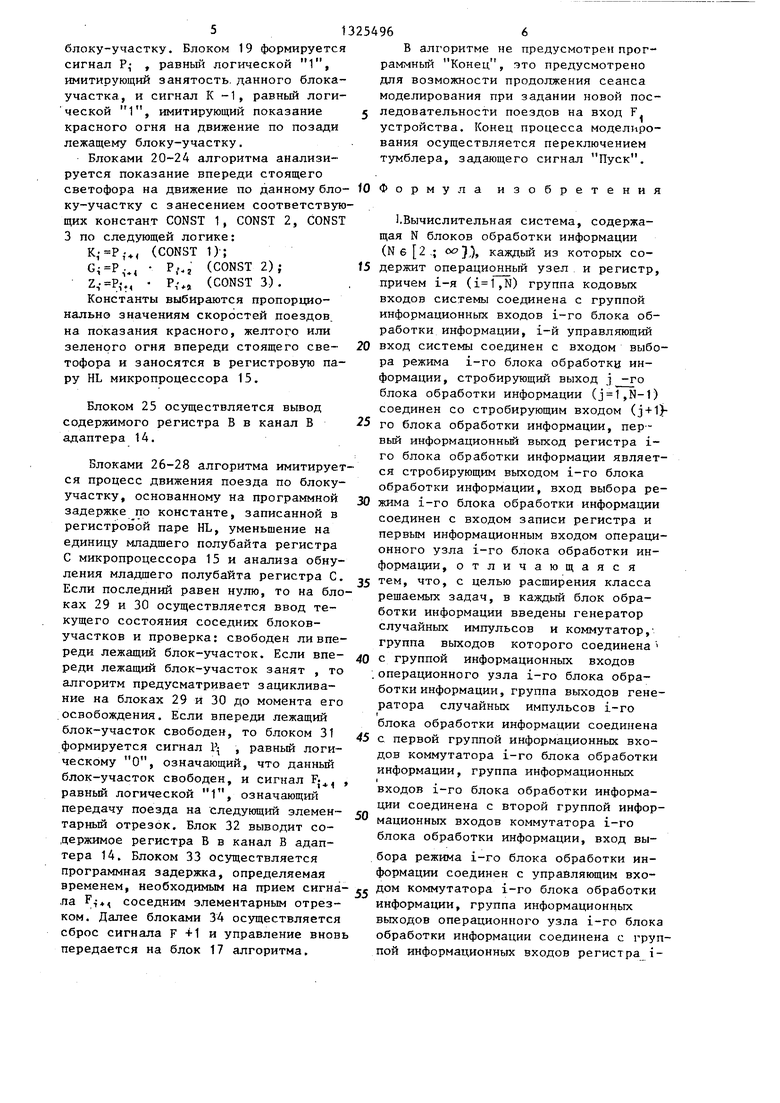

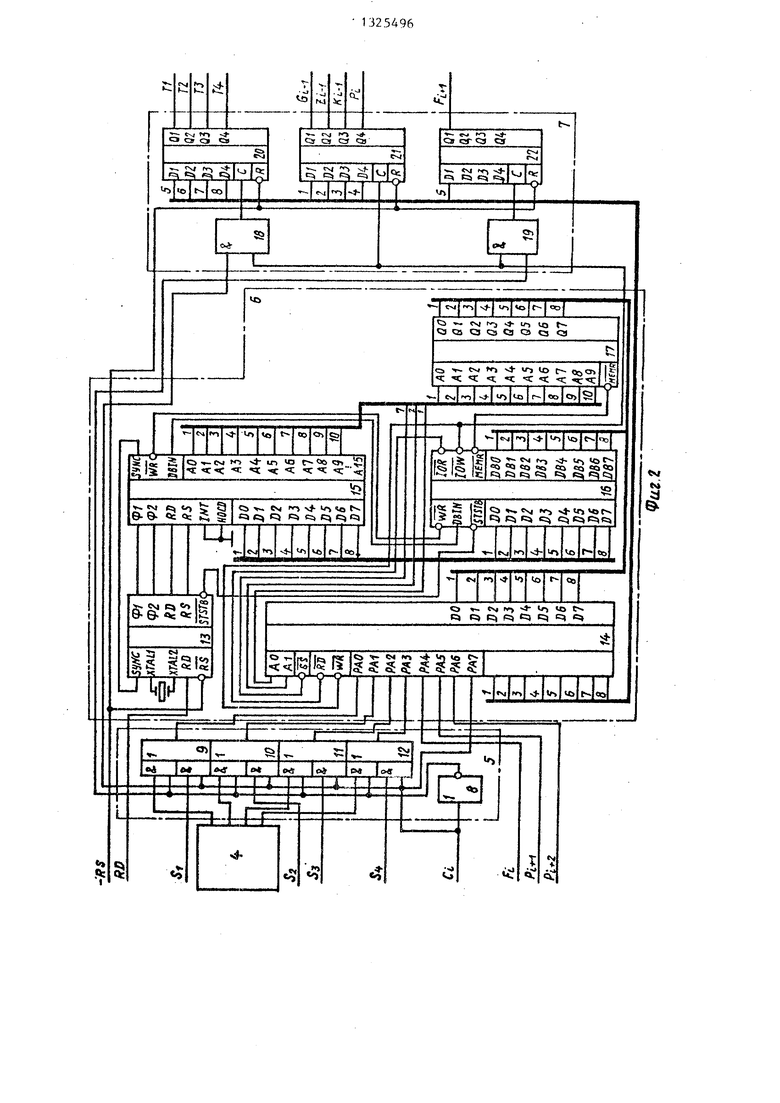

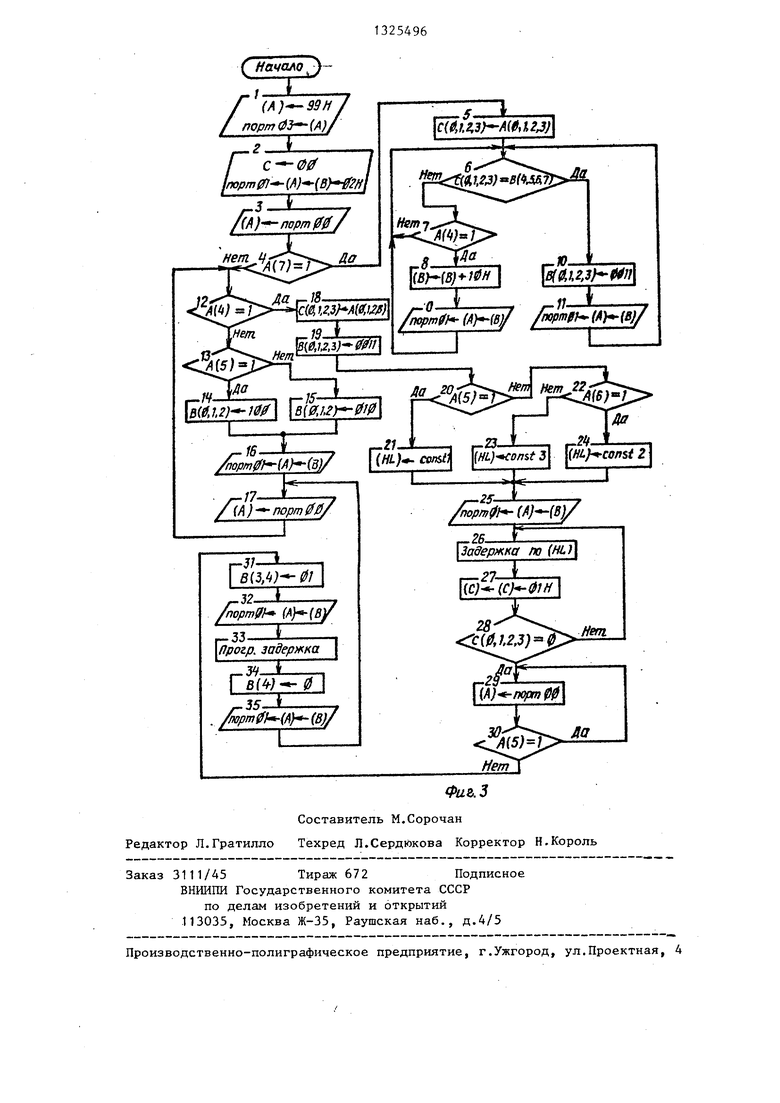

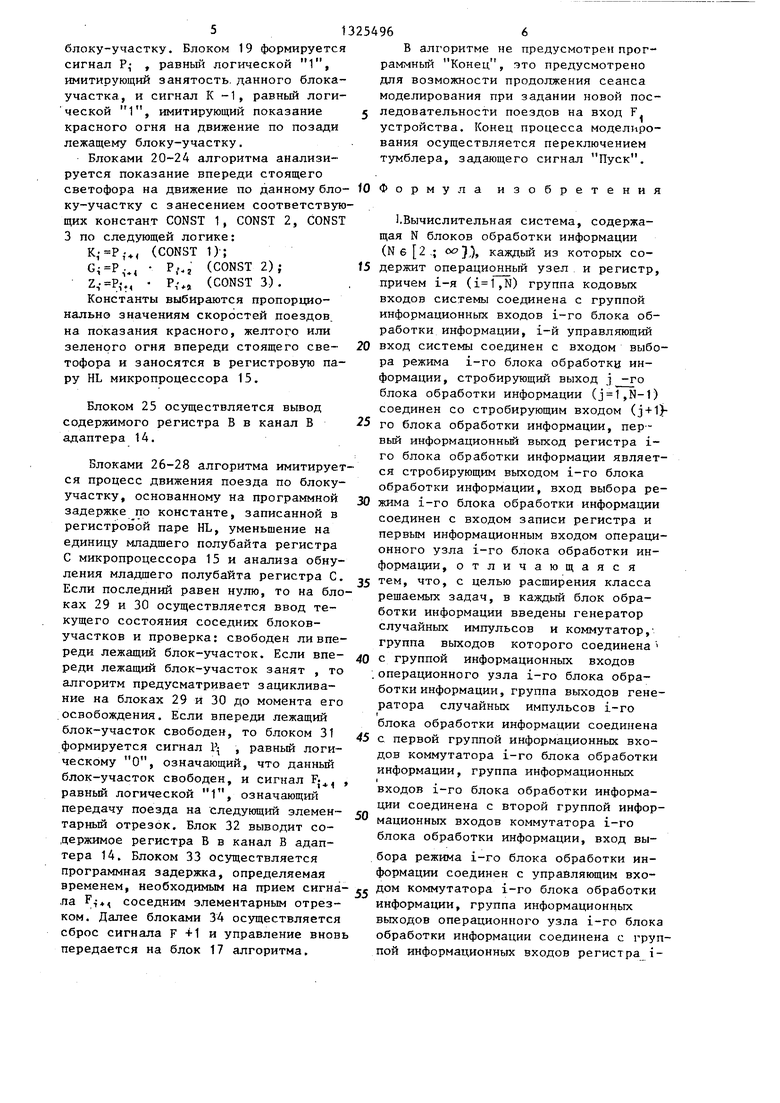

На фиг.1 приведена функциональная схема вычислительной системы; на фиг.2 - функциональная схема блока обработки информации; на фиг.З - блок-схема алгоритма, реализуемого каждым блоком обработки информации.

Вычислительная система (фиг.1) содержит блок 1 ввода, блок 2 вывода, блоки 3 обработки информации, каждьш из которых содержит генератор 4 случайных импульсов, коммутатор 5, операционный узел 6, регистр 7.

Коммутатор 5 (фиг„2) состоит из элемента НЕ 8 и четырех элементов :2И-ИЛИ 9-12. Операционный узел 6 содержит генератор 13 импульсов, периферийный адаптер 14, микропроцессор

вывод, режим работы адаптера 14-ну вой.

При адресации микропроцессором канала А адаптера 14 происходит сч тывание входной информации на шину данных микропроцессора 15.

Разряды 0-3 канала А в зависимо ти от заданного режима работы опре Q деляют следующую информацию: в реж ме станции - код числа пут ей на ст ции; в режиме блока-участка - код времени движения по блоку-участку.

Разряд 4 канала А определяет си нал F - разрешение передачи поезда на данный элементарный отрезок (ло гическая 1); разряды 5 и 6 канал А - сигналы ) Pi4/ состояние логической 1 которых определяет 20 условие того, что соответственно д впереди лежащие элементарные отрез заняты или свободны (логический О разряд 7 канала А - сигнал , оз начающий работу элементарного отре 25 ка в режиме станции (логическая 1 или блока-участка (логический О)

При адресации микропроцессором 15 канала В адаптера 14 происходят считывание информации с шины данны

15

15, системный контроллер 16, постоян- зо микропроцессора 15 и ее вьщача на

ное запоминающее устройство 17. Регистр 7 состоит из двух элементов И 18 и 19, двух групп триггеров 20 и 21 и триггера 22.

Вычислительная система в режиме моделирования работает следующим образом.

Перед началом моделирования с блока 1 ввода необходимо задать режим ра35

регистр 17.

Разряды 0-2 канала В определяют сигналы, имитирующие показания све форной cигнaJшзaции на движение по позади лежащему блоку-участку, соо ветственно наличие одного из сигна лов, имитирующих красный К. , жел тый G,, или зеленый Z,- огни (лог ческая 1) или их отсутствие (лог

боты какого блока 3 обработки инфор- Q ческий О); мации: С логическая 1 - станция;

Cj логическому О - блок-участок.

При задании работы блока 3 в режиме станции с блока 1 ввода также задается число путей на станции. 45

Коммутатор 5 предназначен для коммутации входных параметров на вход операционного узла 6: в режиме станции на вход поступает код числа путей на станции, а в режиме блока- 50 участка - код времени движения поезда по данному блоку-участку с генератора 4. Генератор 4 позволяет генерировать случайные отклонения времени движения поезда по блоку-участку в 55 заданном диапазоне. Биты управляющего слова формируются исходя из того, что канал А периферийного адаптера 14 работает на ввод, а канал В - на

нал Р,

Разряд 3 канала В определяет си

, состояние логической 1 которого означает, что данный элем тарный отрезок занят или свободен (логический О).

Для работы в режиме станции раз ды 4-7 канала А определяют сигналы СТ1-СТ4, означающие число занятых путей поездами на станциях.

Для работы в режиме блока-участ разряд 4 канала В определяет сигна - разрешение передачи поезда следующий элементарный отрезок (ло ческая 1), разряды 5-7 не исполь зуются .

Запись вькодной информации из ад тера 14 в регистр 7 осуществляется порежимно. В режиме станции группо триггеров 20 фиксируется занятие п

вывод, режим работы адаптера 14-нуле- вой.

При адресации микропроцессором 15 канала А адаптера 14 происходит считывание входной информации на шину данных микропроцессора 15.

Разряды 0-3 канала А в зависимости от заданного режима работы опре- деляют следующую информацию: в режиме станции - код числа пут ей на станции; в режиме блока-участка - код времени движения по блоку-участку.

Разряд 4 канала А определяет сигнал F - разрешение передачи поезда на данный элементарный отрезок (логическая 1); разряды 5 и 6 канала А - сигналы ) Pi4/ состояние логической 1 которых определяет условие того, что соответственно два впереди лежащие элементарные отрезки заняты или свободны (логический О); разряд 7 канала А - сигнал , означающий работу элементарного отрез- ка в режиме станции (логическая 1) или блока-участка (логический О).

При адресации микропроцессором 15 канала В адаптера 14 происходят считывание информации с шины данных

микропроцессора 15 и ее вьщача на

регистр 17.

Разряды 0-2 канала В определяют сигналы, имитирующие показания светофорной cигнaJшзaции на движение по позади лежащему блоку-участку, соответственно наличие одного из сигналов, имитирующих красный К. , жел- тый G,, или зеленый Z,- огни (логическая 1) или их отсутствие (логический О);

нал Р,

Разряд 3 канала В определяет сиг, состояние логической 1 которого означает, что данный элементарный отрезок занят или свободен (логический О).

Для работы в режиме станции разряды 4-7 канала А определяют сигналы СТ1-СТ4, означающие число занятых путей поездами на станциях.

Для работы в режиме блока-участка разряд 4 канала В определяет сигнал - разрешение передачи поезда на следующий элементарный отрезок (логическая 1), разряды 5-7 не используются .

Запись вькодной информации из адаптера 14 в регистр 7 осуществляется порежимно. В режиме станции группой триггеров 20 фиксируется занятие пу3

теи станции поездами, группой триггеров 21 - показания светофорной сигнализации и условие того, что станция занята, т.е. заняты все пути станции. В режиме блока-участка группой триггеров 21 также фиксируются показания светофорной сигнализации и условие занятости блока-участка поездом, на триггере 22 фиксируется разрешающий сигнал передачи поезда на следующий элементарный отрезок. Сигналы разрешения записи информации в триггеры 20-22 формируются элементаРабота элементарного отрезка в режиме станции осуществляется блоками 5-11 алгоритма. Блоком 5 в младший полубайт внутреннего регистра С микропроцессора переписывается из аккумулятора код заданного числа путей на станции. Блоком 6 анализируется занятость станции , т.е. занятость всех путей на станции. Если хотя бы один путь свободен, то блоком 7 алгоритма анализируется наличие сигнала разрешение передачи поезда на

10

F- станцию. Если F

равен логической 1

ми И 18 и 19 в зависимости от выбран- 15 блок 8 увеличивает на единицу со- ного режима работы.

Содержимое триггеров 20 и 21 индицируется блоком 2 вывода.

Работа устройства происходит по

держимое старшего полубайта регистра В микропроцессора, в котором хранится число поездов, находящихся на станции. Блок 9 осуществляет вывод содержимого регистра В в канал В адаптера 14 и далее управление передается блоку 6. Если все пути на станции заняты, то в регистр В микропроцессора блоком 10 записывается сиг- 25 нал Р- , равный логической 1, имитирующий занятость станции, и сигнал К,., логической 1, имитирующий показание красного огня по позади лежащему блоку-участку, с последующим выводом содержимого регистра В в порт В адаптера 14 (блок 11),

программе, записанной в постоянное запоминающее устройство 17. Запуск осуществляется сигналом Пуск, разрешающим работу микропроцессора 15. Поезда, которые пропускаются по перегону во время моделирования, имитируются импульсами, поступающими на вход F устройства.

Первый блок алгоритма (фиг.3) предусматривает программирование пери ферийного адаптера 14. Второй блок- запись исходного состояния элементарного отрезка во внутренние регистры С и В микропроцессора 15. В регистре В м.икропроцессора в дальнейшем содержится информация, характеризующая текущее состояние элементарного отрезка. Исходно в регистр В записывается показание зеленого огня на движение по позади лежащему блоку- участку. Этим же блоком содержимое регистра В выводится в канал В адаптера 14.

Блок 3 алгоритма осуществляет ввод содержимого канала А адаптера 14 в аккумулятор микропроцессора 15. Далее блоком 4 анализируется состояние седьмого разряда регистра А, т.е. проверяется какой режим работы элементарного отрезка задан. Если в седьмом разряде - логическая 1, то элементарный отрезок работает в режиме станции, если логический О, то - в режиме блока-участка. Далее алгоритм распадается на две ветви. Первая ветвь по условию Да задает работу в режиме станции, вторая ветвь Нет определяет работу в режиме блока- участка .

5496

Работа элементарного отрезка в режиме станции осуществляется блоками 5-11 алгоритма. Блоком 5 в младший полубайт внутреннего регистра С микропроцессора переписывается из аккумулятора код заданного числа путей на станции. Блоком 6 анализируется занятость станции , т.е. занятость всех путей на станции. Если хотя бы один путь свободен, то блоком 7 алгоритма анализируется наличие сигнала разрешение передачи поезда на

10

F- станцию. Если F

равен логической 1,

5 блок 8 увеличивает на единицу со-

0

0

5

держимое старшего полубайта регистра В микропроцессора, в котором хранится число поездов, находящихся на станции. Блок 9 осуществляет вывод содержимого регистра В в канал В адаптера 14 и далее управление передается блоку 6. Если все пути на станции заняты, то в регистр В микропроцессора блоком 10 записывается сиг- 5 нал Р- , равный логической 1, имитирующий занятость станции, и сигнал К,., логической 1, имитирующий показание красного огня по позади лежащему блоку-участку, с последующим выводом содержимого регистра В в порт В адаптера 14 (блок 11),

Работа элементарного отрезка в режиме блока-участка осуществляется блоками 12-35 алгоритма. Блок 12 проверяет условие наличия сигнала.F,-- разрешения передачи поезда на данный блок-участок. Если F равен логическому О, то блоками 13-15 имитируются только показания светофорной сигнализации на позади лежащем блоке- участке: по условию проверки занятости впереди лежащего (1+1)го блока- участка (блок 13), Если (i+1)-и блок- участок занят, то блоком 14 имитируется желтый огонь на движение по (i-1)- му блоку-участку, если (1+1)-и блок- участок свободен, то - зеленый (блок 15). Блок 16 осуществляет вывод содержимого регистра В в канал В адаптера 14, а блок 17 вводит в аккумулятор новые текущие данные с соседних блоков-участков. Далее управление вновь передается блоку 12,

Если сигнал F- равен логической 1, т, е. на данный блок-участок поступает поезд, то блок 18 считывает из младшего полубайта аккумулятора в младший полубайт регистра С код времени движения поезда по данному

0

5

0

5

блоку-участку. Блоком 19 формируется сигнал Р,- , pasHbrii логической 1, имитирующий занятость, данного блока- участка, и сигнал К -1, равный логи- ческой 1, имитирующий показание

красного огня на движение по позади лeжaщe fy блоку-участку.

Блоками 20-24 алгоритма анализируется показание впереди стоящего

светофора на движение по данному бл ку-участку с занесением соответствущих констант CONST 1, CONST 2, CONS 3 по следующей логике:

., (CONST 1);

,4, P.г (CONST 2);

Z,.P,-M РП., (CONST 3).

Константы выбираются пропорционально значениям скоростей поездов, на показания красного, желтого или зеленого огня впереди стоящего светофора и заносятся в регистровую пару HL микропроцессора 15,

Блоком 25 осуществляется вывод содержимого регистра В в канал В адаптера 14.

Блоками 26-28 алгоритма имитируется процесс движения поезда по блоку- участку, основанному на программной задержке по константе, записанной в регистровой паре HL, уменьшение на единицу младшего полубайта регистра С микропроцессора 15 и анализа обнуления младшего полубайта регистра С. Если последний равен нулю, то на блоках 29 и 30 осуществляется ввод текущего состояния соседних блоков- участков и проверка: свободен ли впе35 тем, что, с целью расширения класс решаемых задач, в каждый блок обра ботки информации введены генератор случайных импульсов и коммутатор группа выходов которого соединен

реди лежащий блок-участок. Если впе- 0 с группой информационных входов

реди лежащий блок-участок занят , то алгоритм предусматривает зацикливание на блоках 29 и 30 до момента его .освобождения. Если впереди лежащий блок-участок свободен, то блоком 31 формируется сигнал Р , равньй логическому О, означающий, что данный блок-участок свободен, и сигнал F. , равный логической 1, означающий передачу поезда на следующий элементарный отрезок. Блок 32 выводит содержимое регистра В в канал В адаптера 14. Блоком 33 осуществляется программная задержка, определяемая

.операционного узла i-ro блока обра ботки информации, группа выходов ге ратора случайных импульсов i-ro

г

блока обработки информации соедине 45 с первой группой информационных вх дов коммутатора i-ro блока обработ информации, группа информационньк

входов i-ro блока обработки информ ции соединена с второй группой инф мационных входов коммутатора i-ro блока обработки информации, вход в бора режима i-ro блока обработки и формации соединен с управляющим вх

50

временем, необходимым на прием сигна- « дом коммутатора 1-го блока обработки ла т соседним элементарным отрез- информации, группа информационных ком. Далее блоками 34 осуществляется выходов операционного узла i-ro блока сброс сигнала F +1 и управление вновь обработки информации соединена с груп- передается на блок 17 алгоритма. пой информационных входов регистра iВ алгоритме не предусмотрен программный Конец, это предусмотрено для возможности продолжения сеанса моделирования при задании новой последовательности поездов на вход F устройства. Конец процесса моделирования осуществляется переключением тумблера, задающего сигнал Пуск.

изобретения

о р м у л а

I.Вычислительная система, содержащая N блоков обработки информации (N6 2.; ..) каждый из которых содержит oпepaциoJнный узел и регистр, причем i-я (,N) группа кодовых входов системы соединена с группой информационных входов i-ro блока обработки информации, i-й управляющий

вход системы соединен с входом выбора режима iro блока обработки информации, стробирующий выход j -го блока обработки информации (,N-1) соединен со стробирующим входом (j + 1)го блока обработки информации, пер-- вый информационньй выход регистра i- го блока обработки информации является стробирующим выходом i-ro блока обработки информации, вход выбора режима i-ro блока обработки информации соединен с входом записи регистра и первым информационным входом операционного узла i-ro блока обработки информации, отличающаяся

тем, что, с целью расширения класса решаемых задач, в каждый блок обработки информации введены генератор случайных импульсов и коммутатор, группа выходов которого соединена

с группой информационных входов

.операционного узла i-ro блока обработки информации, группа выходов генератора случайных импульсов i-ro

г

блока обработки информации соединена 5 с первой группой информационных входов коммутатора i-ro блока обработки информации, группа информационньк

входов i-ro блока обработки информации соединена с второй группой информационных входов коммутатора i-ro блока обработки информации, вход выбора режима i-ro блока обработки информации соединен с управляющим вхо0

го блока обработки информации, группа информационных выходов которого является i-й группой информационных выходов системы, выход вывода информации операционного узла i-ro блока обра- ботки информации соединен с тактовым входом регистра i-ro 6jiOKa обработки информации, второй информационный выход которого Соединен с i-и информационным входом блока вывода, второй информационный выход регистра К-го блока обработки информации ( N) соединен с вторым информационным входом операционного узла (К-1)-го блока обработки информации, второй ин- формационньй вькод регистра т го блока обработки информации ( N) соединен с третьим информационным входом операционного узла (т-2)-го блока обработки информации, вход сброса системы соединен с входами сброса операционных узлов и регистров всех блоков обработки информации, вход установки системы соединен с входами пуска операционных узлов всех блоков обработки информации, стробирутощий вход первого блока обработки информации является входом текущих условий системы

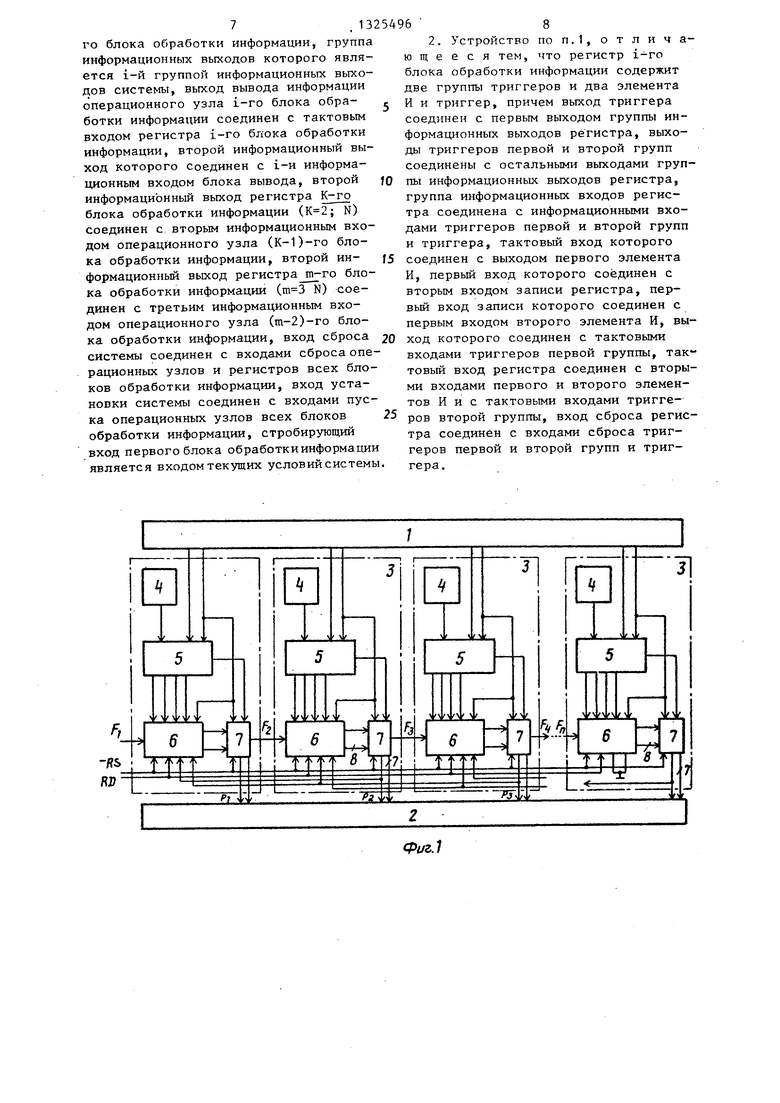

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что регистр i-ro блока обработки информации содержит две группы триггеров и два элемента И и триггер, причем выход триггера соединен с первым выходом группы информационных выходов регистра, выходы триггеров первой и второй групп соединены с остальньми выходами группы информационных выходов регистра, группа информационных входов регистра соединена с информационными входами триггеров первой и второй групп и триггера, тактовый вход которого соединен с выходом первого элемента И, первьш вход которого соединен с вторым входом записи регистра, первый вход записи которого соединен с первым входом второго элемента И, выход которого соединен с тактовыми входами триггеров первой группы, товый вход регистра соединен с вторыми входами первого и второго элементов И и с тактовыми входами триггеров второй группы, вход сброса регистра соединен с входами сброса триггеров первой и второй групп и триггера.

(//аудио 3

Г .,

А /

/ nopm(Jr(A}/

Щ1г.з)А(0,1.

Г 7

1поргп0 W(

г /

/(Л} порт 00/

(

J8

W.z.3hA(f,)

19

{g(g,

i

, .-/5-1

|д(й;. I - i

1

.«

HemJZ/&L MAM3}/ cmsf) )

,. 1/((( порт 00/

-25/ pn J(}(

g

I ,

/iv)pm0t- (A)(B}/ ()/

L

HemJZ-25/ pn J(}(

I 5(3,; 01

/wpm0h (A)(8/

r-33 i Wpozp. задержка

- yj ,

35-jL. /flopm0f -((B)/

r

.26.

I

адержка no (HL)

Hem

Фаь. 3

Составитель М.Сорочан Редактор Л.Гратилло Техред Л.Сердюкова Корректор Н,Король

--- -- ---- --- -«- --- ----.-----...--.--.--.-.-...fc «.«i. и.-. ..--.- ....-.«.,,,,.

Заказ 3111/45 Тираж 672 Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1314350A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОДВИГАТЕЛЕМ СУДОВОЙ ЛЕБЕДКИ | 1994 |

|

RU2074501C1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для моделирования динамики транспортного потока | 1983 |

|

SU1116441A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

Изобретение относится к вычислительной технике, в частности к системам распределенной обработки информации, и может быть использовано для построения вычислительных сетей с локально распределенными ресурса- - ми. Цель изобретения - расширение класса решаемых задач. Вычислительная систему содержит блоки ввода, вывода и обработки информации, каждый из которых состоит из генератора случайных импульсов, коммутатора, операционного узла и регистра. Система позволяет за счет реализации нового .алгоритма работы моделировать транспортный поток на участках железных дорог. При этом каждый блок обработки информации моделирует в зависимости от условий, подаваемых на него с блока,либо элементарный блок-участок дороги, либо станцию. Информация о состоянии данного участка фиксируется блоком вывода. 1 з.п. ф-лы, 3 ил. Л

| Устройство для моделирования динамики транспортного потока | 1983 |

|

SU1116441A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4428048, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1985-11-18—Подача