j-x триггеров захвата и к входам второго элемента ИЛИ, выход которого подключен к первому входу пятого элемента ИЛИ, выход которого подключен к входу установки триггера признака занятости, выход которого является выходом признака занятости адаптера, j-e входы освобождения памяти адаптера подключены к входам сброса соответствующих j-x триггеров захвата и к входам третьего элемента ИЛИ, выход которого подключен к первому входу шестого элемента ИЛИ и к входу установки триггера признака передачи, выход которого является выходом признака передачи адаптера, выход счетчика, через одновибратор подключен к второму входу шестого элемента ИЛИ, выход которого подключен к входу сброса триггера признака занятости, j-e входы признака передачи адаптера соединены с входами четвертого элемента ИЖ, выход которого подключен к входу сброса триггера признака передачи, к второму входу пятого элемента ИЛИ и к входу записи счетчица.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1988 |

|

SU1589287A1 |

| Устройство связи для вычислительной системы | 1986 |

|

SU1315990A1 |

| Устройство для сопряжения К процессоров с М периферийными устройствами | 1987 |

|

SU1432536A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения интерфейсов ввода-вывода с регистратором | 1987 |

|

SU1413636A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

УСТРОЙСТВО ДЛЯ СВЯЗИ ПРОЦЕССОРОВ, содержащее m блоков памяти, m адаптеров, блок синхронизации, первый выход которого подключен к входам синхронизации адаптеров, первый информационный вход-выход i-ro адаптера (,т) подключен к входу-выходу i-ro блока памяти, .п буферных регистров кода управления, где п - количество подключаемых процессоров вход j-го буферного регистра (j r,n) кода управления подключен к .одноименному выходу канала ввода-вывода j-ro процессора, отличающееся тем, что, с целью повьшения производительности обработки информации за счет обмена информацией через блоки памяти общего доступа, в него введены регистр состояния и 11 блоков вывода сигналов управления,выход j-ro буферного регистра подключен к J-M входам кода управления всех адаптеров, вход j-ro блока вывода сигналов управления подключен к выходу управления канала ввода-вывода j-ro процессора, ()-й выход блока синхронизации и (j+l)-й информационный выход всех адаптеров подключены к входу синхронизации канала ввода-вьшода j-ro процессора, выход признака занятости и выход признака передачи i-ro -адаптера подключены к соответствующим входам регистра состояний, выход которого подключен к информационным входам . каналов ввода-вывода всех процессоров, i-e выходы захвата памяти, освобождения памяти, признаки передачи j-ro блока вывода сигналов уп- . равления подключены к одноименным J-M входам i-ro адаптера,причем каж-дый адаптер содержит с первого по шестой элементы ИЛИ, элемент И, i. счетчик, одновибратор, триггер приз|(Л нака занятости, триггер признака передачи, п триггеров захвата, п коммутаторов, первые входы-выходы которых объединены и являются первым информационным входом-выходом адаптера, вторые входы-выходы комму--: таторов являются (j+l)-MH информа(;о ционными входами-выходами адаптера со и подключены к информационным вхоО) дам-выходам каналов ввода-вывода j-ro процессора соответсвенно, вход 00 1С управления j-ro коммутатора подключен к выходу J-TO триггера захвата j-e входы кода управления адаптера соединены с входами первого элемента ИЛИ, выход которого подключен, к информационному входу счетчика, вход синхронизации которого подключен к выходу элемента И, первый и второй входы которого соединены с входом синхронизации и с выходом счетчика соответственно, j-e входы захвата памяти адаптера подключены к входам установки соответствующих

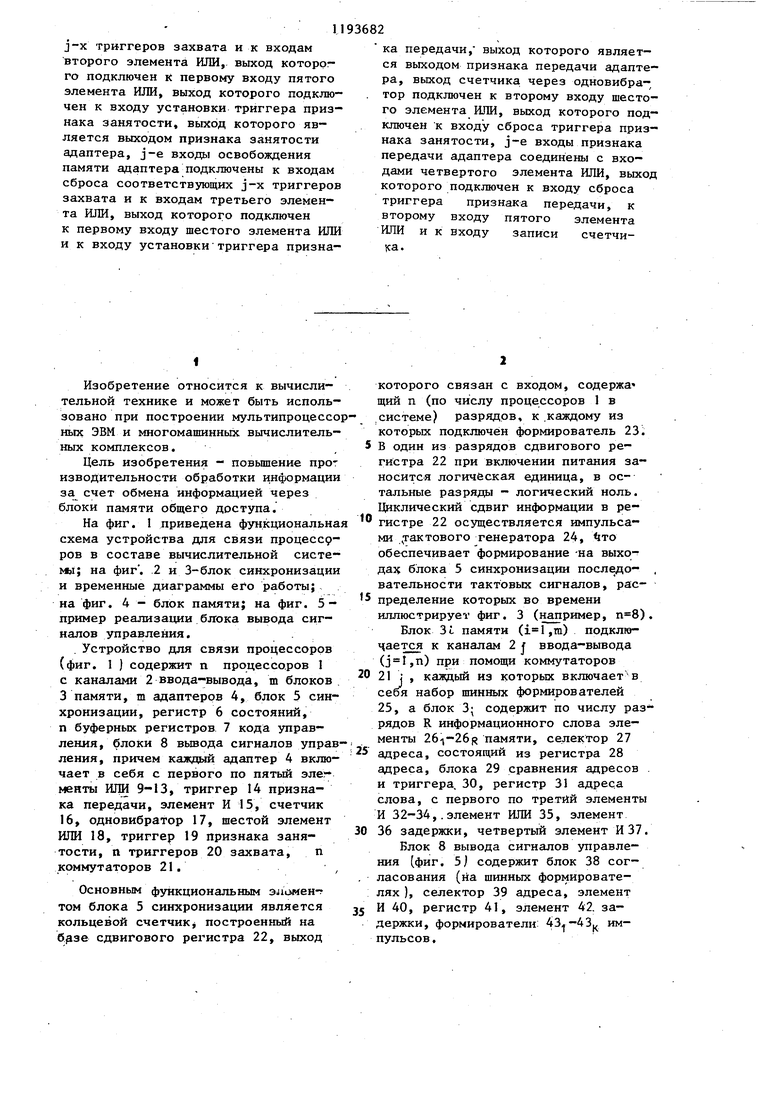

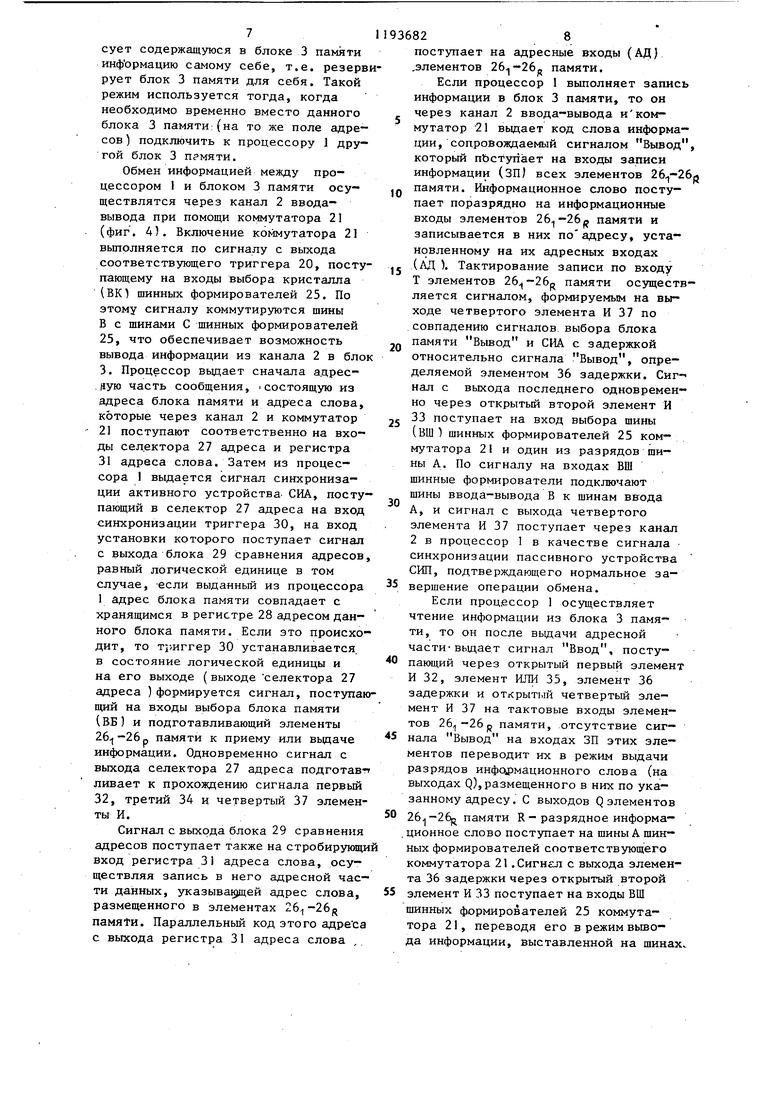

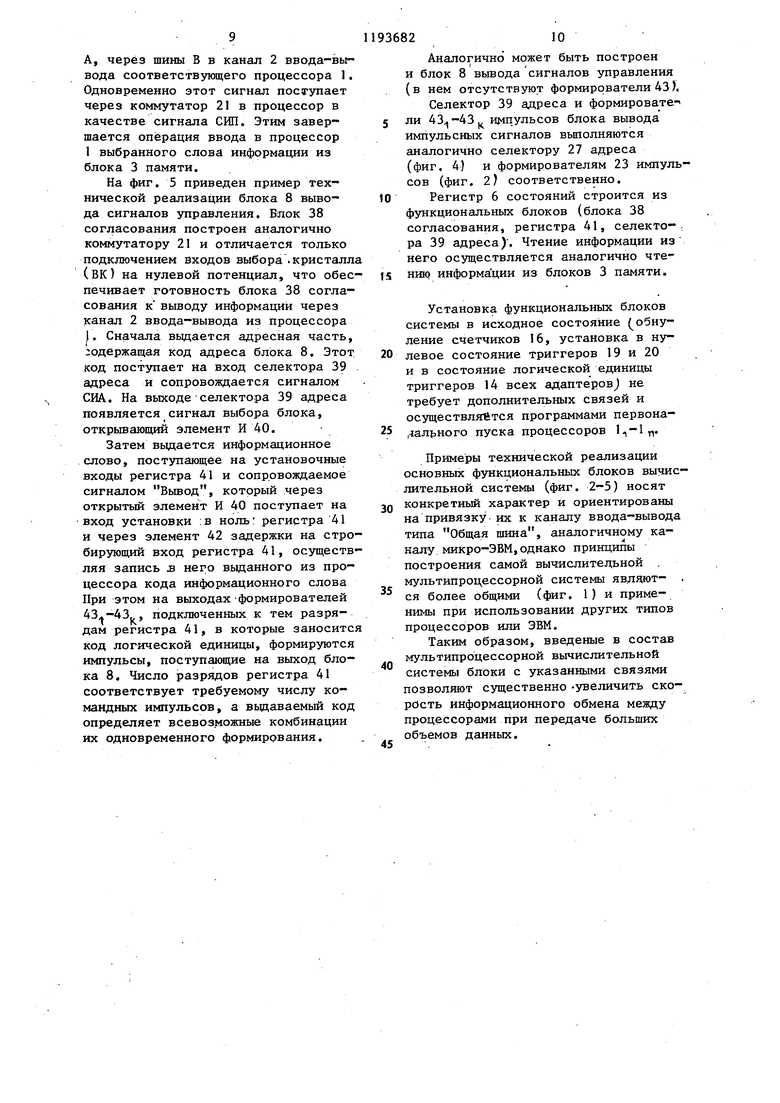

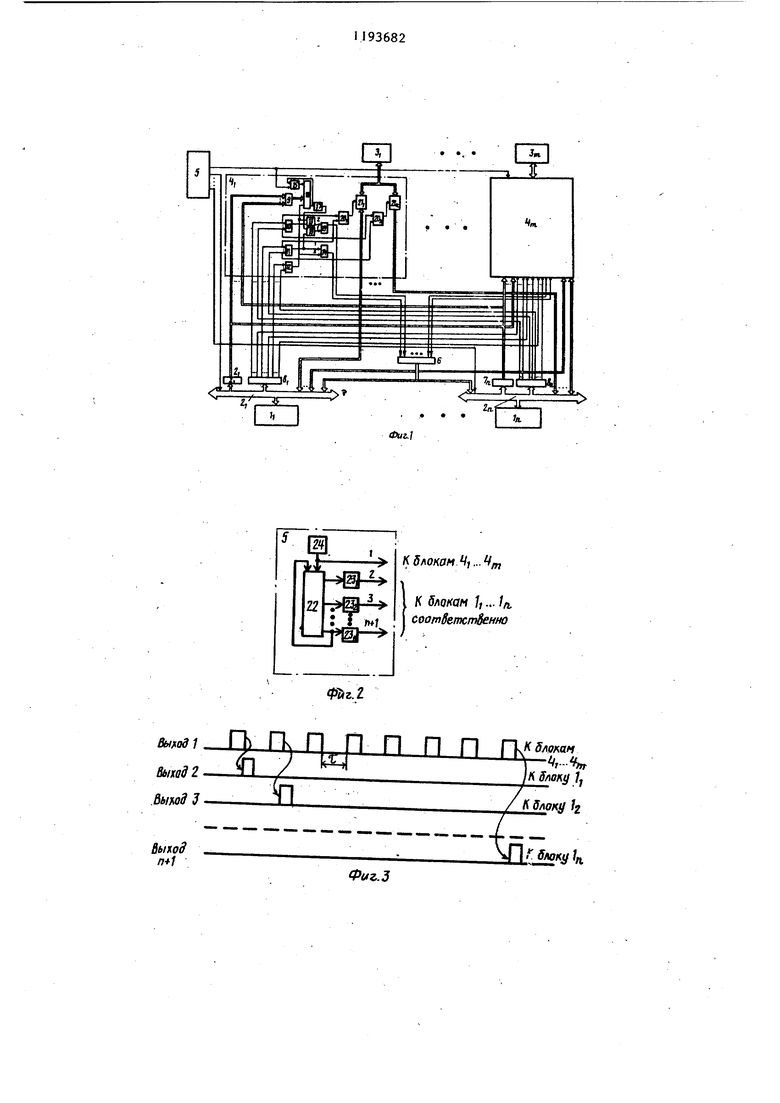

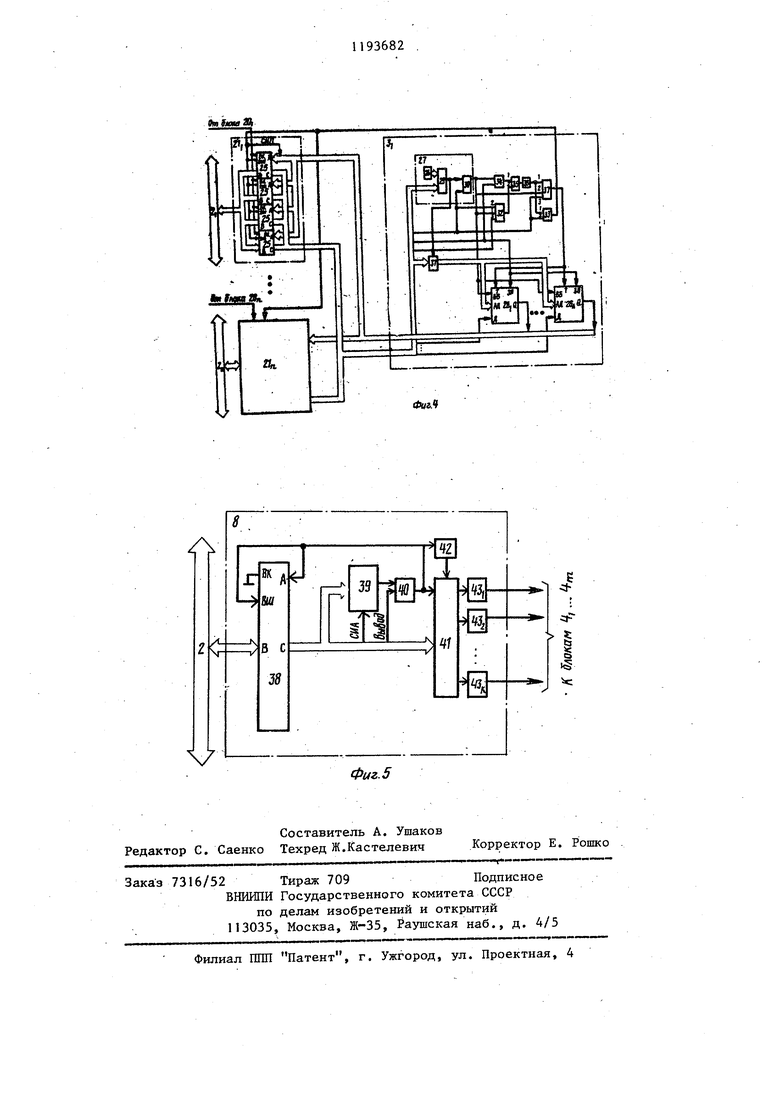

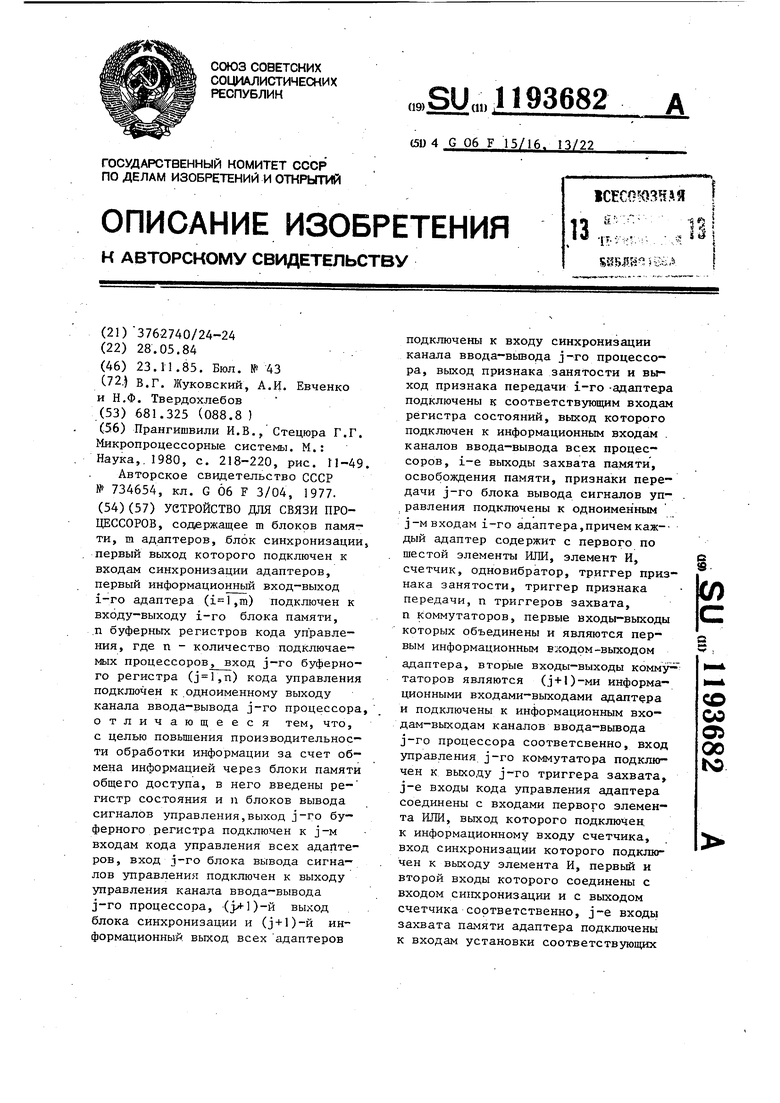

Изобретение относится к вычислительной технике и может быть использовано при построении мультипроцессо ных ЭВМ и многомашинных вычислительных комплексов. Цель изобретения - повьшение про изводительности обработки информации за счет обмена информацией через блоки памяти общего доступа. На фиг. 1 приведена функциональна схема устройства для связи процессф ров в составе вычислительной системд; на фиг . 2 и 3-блок синхронизации и временные диаграммы его работы; на фиг. 4 - блок памяти; на фиг. 5пример реализации блока вывода сигналов управления.. Устройство для связи процессоров (фиг. 1 ) содержит п процессоров 1 с каналами 2 ввода-вывода, m блоков 3 памяти, m адаптеров 4, блок 5 синхронизации, регистр 6 состояний, п буферных регистров 7 кода управления, блоки 8 вьшода сигналов управ ления, причем каждый адаптер 4 включает в себя с первого по пятый элементы ИЛИ 9-13, триггер 14 признака передачи, элемент И 15, счетчик 16, одновибратор 17, шестой элемент ИЛИ 18, триггер 19 признака занятости, п триггеров 20 захвата, п коммутаторов 21. Основным функциональным эломен- том блока 5 синхронизации является кольцевой счетчикj построенный на сдвигового регистра 22, выход которого связан с входом, содержа щий п (по числу процессоров 1 в .системе) разрядов, к .каждому из которых подключён формирователь 23. В один из разрядов сдвигового регистра 22 при включении питания заносится логическая единица, в остальные разряды - логический ноль. Циклический сдвиг информации в регистре 22 осуществляется импульсами тактового генератора 24, то обеспечивает формирование -на выходах блока 5 синхронизации последо- , вательности тактовых сигналов, распределение которых во времени иллюстрирует фиг. 3 (например, ). Блок 3i. памяти (,т) подключается к каналам 2 j ввода-вывода (,n) при помощи коммутаторов 21 j , кавдый из которых включает в себя набор шинных формирователей 25, а блок 3; содержит по числу разрядов R информационного слова элементы памяти, се.лектор 27 адреса, состоящий из регистра 28 адреса, блока 29 сравнения адресов и триггера, 30, регистр 31 адреса слова, с первого по третий элементы И 32-34,.элемент ИЛИ 35, элемент 36 задержки, четвертый элемент И 37. Блок 8 вывода сигналов управления фиг. 5) содержит блок 38 согласования (на шинных формирователях ), селектор 39 адреса, элемент И 40, регистр 41, элемент 42. задержки, формирователи: 43|-43( импульсов . Устройство,работает следующим образом. В системе одиовременно реализует ся несколько (по числу процессоров вычислительных процессов, связанных либо со сбором и обработкой измерительной информации, либо с решением задачи, представленной в виде последовательно-параллельного алгоритма. Например, в информационно-измерительной системе один из процессоров (ЭВМ } может выполнять текущий сбор, допусковьй контроль технологических или электрофизиологических сигналов, а также формиров ние их массивов, другой процессор осуществляет первичную обработку сфорь1ированных ранее первым процесс ром массивов данных ( вьщеление информационных признаков, перекомпо новку данных с привязкой к базовому времени ), а третий процессор выполт няет статическую обработку перекомп .нованных массивов данных, вычисление и вывод для визуального отоб«1 ражения обобщенных показателей состояния .контролируемого объекта. Связь между процессорами (ЭВМ) осуществляется по информации, имеющей зачастую значительный объем. При этом каждый процессор (ЭВМ) осн щается необходимым объемом индивидуальной оперативной памяти, требуемым набором устройств ввода-вывода и отображения информации (н. фиг. 1 не показан1з1 ). Передача инфор мации между процессорами осуществля ся по принципу почтового ящика) в качестве которого используются доступные для всех процессоров Ц-1 блоки 3i-3f. Динамическое распределение блоко памяти между процессорами осу ществляется по тактовым сигналам блока 5 синхронизации, формируемым циклически и поочередно на 2-(п+1)выходах данного блока с периодом t, который может быть равен среднему д всей вычислительной системы значени промежутка времени между соседними обращения1)и процессоров к блокам памяти. По тактовому сигналу с (j+l)-ro выхода (,n) блока 5, поступающему через канал 2j в j-й процессор 1j, последний прерывает свою работу считывает и анализирует содержимое регистра 6 состояния. Содержимое регистра 6 определяется состоянием 24 триггеров 19 и 14 соответственно признака занятости и признака передачи адаптеров ,, за каждым из которых в регистре 6 закреплено по два разряда (первый - за признаком занятости, второй - за признаком переда чи ). Наличие логических нулей в обоих разрядах, закрепленных за i-M (,m) адаптером 4, свидетельствует о том, что соответствующий i-й блок 3 памяти свободен для записи. Если оба разряда находятся в состоянии логической единицы, это свидетельствует о том, что соответствующий блок памяти содержит информацию, адресованную другому процессору, а не тому, в кото- рьш поступает тактовый сигнал. Если только первый из разрядов находится в состоянии логической единицы, это является признаком занятости соответствующего блока памяти обменом с другим процессором. Если в состоянии логической единицы находится только второй разряд, это является признаком того, что соотвествующий блок памяти содержит информацию, адресованную данному процессору. В зависимости от перечисленных вариантов содержимого регистра 6 состояния возможны следующие режи- мы обмена процессора информацией с блоками памяти. Режим Запись-чтение, в этот режим обмена процессор 1 вступает при наличии незанятых блоков/памяти (состояние логического нуля соответствующих разрядов регистра 6) при необходимости расширения объема оперативной памяти данного процессора или при возникновении потребности в хранимой в этом блоке информации (например, общей для всей системы библиотеки под- программ ). При этом процессор может захватить от одного до нескольких блоков памяти. Пусть таким свободным блоком памяти является первый блок 3 памяти, а тактовый сигнал поступает в первый процессор 1, которому требуется расширение оперативной памяти. По тактовому сигналу процессор 1, посыпает в блок 8 код, по которому на первом выходе первой группы его выходов формируется импульс захвата, поступающий на первый вход триггера 20i первого адаптера 4. Триггер 20 ,переклЛ)Чившись, подключает при помощи коммутатора 2 Ц блок 3 памяти к каналу 2 ввода-вывода процессора Ц , обеспечивая тем самым возможность двустороннего обмена информацией между ними. Импульс захвата одновременно, поступает через второй 10 и пятый 13 элементы ИЛИ на вход установки триггера 19, который, переключившис подает в регистр 6 состояния призна занятости блока 3 памяти, который сохраняется вплоть до окончания обм на информацией между процессором 1 и блоком 3., памяти. По окончании об мена процессор Ц посылает в блок 8 код, по которому на первом выход второй группы его выходов формирует ся импульс освобождения памяти,пост пакхций на вход сброса триггера 20 который, переключивпшсь, отключает при помощи коммутатора 21 блок 3. памяти от канала 2 процессора 1 . Одновременно импульс освобождения памяти поступает через третий Пи шестой 18 элементы ИЛИ на вход сбро са триггера 19 признака занятости, который, переключившись, передает в регистр 6 состояния системы признак освобождения блока 3 памяти. Количество одновременно подключаемых к данному процессору 1.- блоко 3. памяти определяется отведенным дпя такого подключения полем адресов процессора. Режим Передача. Этот режим обмена отличГается от указанного тем, что по завершении заполнения данными захваченного блока 3 памяти процессор 1 адресует данный блок, памяти определенному другому процессору. Адресация осуществляется при поступлении очередного тактового сигнала в процессор 1 , по которому он через буферный регистр 7 и первый элемент ИЛИ 9 первого адапте ра 4 ввдает относительный дополнительный код числа, равного месту адресуемого процессора относительно данного (в данном примере первого ) адресующего процессора. Этот код поступает на информационны входы счетчика 16. Затем процессор 1 в блок 8 вьщает код, по которому формируется импульс освобоядв ния блока памяти, отключающий блок памяти 3. от процессора Ц. Последний выдает в блок 8 код, по которо2му формируется импульс передачи, поступающий через четвертый элемент ШШ 12 на вход сброса триггера 14 I признака передачи, который переключившись, передает в регистр 6 состояния системы признак передачи информации,, записанной в блок 3 памяти. Одновременно импульс передачи с выхода четвертого элемента ИЛИ 12 поступает через пятый элемейт ИЛИ 13 на вход установки триггера 19 признака занятости и вход записи счетчика 16. Триггер 19, переключившись, передает в регистр 6 состояния признак занятости блока памяти. По сигналу, поступившему на вход записи счетчика 16, в него заносится дополнительный код относительного адреса процессора-получателя информации. При этом на выходе счетчика 16 появляется сигнал ненулевого состояния, который открьгоает первый элемент И 15 для прохождения тактовых импульсов с первого выхода бло- ка 5 синхронизации на счетный вход счетчика 16. Прохождение тактовых импульсов с первого выхода блока 5 синхронизации на вход синхронизации счетчика 16 продолжается до его обнуления, что происходит одновременно с моментом поступления тактового сигнала прерывания работы адресуемого процессора. При этом сигнал обнуления счетчика 16 поступает на вход первого элемента И 15 и вход одновибратора 17. Элемент И 15 запирается, и поступление тактовых импульсов на вход с инхронизации счетчика 16 прекращается. На выходе одновибратора 17 формируется импульс, который через шестой элемент ШШ 18 поступает на вход сброса триггера 19 признака занятости. Триггер 19, переключившись, снимает признак занятости блока 3 памяти (оставляя неизменным признак передачи ), поэтому адресуемьй процессор 1. распознает, что содержащиеся в блоке 3 памяти данные предназначены ему,и переходит к обмену информацией с ним в режиме Записьчтение. Режим Резервирование. Этот режим отличается-от режима Передача , тем, что в счетчик 16 заносится дополнительный код числа процессоров 1 в вычислительной системе. Это означает, что данный процессор 1 адресует содержащуюся в блоке 3 памяти информацию самому себе, т.е. резерв рует блок 3 памяти для себя. Такой режим используется тогда, когда необходимо временно вместо данного блока 3 памяти:(на то же поле адресов) подключить к процессору 1 другой блок 3 прмяти. Обмен информацией между процессором I и блоком 3 памяти осуществлятся через канал 2 вводавывода при помощи коммутатора 21 (фиг. 4). Включение коммутатора 21 выполняется по сигналу с выхода соответствующего триггера 20, посту пающему на входы выбора кристалла (ВК) шинных формирователей 25. По этому сигналу коммутируются шины В с шинами С шинных формирователей 25, что обеспечивает возможность вывода информации из канала 2 в бло 3. Процессор выдает сначала адрес. №ую часть сообщения, состоящую из адреса блока памяти и адреса слова, которые через канал 2 и коммутатор 21 поступают соответственно на входы селектора 27 адреса и регистра 31 адреса слова. Затем из процессора I выдается сигнал синхронизации активного устройства- СИЛ, посту пающий в селектор 27 адреса на вход синхронизации триггера 30, на вход установки которого поступает сигнал с выхода блока 29 сравнения адресов равный логической единице в том случае, -если выданный из процессора 1 адрес блока памяти совпадает с хранящимся в регистре 28 адресом данного блока памяти. Если это происхо дит, то тгиггер 30 устанавливается, в состояние логической единицы и на его выходе (выходе селектора 27 адреса ) формируется сигнал, поступа щий на Входы выбора блока памяти (ВБ) и подготавливающий элементы памяти к приему или вьщаче информации. Одновременно сигнал с выхода селектора 27 адреса подготав ливает к прохождению сигнала первый 32, третий 34 и четвертый 37 элемен ты И. Сигнал с выхода блока 29 сравнения адресов поступает также на стробирующ вход регистра 31 адреса слова, осуществляя запись в него адресной час ти данных, указыварцей адрес слова, размещенного в элементах памяти. Параллельный код этого адрес с выхода регистра 31 адреса слова поступает на адресные входы (АД) ,элементов памяти. Если процессор 1 выполняет запись информации в блок 3 памяти, то он через канал 2 ввода-вывода икоммутатор 11 выдает код слова информации, сопровождаемый сигналом Вывод, который пЬступает на входы записи информации (ЗП) всех элементов памяти. Информационное слово поступает поразрядно на информационные входы элементов (j памяти и записывается в них поадресу, установленному на их адресных входах (ЛД ). Тактирование записи по входу Т элементов памяти осуществляется сигналом, формируемым на выходе четвертого элемента И 37 по совпадению сигналов, выбора блока памяти Вьшод и СИЛ с задержкой относительно сигнала Вывод, определяемой элементом 36 задержки. Сиг нал с выхода последнего одновременно через открытый второй элемент И 33 поступает на вход выбора шины (ВШ ) шинных формирователей 25 коммутатора 21 и один из разрядов шины А. По сигналу на входах ВШ шинные формирователи подключают шины ввода-вывода В к шинам ввода А, и сигнал с выхода четвертого элемента И 37 поступает через канал 2 в процессор 1 в качестве сигнала синхронизации пассивного устройства СИП, подтверждающего нормальное завершение операции обмена. Если процессор 1 осуществляет чтение информации из блока 3 памяти, то он после выдачи адресной части-выдает сигнал Ввод, поступающий через открытый первый элемент И 32, элемент ИЛИ 35, элемент 36 задержки и открытый четвертый элемент И 37 на тактовые входы элементов 26.,-26р памяти, отсутствие сигнала Вывод на входах ЗП этих элементов переводит их в режим выдачи разрядов информационного слова (на выходах Q),размещенного в них по указанному адресу. С выходов Qэлементов 26 -26jj памяти R - разрядное информационное слово поступает на шины А шинных формирователей соответствующего коммутатора 21 .Сигнгл с выхода элемента 36 задержки через открытый второй элемент И 33 поступает на входы ВШ шинных формирователей 25 коммутатора 21, переводя его в режим вьшо- да информации, выставленной на шинахА, через шины В в канал 2 ввода-вывода соответствующего процессора 1. Одновременно этот сигнал поступает через коммутатор 21 в процессор в качестве сигнала СИП. Этим завершается операция ввода в процессор 1 выбранного слова информации из блока 3 памяти.

На фиг. 5 приведен пример технической реализации блока 8 вывода сигналов управления. Блок 38 согласования построен аналогично коммутатору 21 и отличается только подключением входов выбора .кристалл (ВК) на нулевой потенциал, что обеспечивает готовность блока 38 согласования к выводу информации через канал 2 ввода-вывода из процессора |. Сначала выдается адресная часть, ::одержащая код адреса блока 8. Этот код поступает на вход селектора 39 адреса и сопровождается сигналом СИЛ. На выходе селектора 39 адреса появляется сигнал выбора блока, открывающий элемент И 40.

Затем вьщается информационное слово, поступающие на установочные входы регистра 41 и сопровождаемое сигналом Вывод, который через открытый элемент И 40 поступает на вход установки :в ноль г регистра 41 и через элемент 42 задержки на стробирующий вход регистра 41, осуществляя запись S него вьщанного из процессора кода информационного слова При этом на выходах формирователей ., подключенных к тем разрядам регистра 41, в которые заноситс код логической единицы, формируются импульсы, поступакнцие на выход блока 8. Число разрядов регистра 41 соответствует требуемому числу командных импульсов, а вьщаваемый код определяет всевозможные комбинации их одновременного формирования.

Аналогично может быть построен и блок 8 вывода сигналов управления (в нем отсутствуют формирователи 43), Селектор 39 адреса и формирователи импульсов блока вывода импульсных сигналов выполняются аналогично селектору 27 адреса (фиг. 4) и формирователям 23 импульсов (фиг. 2) соответственно.

0 Регистр 6 состояний строится из функциональных блоков (блока 38 согласования, регистра 41, селекто-, ра 39 адреса). Чтение информации из него осуществляется аналогично чте

5 НИН) информации из блоков 3 памяти.

Установка функциональных блоков системы в исходное состояние (обнуление счетчиков 16, установка в нулевое состояние триггеров 19 и 20 и в состояние логической единицы триггеров 14 всех адаптеров не требует дополнительных связей и осуществляется программами первона5 дального пуска процессоров Ц-1„.

Примеры технической реализации основных функциональных блоков вычислительной системы (фиг. 2-5) носят Q конкретный характер и ориентированы на привязку- их к каналу ввода-вывода типа Общая шина, аналогичному каналу. микро-ЭВМ, однако принципы построения самой вычислительной . мультипроцессорной системы являют- . ся более общими (фиг. 1) и применимы при использовании других типов процессоров или ЭВМ.

Таким образом, введеные в состав мультипроцессорной вычислительной системы блоки с указанными связями позволяют существенно -увеличить скорость информационного обмена между процессорами при передаче больших

объемов данных. 5 .

- Ш1-; 1И-

22

jLjyij-

ГЬ Пч П П п п П П

5

и

Л

.ЧП/ft

- -K5flOKaM4i...ff,

К блокам 1,... /л coofnffemcmSeffHO

./f З/оукац

г-Лг Л 7,

г

7

к Злакя h

urjAai lfln

Фиг-З

вт1ммЯ

ФагА

| Прангишвили И.В., Стецюра Г.Г | |||

| Микропроцессорные системы | |||

| М.: Наука, | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-28—Подача