Изобретение относится к вычислительной технике и может быть использовано для генерирования на требуемом периоде случайных последовательностей с заданными частотными свойствами, определяемыми исходной матри цей частот.

Целью изобретения является расширение функциональных возможностей за счет формирования случайных последовательностей, отвечающих произволь ной заданной в явном виде матрице частот.

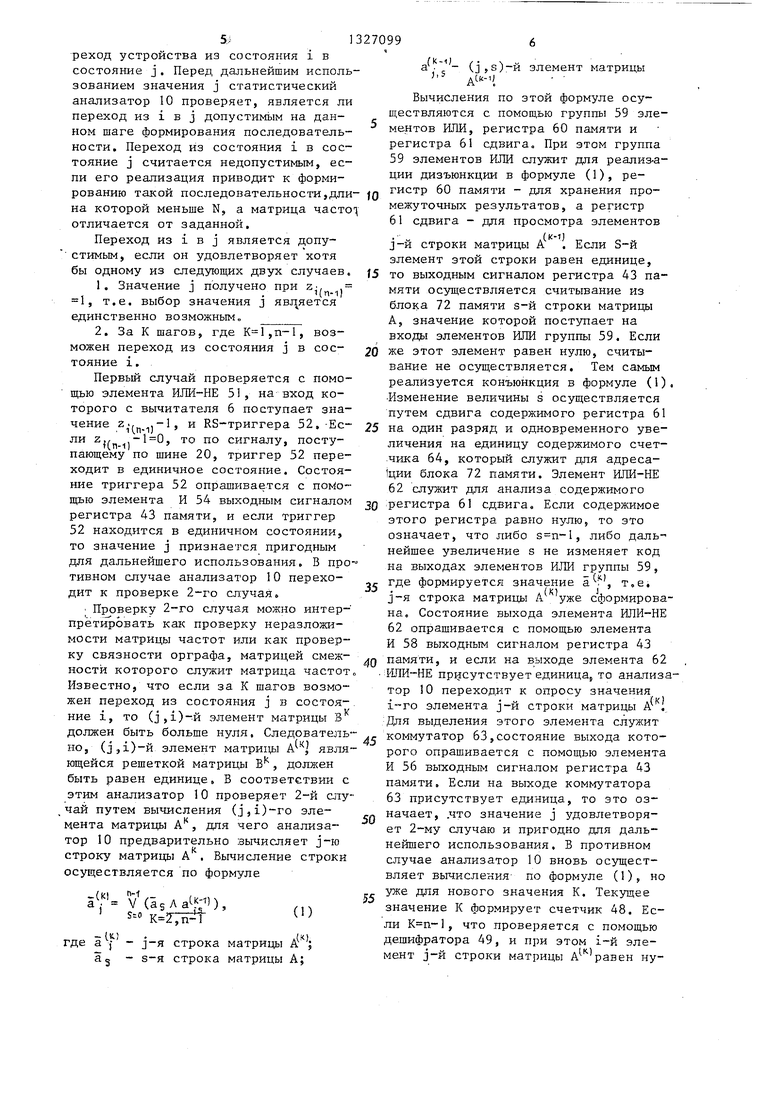

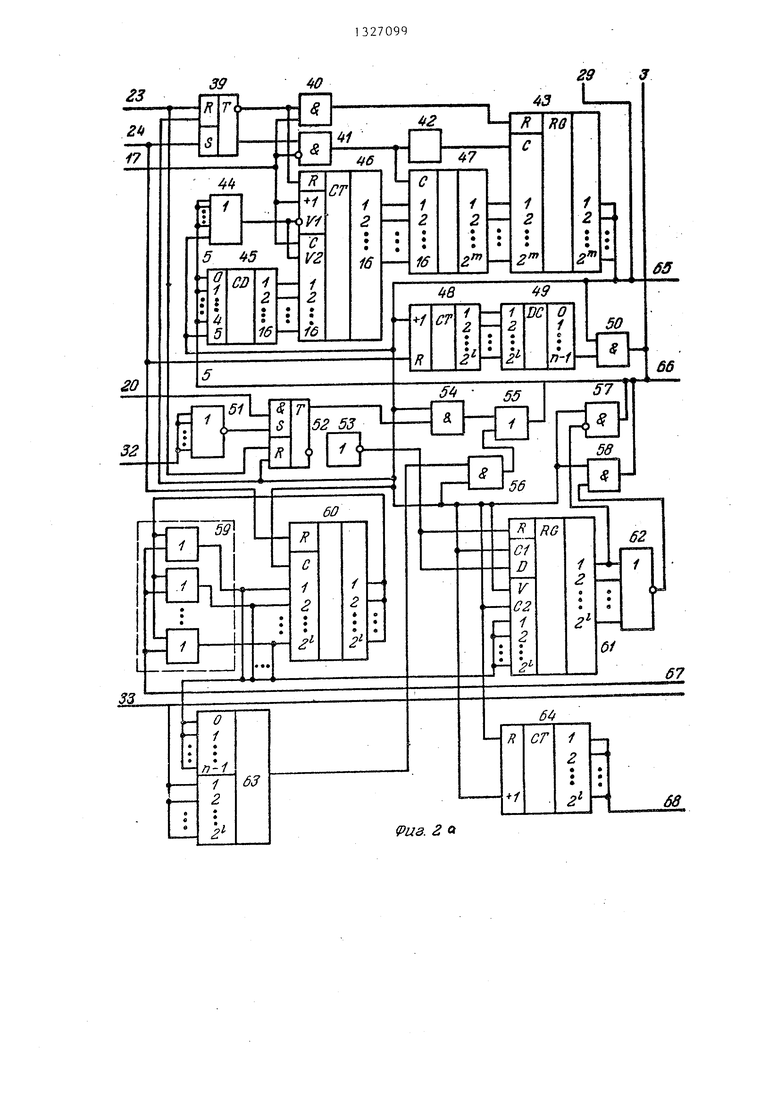

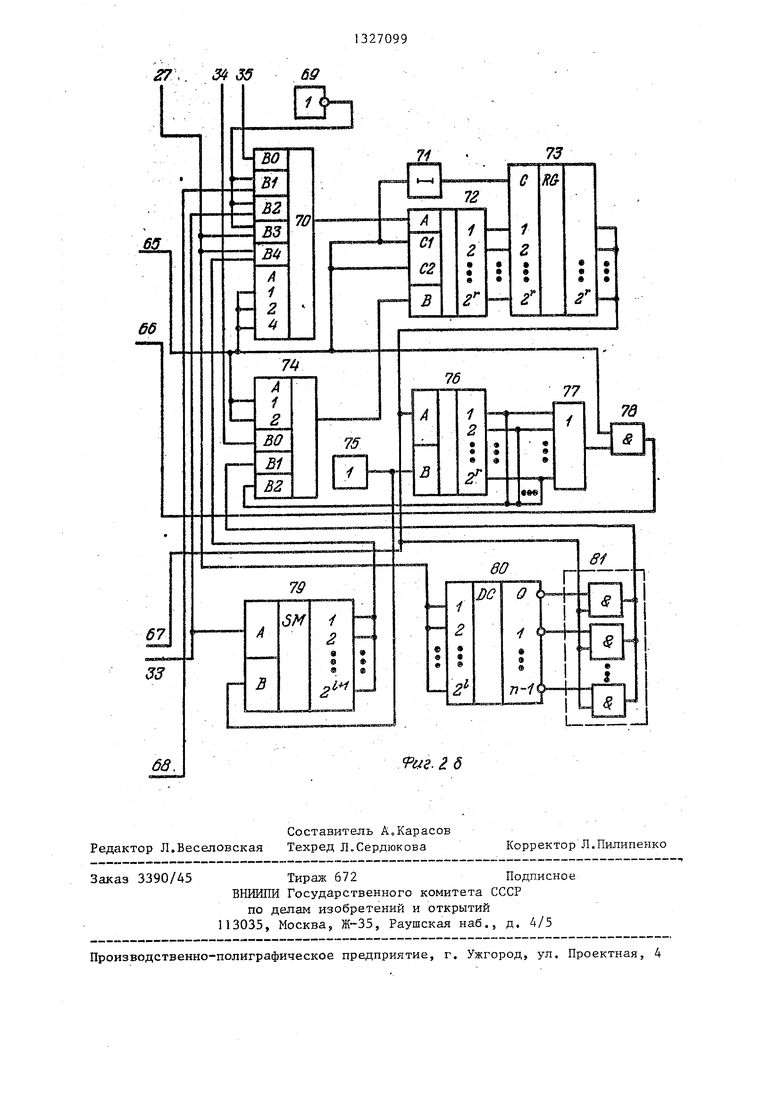

На фиг. 1 изображеМа блок-схема генератора; на фиг. 2(а,б) -схема статистического анализатора.

Предлагаемое устройство содержит генератор 1 тактовых импульсов, датчик 2 случайных двоичных равномерно распределенных чисел, блок 3 задания диапазона случайных чисел, блок 4 выделения значащих разрядов числа, группу 5 элементов И, вычитатель 6, группу 7 элементов И, вероятност- ный преобразователь 8, блок 9 задания функции распределения, статистический анализатор 10, элемент ИЛИ 11 коммутаторы 12 и 13, регистр 14 па

Продолжение таблицы

8

8

Q

5

0

5

14

16

16

8

18Вход случайных чисел

18То же

20Запуск

20Конец цикла

22 Задание кода адреса максимального случайного числа

21Запуск

30 Вход записи 30 Конец цикла 34 Значения матрицы частот

38 А,црес значений накопленных частот

26 Дцресный вход

Значения накопления частот

Режим вывода данных

Информационный вход

Результат преобразования

Запуск

Годен

Негоден

Установка нуля

Вход тактовых импульсов

Запись результата анализа максимального значения накопленной частоты

Максимальное значение накопленной частоты

Вход первого случайного числа

Вход второго случайного числа

Запуск

1327099

таблицы

вы nмецы ет де

16 35 Адрес значений частот

Статистический анализатор (фиг.2а, б) содержит RS-триггер 39, элемент И 40, элемент 41 Запрет, элемент 42 задержки, регистр 43 памяти, мент 44 ИЛИ, шифратор 45, счетчик 46, обладающий возможностью записи параллельного кода, блок 47 постоянной памяти, счетчик 48, дешифратор 49, элемент И 50, элемент ИЛИ-НЕ 51, RS- триггер 52, у которого S-входы объединены по И, источник 53 логического нуля, элемент И 54, элемент ИЛИ 55, элемент И 56, элемент 57 ЗАПРЕТ, элемент И 58, группу 59 элементов ИЛИ, регистр 60 памяти, регистр 61 сдвига.

осуществляющий сдвиг в сторону младших разрядов, элемент ИЛИ-НЕ 62, ком мутатор 63, счетчик 64, связи 65-68 между элементами блока, источник 69 лргического нуля, коммутатор 70, элемент 71 задержки, блок 72 оперативной памяти, регистр 73 памяти, комму татор 74, источник 75 логической единицы, вычитатель 76, элемент ИЛИ 77, элемент И 78, сумматор 79, дешифратор 80 и группу 81 элементов И

Устройство работает следующим образом.

Структуру последовательности задают в виде неразложимой неотрицательной целочисленной п -п-матрицы B(b,-j), i,,n-l, где п - количество букв (чисел, состояний),из которых формируется последовательность Ъ--- количество случаев, когда в последовательности за i-й буквой следует буква.

Матрица должна обладать следующими свойствами: сумма элементов Ь,-1 в i-й строке должна быть равна общему количеству появлений i-й буквы в последовательности, а сумма всех элементов матрицы - длине последовательности N; суммы элементов в строке и столбце с одинаковыми номерами должны совпадать.

10

, , .

40

30

;

По данной матрице предварительно вычисляют матрицу Z(Zj-), i,, n1, элемент z. которой равен сумме элементов , ,Ь,- ,... ,Ъ матрицы В. Каждая строка матрицы Z задает свою определенную функцию распределения случайных чисел.

Кроме того вычисляют матрицу А (a..J),

, i,, n-1, являющуюся решеткой матрицы В. При этом , если Ъ,; О, и а,-,- 0, если bj; 0.

20

25

Матриць В, Z и А, а также номер начальной строки матрицы Z вводят в

15 устройство с помощью блока 16, причем матрица.Z поступает в вероятностный преобразователь 8, матрицы А и В - в статистический анализатор 10, а номер начгшьной строки - в регистр 14.

Работа устройства начинается с формирования числа с равномерным распределением. Формирование такого числа осуществляется с помощью блоков 2-5. Блок 3 по шине 22 запирает элементы И группы 7, в результате чего на адресный вход вероятностного преобразователя 8 с коммутатора 13 поступает код i 00...О, где i -.содержимое регистра 14. Этот код является адресом числа z., которое с вероятностного преобразователя 8 поступает на вход блока 4 выделения значащих разрядов числа. Блок 4 присваивает всем двоичным разрядам числа ,- которые младше самого старшего значащего разряда, значение единицы, оставляя старшие незначаш 1е разряды нулевыми. Сформированное блоком 4 ело используется для управления элементами И группы 5, на другие входы которых поступает случайное число с датчика 2. В результате количество значаш 1х разрядов в случайном числе на шине 18 не превышает количе45 ства значаш 1х разрядов в числе Z M,,) . Блок 3 проверяет вьшолнение неравенства i z- , отбирая при этом толь- ко те случайные числа, которые удовлетворяют этому неравенству. В слу50 чае вьшолнения неравенства блок 3 вьщает на шину 20 сигнал, разреша- работу вероятного преобразова- теля 8, который преобразует Е р число j в соответствии с распределе55 нием, записанным в i-й строке матрицы Z, причем значение i задает содержимое регистра 14.

После получения значения j считают, что случайным образом выбран переход устройства из состояния i в состояние j. Перед дальнейшим использованием значения j статистический анализатор 10 нроверяет, является ли переход из i в j допустимь1м на данном шаге формирования последовательности. Переход из состояния i в состояние j считается недопустимым, ес- пи его реализация приводит к формированию такой последовательности,длина которой меньше N, а матрица часто отличается от заданной.

Переход из i в j является допу- стимым, если он удовлетворяет хотя бы одному из следующих двух случаев,

1.Значение j получено при Zj, 1, т.е. выбор значения j является единственно возможным,

2,За К шагов, где ,п-1, возможен переход из состояния j в состояние i.

Первый случай проверяется с помо- щью элемента ИЛИ-НЕ 51, на вход которого с вычитателя 6 поступает значение iffi-i) RS-триггера 52, -Если Zj, , то по сигналу, поступающему по шине 20, триггер 52 переходит в единичное состояние. Состояние триггера 52 опрашивается с помощью элемента И 54 выходным сигналом регистра 43 памяти, и если триггер 52 находится в единичном состоянии, то значение j признается пригодным для дальнейшего использования, В про- тивном случае анализатор 10 переходит к проверке 2-го случая.

Проверку 2-го случая можно интер- прётйровать как проверку неразложимости матрицы частот или как проверку связности орграфа, матрицей смежности которого служит матрица частот Известно, что если за К шагов возможен переход из состояния j в состояние i, то (j,i)-.u элемент матрицы В должен быть больше нуля. Следовательно, (з,1)-й элемент матрихц, А, являющейся решеткой матрицы В , должен быть равен единице, В соответствии с этим анализатор 10 проверяет 2-й слуай путем вычисления (j,i)-ro элеента матрицы А , для чего анализаор 10 предварительно вычисляет j-ю троку матрицы А . Вычисление строки существляется по формуле

VcisAa ),

(1)

- W Дк)

где а j - j-H строка матрицы А ,

а, - S-H строка матрицы А;

а V (з)-й элемент матрицы

Ь5

Вычисления по этой формуле осуществляются с помощью группы 59 эле- ментов ИЛИ, регистра 60 памяти и регистра 61 сдвига. При этом группа 59 элементов ИЛИ служит для реализ-а- ции дизъюнкции в формуле (1), регистр 60 памяти - для хранения промежуточных результатов, а регистр 61 сдвига - для просмотра элементов

(-)

j-й строки матрицы А . Если S-й элемент этой строки равен единице,

то выходным сигналом регистра 43 памяти осуществляется считывание из блока 72 памяти s-й строки матрицы А, значение которой поступает на входы элементов ИЛИ группы 59. Если

же этот элемент равен нулю, считывание не осуществляется. Тем самым реализуется конъюнкция в формуле (1). Изменение величины s осуществляется путем сдвига содержимого регистра 61

на один разряд и одновременного увеличения на единицу содержимого счет- -чика 64, который служит для адреса- 1ции блока 72 памяти. Элемент ИЛИ-НЕ 62 служит для анализа содержимого

Регистра 61 сдвига. Если содержимое этого регистра, равно нулю, то это означает, что либо , либо даль нейшее увеличение s не изменяет код на выходах элементов ИЛИ группы 59,

где формируется значение , т.е. j-я строка матрицы А уже сформирована. Состояние выхода элемента ИЛИ-ПЕ

62опрашивается с помощью элемента И 58 выходным сигналом регистра 43

памяти, и если на выходе элемента 62 ИЛИ-НЕ присутствует единица, то анализатор 10 переходит к опросу значения

элемента j-и строки матрицы А ,

;Для выделения этого элемента слулшт коммутатор 63,состояние выхода которого опрашивается с помощью элемента И 56 выходным сигналом регистра 43 памяти. Если на выходе коммутатора

63присутствует единица, то это оз- начает, .что значение j удовлетворяет случаю и пригодно для даль- нейвдего использования, Б противном случае анализатор 10 вновь осуществляет вычисления по формуле (1), но

уже для нового значения К. Текущее

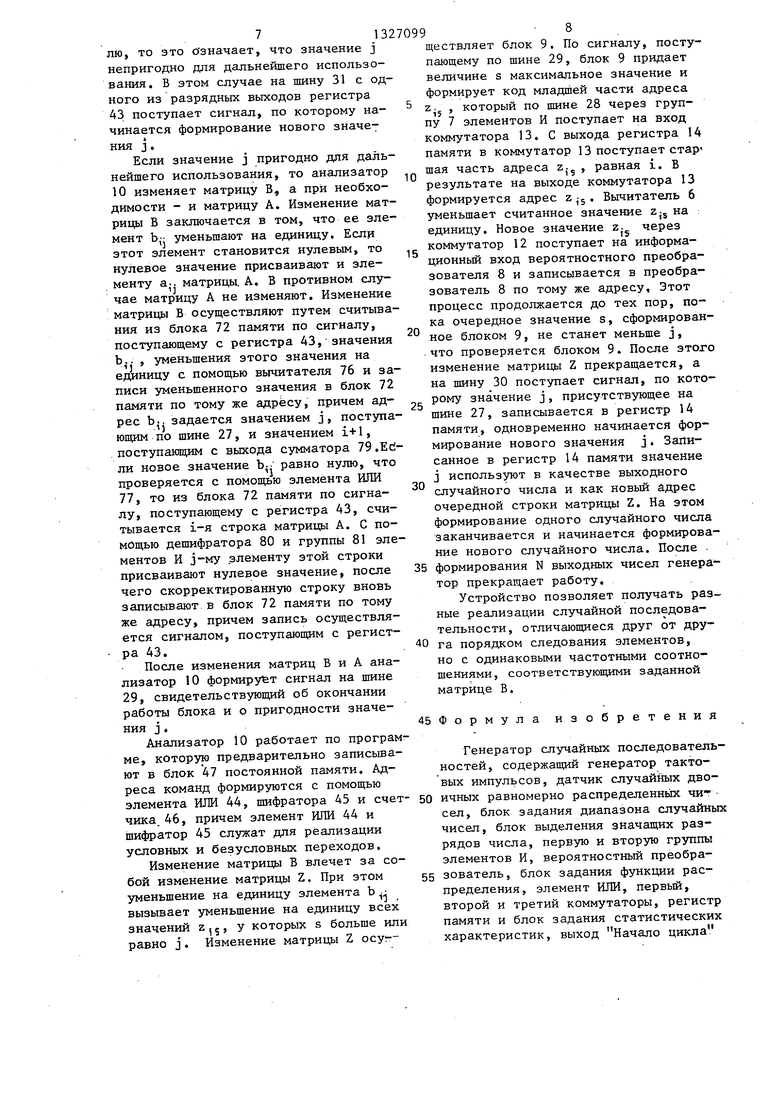

значение К формирует счетчик 48. Если , что проверяется с помощью дешифратора 49, и при этом i-й элемент j-й строки матрицы А равен нулю, то это о значает, что значение j непригодно для дальнейшего использования. В этом случае на шину 31 с одного из разрядных выходов регистра 43 поступает сигнал, по которому начинается формирование нового значе7 ния j .

Если значение j пригодно для дальнейшего использования, то анализатор 10 изменяет матрицу В, а при необходимости - и матрицу А, Изменение матрицы В заключается в том, что ее элемент Ь- уменьшают на единицу. Если этот элемент становится нулевым, то нулевое значение присваивают и элементу а. матрицы. А. В противном случае матрицу А не изменяют. Изменение матрицы В осуществляют путем считывания из блока 72 памяти по сигналу, поступающему с регистра 43, значения Ь.. , уменьшения этого значения на единицу с помощью вьгчитателя 76 и записи уменьшенного значения в блок 72 памяти по тому же адресу, причем адрес Ь. задается значением j, поступающим по шине 27, и значением i+1, . поступающим с выхода сумматора 79.Ed- ли новое значение равно нулю, что проверяется с помощью элемента ИЖ 77, то из блока 72 памяти по сигналу, поступающему с регистра 43, считывается i-я строка матрицы А. С помощью дешифратора 80 и группы 81 элементов И j-му элементу этой строки присваивают нулевое значение, после чего скорректированную строку вновь записывают в блок 72 памяти по тому же адресу, причем запись осуществляется сигналом, поступающим с регистра 43.

После изменения матриц В и А анализатор 10 формирует сигнал на шине 29, свидетельствующий об окончании работы блока и о пригодности значения j .

Анализатор 10 работает по программе, которую предварительно записывают в блок 47 постоянной памяти. Адреса команд формируются с помощью элемента ИЛИ 44, шифратора 45 и счетчика. 46, причем элемент ИЛИ 44 и шифратор 45 служат для реализации условных и безусловных переходов.

Изменение матрицы В влечет за собой изменение матрицы Z. При этом уменьшение на единицу элемента b вызывает уменьшение на единицу всех значений z, у которых s больше или равно j. Изменение матрицы Z осуг-

ществляет блок 9. По сигналу, поступающему по шине 29, блок 9 придает величине s максимальное значение и формирует код младшей части адреса , который по шине 28 через группу 7 элементов И поступает на вход коммутатора 13. С выхода регистра 14 памяти в коммутатор 13 поступает стар шая часть адреса Zj , равная i. В результате на выходе коммутатора 13 формируется адрес . Вычитатель 6 уменьшает считанное значение Zj на

единицу. Новое значение z. через коммутатор 12 поступает на информа0

ционный вход вероятностного преобразователя 8 и записывается в преобразователь 8 по тому же адресу. Этот процесс продолжается до тех пор, пока очередное значение s, сформированное блоком 9, не станет меньше j, что проверяется блоком 9. После этого изменение матрицы Z прекращается, а на шину 30 поступает сигнал, по которому значение j, присутствующее на шине 27, записывается в регистр 14 памяти, одновременно начинается формирование нового значения j. Записанное в регистр 14 памяти значение j используют в качестве выходного случайного числа и как новый адрес очередной строки матрицы Z. На этом формирование одного случайного числа заканчивается и начинается формирование нового случайного числа. После .

5 формирования N выходных чисел генератор прекращает работу.

Устройство позволяет получать разные реализации случайной последовательности, отличающиеся друг от дру0 га порядком следования элементов, но с одинаковыми частотными соотношениями, соответствующими заданной матрице В.

5 Формула изобретения

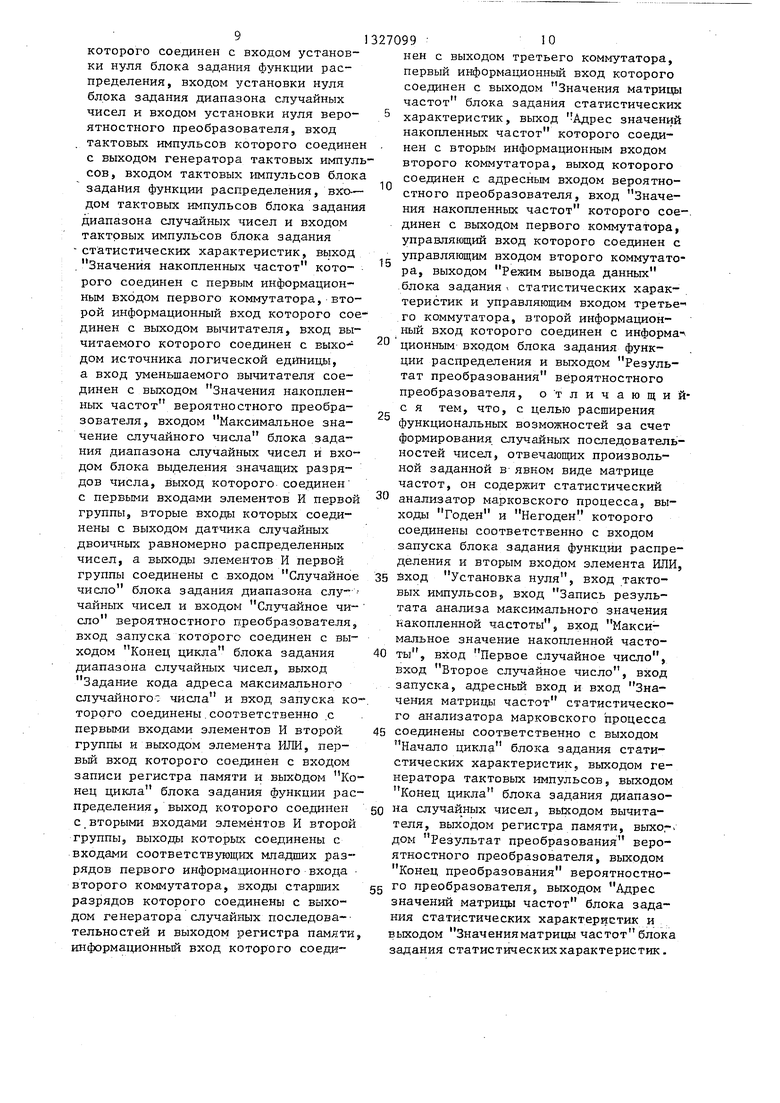

Генератор случайных последовательностей, содержаш й генератор тактовых импульсов, датчик случай:ных дво0 ичных равномерно распределенных чи сел, блок задания диапазона случайных чисел, блок выделения значащих разрядов числа, первую и вторую группы элементов И, вероятностный преобра5 зователь, блок задания функции распределения, элемент ИЛИ, первый, второй и третий коммутаторы, регистр памяти и блок задания статистических характеристик, выход Начало цикла

9

которого соединен с входом установки нуля блока задания функции распределения, входом установки нуля блока задания диапазона случайных чисел и входом установки нуля вероятностного преобразователя, вход тактовых импульсов которого соединен с выходом генератора тактовых импульсов, входом тактовых импульсов блока задания функции распределения, входом тактовых импульсов блока задания диапазона случайных чисел и входом тактовых импульсов блока задания -статистических характеристик, выход .Значения накопленных частот которого соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом вычитателя, вход вычитаемого которого соединен с выхо- дом источника логической единицы, а вход уменьшаемого вычитателя соединен с выходом Значения накопленных частот вероятностного преобразователя, входом Максимальное значение случайного числа блока .задания диапазона случайных чисел и входом блока выделения значащих разрядов числа, выход которого- соединен с первыми входами элементов И первой группы, вторые входы которых соединены с выходом датчика случайных двоичных равномерно распределенных чисел, а выходы элементов И первой группы соединены с входом Случайное число блока задания диапазона чайных чисел и входом Случайное чи- ело вероятностного преобразователя, вход запуска которого соединен с выходом Конец цикла блока задания диапазона случайных чисел, вькод Задание кода адреса максимального случаз ногоо числа и вход запуска которого соединены.соответственно .с первыми входами элементов И второй группы и выходом элемента ИЛИ, пер- вьй вход которого соединен с входом записи регистра памяти и выходом Конец цикла блока задания функции распределения , выход которого соединен с вторыми входа ш элементов И второй группы, выходы которых соединены с входами соответствующ.их младших разрядов первого информационного входа - второго коммутатора, входы старших разрядов которого соединены с выходом генератора случайных последова-- тельностей и выходом регистра памяти информационньш вход котор ого соеди10

27099 10

нен с выходом третьего коммутатора, первый информапдонный вход которого соединен с выходом Значения матрицы частот блока задания статистических 5 характеристик, выход Адрес значений накопленных частот которого соединен с вторым информационным входом второго коммутатора, выход которого соединен с адресным входом вероятностного преобразователя, вход Значения накопленных частот которого сое-. динен с выходом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора, выходом Режим вывода данньт блока задания статистических характеристик и управляющим входом третье- го коммутатора, второй информационный вход которого соединен с информа- 20 ционным входом блока задания функции распределения и выходом Результат преобразования вероятностного преобразователя, отличающий15

5

0

0

5

с я тем, что, с целью расширения

функциональных возможностей за счет формирования, случайных последовательностей чисел, отвечающих произвольной заданной в- явном виде матрице частот, он содержит статистический анализатор марковского процесса, выходы Годен и Негоден которого соединены соответственно с входом запуска блока задания функции распределения и вторым входом элемента PfflH,

5 Зход Установка нуля, вход тактовых импульсовр вход Запись результата анализа максимального значения Накопленной частоты, вход Максимальное значение накопленной частоты, вход Первое случайное число, вход Второе случайное число, вход запуска, адресньй вход и вход Значения матрицы: частот статистического анализатора марковского процесса соединены соответственно с выходом Начало цикла блока задания статистических характеристик5 выходом генератора тактовых 1-1мпульсов, выходом Конец цикла блока задания диапазона случай ных чисел э вьГходом вычитателя, выходом регистра памяти, выхог дом Результат преобразования вероятностного преобразователя, выходом Конец преобразования вероятностно5 го преобразователя, выходом Адрес значений матрицы частот блока задания статистических характеристик и выходом Значенияматрицы частот блока задания статистическиххарактеристик.

0

и13

2. Генератор по п. 1, отличающийся тем, что статистический анализатор марковского процес са содержит два RS-триггера, два элемента ЗАПРЕТ, шесть элементов И, два элемента задержки, три элемента ИЛИ, шифратор, три счетчика, два блока памяти, три регистра памяти, два дешифратора, два элемента ИЛИ-НЕ, два источника логического нуля, группу элементов ИЛИ, регистр сдвига, три коммутатора, источник логической единицы, вычитатель, сумматор и группу элементов И, первый R-вход первого RS-триггера соединен с первым R- входом второго RS-триггера и является входом Установка нуля анализатора, входом Максимальное значение накопленной частоты которого являются входы первого элемента ИЛИ-НЕ, выход которого соединен с первым S- входом второго RS-триггера, второй S-вход которого является входом Запись результата анализа максимального значения накопленной частоты анализатора, выходом Годен которого является выход первого разряда первого регистра памяти, выход второго разряда которого соединен с вторым R-входом первого RS-триггера и вторым R-входом второго RS-триггера, единичный выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом третьего разряда первого регистра памяти, выходы четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого разрядов которого соединены соответственно с первым входом второго элемента И, первым входом третьего элемента И, первым входом четвертого элемента И, входом управления режимом работы регистра сдвига, неинвертирующим входом первого элемента ЗАПРЕТ, входом Запись первого блока памяти, первым входом пятого элемента И и счетньм входом первого счетчика, выходы разрядов которого соединены соответственно с входами первого дешифратора, выход которого соединен с вторым входом второго элемента- И, выход которого соединен с первым входом первого элемента ИЛИ первым входом шифратора и является выходом Негоден анализатора, адресным входом которого является первый информационный вход первого коммутатора, старшие разряды второго инфор

9

12

мационного входа которого соединены с выходом первого источника логического нуля, старшими разрядами третье-, го информационного входа первого коммутатора и старшими разрядами четвертого информационного входа первого коммутатора, младшие разряды четвертого информационного входа первого коммутатора соединены с входами

второго дешифратора соответственно, с младшими разрядами пятого информационного входа первого коммутатора и являются входом Второе случайное число анализатора, входом Значения

матрицы частот которого является первый информационньш вход второго коммутатора, разряды второго информационного входа которого соединены с выходами соответствующих элементов

И группы, первые входы которых соединены с cooтвeтcтвyюш iми выходами - второго дешифратора, а вторые входы элементов И группы соединены с первыми входами элементов ИЛИ группы,

с выходами разрядов второго регистра памяти, и входом уменьшаемого вмчита- теля соответственно, вход вычитаемого которого соединен с выходом источника логической единицы и первым

входом с мматора, а выходы разрядов вычитателя соединены с треты-гм информационным входом второго коммутатора и входами второго элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента 1-1ЛИ и вторым входом шифратора, третий вход которого соединен с третьим входом первого элемента

ИЛИ и выходом третьего элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй вход третьего элемента ИЛИ соединен с выходом третьего элемента И, второй вход которого соединен с выходом третьего коммутатора, управляющий вход которого является входом Первое случайное число анализатора и соединен с младшими разрядами третьего

информационного входа первого коммутатора и вторым входом сумматора,выходы которого соединены со старшими разрядами пятого информационного входа первого коммутатора, младшие разряды второго информационного входа которого соединены с выходами разря- . доз второго счетчика соответственно, счетный вход которого соединен с входом сдвига регистра сдвига и выходом

двенадцатого разряда первого регистра памяти, выходы тринадцатого и четырнадцатого разрядов которого соединены с управляющим входом второго KONfMYTaTopa, выход которого соединен с информационным вкодом первого блока памяти, выходы разрядов которого соединены с соответствующими разрядами второго регистра памяти, вход записи которого соединен с выходом первого элемента задержки, вход которого соединен с входом считьюания первого блока памяти и выходом пятнадцатого разряда первого регистра памяти, выходы шестнадцатого, семнадцатого и восемнадцатого разрядов которого соединены с управляющие входом первого коммутатора, выход которого соединен с адресным входом первого блока памяти, S-вход первого RS-триггера является входом запуска анализатора, входом тактовых импульсов которого является первьш вход щестого элемента И, соединенный с инвертирующим входом второго элемента ЗАПРЕТ, счетным входом третьего счетчика и входом записи кода третьего счетчика, вход разрешения записи кода которого соединен с входом раз решения счета третьего счетчика и выходом первого элемента ИЛИ, четвертый вход которого соединен с четвертым входом шифратора и выходом первого элемента ЗАПРЕТ, инвертирующий вход которого соединен с выходом младшего разряда регистра сдвига R-вход которого соединен с выходом второгЬ источника логического нуля и D-входом регистра сдвига, выходы разрядов которого соединены с соответствующими вxoдaIvш второго элемента ИЛИ-НЕ, выход которого соединен с

0

5

0

вторым входом четвертого элемента И, выход которого соединен с пятым входом первого элемента ИЛИ и пятым входом шифратора, шестой вход которого соединен с шестым входом первого элемента ИЛИ и выходом девятнадцатого разряда первого регистра памяти, информационный вход которого соединен с выходом второго блока памяти, адресный вход которого соединен с выходом третьего счетчика,входы разрядов которого соединены с соответствующими выходами шифратора, а Н-вход третьего счетчика соединен с инверсным ВЕзПСодом первого RS-триг- тера и вторым входом шестого элемен- та И, выход которого соединен с R входом первого регистра-памяти, вход . записи которого соединен с выходом второго элемента задержки, вход которого соединен с входом считывания второго блока памяти и выходом второго элемента ЗАПРЕТ, неинвертируюшдй вход которого соединен с единичным выходом первого RS-триггера, S-вкод которого соединен с R-входами первого счетчика и третьего регистра памяти, вход записи которого соединен с выходом двадцатого разряда первого регистра памяти выход двадцать первого разряда которого соединен с R-BXO- дом второго счетчика и входом записи кода регистра сдвига, входы разрядов которого соединены с соответ5 ствующимн информационными входами третьего коммутатора, с соответству- выходами элементов ИЛИ группы и соответству1ощ11ми входами разрядов третьего регистра памяти, выходы

0 разрядов которого соединены с вторыми входами элементов ИЛИ группы соответственно о

5

0

гз

27 3 35

6ff

68,

Редактор Л.Веселовская

Составитель А,Карасов Техред Л.Сердюкова

Заказ 3390/45

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

PtfS. г 6

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных последовательностей | 1983 |

|

SU1180887A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Генератор цепей Маркова | 1982 |

|

SU1049903A1 |

| Устройство для контроля вычислительных программ | 1985 |

|

SU1278856A1 |

| Генератор случайных чисел | 1980 |

|

SU922738A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Генератор случайных процессов | 1981 |

|

SU1012256A1 |

| Генератор случайных чисел | 1981 |

|

SU991422A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Генератор нестационарных потоков случайных импульсов | 1981 |

|

SU976441A1 |

Изобретение относится к вычислительной технике и может быть использовано для генерирования на требуемом периоде случайных последовательностей с заданными частотными свойствами, определяемыми исходной матрицей частот. Целью изобретения является расширение функциональных воз можностей за счет формирования случайных последовательностей, отвечающих произвольной заданной в явном виде матрице частот. Генератор содержит генератор 1 тактовых импульсов датчик 2 случайных двоичных равномерно распределенных чисел, блок З задания диапазона случайных чисел, блок 4 выделения значащих разрядов числа, группу 5 элементов И, вычитате11Ь 6, группу 7 элементов И, вероятностный преобразователь 8, блок 9 задания функции распределения,статистичесг кий анализатор 10, элемент И ИЛИ, коммутаторы 12, 13, регистр 14 памяти, коммутатор 15, блок 16 задания статистических характеристик и связи 17-38 между блоками. Устройство nor. зволяет получать разные реализации случайной последовательности, отличающиеся друг от друга порядком следования элементов, но с одинаковыми частотными соотношениями, соответствующими заданной матрице Б. 1 з,П4 ф-лы, 2 ил.,1 табл. (Л с

| Генератор псевдослучайных чисел | 1980 |

|

SU943722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор случайных последовательностей | 1983 |

|

SU1180887A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1985-10-14—Подача