ния счетчика этого же блока, информа ционный выход которого соединен с первым информационным входом коммута тора этого же блока и с вторым инфор мационным входом второго коммутатора выход регистра задания адреса блока формирования статистических характеристик соединен с вторым информацион ным входом коммутатора этого же блок выход которого соединен с первым адресным входом регистра памяти этого же блока, второй информационный вход которого соединен с .выходом регистра задания начальных условий этого же блока и с первым информационным входом третьего коммутатора, первый выход дешифратора блока задания статис тических характеристик соединен с пе выми входами первого элемента ИЛИ и первого элемента И этого же блока и с управляющим входом третьего коммутатс а, выход первого элемента И блока формирования статистических характеристик соединен с первым входом первого элемента ИЛИ, выход регистра задания работы блока формирования статистических характеристик соединен с входом дешифратора этого же блока, второй выход которого соединен с вторым входом первого эле мента ИЛИ этого же блока, с управляющим входом коммутатора этого же блока и с первым входом второго элемента И этого же блока, третий выход дешифратора блока задания статистических характеристик соединен с первыми входами третьего, четвертого, пятого, шестого и седьмого

элементов И этого же блока, выход третьего элемента И блока формирования статистических характеристик соединен с первым входом второго элемента ИЛИ, выход шестого элемента И блока формирования статистических характеристик соединен с первым входом третьего элемента ИЛИ, второй вход шестого элемента И блока формирования статистических характеристик соединен с инверсным вькодом первого RS-триггера данного блока, S-вход ,которого соединен с первым 8-входом второго RS-триггера и выходом седьмо го элемента И данного блока, второй вход которого соединен с выходом формирователя пускового сигнала и первым входом восьмого элемента И данного блока, второй вход которого соединен с выходом первого элемента 1ШИ данного блока, а выход 1

генератора тактовых импульсов и с С-входом D-триггера, С-входом регистра сдвига и входом элемента НЕ данного блока, выход которого соединен с третьим входом элемента И, выход которого соединен со счетным входом счетчика данного блока, первый вход схемы сравнения блока формирования диапазона случайных чисел объединен с третьим входом вероятностного преобразователя и подключен к выходу первого блока элементов И, второй вход схемы сравнения блока формирования диапазона случайных чисел соединен с входом блока формирования числа разрядов случайной последовательности, с входом уменьшаемого вычитателя и с первым выходом вероятностного преобразователя, выход схемы сравнения бло7восьмого элемента И соединен с вторым S-входом второго RS-триггера данного блока, выход которого соединен с D-ВХОДОМ D-триггера данного блока, выход которого соединен с вторым R-входом второго RS-триггера и первым входом второго элемента ИЛИ данного блока, второй вход которого соединен с выходом девятого элемента И данного блока, первый вход которого соединен с прямым выходом первого RS-триггера, а второй вход девятого элемента И соединен с третьим входом шестого элемента И, вторым входом пятого элемента И И выходом первого разряда регистра данного блока, D-вход которого соединен с выходом второго элемента ИЛИ, а выход второго разряда регистра сдвига соединен с первым входом десяфого элемента И и первым входом третьегхэ элемента ИЛИ данного блока, второй вход которого соединен с выходом третьего разряда регистра сдвига, а выход третьего элемента ИЛИ соединен с вторым входом четвертого элемента И данного блока, выход которого соединен с входом считывания регистра памяти, вход записи которого соединен с выходом второго элемента И данного блока, второй вход которого соединен с вторым входом третьего элемента И, вторым входом первого элемента И и выходом десятого элемента И данного блока, второй,вход которого соединен с выходом элемента задержки, вход которого соединен с выходом

ка формирования диапазона случайньЬс чисел соединен с первым входом первого элемента И данного блока, второй вход которого соединен с выходом D-триггера, входом первого элемента задержки и первым входом второго элемента И данного блока, выход которого соединен с входом датчика случайных двоичных равномерно распределенных чисел, выход первого элемента И блока формирования диапазона случайных чисел соединен с первым входом элемента ИЛИ и входом первого элемента НЕ данного блока, выход которого соединен с первым входом третьего элемента И данного блока второй вход которого соединен с выходом первого элемента данного блока, а выход третьего элемента И данного блока соединен с четвертым входом верояностного преобразователя, выход генератора тактовых импульсов соединен с входами второго элемента НЕ, с Свходом регистра сдвига, с С-входом D-триггера и входом второго элемента задержки блока формирования диапазона случайных чисел, выход второго элемента задержки этого же блока соединен с вторым входом второго элемента И данного блока, выход второго элемента НЕ этого же блока соединен с третьим входом третьего элемента И, первым входом четвертого элемента И и с первым входом пятого элемента И данного блока, второй вход которого соединен с выходом первого разряда регистра сдвига этого же блока,. D-вход которого соеди- йен с выходом третьего элемента ИЛИ, выход второго разряда регистра сдвига блока формирования диапазона случайных чисел соединен с вторым входом четвертого элемента ИЛИ, выход четвертого элемента И блока формирования диапазона случайных чисел соединен с первым входом пятого элемента ИЛИ, выход пятого элемента И блока формирования диапазона случайных

чисел соединен с первым R-входом RS-триггера и вторым входом элемента ИЛИ этого же блока, выход которого соединен с D-входом D-триггера этого же блока, R-вход которого соединен с вторым R-входом RS-триггера, R-входом регистра сдвига этого же

блока и с вторым входом вероятностного преобразователя, выход третьего разряда регистра сдвига блока формирования диапазона случайных чисел соединен с S-входом RS-триггера, инверсный выход которого соединен с первым входом второго блока элементов И, выход генератора тактовых импульсов соединен с С-входом регистра сдвига и с. входом первого элемента НЕ блока формирования функции распределения, выход которого соединен с первыми входами первого, второго и третьего элементов И же блока, выход первого элемента И этого же

блока соединенс вторым входом пятого элемента.ИЛИ, второй выход вероятностного преобразователя соединен с Sвходом первого RS-TpHrrepa, с установочным входом счетчика и первым входом элемента ИЛИ блока формирова- ния функции распределения, второй вход которого соединен с выходом четвертого элемента И данного блока, а выход элемента ИЛИ данного блока соединен с D-входом регистра сдвига данного блока, выход, пгрвого разряда которого соединен с Sвходом второго RS-триггера данного блока, а выход второго разряда регистра сдвига данного блока соединен с вторым входом первого элемента И и вторым входом четвёртого элемента ИЛИ, второй вход второго элемента ИЛИ подключен к выходу второго элемента И блока формирования функций распределения, второй вход которого соединен с выходом третьего разряда регистра сдвига данного-блока, а выход четвертого разряда регистра сдвига данного блока соединен с вторым входом третьего элемента И данного блока, выход которого соединен с первым R-входом второго RSтриггера, входом элемента задержки и счетным входом счетчика данного блока, информационный выход которого соединен с первым входом схемы сравнения и с информационным входом регистра памяти данного блока, входсчитывания которрго соединен с

выходом второго RS-триггера данного блока, выход регистра памяти соединен с первым информационным входом коммутатора блока, выход которого соединен с вторым входом второго блока элементов И, третий выход вероятностного преобразователя соединен

с вторым информационным входом третЬего коммутатора,,а также с вторьм информационным входом коммутатора

и с вторым входом схемы сравнения блока формирования функции распределения, выход которой соединен с первым входом .пятого элемента И и входом второго элемента НЕ данного:, блока, выход которого соединен с первым входом четвертого элемента И данного блока, второй вход которого соединен с выходом элемента задержки и вторым входом пятого элемента И данного блока, выходкоторого соединен с первым R-входом первого RS-триггера данного блока и с вторыми вхЬдами первого и третьего элементов И, второй вход вероятностного преобразователя соединен с Rвходом регистра сдвига, с R-входом второго RS-триггера и вторым R-TBXO.дом первого RS-триггера блока формирования функции распределения, выход которого соединен с управляющим входом коммутатора этого же блока, выходы четвертого и пятого элементов ИЛИ соединены соответственно с пятым и шестым входами вероятностного преобразователя, седьмой вход которого подключен к выходу второго элемента ИЛИ, выходы первого и второго коммутаторов подключены соответственно к восьмому и девятому входам вероятностного преобразовател выход датчика случайных двоичных равномерно распределенных чисел соединен с первым входом первого блока элементов И, второй вход которого соединен с выходом блока формирования числа разрядов случайной последЬвдтельности, второй информационный вход первого коммутатора подключен к выходу вычитателя, вход вьгаитаемого которого является управляющим входом генератора, выход третьего коммутатора соединен с информационным входом регистра памяти, считывающий вход которого подключен к выходу первого элемента ИЛИ, а выход регистра памяти является выходом генератора и соединен с вторым информационным входом второго коммутатора, третий информационный в ход которого подклчен к выходу второго блока элементов И.

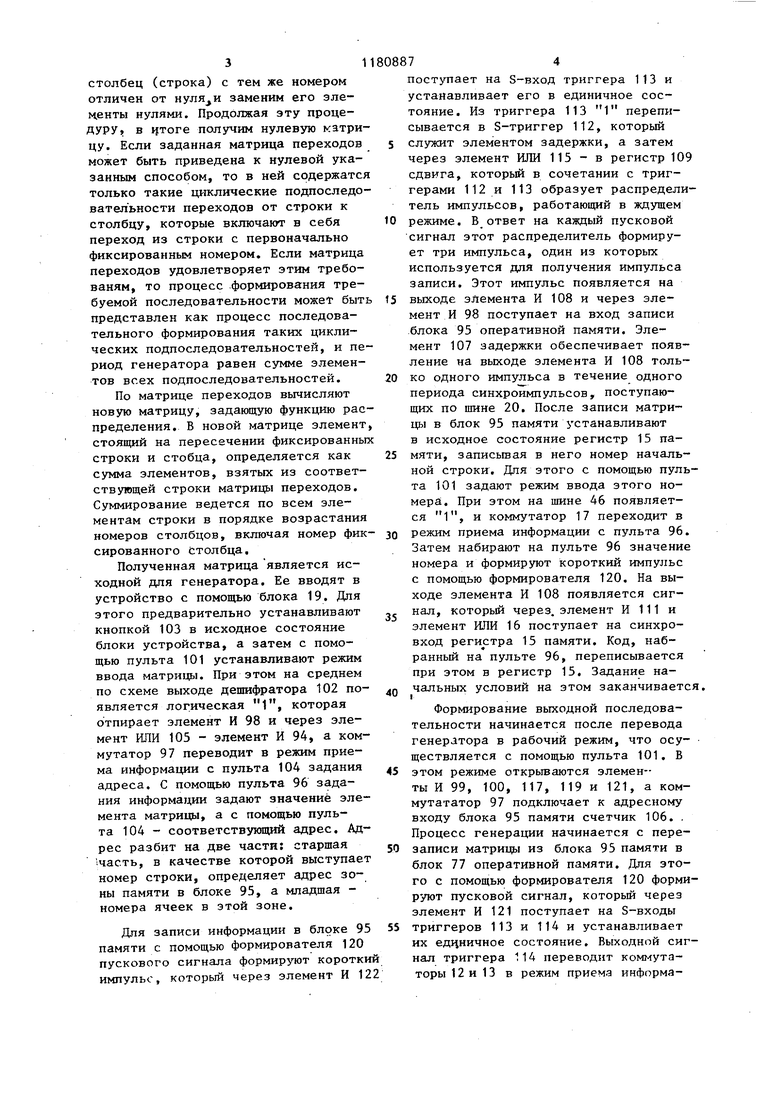

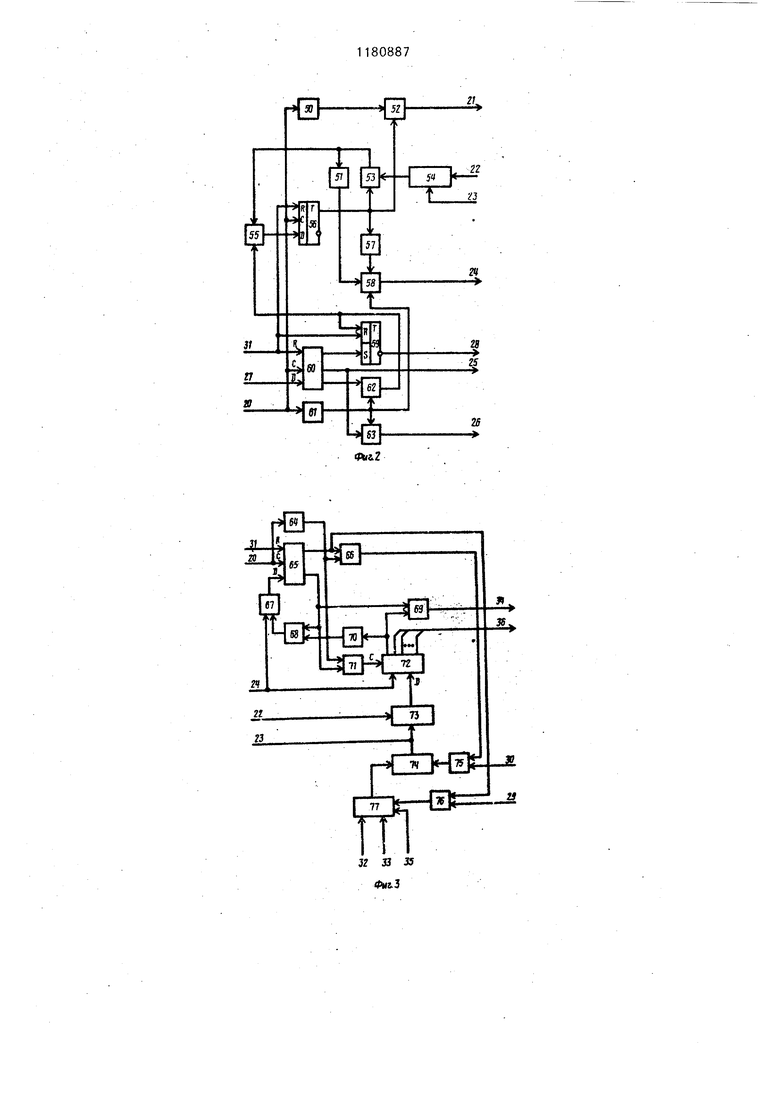

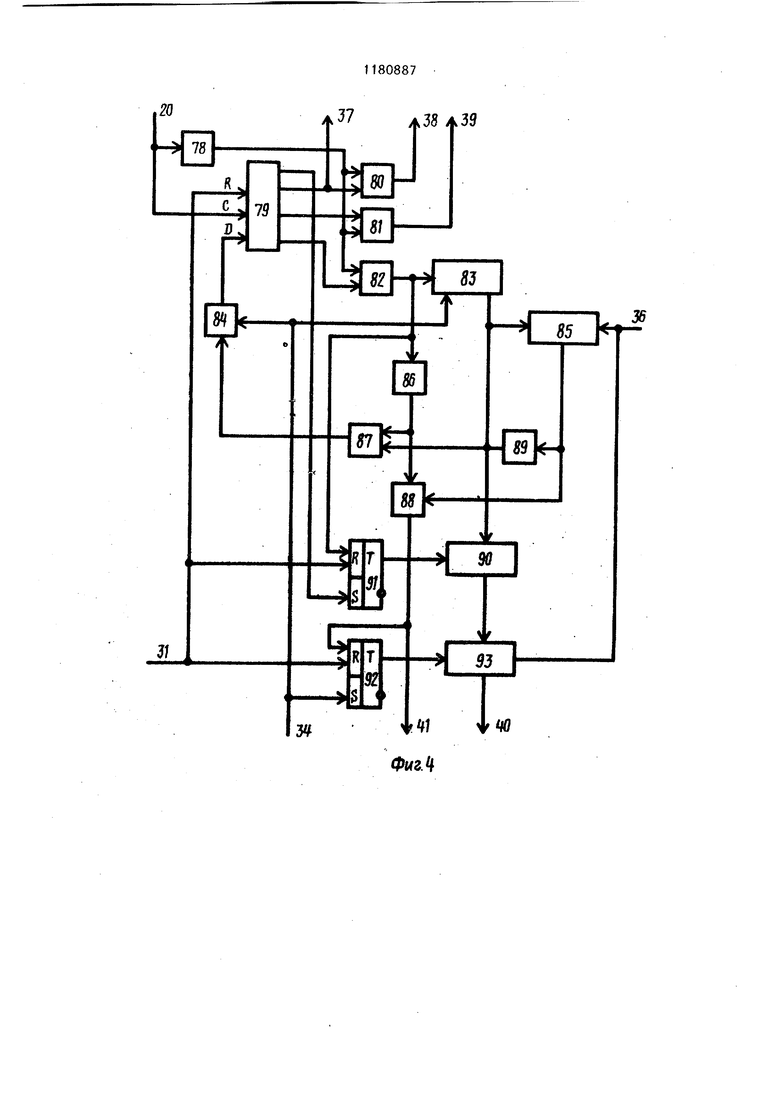

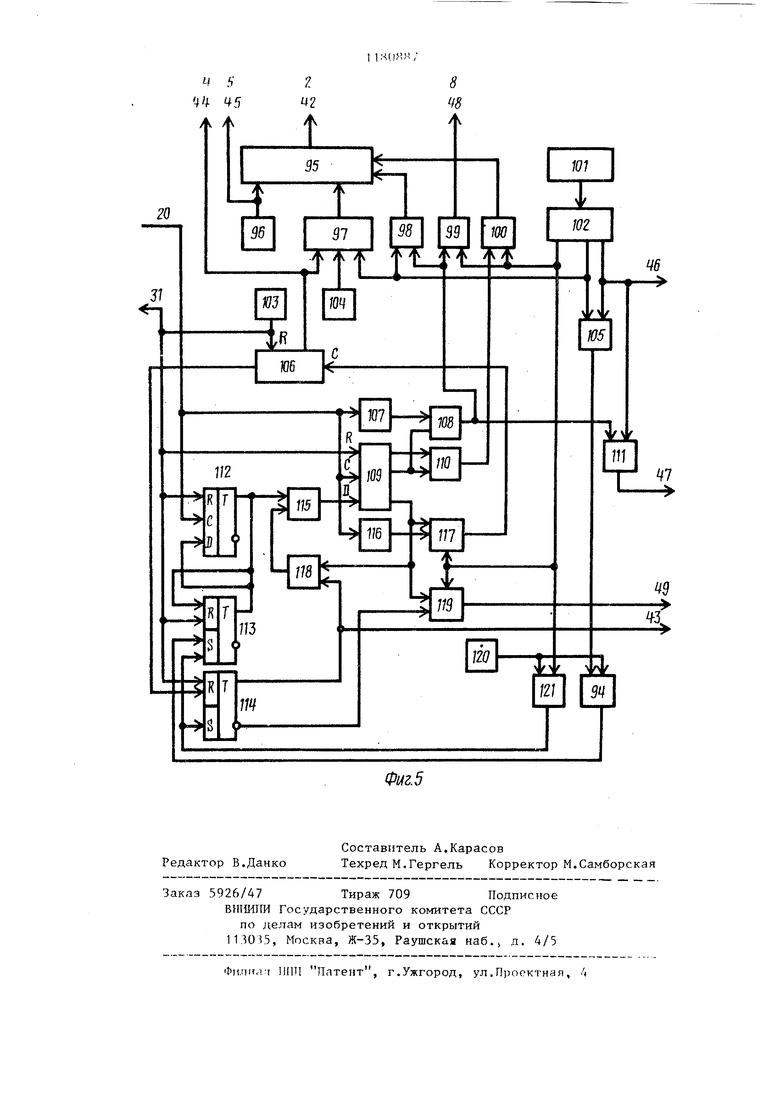

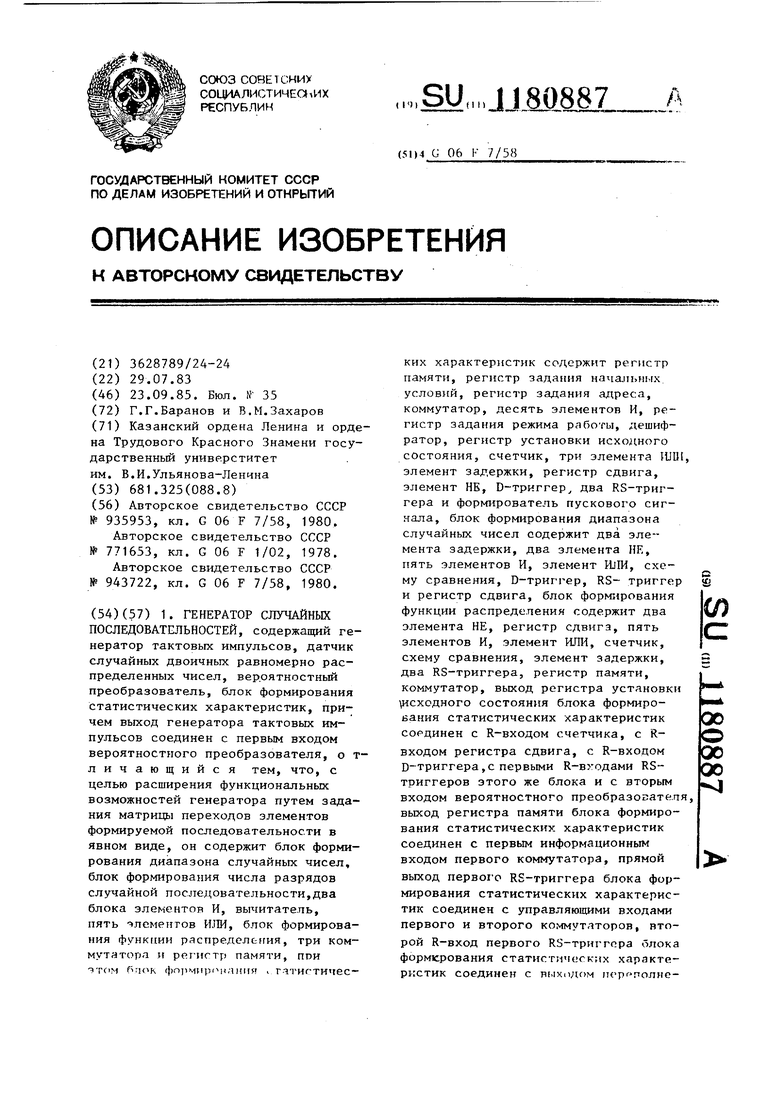

2. Генератор по п. 1, отличающийся тем, что, вероятностный преобразователь содержит два элемента НЕ, первьш регистр сдвига, четыре элемента И, три элемента ИЛИ, второй регистр сдвига, схему сравнения, регистр памяти и блок памяти, причем вход первого элемента НЕ является певым входом вероятностного преобразователя и соединен с С-входом первого регистра сдвига, К-вход которого явлется вторым входом вероятностного преобразователя, третьим и четвёртым входами вероятностного преобразователя являются соответственно первый вход схемы сравнения и вход Запись второго регистра, вход Запись второго регистра сдвига соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход первого элемента ШШ соединен с D-входом первого регистра сдвига, выход первого разряда которого соединен с первым входом второго элемента И и первым входом второго элемента ШШ, второй вход которого является пятым входом вероятностного преобразователя, выход первого элемента НЕ соединен с первым входом третьего элемента И и вторым входом второго элемента И, выход которого соединен с первым входом третьего элемента ШШ, второй вход которого является шестым входом вероятностного преобразователя, седьмым, восьмым и девятым входа1 ш которого являются соответственно вход Запись блока памяти, информационный вход блока памяти и адресный вхо блока памяти, вход считывания которого соединен с выходом второго элемента ИЛИ, а выход блока оперативной памяти соединены с D-входом регистра памяти, С-вход котюрого соединен с выходом третьего элемента ШШ, а выход региотра памяти является первым выходом вероятностного преобразователя и соединен с вторым входом схемы сравнения, выход которой соединен с D-входом второго регистра сдвига, С-вход которого соединен с выходом третьего элемента И, второй вход которого соединен с выходом второго разряда первого регистра сдвига, первым входом четвертого элемента И и первым входом первого элемента И, второй вход которого соединен с вытходом второго элемента НЕ, вход которого соединен с выходом последнего разряда второго регистра сдвига и вторым входом четвертого элемента И, выход которого является вторым выходом вероятностного преобразователя, третьим выходом которого являются выходы первых разрядов второго регистра сдвига ((к+1) - число разрядов второго регистра сдвига). Изобретение относится к вычислительной технике и может быть использовано при решении задач статистичес кими методами. Целью изобретения является расши- рение функциональных возможностей генератора путем задания матрицы переходов элементов формируемой последовательности в явном виде. На фиг, 1 приведена блок-схема генератора случайных последовательностей; на фиг. 2 - схема блока формирования диапазона случайных чисел; на фиг. 3 - схема вероятностного преобразования , на фиг. 4 - схема блока формирования функции распределения; на фиг. 5 - схема §лока формирования статистических характеристик. На фиг. 2-5 введены следующие обозначения: R - вход установки С - синхровход; D - информационный вход S - вход установки Т триггер. Генератор случайных последовательностей содержит генератор 1 тактовых импульсов, датчик 2 случайных двоичных равномерно распределенных чисел, блок 3 формирования диапазона случайных чисел, блок 4 фор.мирования числа разрядов случайной последовательности (вьщеления значащих разрядов числа), блок 5 эле- , ментов И, вычитатель 6, первый 7 и второй 8 элементы ИЛИ, вероятностный преобразователь 9, третий элемент ИЖ 10, блок 11 формирования функции распределения, первый коммутатор 12, второй коммутатор 13, второй блок 14 элементов И, регистр 15 памяти, четвертый элемент ИЛИ 16, третий коммутатор 17, пятый элемент ИЛИ 18, блок 19 формирования статистических характеристик и Связи 20-49 между блоками. Блок 3 формирования диапазона слу чайных чисел содержит элемент 50 задержки, элемент НЕ 51, элемен ты И 32, 53, Схему, 54 сравнения, эле мент ИЛИ 55, D-триггер 56, элемент 5 задержки, элемент 58: И, RS-триггер 5 регистр 60 сдвига, элемент НЕ 61 и элементы И 62, 63, Вероятностный преобразователь 9 содержит элемент НЕ 64, регистр 65 сдвига, элемент И 66, элемент ИЛИ 67 элементы И 68,. 69, элемент НЕ 70, элемент И 71, регистр 72 сдвига, схе му 73 сравнения, регистр 74 памяти, элементы ИЛИ 75, 76 и блок 77 оперативной памяти. Блок 11 формирования функции распределения содержит элемент НЕ 78, регистр 79 сдвига, элементы И 80-82, вычитающий счетчик 83, элемент ИЛИ 84, схему 85 сравнения,элемент 86 задержки, элементы И 87, 88, элемент НЕ 89, блок 90 постоянной памяти, RS-триггеры 91, 92 и коммутатор 93. Блок 19 формирования статистических-характеристик содержит элемент И 94, блок 95 оперативной паяти, регистр 96 задания начальных условий, коммутатор 97, элементы И 98-100, регистр 101 задания режима работы, дешифратор 102, регистр 103 установки исходного состояния, регистр 104 задания адреса, элемент ИЛИ 105, двоичньй суммирукидий счетчик 106, элемент 107 задержки, элемент И 108, регистр 109 сдвига, элемент ИЛИ 110, элемент И 111, D-триггер 112, RSтриггеры 113, 114, элемент ИЛИ 115, элемент НЕ 116, элементы И 117-119, формирователь 120 пускового сигнала и элемент И 121, Устройство работает следующим образом. Структура формируемой последовательности предварительно задается в виде квадратной матрицы переходов. Каждьй элемент в этой матрице обозначает количество случаев появления фиксироваиного сигнала за другим фиксированным сигналом. Эта матрица должна удовлетворять следукицим требованиям: суммы элементов в строке и столбце с одинаковыми номерами должны совпадатьi матрица должна быть приводима к (Нулевой матрице путем следукяцей процедуры. Фиксируем в матрице номер строки, сумма элементов которой не меньше суммы элементов любой другой строки. Заменим элементы в этой фиксированной строке и столбце с тем же номером нулями, В полученной матрице найдем нулевую строку (столбец), для которой столбец (строка) с тем же. номером имеет сумму элементов, отличную от нуля и заменим элементы этого столбца (строки) нулями, В полученной таким образом матрице иайдем нуевую строку (столбец), для которой

столбец (строка) с тем же номером отличен от нулями заменим его элененты нулями. Продолжая эту процедуру в итоге получим нулевую матрицу. Если заданная матрица переходов может быть приведена к нулевой указанным способом, то в ней содержатся только такие циклические подпоследовательности переходов от строки к столбцу, которые включают в себя переход из строки с первоначально фиксированным номером. Если матрица переходов удовлетворяет этим требованям, то процесс формирования требуемой последовательности может быт представлен как процесс последовательного формирования таких циклических подпоследовательностей, и период генератора равен сумме элементов всех подпоследовательностей,

По матрице переходов вычисляют новую матрицу, задающую функцию распределения, В новой матрице элемент стоящий на пересечении фиксированны строки и стобца, определяется как сумма элементов, взятых из соответствующей строки матрицы переходов. Суммирование ведется по всем элементам строки в порядке возрастания номеров столбцов, включая номер фик сированного Столбца,

Полученная матрица является исходной для генератора. Ее вводят в устройство с помощью блока 19, Для этого предварительно устанавливают кнопкой 103 в исходное состояние блоки устройства, а затем с помощью пульта 101 устанавливают режим ввода матрицы. При этом на среднем по схеме выходе дешифратора 102 появляется логическая 1, которая отпирает элемент И 98 и через элемент ИЛИ 105 - элемент И 94, а коммутатор 97 переводит в режим приема информации с пульта 104 задания адреса. С помощью пульта 96 задания информации задают значение элемента матрицы, а с помощью пульта 104 - соответствующий адрес. Адрес разбит на две части; старшая Участь, в качестве которой выступает номер строки, определяет адрес зоны памяти в блоке 95, а младшая номера ячеек в этой зоне,

Для записи информации в блоке 95 памяти с помощью формирователя 120 пускового сигнала формируют коротки импульс, который через элемент И 12

поступает на S-вход триггера 113 и устанавливает его в единичное состояние. Из триггера 113 1 переписывается в S-триггер 112, который служит элементом задержки, а затем через элемент ИЛИ 115 - в регистр 10 сдвига, которьм в сочетании с триггерами 112 и 113 образует распределитель импульсов, работающий в ждущем режиме, В ответ на каждый пусковой сигнал этот распределитель формирует три импульса, один из которых используется для получения импульса записи. Этот импульс появляется на выходе элемента И 108 и через элемент И 98 поступает на вход записи блока 95 оперативной памяти. Элемент 107 задержки обеспечивает появление на выходе элемента И 108 толь ко одного импульса в течение одного периода синхроимпульсов, поступающих по шине 20, После записи матрицы в блок 95 памяти устанавливают в исходное состояние регистр 15 памяти, записьшая в него номер начальной строки. Для этого с помощью пульта 101 задают режим ввода этого номера. При этом на шине 46 появляется 1, и коммутатор 17 переходит в режим приема информации с пульта 96, Затем набирают на пульте 96 значение номера и формируют короткий импульс с помощью формирователя 120, На выходе элемента И 108 появляется сигнал, который через, элемент И 111 и элемент ИЛИ 16 поступает на синхровход регистра 15 памяти. Код, набранный на пульте 96, переписывается при этом в регистр 15, Задание начальных условий на этом заканчиваетс

Формирование выходной последовательности начинается после перевода генератора в рабочий режим, что осуществляется с помощью пульта 101, В этом режиме открываются элементы И 99, 100, 117, 119 и 121, а коммутататор 97 подключает к адресному входу блока 95 памяти счетчик 106, . Процесс генерации начинается с перезаписи матрицы из блока 95 памяти в блок 77 оперативной памяти. Для этого с помощью формирователя 120 формируют пусковой сигнал, который через элемент И 121 поступает на S-входы триггеров 113 и 114 и устанавливает их единичное состояние. Выходной сигнал триггера 114 переводит коммутаторы 12 и 13 в режим приема информации с блока 95 памяти и счетчика 106 соответственно и одновременно открывает элемент И 118, замыкая тем самым цепь обратной связи регистра 109 благодаря чему формирование импульсов регистром 109 происходит до тех пор,пока триггер 1 14 остается в единичном сос Тоянии. Сброс триггера 114 осуществляется сигналом, поступающим со счетчика 106, которьй служит не только для формирования адресов, но и для подсчета количества переписанных чисел. Для перезаписи каждого числа формируется импульс считьшания, который через элемент И 100 поступает на шину считывания блока 95 памяти, и импульс записи, который через элемент И 99 и элемент ИЛИ 10 поступает на шину записи блока 77 памяти. После перезаписи каждого числа на выходе элемента И 11 появляется сигнал, который поступает на вход счетчика 106 и увеличивает его содержимое на 1. Б момент окончания перезаписи матрицы счетчик 106 выдает сигнал, устанавливающий триггер 114 в исходное состояние. Процесс перезаписи при этом прекращается, а на выходе элемента И 119 появляется импульс, которьш свидетельствует об окончания перезаписи матрицы и одновременно служит пусковым сигналом для блока 3 изменения диапазона случайных чисел. .

Пусковый сигнал, поступающий в блок 3 по шине 27, записывает 1 в регистр 60 сдвига, который в свою очередь устанавливает в 1 триггер 59. При этом элементы И набора блока 14 закрываются, в результате чего младшая часть адреса принимает нулевое значение. Импульс со второго (среднего по схеме) выхода регистра 60 поступает через злемент ИЛИ 7 и элемент ИЛИ 76 на шину считывания блока 77 памяти вероятностного преобразователя 9. При зтом считывается значение, записанное по адресу, старшая часть которого представляет собой содержимое регистра 15 памяти, а младшая часть равна О. Импульс с выхода элемента И 63 через элемент ИЛИ 8 и элемент ИЛИ 75 поступает на синхровход регистра 74 памяти и записывает в него результат считывания. По шине 23 это значетше поступает в

блок 4 вьщеления значащих рагчяло числа и на схему 34 сравнения. 1ри этом па выходе блока 4 все разряды числа, которые младше самого старшего, отличного от О разряда, принимают единичное значение, а незначащие старшие разряды остаются нулевыми. Этот код управляет набором 5 элементов И, причем те элементы И, которые отвечают незначающим разрядам числа, запираются.

Сигнал, появляющийся на третьем выходе регистра 60, открывает эле|мент И 62, в результате чего триггер 59 возвращается в исходное состояние, а очередной синхроимпульс, поступающий по шине 20, записывает 1 в D-триггер 56. Выходной сигнал триггера 56 открьгоает элемент И 52, и на шину 21 поступает импульс, по которому датчик 2 случайных чисел вырабатывает случайное число. После прохождения этот числа через набор блока 5 элементов И количество его значащих разрядов не превьшгает количества значащих разрядов числа, хранящегося в регистре 74, Полученное таким случайное число сравнивают со значением числа, хранящегося в регистре 74, с помощью схемь 54 сравнения. Если случайное число меньше, то считают его пригодным для дальнейшего использования, в противном случае формируют новое случайное число. В последнем случае на выходе схемы 54 сравнения присутствует уровень логической 1, так что триггер 56 остается в единичном состоянии, а на выходе элемента И 52 появляется новый импульс, по которому датчик 2 вырабатывает новое случайное число.

Если условие меньще выполняется, то на выходе схемы 54 сравнения появляется О, элемент И 53 закрывается, и очередной синхроимпульс устанавливает триггер 56 а нулевое состояние. Элемент 30 задержки препятствует появлению дополнительного импульса на шине 21, для чего время задержки сигнала этим элементом должно превышать время срабатывания триггера 56. Окончание поиска случайного числа, удовлетворяющего неравенству меньше, сопровождается появлением импульса на выходе элемента И 58, который служит в к-а«естве пускового сигнала для вероятност ного пре6браэовате)1я 9. Элемент 57 задержки препятствует появлению этого сигнала в момент перехода тр,и гера 56 в единичное состояние. Время задержки сигнала этим элементом должно превьшать время задержки сигнала инвертором 61. Полученное случайное число поступает в вероятностный преобразователь 9, который преобразует его в вы ходное число-. Преобразование состои в определении интервала между значениями функции распределения, в ко торый попадает случайное число, Зна чениями функции распределения служа значения элементов матрицы, причем номер строки матрицы задает код, хранящийся в регистре 15. Матрица переходов, по которой составляют исходную для генератора матрицу, задает не только вероятнос шую структуру последовательности вы ходных чисел, но и длину этой после довательности, которая равна суммеэлементов матрицы переходов. После фор1-шрования каждого выходного числа длина оставшейся части последовател ности уменьшается на 1, поэтому необходимо вычесть 1 из соответствуняцего элемента матрищ) переходов. При этом нов&я матрица описывает вероятностную структуру и длину оставшейся части последовательности которую предстоит сформироватд. Изменение матрицы переходов влечет за собой изменение исходной матрицы. Таким образом, матрица, хранящаяся в блоке 77 памяти, в процессе формирования последовательности постоянно изменяется в сторону уменьшения своих элементов, превращаясь в конце концов в нулевую матрицу. Необходимое изменение этой матрицы обеспечивает блок 11. После обнуления информации в блоке 77 формирование последовательности автоматически прекращается, так как с блока 77 памяти в блок 3 поступает нулевое значение. § результате этого происходит зацикливание блока 3. Генератор позволяет получать различные реализации заданного случайного процесса. Для получения новой реализации достаточно вновь установить блоки устройства в исходное состояние, занести в регистр 15 начальное значение номера матрицы и переписать матрицу из блока 95 памяти в блок 77 памяти, после чего автоматически начинается формирование новой последовательности. Эффективность предлагаемого устройства по сравнению с известным состоит в том, 4fo матрица переходов, задающая статистические характеристики последовательности, может быть задана в явном виде, благодаря чему задаваемый процесс имеет более полное описание и, следовательно, в большей мере удовлетворяет, требованиям потребителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Генератор цепей Маркова | 1982 |

|

SU1049903A1 |

| Устройство для вероятностного моделирования | 1980 |

|

SU922707A2 |

| Устройство для определения законов распределения вероятностей | 1984 |

|

SU1188753A2 |

| Датчик случайных чисел | 1983 |

|

SU1200285A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Генератор случайных чисел | 1980 |

|

SU922738A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

1. ГЕНЕРАТОР СЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащий генератор тактовых импульсов, датчик случайных двоичных равномерно распределенных чисел, вероятностный преобразователь, блок формирования статистических характеристик, причем выход генератора тактовых импульсов соединен с первым входом вероятностного преобразователя, о тличающийся тем, что, с целью расширения функциональных возможностей генератора путем задания матрицы переходов элементов формируемой последовательности в явном виде, он содержит блок формирования диапазона случайных чисел, блок формирования числа разрядов случайной последовательности,два блока элементов И, вычитатель, пять элементов ИЛИ, блок формирования функгши распределс-пия, три коммутатор 1 и регигтр памяти, пои -этом RrioK фо 1мир1М.чння с г-чтиг-тических характеристик содержит регистр памяти, регистр задания начальных условий, регистр задания адреса, коммутатор, десять элементов И, регистр задания режима работы, дешифратор, регистр установки исходного состояния, счетчик, три элемента ШШ, элемент задержки, регистр сдвига, элемент НЕ, D-триггер два RS-триггера и форшфователь пускового сигнала, блок формирования диапазона случайных чисел содержит два элемента задержки, два элемента НЕ, пять элементов И, элемент ИЛИ, схес му сравнения, D-триггер, RS- триггер ifi и регистр сдвига, блок формирования ел функции распределения содержит два элемента НЕ, регистр сдвига, пять элементов И, элемент ИЛИ, счетчик, схему сравнения, элемент задержки, два RS-триггера, регистр памяти, коммутатор, выход регистра установки исходного состояния блока формироСХ) вания статистических характеристик о соединен с R-входом счетчика, с R00 00 входом регистра сдвига, с R-входом р-триггера,с первыми R-вгодами RSтриггеров этого же блока и с вторым ч входом вероятностного преобразователя, выход регистра памяти блока формирования статистических характеристик соединен с первым информационным входом первого коммутатора, прямой выход первого RS-триггера блока формирования статистических характеристик соединен с управляющими входами первого и второго коммутаторов, второй R-вход первого RS-триггора блока формкрования статистич(;ск;1х характеристик соединен с Bf.ixivu)M исргполне

3

u40

Фиг.

| Генератор случайных последовательностей чисел | 1980 |

|

SU935953A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляемый датчик случайных чисел | 1978 |

|

SU771653A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU943722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1983-07-29—Подача