(54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1983 |

|

SU1108614A1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU951301A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Генератор псевдослучайных чисел | 1985 |

|

SU1272484A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1010622A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Генератор псевдослучайных чисел | 1987 |

|

SU1529218A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПРОДОЛЖИТЕЛЬНОСТИ ВЫЧИСЛИТЕЛЬНОГО ЭКСПЕРИМЕНТА, ПРОВОДИМОГО НА ЭВМ | 1991 |

|

RU2011220C1 |

Изобретение относится к вычислительной технике и июжет быть использовано при моделировании систем массового обслуживания и как датчик случайных при стохастических испытаниях.

Ишестны генераторы псевдослучайных чисел, содержащие генератор М-последовательностиГП и 2

Недостаток этих устройств заключается в том, что они являются не регулируемы-jQ ми.

Известен также генератор псевдослучайных чисел, содержащий датчик равномерно распределенных псевдослучайных чисел, регистр кода, датчик потоков им- )5 пульсов, логические элементы И, .

Это устройство позволяет изменить вероятность появления единичного сигнала на своих выходах, однако с его помощью нельзя noJTy4HTb заданный закон распреде го ления чисел.

Наиболее близким техническим решением к изобретению является управляемый датчик случайных чисел, содержащий генератор равномерно распределенных случайных чисел и последовательно соединенные блок ввода функции распреаеле151я, блок параллельного сравнения чисел и дешифратор, причем генератор равномерно распределенных чисел соединен с дешифратороми блоком параллельного сравнения чисел 43.

Недостатком такого устройства является отсутствие средств для формяроваиия пceвдocJ1yчaйныx процессов, опнсываемык разными матрицами переходных вероятностей и одним и тем же заданным вектором стацисиарного распре делювия, что сужает область применения устройства, так как в ряде случаев, например при моделировании систем массового обслуживания, воаника г ет необходимость формирования именно таких прсдаессов.

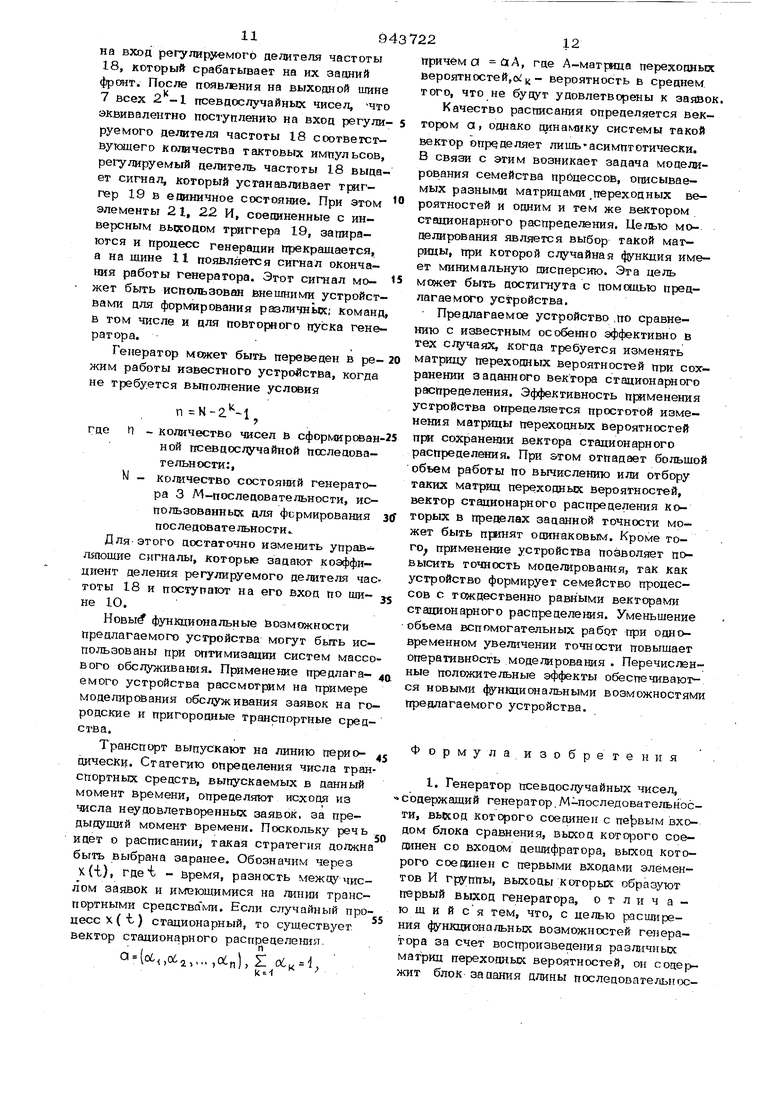

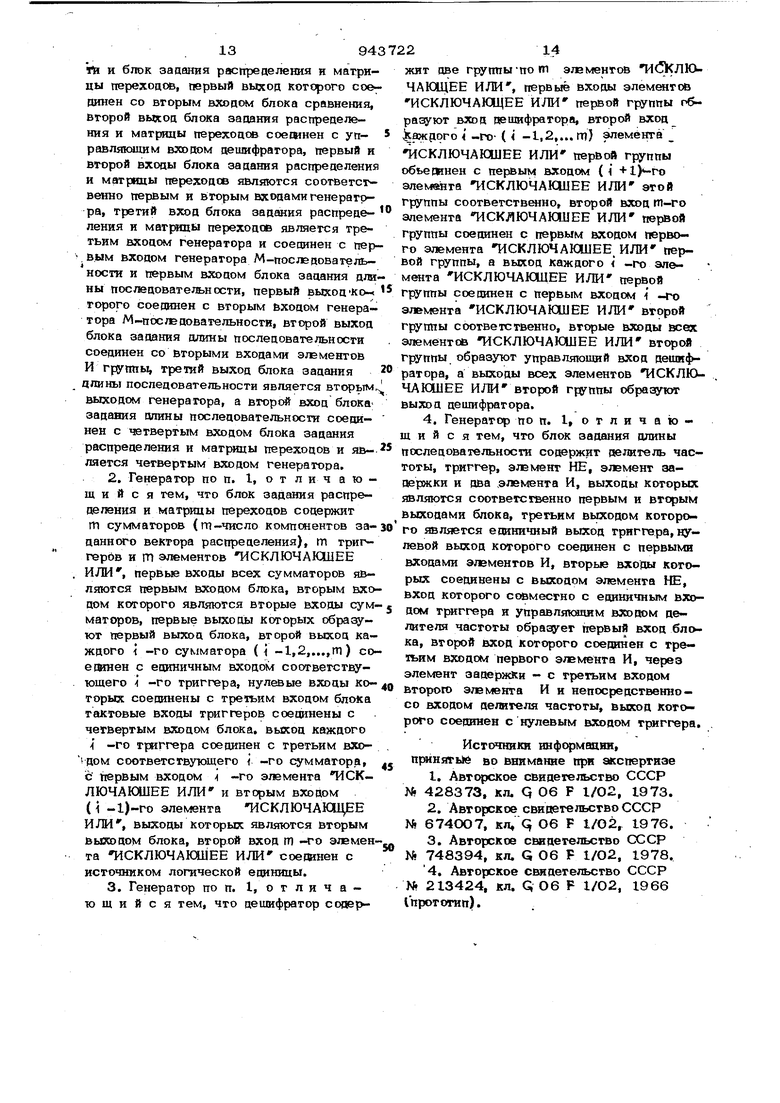

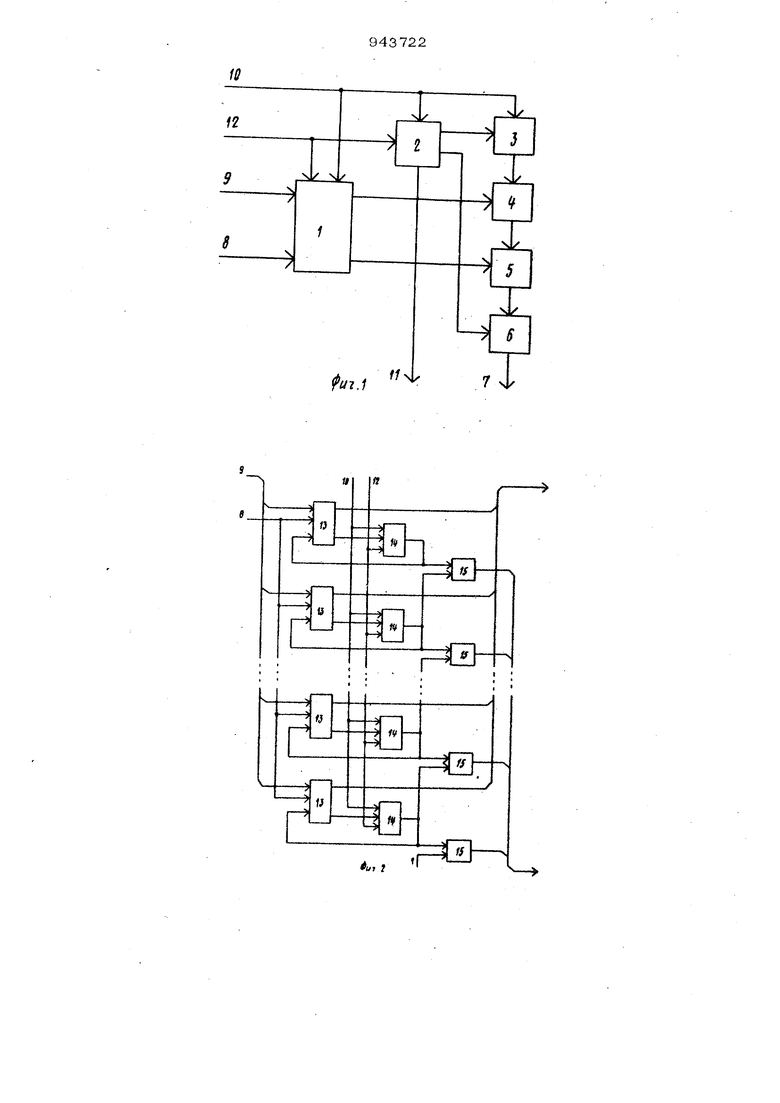

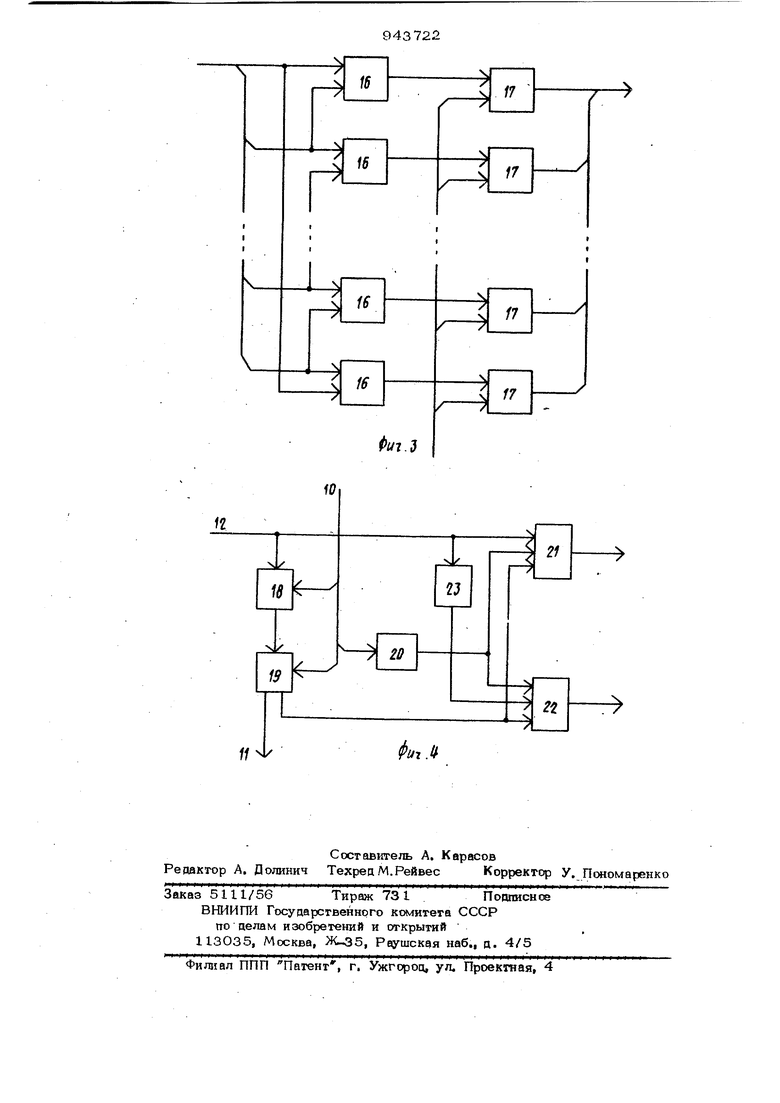

Цель изобретения - формирование псевдослучайных процессов, описываемьк разными матртцами переходных вероятностей и одним и тем же заданным вектором стационарного распределения, т.е. расширение функциональньк возмтокностеЛ. Для достижения поставленной цели в известный генератор псевдослучайных чисел, содержащий генератор М-последовательности, выход которого сое{шнен с пер вым входом блока сравнения, выход которого соединен со входом дешифратора, вы ход которого соещшен с первыми входами элементов И группы, вьвсод которых является первым выходом генератора, введены блок задания дшны последовательности и блок задания растфеделения и матрицы пе реходов, первые выход которого соединен с вторым входом блока сравнения, второй выход блока задания распределения и матрицы переходов соединен с управляющим входом дешифратора, первый и второй входы блока задания распределения н матрицы переходов являются соответственно первым и вторым входами генератора, третий вход блока задания распределения и матрицы переходов является третьим входом генератора и соединен с первым входом генератора М-последовательнодти и первым входом блока задания длины последовательности, первый выход которого соединен с вторым входом генератора М-последовательности; второй вы ход блока задания длины последовательности соединен со вторыми входами элементов И группы, третий выход блока заДания длины последовательности является вторым выходом генератора, а второй вход блока задания длины последовательности соединен с четвертым входом блока задания распределения и матрицы переходов и является четвертым входом генератора. Кроме того, блок задания распределения и матртцы переходов содержит m сумматоров (т-число компонентов заданного вектора распределения),m -триггеров и m элемент ИСКЛЮЧАЮЩЕЕ ИЛИ первые входы всех сумматоров являются первым входом блока, вторым входом которого являются вторые входы сумматоров, первые выходы которых образуют первый выход блока, второй выход каждого 1-го cy лмaтopa (i l,2,,,.,rti) соединен с единичным входом соответствующего -го триггера, нулевые входы которых соединены с третьим входом блока тактовые входы триггеров соединены с четвертым входом блока, выход каждого i -го триггера соединен с третьим входом соответствующего i -го сумматора, с первым входом -го элементаИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом (i -1)-г элемента ИСКЛЮЧАКХИЕВ ИЛИ , выходы которых явл5потся вторым выходом блока, второй вход ИП-го эле мент аИСК Л ЮЧ А ЮШЕЕ ИЛИсоединен с источником логической единицы. Кроме того, дешифратор содержит две группы по m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ , первые входы элементов ИСКЛЮЧАЮШЕЕ ИЛИС первой группы образуют вход деишфратора, второй вход каждого i -го i -l,2,...m) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ .первой группы объединены с первым входом ( t элементаИСКЛЮЧАЮЩЕЕ ИЛИэтой группы соответсгеенно, второй входт-го элемента ИСКЛЮЧАЮШЕЕ ИЛИ первой группы соединен. с первым входом первого элемента ИСКЛЮЧАЮШЕЕ ИЛИ этой группы, а выход каждого -го эле ментаИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с первым входом i -го эле мен т аИ С КЛЮЧ А1Ш1ЕЕ ИЛИ второй группы соответственно; вторые входы всех элементовИСКЛЮЧАЮЩЕЕ ИЛИ второй группы образуют управляющий вход деши ратора, а вькоды всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы образуют вькод дешифратора. Кроме того, .блок задания длины пос ледова тельное га содержит делитель частоты, тртггер, элемент НЕ, элемент задержки и два элемента И, вькоды котоР Х являются соответственно первым и вторым выходами блока, третьим выходом которого является единичный вькод триггера, нулевой выход которого соединен с первыми входами элементов И, вторые входы которых соединены с вькодом элемента, НЕ, вход которого совместно с единичным входомтриггера и управляющим входом делителя частоты образует первый взсод блока, второй вход которого соединен с третьим входом первого эле- . мента И, через элемент задержки - с третьим входом второго элемента И и непосредственно - со входом далителя частоты, вькод которого соединен с нулевым Вькодом триггера. На фиг. I приведена блок-схема сгенератора:, на фиг. 2 приведена схема блока задания распределения и матрицы переходов;, на фиг. 3 - схема дешифратора; на фиг. 4 - схема блока задания длины последовательности. Генератор содержит блок 1 задания распределения и матрицы переходов, блок 2 задания длины последовательности и последовательно соединенные генератор 3 М-последовательности, блок 4 параллельного сравнения, дешифратор 5 и блок 6 элементов И, группа вькоцов которого образует шину 7 и является первым выхо594дом генератора. Первая группа входов блока I образует шину 8, является первым входом генератора и служит для заДания матрицы переходов. Вторая группа входов блока I образует шину 9, является вторым входом генератора и служит для задания вектора распределения. Первая группа выходов блока 1 соединена с второй группой входов блока 4 параллельного сравнения, а вторая группа выходов соединена с второй группой входов деши({ ратора 5. Третий вход блока 1, первый .вход блока 2 задания длины последовательности и первый вход Генератора 3 Мпоследовательности образуют шину Ю УСтановки исходного состояния. Которая является третьим входом генератора. .Первый выход блока 2 задания длины последовательности соединен с вторым входом генератора 3 М-последовательности, второй выход блока 2 соединен с вторым входом блока 6 элементов И, третий выход образует шину 11, которая является вт.орым выходом генератора и по которой на внешние устройства поступает сигнал об окончании прадесса генерации. Второй вход блока 2 соединен с четвертым входом блока 1 и шиной 12, которая является четвертым входом генератора и по которой поступают тактовые «мпульсы. БЛ.ОК 1 задания распределения и матрщы переходов состоит из сумматоров 13. mD-триггеров 14. и m элементов 15 ИСКЛЮЧАКШЕЕ ИЛИ , причем первые входы сумматоров 13 соединены с шиной 8, вторые входы сумматоров 13 соединены с шиной 9, первые выходы сумматоров 13 соединены первым , блока 1 задания распределения и матрицы переходов, а второй выход 4 -го сумматора соединен с первым входом 1-го триггера 14, вьссод которого соединен с третьим входом 1-го сумматора 13, первым /входом -i -го элемента 15 ИСКЛЮЧАЮЩЕЕ , . ... ,npP ипй та 15 ИСКЛЮЧАЮЩЕЕ ИЛИ пр гчем второй вход m -го элемента .15 ИС.КЛЮЧАЮШЕЕ-ИЛИ соединен с источНИКОМ уровня логической единицы. Вторью входы триггеров 14 соединены с шиной 10, третьи выходы триггеров 14 соединены с ШИНОЙ 12, а выходы элементов 15 ИСКЛЮЧАКЩЕЕ ИЛИ соединены с вторым выходом блока 1 задания распределе ния и матрицы переходов. Дешифратор 5 содержит m элементов 16 ИСКЛЮЧАЮ ЩЕЕ ИЛИ и m элементов 17 ИСКЛЮЧА ЮЩЕЕ ИЛИ , причем первые входы элементов 16 каждого разряда соединены с Й6 первым входом дешифратора 5, вгорой вхоц элемента 16 каждого разряда соединен с первым входом элемента 16 последующего разряда, а. второй вход элемента 16 стпрщего разряда соединен с первым входом элемента 16 первого разряда, выход элемента 16 в каждом разряде соединен с первым входом элемента 17 ИСКЛЮЧАЮЩЕЕ ИЛИ того же разряда, вторые входы которых соединены с вторым входом дешифратора 5, а выходы элементов 17 ИСКЛЮЧАЮиЕЕ ИЛИ соединены с выходом дешифратора 5. Блок 2 задания длины последовательности содержит регудируемый делитель частоты 18, триггер ig, элемент 20 НЕ, элементы 21, 22 И „ элемент 23 задержки, вход которого соещгаен с первым входом эшмента 2 1 И, первым входом регулируемого делителя частоты 18 и шиной 12. Вход элемента 2О НЕ, первый вход триггера 19 и втор д од регулируемого делителя частоты 18 соединены с шрной Ю. Выход элемента 0 НЕ соединен с вторым входом элеменга 2 I и первым входом элемента 22И, второй вход которого соединен с выходом элемента 23 задержки. Выход регулируе делителя частоты 18 соединен с торым входом триггера 19, первый которого соединен с третьим входом элемента 21 И и третьим входом элемен а 22 И. Второй.выход триггера 19 сое элемента 21 И соешшен с первым выходом блока 2 зада„„д последовательности; а выход элемента 22 и соединен с вторым выходом того же блока. . Устройство работает следующим образом. Генератор 3 М-последоватейЬности имеет 2 .-1 состояний, где к - число триггеров в регистре генератора 3. Эти состояния закодируем числами от I до 2 -1 будем использовать все множество чисел. Разобьем это множества на-пГ-непустых непересекаюишхся подмножеств (Q. Если состоянию генератора 3 отвечает число , будем считать, что устройство в Этот момент времени „ одится в состоянш а . Обозначим череза,(1 ) событие, означающее, что в омшт t устройство нахгдатся в. состо д,. символомр( а) - относит.елы ную частоту наблюдения события, а за время прохождения генератором 3 всего множества 2 Iсостояний. Тогда .(,ш1- Г4P(o((t)) с - число перехоаов из состо5шия 0 в сосгояние dj ,с - число наотуп/лений события 0ц (число элементов попмножества , - отяосигельная час тота перехода усгройсгва иэ состояния 0({ в состояние dj . Матрица перехопов А(( ), элементы которой вычислены по формуле (I), является стохастической и неразложимой. Стационарное распрецеление, отвечающее этой матрице, имеет компоненты С / /(), ,2,.,., m . Вектор распределения задают с помощью чисел Г , г ,. ни определяюищх нижние границы noдмнoнcecтвa| Q j. Эти «сла через блок I задания распределения и мат(ящы переходов поступают в блок 4 параллельного сравнения, который в сочетании с. дешифратором 5 осуществляет разбиение множества чисел генератора 3 на m подмножестваЙД и определяет, для какого значения м выполняется условие Появление единичного сигнала и а -ом выходе дешифратора 5 означает выполнение ус ловия е{0 и переход устройства в сосгояние а . Полученный процесс имеет стационарный вектор с ком понентами Га-гО ) ,(,-Р) , . . При этом q«r,.,r.,b-l.2,...,m-i.с„, 2«-1. т- -f-t-r -t mi .,if f. Увеличим все значения г на одну и ту же ветчину Аг О, 1,2,...,2 -2. Это Приведет к изменению матрицы переходов поскольку Во всех подмножествах {Qi} изменится состав э;юментов. Число же элементов в подмножествах fQЛ останется прежним с()-( Ь и- - 1Следовательно, при изменении всех значений на одну, и ту же веодчину вектор распределения не меняется. Таким образом, увеличивая все значения Г на величинудг 0,1,2,.. , 2 -2, можно получить псевдос/учайных посждовагельностей на выходе дешифратора 5, имеющих разные матртцы переходных вероятностей и один и тот же вектор стациО-v нарного распределения. Матрицу переходов задают с гдомодью числа ,Д г . Это число поступает по шине 8 в олок 1 задания распределения и матрицы переходов и суммируется с числами Т , поступающими по шине 9, Суммы,5 образуются по следутодему Щ)аЁ1«лу: fc ДГ ,при Г vAri (2ч)при р + Полученные значения сумм 5 используют при разбиении множества чисел генератора 3 в качества новых значений Г|, т.е. принимаются . Эти числа с выхода блока 1 поступают на вход блока 4 параллельного сравнения. ЁслиЛГ О, то и на выходе блока 4 формируется мтотонная функция распределения. Если , то для одного из значений П Г и монотонность wKuxa распределения нар(ушается. Это приводит к необхооимости управ;юния работой дешифратора 5. Такое управление осуществляется путем выделения и блоке I того значения/} , щт котором Г , Шолу- ченное значение поступает на второй вход дёшифратора 5 в виде единичного позиционного кода и перестраивает его логическую функцию Ри V-i Lyuty y {4-iyi Ри для i 1,2,...,гл-1 , вля X « m имеем .. РИ Зоесь Zi - лотическая функция -( -го выхода дешифратора 5, f -логический уровень i выхода блока 4, причем го, при,.п j, ,пр11 (,, . i-,2,...,m где ( - псевдослучайное число, поступающее в блок 4 с BbORooa генератора 3. В результате коррекции логической функции дешифратора 5 на его выходе по.гчают заданный вектор распределения, описываемый выражением (2). Матрица переходов полученного псевдослучайного процесса определена сформированными значениями г, 5 причем 5 вычисля 9Й4ется по формуле (3), Элементы матрицы перехоцов могут быть вычислены по формуле (I). Устройство работает следующим обраВектор CTajMOHajftioro распределения задают с помощью R-разрядных двоичных чисел Г , которые поступают в блок I задания распределения и матрицы переходов по шине 9. Матрицу переходе задают с помощью к-разрядного двоичного чис ла Д г , которое поступает в блок I по шине 8. В блоке 1 (см. фиг. 2) эти числа поступают на k -разрядные суммато ры 13, число которых равно m . Если -I, на выходе переноса д -го сумматора 13 появляется уровень логической единицы. D г-триггеры 14 перед началом работы устанешшвают в исходное нулевое состояние сигналом, поступающим по шине 10. Начало работы определяется моменгрм снятия сигнала установки исходкого состояли. этом тактовые импульсы, псктупающие на синхроьход тригj rejTOB.14 по шине 12, устанавливают -и триггер 14 в единичное состояние, еслиГ 4ЛГ 2-- I, или в нулевое состояние, еслиГ;-f ЛГ . С выхода -i -го триггера 14 сигнал поступает на вход переноса -го сумматора 13. При этом формирование суммы -i -м сумматором 13 осуществляется согласно формуле (3). По лученные значения поступают в блок 4 параллельного сравнения. Элементы 15 ИСКЛЮЧАЮЩЕЕ ИЛИ служат для отыскания интервала , в котором нарушается монотинность функции распределения. При монотонной функции распределения на выходах i -го и (+1)-го триггеров 14 присутствует уровень логического нуля и; следовательно; на выходе { -го элемента 15 ИСКЛЮЧАЮШЕЕ ИЛИ также имеем уровень логического нуля. Если же в i - tri интервале монотонность функции распределения нарушается, то на выходе ( +1)-го триг гера 14 появляется уроВ(внь логической единицы. При этом на выходе i го элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ таюке появляется урстень логической единицы, который поступает в дешифратор 5 и изменяет логическую функцию -го выхода дешифратора 5. Генератор 3 М-последователыюсти фо мкрует к-разрядные псевдослучайные двоичные числа, которые поступают в блок 4 параллельного сравнения, где сравнивеется со значениями интервалов равнения множества чисел генератора 3. Впок 4 210 соиержиг m схем сравнения и формирует функиию распределения, причем для V -ой схемы сравнения имеет место соотношение (6), Кодовые комбинации, описывающие функцию распределения, поступают на вход дешифратора 5, функциональная схема которого изображена на фиг. 3. Дешифрг тор 5 состоит из элементов 16 и 17 ИСКЛЮЧАЮЩЕЕ ИЛИ , причем группа э/вменгов 1б ТЮКЛЮЧАЮЩЕЕ ИЛИ для кодовых комбинаций блока 4, а группа элементов 17 ИСКЛЮЧАЮЩЕЕ ИЛИ служит для коррекции группы элементов 17. Логическая функция -го выхоси дешифратора 5 описывается выражениями (4) и (5). Псевдосдучзйный прсцесс, заданный с помощью чисел г и лг , формируется на выходах элементов 17 иИСКЛЮЧАЮЩЕЕ ИЛИ . Мат{жца переходных вероятностей и вектор стационарного распределения этого процесса описываются выражениями ( 1) и (2) соответственно, если количество чисел в сформированной псевдослучайной последовательности и количество использованных для этой цели состояний генератора 3 М-последовательности буСО т равны 2-1 нлк кратны этому чкспу. Выполнение этого условия обеспечивает блок 2 задания д«шы последовательности, функциональная схема которого изображена на фиг. 4. Перед началом работы регулируемый делитель частоты 18 устанавливают в исходное, нулевое состояние. управляющие входы подают сигнал, задакшие требуемый коэффициент деления, Управляющие сигналы и сигнал установки нулевого состояния поступают на шине 10. Одновременно по шине 1О поступают игнал устанадки нулевого состояния триГ-. Р сигнал блокировки, который иивертируется элементом 2О НЕ и запираег элементы 21, 22 И. Момент начала работы определяется моментом снятия сигна- лов установки состояния и блокировки,-При этом элементы 21, 22 И отпираются и на вход генератора 3 через элемент 21 И начинают поступать TISKтовые импульсы с шины 12. На выхо|1е элэмеита 22 и тактовые импульлы появляются с засеержкой, так как предварительно проходят через элемент 23 задержки. Величину задержки определяют исходя из условия окончания переходных процессов в блоках 3,4,5. Задержанные тактовые импульсы используются для стробирования. выходов деиифратора 5, что осущесгаляется с помощью блока 6 элэментов И. Одновременно такгсеые импульсы поступают на вход регулир}5емого делителя частоты 18, который срабатывает на их задний фронт. После появления на выходной шине 7 всех 2-1 псевдослучайных чисел, -что эквивалентно поступлению на вход регулируемого делителя частоты 18 соотвегсгвукнцего количества тактовых импульсов, регулируемый делитель частоты 18 выдает сигнал, который устанавливает Tf irгер 19 в единичное состояние. При этом элементы 21, 22 И, соединенные с инверсным выходом триггера 19, запираются и процесс генерации прекращается, а на щине 11 появляется сигнал окончания работы генератора. Этот сигнал может быть использован внешними устройствами для формирования разлидаьос; команд в том числе и для повторного пуска генератора. Генератор может быть переведен в ре- 20 жим работы известного устройства, когда не требуется выполнение условия п где П - количество чисел в сформирован-25 ной псевдосдучайной последовательности:, N - количество состояний генератора 3 М-последовательности, ис- пользованных для формирования последовательности.. Для-этого достаточно изменить управляющие сигналы, которые задают коэффициент деления регулируемого делителя час тоты 18 и поступают на его вход по шине 1О. Новы функциональные Возможности предлагаемого устройства могут быть использованы при оптимизации систем массо вого обслуживания. Применение предлагаемого устройства рассмотрим на примере моделирования обслуживания заявок на городские и пригородные транспортные средства. Транспорт выпускают на линию периодичесКи. Статегию определения числа тран спортных средств, выпускаемых в данный момент времени, определяют исходя из числа неудовлетворенных заявок, за предыдущий момент времени. Поскольку речь идет о расписании, такая стратегия должна быть выбрана заранее. Обозначим через x(t). где. - Время, разность между числом заявок и имеющимися на линии транспортными средствами. Если случайный процесс X ( Ь ) стационарный, то существует вектор стационарного распределешит. а (об,,об2,.., ,обп),, 94 2212 причём а аА, где А-матрииа переходных вероятностей, - вероятность в среднем того, что не будут удовлетворены к заявок. Качество расписания определяется вектором а, однако данамику системы такой вектор определяет лишь-асимптотически. В связи с этим возникает задача моделирования семейства процессов, описываемых разными матрицами .переходных вероятностей и одним и тем же вектором стационарного распределения. Целью моделирования является выбор такой матрицы, при которой случайная нкиия имеет минимальную дисперсию. Эта цель может быть достигнута с помощью предлагаемого устройства. Предлагаемое устройство ,по сравнению с известным особенно эффективно в тех случаях, когда требуется изменять матрицу переходных вероятностей при созгранении заданного вектора стационарного распределения. Эффективность применения устройства определяется простотой изменения матрицы переходных вероятностей прк сохранении вектора стационарного распределения. При этом отпадает большой обьем работы по вычислению или отбору таких матриц переходных вероятностей, вектор стационарного распределения когорых в пределах заданной точности может быть принят одинаковым. Кроме тогo применение устройства позволяет повысить точность моделирования, так как устройство формирует семейство процес ° тождественно равными векторами стационарного распределения. Уменьшение объема вспомогательных работ при одновременном увеличении точности повышает оперативность моделирования . Перечисдан ® положительные эффекты обеспечиваются новыми функциональными возможностями предлагаемого устройства. Ф ормулаизобрете ни я 1. Генератор псевдос/;учайных чисел, содержащий генератор. М-последовательности, вь«од которого соединен с первым входом блока сравнения, выход которого соединен со входом дешифратора, выход которого соединен с первыми входами элементов И группы, выходы которых образуют первый выход генератора, о т л и ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей генератора за счет воспроизведения различных матриц переходных вероятностей, он содержит блок задания длины последовательноеfh и блок зацания распределения и матрицы переходе, первый выход которого сое динен со вторым входом блока сравнения, второй ввдсод блока задания распределения и матрицы переходов соеданен с управл5пощим входом дешифратора, первый и второй входы блока задания распределения и матрицы переходсв являются соответственно первым в вторым входами генератора, третий вход блока задания распределения и матртцы переходов является третьим входом генератора и соединен с пер . вым входом генератора М-последователь- ности и первым входом блока задания дли ны последоватета:,ности, первый выход-ко-; торого соединен с вторым входом генератора М-посждовательности, второй выход блока задания длины последовательности соединен со вторыми входами э;кментов И группы, третий выход блока задания цлины последовательности является вторьпи выходом Генератора, а второй вход блоказадания дгшны последовательности соединен с четвертым входом блока задания распределения и матрицы переходов и является четвертым входом генератора. 2. Генератор по п. I, о т л и ч а ю щ и и с я тем, что блок зацания распределения и матрицы переходов содертшт m сумматоров (т-число компшентов заданного вектора распределения), m триггеров и m эжментов ИСКЛЮЧАЮЩЕЕ ИЛИ , первые входы всех сумматоров явЛ5потся первым входом блока, вторым BXf дом которого являются вторые входы сум маторов, первые выходы которых первый выход блока, второй выход каждого i -го сумматора ( -1,2,...,т) со ешянен с единичным входом соответствующего i -го триггера, нулевые входы которых соединены с третьим входом блока тактовые входы триггеров соеданены с четвертым входом блока, вьссод каждого -го триггера соединен с третьим вхоНдом соответствующего I -го сумматора, с первым входом н -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом (i -1)-го элемента ИСКЛЮЧАЮи БЕ ИЛИ, выходы которых являпотся вторым выходом блока, второй вход m -го элемен та ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с источником логической единицы. 3. Генератор по п. 1, о т л и ч а ю щ и и с я тем, что дешифратор сооер94214 жит две группы-пот эжментов ИС ЛЮЧАЮЩЕЕ ИЛИ , первые входы элементш ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы обращуют вход дешифратора, второй вход аждого t -го- ( -1,2,... т) элемента ИСКЛЮЧАЮЩЕЕ или первой группы обье синен с первым входом ( -Ibro элемента ИСКЛЮЧА1СШЕЕ ИЛИ этой группы соответственно, второй вход т-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, а вьвсод каждого -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с первым входом i -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соответственно, вторые входы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы образуют управляющий вход дешифратора, а выходы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы образуют выход дешифратора. 4. Генератор по п. 1, о т л и ч а ю щ и и с я тем, что блок задания длины последовательности содержит делитель частоты, триггер, элемент НЕ, элемент задержки и два .элемента И, выходы которых явл5потся соответственно первым и вторым выходами блока, третьим вьрсодом которого является единичный выход триггера, нулевой выход которого соединен с первыми входами элэментов И, вторые входы которых соединены с выходом элемента НЕ, вход которого совместно с единичным входом триггера и управлякицим входом целителя частоты обра;эует первый вход блока, второй вход которого соединен с тре- входом первого элемента И, через элемент задерх си - с третьим входом второго элемента И и непосредственносо входом делителя частоты, выход котснрого соединен с нулевым входом триггера. Источники ВНФСФМШ1ИИ, П{мснятыб во внимание при экспертизе 1,Авторское свидетельство СССР N 428373, кл, Q 06 F 1/02, 1973. 2,Авгорсксе свипетальство СССР N 674ОО7, кп, q Об F 1/О2, 1976. 3,Авторское свидетельство СССР N 748394, кл, Q 06 F 1/О2, 1978. 4, Авторское свидетельство СССР № 213424, кл. Q Об F 1/О2, 1966 Спрототип),

ff vj/

//z.

Авторы

Даты

1982-07-15—Публикация

1980-12-29—Подача