Изобретение относится к вычислительной технике и может быть использовано в устройствах управления специализированных цифровых вычислительных машин (СЦВМ) для обеспечения от- , ладки программ вычисления сложных математических функций.

Цель изобретения - расширение класса решаемых задач за счет обеспечения статистического контроля вы- 10 числительных программ.

Предлагаемое устройство реализует вероятностный метод тестирования программ, сущность которого заключается

подробно описан и сводится к вычисле нию законов распределения значений функций от случайных аргументов. Пре имуществом является то, что расчеты эталонных вероятностных характеристик для любой программы из рассматриваемого класса вычислительных прог рамм выполняются по одному и тому же алгоритму. Описан также метод опреде ления доверительных интервалов для значений вероятностных характеристик выходных случайных величин для задан ной доверительной вероятности (достоверности правильного обнаружения

в следующем. На вход испытуемой прог-15 ошибки). Блок статистических нали- раммы подаются наборы значений входных переменных, представляющих собой случайные числа, распределенные по некоторому закону. На каждом из наборов реализуется программа и определяются вероятностные характеристики случайных величин,, являющихся вы- ходньми для выбранного множества кон20

заторов устройства вычисляет МОЖ выходных величин. Сравнение вычисленных МОЖ с эталонными производится оператором вручную.

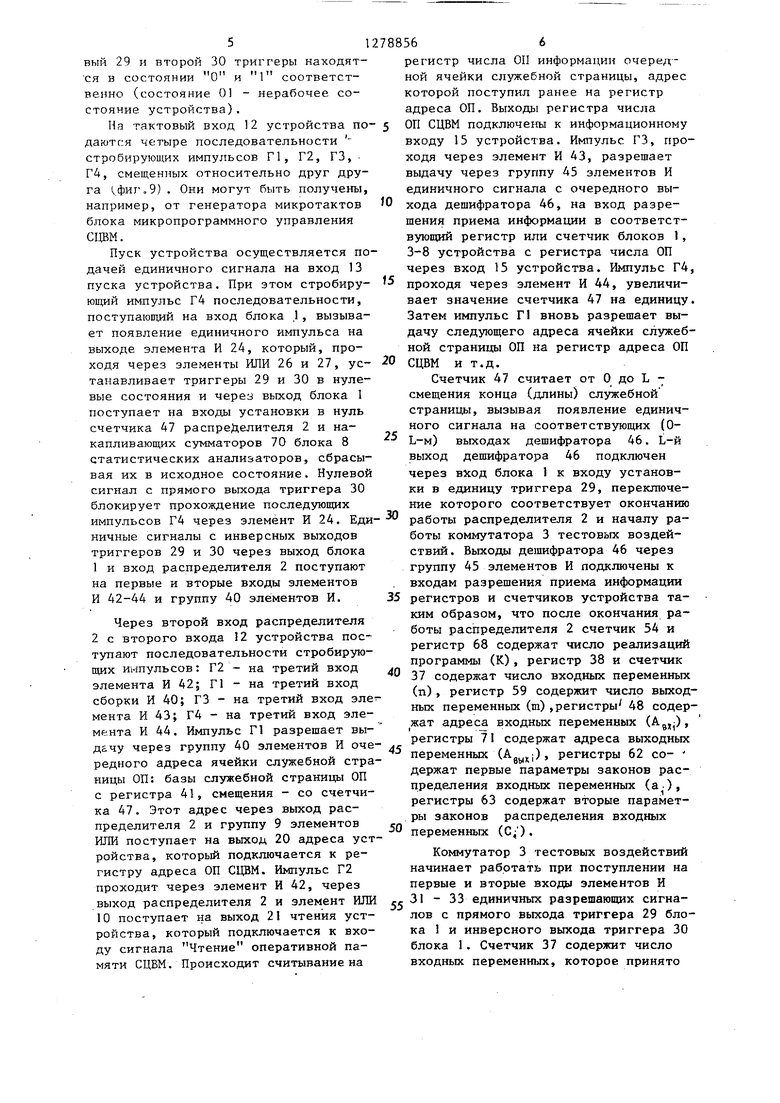

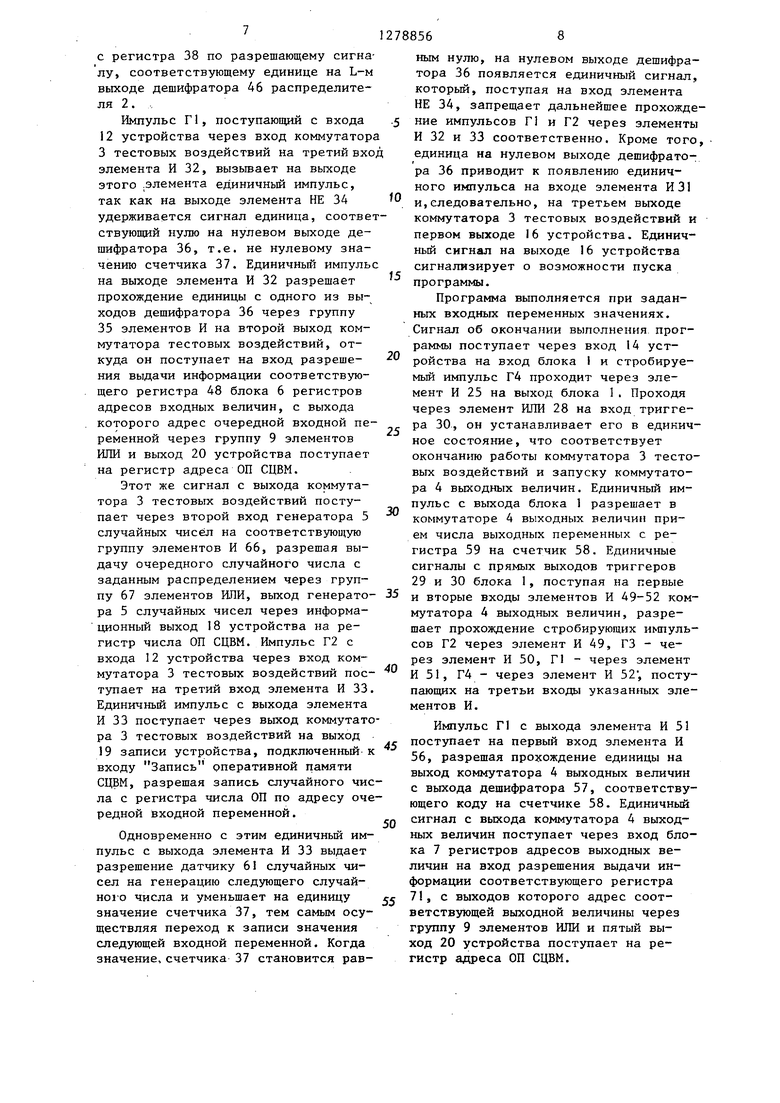

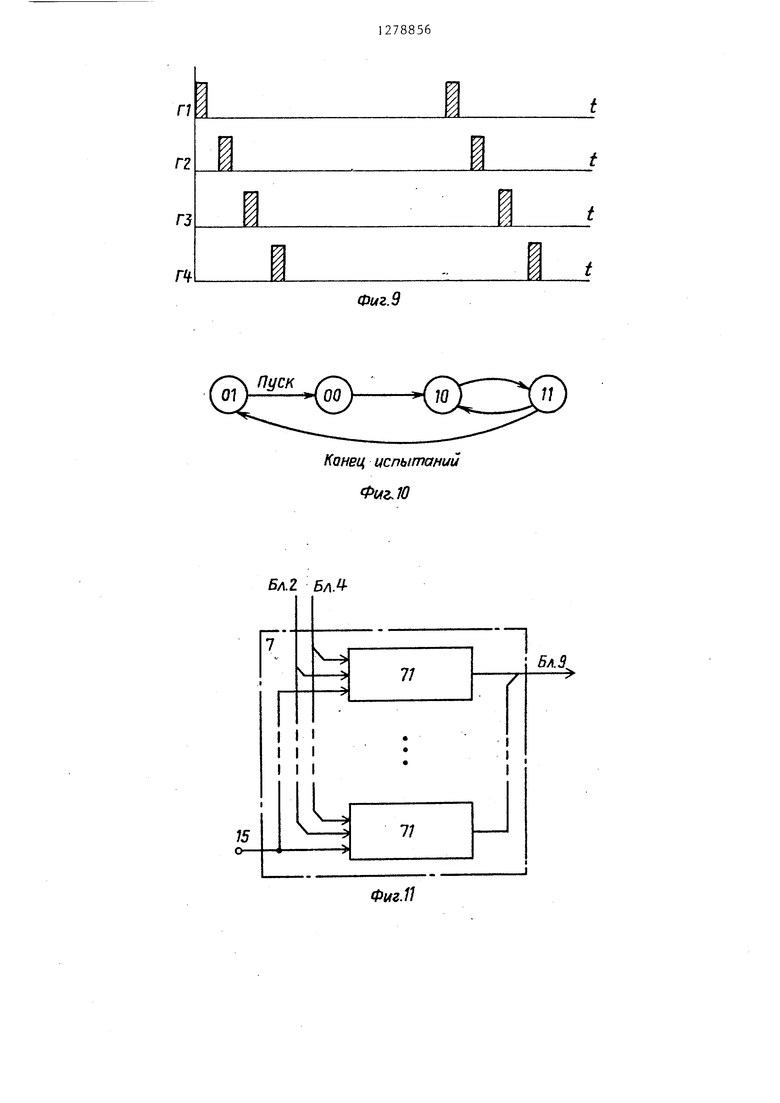

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока задания режима; на фиг.З - структурная схема коммутатора тестовых воздействий; на фиг.4 структурная схема распределителя импульсов; на фиг.5 - структурная схема блока регистров адресов входных величин; на фиг.6 - структурная схема коммутатора выходных величин; на фиг.7 - структурная схема генератора случайных чисел; на фиг.8 - структур ная схема блока статистических анализаторов; на фиг.9 - временные диаграммы стробирующих сигналов; на фиг.10 - граф автомата, реализованного блоком управления устройства; на фиг.11 - структурная схема блока регистров адресов выходных величин; на фиг.12- структура служебной страницы оперативной памяти СЦВМ.

трольньпс точек программы. Полученные вероятностные характеристики сравниваются с эталонными, полученными в результате аналитического.расчета по алгоритму, подлежащему реализации испытуемой программой, для тех же зако ;нов распределения входных переменных. В зависимости от степени совпадения экспериментально определенных вероятностных характеристик с зта-п лонными делается вывод о правильности программы или наличии в ней ошибок с определенной доверительной вероятностью.

В предлагаемом устройстве в качестве вероятностных характеристик используются первые моменты (математические ожидания) случайных ве- личин Z; на выходе программь, рас3

считываемые по формуле

.

ilZ

Z.

it

к

И

t-1

5ie, К

где Z, - значение, j-й выходной переменной после 1-й реализации программы; К - число реализаций программы.

Устройство рассчитано на генераУстройство для контроля вычислительных программ (фиг.1) содержит блок 1 задания режима, распределитель 2 импульсов, коммутатор 3 тестовых воздействий, коммутатор 4 вы-- ходных величин, генератор 5 случайных чисел, блок 6 регистров адресов входных величин, блок 7 регистров адресов выходных величин, блок 8 ста тистических анализаторов, группу 9 элементов ИЛИ, элемент ИЛИ 10, первый информационный вход 11 устройства, тактовые входы 12, вход 13 пуска

цию значений входных переменных программы, распределенных по равномерно- устройства, вхор 14 останова выпол- му закону внутри интервалов t аь Ь нения программы, информационный вход Метод аналитического расчета математических ожиданий выходных величин по входньм (не вьшолняя программы)

15, выход 16 пуска программы, выход 17 конца испытаний программы, информационный выход 18 устройства, выход

подробно описан и сводится к вычислению законов распределения значений функций от случайных аргументов. Преимуществом является то, что расчеты эталонных вероятностных характеристик для любой программы из рассматриваемого класса вычислительных программ выполняются по одному и тому же алгоритму. Описан также метод определения доверительных интервалов для значений вероятностных характеристик выходных случайных величин для заданной доверительной вероятности (достоверности правильного обнаружения

ошибки). Блок статистических нали-

заторов устройства вычисляет МОЖ выходных величин. Сравнение вычисленных МОЖ с эталонными производится оператором вручную.

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока задания режима; на фиг.З - структурная схема коммутатора тестовых воздействий; на фиг.4- структурная схема распределителя импульсов; на фиг.5 - структурная схема блока регистров адресов входных величин; на фиг.6 - структурная схема коммутатора выходных величин; на фиг.7 - структурная схема генератора случайных чисел; на фиг.8 - структурная схема блока статистических анализаторов; на фиг.9 - временные диаграммы стробирующих сигналов; на фиг.10 - граф автомата, реализованного блоком управления устройства; на фиг.11 - структурная схема блока регистров адресов выходных величин; на фиг.12- структура служебной страницы оперативной памяти СЦВМ.

Устройство для контроля вычислительных программ (фиг.1) содержит блок 1 задания режима, распределитель 2 импульсов, коммутатор 3 тестовых воздействий, коммутатор 4 вы-- ходных величин, генератор 5 случайных чисел, блок 6 регистров адресов входных величин, блок 7 регистров адресов выходных величин, блок 8 статистических анализаторов, группу 9 элементов ИЛИ, элемент ИЛИ 10, первый информационный вход 11 устройства, тактовые входы 12, вход 13 пуска

устройства, вхор 14 останова выпол- нения программы, информационный вход

устройства, вхор 14 останова выпол- нения программы, информационный вход

15, выход 16 пуска программы, выход 17 конца испытаний программы, информационный выход 18 устройства, выход

19 записи, выход 20 адреса, выход 21 чтения, выход 22 результата контроля программы.

Блок 1 задания режима (фиг,2) содержит первый 23, третий 24 и вто- рой 25 элементы И, первьт 26, второй 27 и третий 28 элементы ИЛИ, первый 29 и второй 30 триггеры.

Коммутатор 3 тестовых воздействий (фиг.З) содержит первьш 31, второй 32 и третий 33 элементы И, элементы НЕ 34, группу 35 элементов И, дешифратор 36, счетчик 37, регистр 38 и элемент ИЛИ 39.

Распределитель 2 импульсов (фиг.4 содержит первую группу 40 элементов И, регистр 41 базы служебной страницы, первый 42, второй 43 и третий 44 элементы И, вторую группу 45 элементов И, дешифратор 46 и счетчик 47.

Блок 6 регистров адресов входных величин (фиг.5) содержит группу регистров 48.

Коммутатор 4 выходных величин (фиг.6) содержит первый 49, второй 50, третий 51 и четвертый 52 элементы И, элемент ШШ-НЕ 53, счетчик .54 числа реализаций программы, первую 55 и вторую 56 группы элементов И, дешифратор 57, счетчик 58 числа вы- ходных переменных и регистр 59.

Генератор 5 случайных чисел (фиг.7) содержит группу преобразователей 60, датчик 61 случайных чисел (ДСЧ), каждьш преобразователь 60 со- держит первый 62 и второй 63 регистры, множитель 64, сумматор 65 и элемент И 66, выходы всех преобразователей соединены с соответствующим входом группы 67 элементов ИЛИ.

Блок 8 статистических анализаторов (фиг.8) содержит регистр 68, группу делителей 69 на N, группу накапливающих сумматоров 70.

Блок 7 регистров адресов выходны5с величин (фиг.11) содержит группу регистров 71 .

Устройство работает следующим об

разом.

До запуска устройства в оперативную память (ОП) СЦВМ записывается тестируемая программа и информация служебной страницы, структура которой приведена на фиг.12. Служебная стра- ница располагается в ОП с адреса, кратного А 2 / L, где L - длина . служебной страницы. Старшие R-r разряды базствого адреса служебной стра12788564

ницы заносятся через первый вход

П

0

fO

15

ЗО

5 0

5

5

0

5

устройства на регистр, 4 распределителя 2 (R - общее число разрядов адреса в ОП СЦВМ). В нулевую ячейку служебной странигда должно быть записано число реализаций тестируемой программы К (размерность случайной выборки), в первую и вторую ячейки заносятся количества входных п и выходных m (контролируемых) переменных программы соответственно, адреса этих переменных для зафиксированного расположения тестируемой программы в ОП записываются в ячейки служебной с-траницы, отмеченные на фиг. 12 как А. и A(,b,xj соответственно. Количество входных переменных программы, которым при тестировании присваиваются случайные значения, распределенные по заданному закону, не может превышать значения N, аналогично количество анализируемых выходных переменных не должно превышать М (N и М - максимальные количества входных и выходных переменных программ, на которые рассчитано устройство). Кроме того, в служебной странице для каждой входной переменной программы задаются параметры равномерного закона распределения ее значений: а- - левая граница интервала и b ; - правая граница инлгервала, ,2,,..

Случайное число h , распределенное равномерно в интервале, получается из равномерно распределенного на интервале 0,1 случайного числа , поступаемого с ДСЧ 61, следующим образом:

, +(Ъ, - а,) а, , Эти преобразования осуществляются преобразователями 60 генератора 5 случайных чисел устройства. Если число входных (выходных) переменных n(m) меньше N(M), то их адреса и параметры законов распределения записываются подряд, начиная с первой ячейки соответствующей области служебной страницы. Остальные N-n(M-m) ячеек заполняются произвольной, например нулевой, информацией.

Блок 1 задания режима является автоматом с памятью и может находиться в текущий момент времени в одном из четырех состояний, определяемых состояниями первого 29 и второго 30 триггеров (граф переходов приведен на фиг.10). В исходном состоянии, в которое блок 1 переходит после окончания предыдущего цикла работы, первый 29 н второй 30 триггеры находят- ся в состоянии О и 1 соответственно (состояние 0 - нерабочее состояние устройства).

На тактовый вход 12 устройства по даются четыре последовательности стробирующих импульсов Г1, Г2, ГЗ, Г4, смещенных относительно друг друга чфиго9) , Они могут быть получены,

например, от генератора микротактов блока микропрограммного управления СЦВМ.

Пуск устройства осуществляется подачей единичного сигнала на вход 13 пуска устройства. При этом стробиру- ющий импульс Г4 последовательности, поступающий на вход блока ,1 , вызывает появление единичного импульса на выходе элемента И 24, который, проходя через элементы ИЛИ 26 и 27, устанавливает триггеры 29 и 30 в нулевые состояния и через выход блока I поступает на входы установки в нуль счетчика 47 распределителя 2 и накапливающих сумматоров 70 блока 8 статистических анализаторов, сбрасывая их в исходное состояние. Нулевой сигнал с прямого выхода триггера 30 блокирует прохождение последующих импульсов Г4 через элемент И 24. Еди ничные сигналы с инверсных выходов триггеров 29 и 30 через выход блока

1и вход распределителя 2 поступают на первые и вторые входы элементов И 42-44 и группу 40 элементов И.

Через второй вход распределителя

2с второго входа 12 устройства поступают последовательности стробирующих импульсов: Г2 - на третий вход элемента И 42; Г1 - на третий вход сборки И 40; ГЗ - на третий вход элемента И 43; Г4 - на третий вход элемента И 44. Импульс Г1 разрешает выдачу через группу 40 элементов И очередного адреса ячейки служебной страницы СП: базы служебной страницы ОП

с регистра 41, смещения - со счетчика 47. Этот адрес через выход распределителя 2 и группу 9 элементов ИЛИ поступает на выход 20 адреса устройства, который подключается к регистру адреса ОП СЦВМ. Импульс Г2 проходит через элемент И 42, через выход распределителя 2 и элемент ИЛИ 10 поступает на выход 21 чтения устройства, который подключается к входу сигнала Чтение оперативной памяти СЦВМ. Происходит считывание на

5

15

20

25

30

О

регистр числа ОП информации очередной ячейки служебной страницы, адрес которой поступил ранее на регистр адреса ОП. Выходы регистра числа ОП СЦВМ подключены к информационному входу 15 устройства. Импульс ГЗ, проходя через элемент И 43, разрешает выдачу через группу 45 элементов И единичного сигнала с очередного выхода дешифратора 46, на вход разрешения приема информации в соответствующий регистр или счетчик блоков 1, 3-8 устройства с регистра числа ОП через вход 15 устройства. Импульс Г4, проходя через эл ;мент И 44, увеличивает значение счетчика 47 на единицу. Затем импульс Г1 вновь разрешает выдачу следующего адреса ячейки служебной страницы ОП на регистр адреса ОП СЦВМ и т.д.

Счетчик 47 считает от О до L - смещения конца (;цлины) служебной страницы, вызывая появление единичного сигнала на соответствующих (0- L-M) выходах дешифратора 46. L-й выход дешифратора 46 подключен через вход блока 1 к входу установки в единицу триггера 29, переключение которого соответствует окончанию работы распределителя 2 и началу работы коммутатора 3 тестовых воздействий. Выходы дешифратора 46 через группу 45 элементов И подключены к входам разрешения приема информации регистров и счетчиков устройства таким образом, что после окончания работы распределителя 2 счетчик 54 и регистр 68 содержат число реализаций программы (К), регистр 38 и счетчик 37 содержат число входных переменных (п), регистр 59 содержит число выходных переменных (га) , регистры 48 содер- жат адресу входных переменных (Ац,-), регистры 71 содержат адреса выходных переменных (), регистры 62 со- держат первые параметры законов рас- цределения входных переменных (а ), регистры 63 содержат вторые параметры законов распределения входных переменных () .

Коммутатор 3 тестовых воздействий начинает работать при поступлении на первые и вторые входы элементов И „31 - 33 единичных разрешающих сигналов с прямого выхода триггера 29 блока 1 и инверсного выхода триггера 30 блока 1. Счетчик 37 содержит число входных переменных, которое принято

35

40

45

50

с регистра 38 по разрешающему сигналу, соответствующему единице на L-M выходе дешифратора 46 распределителя 2 .,

Импульс Г1, поступающий с входа 12 устройства через вход коммутатор 3 тестовых воздействий на третий вх элемента И 32, вызьтает на выходе этого .элемента единичный импульс, так как на выходе элемента НЕ 34 удерживается сигнал единица, соотвествующий нулю на нулевом выходе дешифратора 36, т.е. не нулевому значению счетчика 37. Единичный импуль на выходе элемента И 32 разрешает прохождение единицы с одного из выходов дешифратора 36 через группу 35 элементов И на второй выход коммутатора тестовых воздействий, откуда он поступает на вход разрешения выдачи информации соответствующего регистра 48 блока 6 регистров адресов входных величин, с выхода которого адрес очередной входной переменной через группу 9 элементов ИЛИ и выход 20 устройства поступает на регистр адреса ОП СЦВМ.

Этот же сигнал с выхода коммутатора 3 тестовых воздействий поступает через второй вход генератора 5 случайных чисел на соответствующую группу элементов И 66, разрешая выдачу очередного случайного числа с заданным распределением через группу 67 элементов ИЛИ, выход генерато ра 5 случайных чисел через информационный выход 18 устройства на регистр числа ОП СЦВМ. Импульс Г2 с входа 12 устройства через вход коммутатора 3 тестовых воздействий поступает на третий вход элемента И 33 Единичньй импульс с выхода элемента И 33 поступает через выход коммутат

Импульс Г1 с выхода элемента И 51

50

ра 3 тестовых воздействий на выход ,, поступает на первый вход элемента И

56, разрешая прохождение единицы на выход коммутатора 4 выходных величин с выхода дешифратора 57, соответствующего коду на счетчике 58. Единичный сигнал с выхода коммутатора 4 выходных величин поступает через вход блока 7 регистров адресов выходных величин на вход разрешения выдачи информации соответствующего регистра 71, с выходов которого адрес соответствующей выходной величины через группу 9 элементов ИЛИ и пятый вы19 записи устройства, подключенный к входу Запись оперативной памяти СЦВМ, разрешая запись случайного числа с регистра числа ОП по адресу очередной входной переменной.

Одновременно с этим единичный импульс с выхода элемента И 33 выдает разрешение датчику 61 случайных чисел на генерацию следующего случай- Hoi o числа и уменьшает на единицу значение счетчика 37, тем самым осуществляя переход к записи значения следующей входной переменной. Когда значение,счетчика 37 становится рав55

ход 20 устройства поступает на регистр адреса ОП СЦВМ.

8

J5

20

.5 0 5

25

0

0

ным нулю, на нулевом выходе дешифратора 36 появляется единичный сигнал, который, поступая на вход элемента НЕ 34, запрещает дальнейшее прохождение импульсов Г1 и Г2 через элементы И 32 и 33 соответственно. Кроме того, единица на нулевом выходе дешифратора 36 приводит к появлению единичного импульса на входе элемента И 31 и,следовательно, на третьем выходе коммутатора 3 тестовых воздействий и первом выходе 16 устройства. Единичный сигнал на выходе 16 устройства сигнализирует о возможности пуска программы.

Программа выполняется при заданных входных переменных значениях. Сигнал об окончании выполнения программы поступает через вход 14 устройства на вход блока 1 и стробируе- мьй импульс Г4 проходит через элемент И 25 на выход блока 1. Проходя через элемент ИЛИ 28 на вход триггера 30, он устанавливает его в единичное состояние, что соответствует окончанию работы коммутатора 3 тестовых воздействий и запуску коммутатора 4 выходных величин. Единичный импульс с выхода блока 1 разрешает в коммутаторе 4 выходных величин прием числа выходных переменных с регистра 59 на счетчик 58. Единичные сигналы с прямых выходов триггеров 29 и 30 блока I, поступая на первые и вторые входы элементов И 49-52 коммутатора 4 выходных величин, разрешает прохождение стробирующих импульсов Г2 через элемент И 49, ГЗ - через элемент И 50, Г1 - через элемент И 51, Г4 - через элемент И 52, поступающих на третьи входы указанных элементов И.

Импульс Г1 с выхода элемента И 51

,, поступает на первый вход элемента И

ход 20 устройства поступает на регистр адреса ОП СЦВМ.

91278856

Импульс Г2 через элемент И 49, выход коммутатора 4 выходных величин элемент ИЛИ 10 и выход 21 устройства поступает на вход Чтение ОП СЦВМ, вызывая считывание очередного значения выходной переменной, адрес которой был занесен на регистр адреса ОП, на регистр числа ОП СЦВМ,

Импульс ГЗ с выхода элемента И 50 поступает на первый вход элемента И 55, разрешая выдачу на выход коммутатора выходных величин единичного сигнала с выхода дешифратора 57, соответствующего коду на счетчике 58. Этот сигнал, соответствующий не нуле вому коду на счетчике 58, поступает через вход блока 8 статистических анализаторов на вход разрешения приема числа соответствующего накапли«0

.-15

10 .

сигнал, поступая через вход коммутатора 3 тестовых воздействий и элемент ИЛИ 39 на вход разрешения приема информации счетчика 37, переписывает в счетчик 37 число входных величин с регистра 38. Последовательная работа коммутатора 3 тестовых воздействий и коммутатора 4 выходных величин повторяется до тех пор, пока на счетчике 54 числа реализаций прог- раммьт не установится нулевой код, который приводит к появлению на выходе элемента ИЛИ-НЕ 53 единичного сигнала, соответствующего окончанию работы устройства. Этот сигнал, проходя через выход коммутатора 4 выходных величин, вход блока 1, элементы И 23 и ИЛИ 26 на вход установки в нуль первого триггера 29, устанавливает

Бающего сумматора 70. На информацион- О его в единичное состояние, а блок 1 в

ные входы сумматоров 70 в это время поступает значение выходной переменной с регистра числа ОП СЦВМ через вход 15 устройства, первый вход блока 8 статистических анализаторов и делитель 1/К 69. Тем самым к значению соответствующего накапливающего сумматора 70 прибавляется очередное слагаемое Z/K, где Z - значение соответствующей выходной перемен ной после очередного прогона программы.

Следующий импульс Г4, проходя через элемент И 52 на вычитающий вход счетчика 58, уменьшает его значение на единицу, что соответствует переходу к выборке значения следующей выходной переменной, и цикл работы коммут-атора 4 выходных величин повторяется .

Коммутатор 4 выходных величин работает до тех пор, пока значение счетчика 58 не станет равным нулю. Соответствующий этому единичный сиг- нал с нулевого выхода дешифратора 57 через группу 55 элементов И, поступая на вычитающий вход счетчика 54 числа прогонов программы, уменьшает его значение на единицу. Одновременно этот сигнал через второй выход коммутатора 4 выходных величин поступает через вход блока 1 и элемент ИПИ 27 на вход установки в нуль триггера 30, переводя блок 1 в состоя- ние 10, соответствующее окончанию работы коммутатора 4 выходных величин и началу работы коммутатора 3 тестовых воздействий. Кроме того, этот же

«0

15

10 .

сигнал, поступая через вход коммутатора 3 тестовых воздействий и элемент ИЛИ 39 на вход разрешения приема информации счетчика 37, переписывает в счетчик 37 число входных величин с регистра 38. Последовательная работа коммутатора 3 тестовых воздействий и коммутатора 4 выходных величин повторяется до тех пор, пока на счетчике 54 числа реализаций прог- раммьт не установится нулевой код, который приводит к появлению на выходе элемента ИЛИ-НЕ 53 единичного сигнала, соответствующего окончанию работы устройства. Этот сигнал, проходя через выход коммутатора 4 выходных величин, вход блока 1, элементы И 23 и ИЛИ 26 на вход установки в нуль первого триггера 29, устанавливает

5

45 5

35

40

50

исходное состояние 01. Этот же сигнал поступает на второй выход 17 устройства, сигнсшизируя об окончании испытаний программы..

Результаты испытаний (математическое ожидание значений выходных переменных программы) с выходов накапливающих сумматоров 70 выдаются на выход 22 устройства. По степени соответствия этих результатов расчетным судят о наличии или отсутствии ошибок в программе с заданной достоверностью.

Формула изобретения

1. Устройство дпя контроля вычислительных программ, содержащее блок задания режима, генератор случайных чисел, блок статистических анализаторов, отличающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения статистического контроля программ, в устройство введены распределитель . импульсов, коммутатор тестовых воз- Iдействий, коммутатор выходных величин, блок регистров адресов входных величин, блок регистров адресов выходных величин, группа элементов ИЛИ, элемент ИЛИ, причем распределитель импульсов содержит первый, второй, третий и четвертый элементы И, счетчик импульсов, первую и вторую группы элементов И и дешифратор, тактовый вход устройства соединен с тактовым входом коммутатора выходных величин и с первыми входами элементов

и первой группы распределителя импульсов, с первыми входами первого, второго и третьего элементов И распределителя импульсов, коммутатора тестовых воздействий и.блока задани режима, выход которого соединен с входом.начальной установки счетчика распределителя импульсов и входом начальной установки блока статистических анализаторов, входы запуска устройства и останова контролируемой программы устройства соединены сот- ветственно с входами пуска и начала контроля блока задания режима, первый информационный вход устройства соединен с информационным входом регистра распределителя импульсов, выход состояния режима блока задания режима соединен соответственно с вторым и третьим входами элементов И первой группы распределителя импульсов, с вторыми и третьими входами первого, второго и третьего элементов И распределителя импульсов, выходы первого, второго и третьего элементов И распределителя импульсов соединены соответственно с первым входом элемента ИЛИ, с первыми -входами элементов И второй группы распределителя импульсов, со счетным входом счетчика импульсов распределителя импульсов, выходы счетчика импульсов, разрядные выходы регистра соединены с четвертыми входами соответствующих элементов И первой группы распределителя импульсов, выходы счетчика импульсов соединены с входами дешифратора, выходы которого соединены с вторыми входами соответствующих элементов И второй группы распределителя импульсов, выходы элементов И первой группы распределителя импульсов соединены с первыми входами элементов ИЛИ группы, выходы которых образуют группу адресных выходов устройства, выходы элементов И второй группы распределителя импульсов соединены с входом установки режима блока задания режима, с входом записи генератора случайных чисел, первым управляющим входом коммутатора тестовых воздействий и с управляющими входами коммутатора выходных величин, с входами записи блоков, регистров адресов входных и выходных величин и с входом записи блока статистических анализаторов,выход начала анализа результатов контролируемой программы блока задания режи7885612

ма соединен с вторы;ч управляющим входом ко 1мутатора выходных величин, выход состояния режима блока задания режима соединен с третьим управляю- с щим входом коммутатора выходных величин, второй информационный вход устройства соединен с информационными входами блока статистических анализаторов, блока регистров адресов вы- 10 ходных величин, информационный вход коммутатора выходных величин - с информационным входом коммутатора тестовых воздействий, блока регистров адресов входных величин и генератора /5 случайных чисел, первый выход коммутатора выходных величин соединен с входом изменения режима блока задания режима и является выходом окончания контроля устройства, второй вы- 0 ход коммутатора выходных величин соединен с вторь М входом элемента ИЛИ, выход которого является выходом чтения устройства, выходы блока регистров адресов входных величин и блока 5 регистров адресов выходных величин соединены соответственно с вторыми и третьими входами элементов ИЛИ группы, выходы которых образуют группу адресных выходов устройства, третий 0 выход коммутатора выходных величин соединен с входом считывания блока регистров адресов выходных величин, четвертый выход коммутатора выходных величин соединен с входом приема бло- 5 ка статистических анализаторов, с входом останова блока задания режима, и-вторым управляющим входом коммутатора тестовых воздействий, первый выход коммутатора тестовых воздейст- 0 ВИЙ соединен с- тактовым входом генератора случайных чисел и является выходом записи устройства, второй выход коммутатора тестовых воздействий является выходом запуска контролиру- 5 емой программы, третий выход коммутатора тестовых воздействий соединен с входом разрешения выдачи адреса блока регистров адресов входных величин и с входом синхронизации гене- 0 ратора случайных- чисел, выход которого является информационным выходом устройства, выход блока статистических анализаторов является выходом результата контроля программы устрой- 5 ства.

2. Устройство по п.1, о т л и - чающе е ся тем, что блок задания режима содержит три элемента И,

13

три элемента Ш1И н дна триггера, причем тактовый вход блока соединен с первь№т входами первого, второго и третьего элементов И, вход остапова блока соединен с вторым входом первого элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, вход nycKai блока соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемета ИЛИ, с первым входом третьего элемента ИЛИ и является тактовым выходом блока, вход начала контроля зявляемого устройства соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом второго элемента 1-ШИ и является выходом начала анализа результата контролируемой программы блокаj вхо установки задания режима блока соединен с единичным входом первого триггера, инверсньм и прямой выходы которого соединены с третьими входами соответственно второго и третьег элементов И, вход изменения режима блока соединен с вторым входом третего элемента ИЛИ, выход которого содинен с нулевым входом второго триггера, прямой и инверсный выходы которого соединены с четвертыми входам соответственно второго и третьего элементов И, выходы первого и второго элементов РШИ соединены соответсвенно с нулевым входом первого триг гера и единичным значением второго триггера, прямые и инверсные выходы первого триггера являются выходами состояния режима блока.

3. Устройство по П.1, о т л и

чающееся тем, что коммутатор тестовых воздействий содержит четыре элемента И, элемент НЕ, элемент ИЛИ, регистр, счетчик и дешифратор, причем информационный вход блока соединен с информационным входом регистра которого соединен с информационным входом счетчика, первьш и второй управляющие входы блока соеди нены с первыми и вторыми входами соответственно первого, второго и третьего элементов И, первый и второй тактовые входы блока соединены с третьими входами соответственно второго и третьего элементов И, выход счетчика соединен с входами дешифратора, выход которого соединен, с первым входом четвертого элемента

J5

8856

35

0

25

30

40

45

д

55

14

И и через элемент НЕ с четвертыми входами второго и третьего элементов И, выход третьего элемента И соединен с счетным входом счетчика и является первым выходом блока, выход, второго элемента И соединен с вторым входом четвертого элемента И, выход которого соединен с третьим входом первого элемента И, выход которого является вторым выходом блока, выход четвертого элемента И является третьим выходом блока, первый управляющий вход блока соединен с первым входом эл.емента ИЛИ, выход которого соединен с входом записи счетчика, второй управляющий вход блока соединен, с вторым входом элемента ИЛИ.

4., Устройство по п.4, о т л и - чающееся тем, что блок статистических: анализаторов содержит регистр , группу делителей и группу накапливающих сумматоров, причем ин- формационньм вход блока соединен с первым информационным входом делителя и регистра, выход которого соединен с вторым информационным входом делителя, вход записи блока соединен с входом записи регистра, вход начальной установки блока и вход приема блока соединены соответственно с входом пуска каждого накапливающего сумматора группы и с входом начальной установки каждого накапливающего сумматора группы, выход каждого делителя группы соединен с информационным входом соответствующего накапливающего сумматора группы, выходы всех накапливающих сумматоров группы образуют группу выходов блока.

5. Устройство по П.1, о т л и - чающееся тем, что коммутатор выходных величин содержит четыре элемента И, две группы элементов И, элемент ИЛИ-НЕ, регистр, счетчик числа выходных переменных, счетчик числа реализаций программы и дешифратор, причем первый и второй управляющие входы блока соединены соответственно с первыми и вторыьш входами первого, второго, третьего и четвертого элементов И, первый., второй, третий и четвертьй тактовые входы блока соединены с третьими входами соответст- венно третьего, первого, второго и четвертого элементов И, информацион- ньш вход блока соединен с информационными входами регистра и счетчика числа реализаций программы, выходы

151

регистра и четвертого элемента И соединены соответственно с информационным и счетным входами счетчика числа выходных переменных, выход которого соединен с входами дешифратора, выходы которого соединены с первыми входами элементов И первой и второй групп, выходы второго и третьего элементов И соединены с вторыми входами элементов И соответственно первой и второй групп, выходы элементов И первой группь соединены с счетньш

7885616

входом числа реализации программы и является выходом начала анализа блока, выходы счетчика числа реализаций программы соединены с входами элемента ИЛИ-НЕ, выход которого является выходом конца проверки блока, выход первого элемента И является тактовым выходом блока, выходы элементов И второй группы являются выходами чтения блока,вход записи блока соединен с входоми записи регистра и счетчика числа реализаций программы.

.5

0

ipttz.l

бл2,5Л

ФигЛ

Фиг. 5

Puz.S

Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Устройство для отладки программ | 1982 |

|

SU1083194A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Устройство для отладки программ | 1985 |

|

SU1280636A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

Предлагается устройство для тестирования вычислительных программ, относящееся к области вычислительной техники и содержащее блок управле- (Л1Я, генератор случайных чисел, блок статистических анализаторов. С целью расширения класса решаемых задач путем обеспечения возможности статистического контроля вычислительных программ в устройство введены распределитель, коммутатор тестовых воздействий, коммутатор выходных величин, блок регистров адресов входных величин, блок регистров адресов выходных величин, элемент ИЛИ, группа элементов ИЛИ. Устройство позволяет реализовать метод вероятностного тестирования программ и может быть использовано в устройствах управления специализированных цифровых вычислительных машин при отладке про- «g грамм, реализующих вычисление сложных математических функций. 4 з.п. ф-лы, 12 ил. (Л С ts9 00 00 СП О5

Фиг,. 8

Фиг.9

Конец испытаний Ф(Аг.10

Бл.г БлЯ

Фиг.11

Структура страницы ОП

Фиг. 12

| Устройство для отладки программ | 1977 |

|

SU630630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское, свидетельство СССР № 527707, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-07-02—Подача