113

Изобретение относится к технике телефонной связи и предназначено для использования в автоматических междугородних телефонных стани 1ях для приема и передачи многочастотньк сигналов в коде 2 и 6.

Цель изобретения - повышение помехоустойчивости путем уменьшения уровня шумов коммутации,

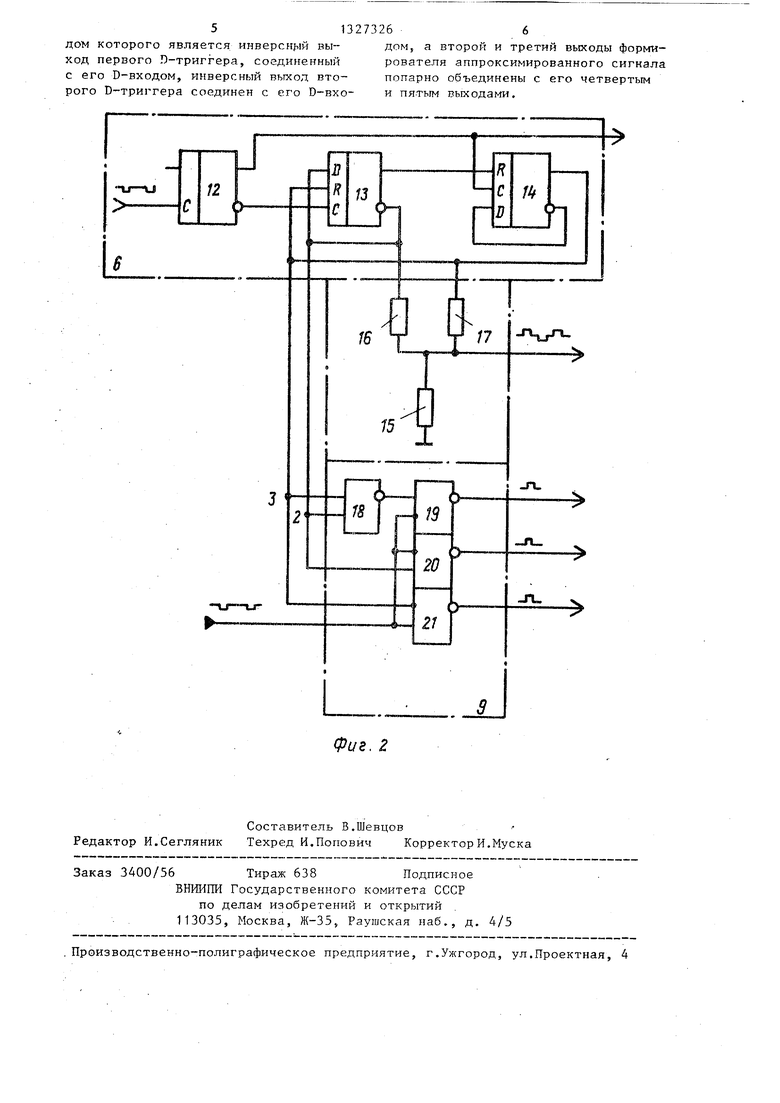

На фиг. 1 приведена структурная схема приемопередатчика многочастотных сигналов; на фиг. 2 - принципиальные электрические схемы формирователя аппроксимированного сигнала, сумматора и формирователя импульсов коммутации.

Приемопередатчик многочастотных сигналов содержит счетчик 1 состояния, блок 2 управления коэффициентом деления, делитель 3 частоты с пере- менньм коэффициентом деления, сумматор 4, первый ключ 5, формирователь 6 аппроксимированного сигнала, дешифратор 7s второй ключ 8, формирователь 9 импульсов коммутации, синхронный фильтр 10 и амплитудный детектор 11. Формирователь аппроксимированного сигнала содержит счетный триггер 12, и первый и второй D-триг- гер 13 и 14, Сумматор состоит из первого, второго и третьего резисторов 15 - 17о Формирователь импульсов коммутации содержит элемент И-НЕ 18, первый, второй и третий элементы ИЛИ- НЕ 19 - 21.

.Приемодатчик многочастотных сигналов работает следующим образом.

В режиме ожидания происходит следующее о

В исходном состоянии на делитель 3 поступает внешняя тактовая частота, которая делится на соответствующий коэффициент деления, который устанавливается счетчиком 1 через блок 2. Счетчик 1 находится в одном из допустимых состояний, каждое из которых соответствует принимаемой частоте. Частота, полученная в результате деления делителем 3, поступает на формирователь 6. Счетньй триггер 12 формирователя 6 формирует из пришедшей частоты сигнал формы меандр,, Это необходимо для того, чтобы разделить период принимаемого и формируемого сигналов на равные части. Первый и второй D-триггеры 13 и 14 формируют непосредственно аппроксимированньш сигнал следующим образом. Второй

73262

D-триггер 14 срабатывает от прямого плеча счетного триггера 12 и запрещает работу перрого D-триггера 14 на время своей работы. С приходом следующего переднего фронта от прямого плеча счетного триггера 12 он сбрасывается и разрешает работу первого. D-триггера 13, который срабатывает

0 через полпериода от инверсного плеча счетного триггера 12, блокируя, в свою очередь, второй D-триггер 14 на время своей работы. С приходом следующего переднего фронта от инверсно15 го плеча счетного триггера 12 первый D-триггер 13 сбрасывается. В дальней- тем описанный процесс повторяется. Сигналы с инверсного и прямого плеча первого и второго D-триггеров 13 и 14

0 поступают на сумматор 4, состоящий из первого, второго и третьего резисторов 15 17. Если сработал второй D-триггер 14, то на выходе сумматора 4 будет следующий потенциал, рав25 ный-2/3 входного потенциала.

Если первый и второй D-триггера 13 и 14 не включены, то входное напряжение будет равно 1/3 входного потен- ииала.

30 Если первый D-триггера 13 сработал, то выходное напряжение равно нулю.

Таким образом, получили трехуровневый сигнал. Период формируемого

35 сигнала разбит на шесть равных частей. Вьгбор количества участков разбиения (шесть участков) выходного сигнала за од71н период при заданных нелинейных искажениях (Кг 10% по

40 требованиям МККТ, где Кг - коэффициент гармоник) определялся с помощью разложения функции в ряде Фурье. Для управления синхронным фильтром 10 служит формирователь 9, который де45 лит период принимаемого сигнала на три равные части при помощи элемента И-НЕ 18 и первого, второго и третьего элементов ИЛИ-НЕ 19 - 21. Для того, чтобы уменьшить шумь коммута50 ции в синхронном фильтре 10, конденсаторы, входящие в его состав, подключаются не полностью на одну треть, а на б.олее короткое время. В остальное время дешифратор 7 блокирует фор55 мирователь 9 и открывает второй ключ 8, которьш шунтирует выход синхронного фильтра 10 для того, чтобы в это время принимаемый сигнал не проходил через синхронный фильтр 10 на

313273264

амплитудный детектор 11. В результа-тель импульсов ко№-1утацнн, первый, те того, что время заряда конденсато-второй и третий выходы которого под- ров в синхронном фильтре 10 мало, тоключены к соответствующим первому, в следующем подключении его перезарядвторому и третьему входам синхрон- будет минимальным, т.е. шумы коммута-ного фильтра, выход которого подклю- ции будут меньше. Уменьшение временичен к входу амплитудного детектора, заряда конденсаторов приводит к повы-отличающийся тем, что, шению добротности синхронного фильт-с целью повьтшения помехоустойчивости ра 10. Qлутем уменьшения уровня шумов комму- Описанный процесс повторяется цик-тации, введены последовательно соедилически.

В режиме приема происходит следующее . При поступлении на вход приемопередатчика многочастотных сигналов синусоидального сигнала и при совпадении частоты коммутации синхронного фильтра 10 с частотой .этого сигнала он пропускает этот сигна,т1 на вход амплитудного детектора 11. Если уровень принимаемого сигнала больше опорного сигнала амплитудного детектора 11, то последний срабатывает и фиксирует счетчик 1, а также подает сигнал внешнему устройству, что принята частота, код которой зафиксирован на выходах счетчика 1. Внешнее устройство может сосчитать код для дальнейшей его обработки. Как только на входе пропадет или сменится частота, амплитудный детектор 11 сбросится и разрешит работу счетчику 1. Процесс приема следующей частоты повторится.

I . .

В режиме передачи происходит следующее. При приходе сигналов управления на первый ключ 5 и кода на счетчик 1.0Т внешнего устройства передатчик многочастотных сигналов переходит в режим передачи. Делитель 3 будет формировать только одну частоту, код которой выставлен на счетчик 1, который не воспринимает сигналы от делителя 3 и амплитудного детектора 11, так как на его установочных входах стоит код. Синусоидальный сигнал с сумматора 4 через первый ключ 5 проходит на выход приемопередатчика многочастотных сигналов. Формирование следзтощей частоты происходит аналогично.

Формула изобретения

1. Приемопередатчик многочастотных сигналов, содержащий последовательно соединенные счетчик состояния, блок управления коэффициентом деления и делитель частоты с переменным коэффициентом деления, а также формирова

ненные сумматор и первый ключ, а также последовательно соединенные формирователь аппроксимированного сигнала, дешифратор и второй ключ, выход которого соединен с нулевым проводом, информационный вход второго ключа подключен к выходу синхронного фильтра, управляющий вход которого подключен к выходу первого ключа, выход амплитудного детектора подключен к разрешающему входу счетчика состояния, информационный вход которого соединен с первым выходом делителя частоты с переменным коэффициентом деления, второй выход которого соединен с входом формирователя аппроксимированного сигнала, второй и третий выходы которого подключены соответственно к первому и второму входам формирователя импульсов коммутации, третий вход которого соединен с выходом дешифратора, второй и третий входы которого подключены соответственно к третьему и четвертому выходам делителя частоты с переменным коэффициен- том деления, а четвертый и пятыйвыходы формирователя аппроксмированногосигнала подключенысоответственно к первому и второму входам сумматора.

2. Приемопередатчик по п. 1, отличающийся тем, что формирователь аппроксимированного сигнала содержит счетный триггер . и последовательно соединенные первьш и второй D-триггеры, причем выход счетного триггера соединен со счетным входом второго D-триггера и является первым выходом формирователя аппроксимированного сигнала, входом которого является вход счетного триггера, инверсный выход которого подключен к счетному входу первого D-триггера, выход которого подключен к установоч- ному входу второго D-триггера, выход которого соединен с установочным входом первого D-триггера и является вторым выходом формирователя аппроксимированного сигнала, третьим выхо

513273266

дом которого является инверсн й вы- дом, а второй и третий выходы форми- ход первого D-триггера, соединенный рователя аппроксимированного сигнала с его D-входом, инверсный выход вто- попарно объединены с его четвертым рого D-триггера соединен с его D-BXO- и пятым выходами.

Фи. Z

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| Устройство для приема многочастотных сигналов | 1980 |

|

SU1070708A1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246801C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2316142C1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| Цифровой термометр | 1984 |

|

SU1278625A1 |

Изобретение относится к теле- ;фонной связи. Цель изобретения - повышение помехоустойчивости путем уменьшения уровня шумов коммутации. Приемопередатчик содержит счетчик 1 состояния, блок управления 2 коэффициентом деления, делитель 3 частоты с переменным коэффициентом деления, сумматор 4, ключи 5 и 8, формирователь (Ф) 6 аппроксимированного сигнала, дешифратор 7, Ф 9 импульсов коммутации, синхронный фильтр (СФ) 10 и амплитудный детектор 11. Приемопередатчик работает в трех режимах: ожидание, прием и передача. Для уменьшения шумов коммутации, образуемых в СФ 10 в режиме ожидания, конденсаторы, входящие в состав СФ 10, подключаются не полностью на одну треть периода принимаемого сигнала, а на более короткое время. В остальное время дешифратор 7 блокирует Ф 9 и открывает ключ 8, который шунтирует выход СФ 10 для того, чтобы в это время принимаемый сигнал не проходил через СФ 10 на амплитудный детектор 11. Цель достигаетс я введением сумматора 4, ключей 5 и 8, Ф 6 и дешифратора 7. Приемопередатчик по п. 2 ф-лы отличается вьтолнением Ф 6, 1 3.п. ф-лы, 2 ил. . (Л Фиг.1 Т linpaSneHue

| Заявка ФРГ № 1951678, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-30—Публикация

1986-01-03—Подача