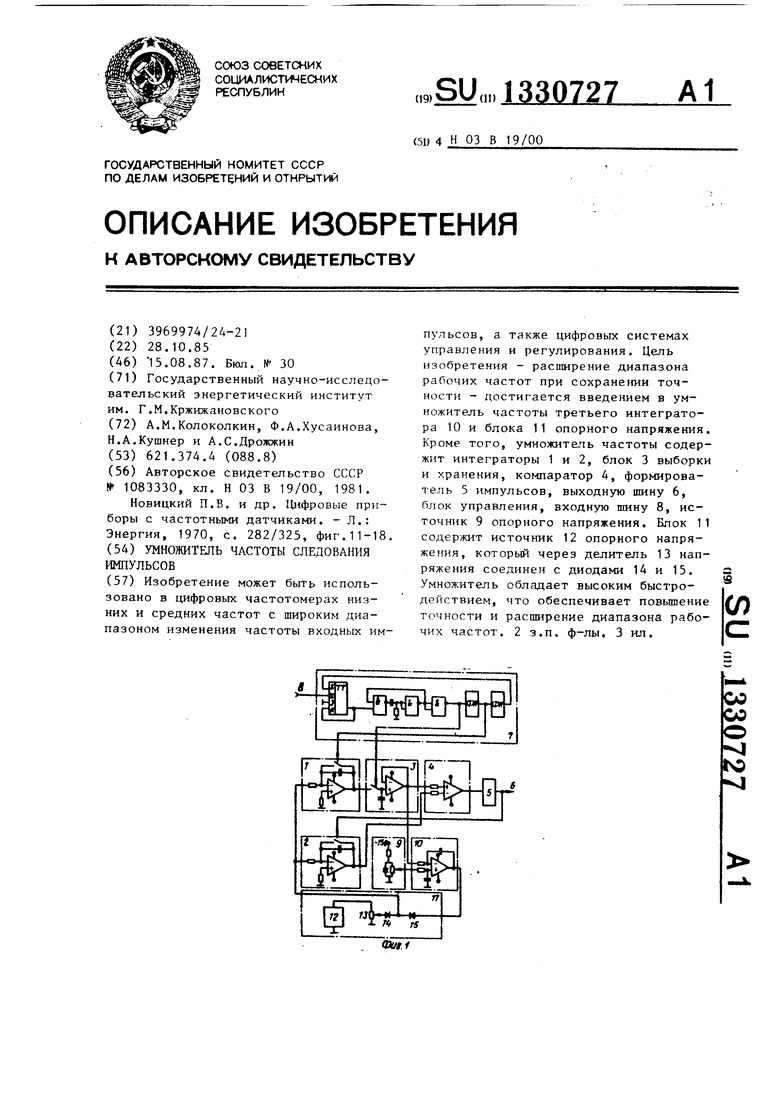

Изобретение относится к импульсной технике, в частности к умножителям частоты импульсов, и может быть использовано в цифровых частотомерах низких и средних частот с широким диапазоном изменения частоты входных импульсов, а такде цифровых системах управления и регулирования.

Цель изобретения - расширение диа- ю выходе блока 7 управления; - наппазона рабочих частот при сохранении точности.

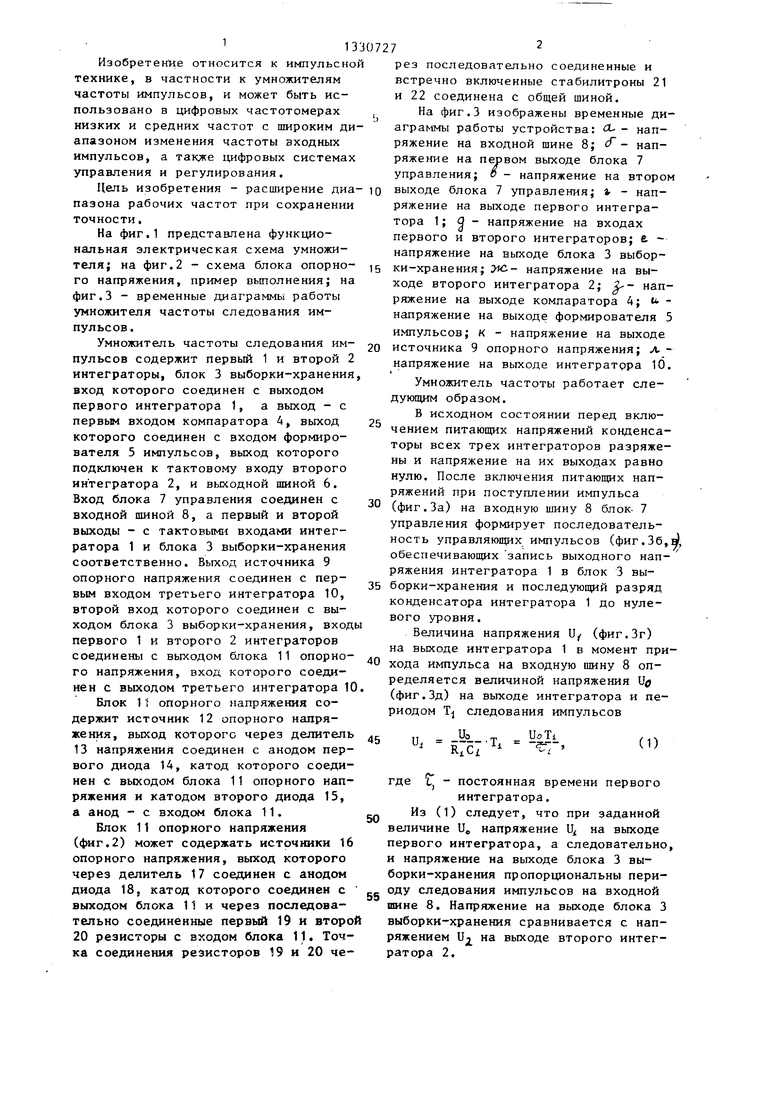

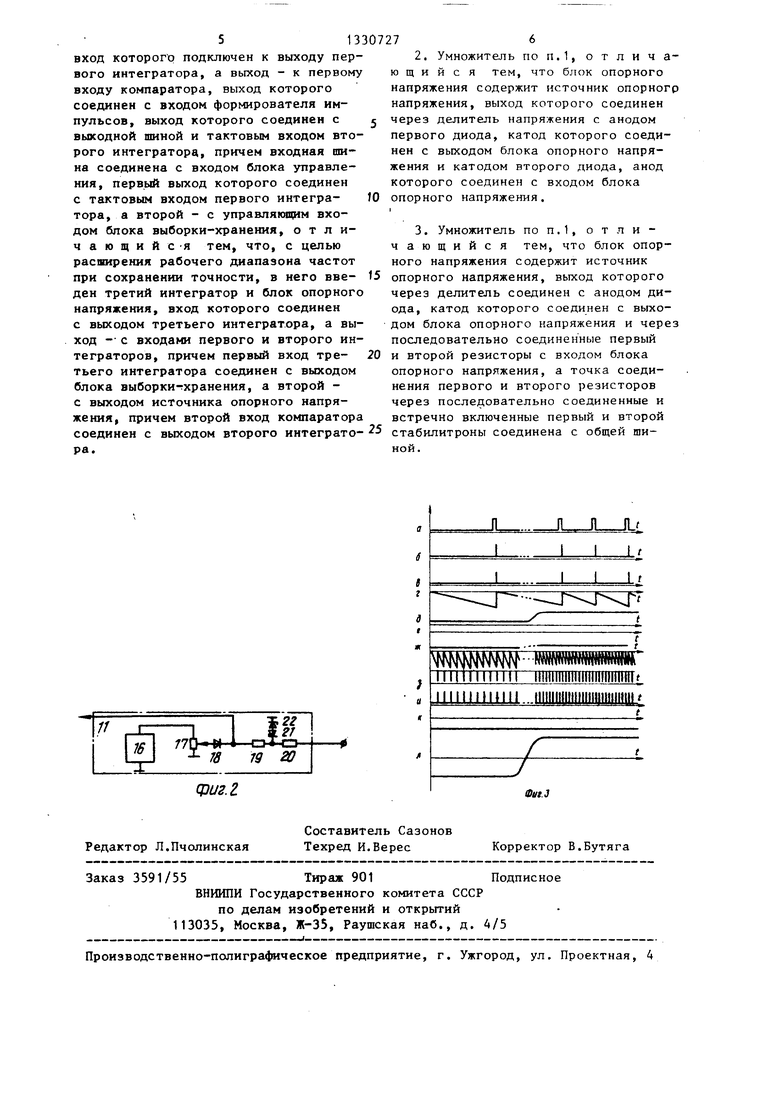

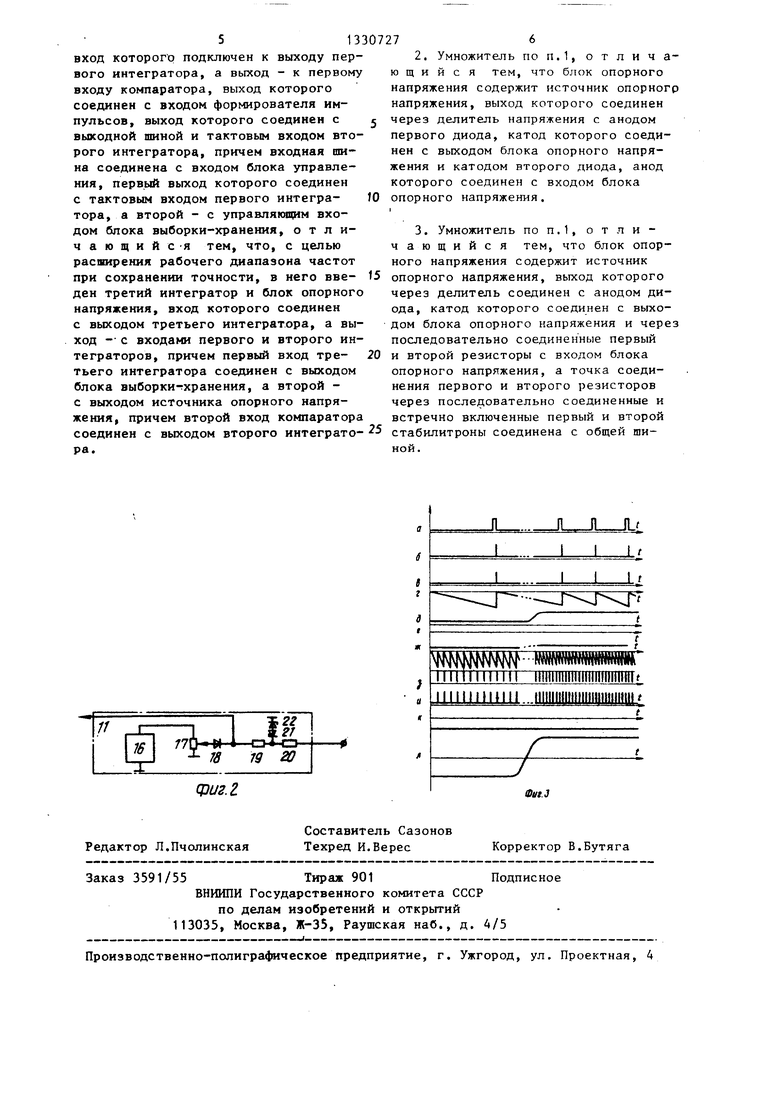

На фиг.1 представлена функциональная электрическая схема умножителя; на фиг.2 - схема блока опорного напряжения, пример выполнения; на фиг.3 - временные диаграммы работы умножителя частоты следования импульсов.

Умножитель частоты следования импульсов содержит первый 1 и второй 2 интеграторы, блок 3 выборки-хранения, вход которого соединен с выходом первого интегратора 1, а выход - с первым входом компаратора 4, выход которого соединен с входом формирователя 5 импульсов, выход которого подключен к тактовому входу второго интегратора 2, и выходной шиной 6. Вход блока 7 управления соединен с входной шиной 8, а первый и второй выходы - с тактовыми входами интегратора 1 и блока 3 выборки-хранения соответственно. Выход источника 9 опорного напряжения соединен с первым входом третьего интегратора 10, второй вход которого соединен с выходом блока 3 выборки-хранения, входы первого 1 и второго 2 интеграторов соединены с выходом блока 11 опорного напряжения, вход которого соединен с выходом третьего интегратора 10.

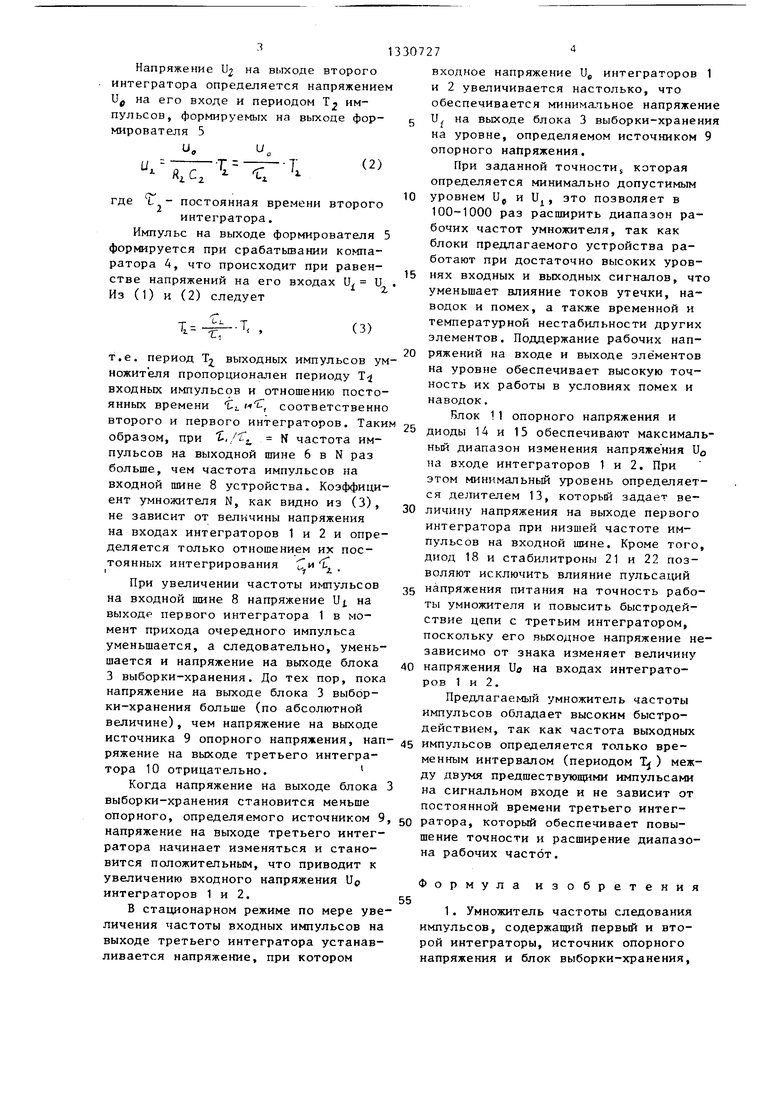

Блок 11 опорного напряжения содержит источник 12 опорного напряжения, выход которого через делитель 13 напряжения соединен с анодом первого диода 14, катод которого соединен с выходом блока 11 опорного напряжения и катодом второго диода 15, а анод - с входом блока 11.

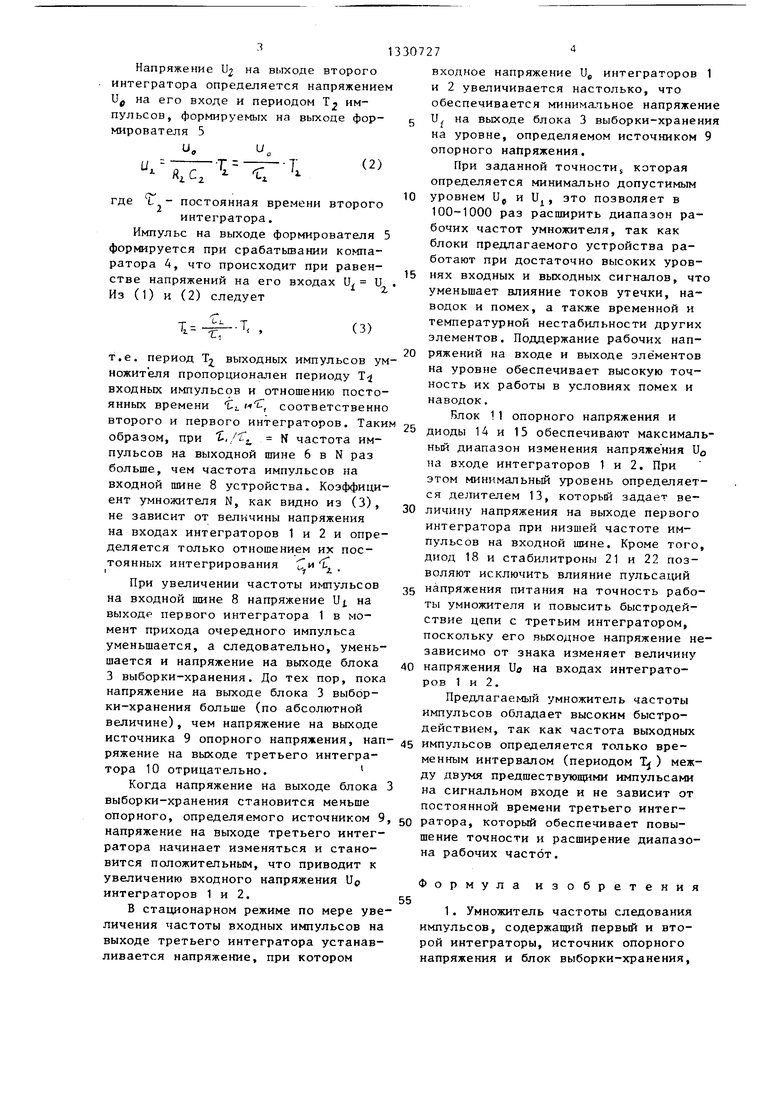

Блок 11 опорного напряжения (фиг.2) может содержать источники 16 опорного напряжения, выход которого через делитель 17 соединен с анодом диода 18, катод которого соединен с выходом блока 11 и через последовательно соединенные первый 19 и второй 20 резисторы с входом блока 11. Точка соединения резисторов 19 и 20 че20

25

ряжение на выходе первого интегратора 1; Q - напряжение на входах первого и второго интеграторов; е. - напряжение на выходе блока 3 выбор- 15 ки-хранения; ,- напряжение на выходе второго интегратора 2; i-- напряжение на выходе компаратора 4; к- - напряжение на выходе формирователя 5 импульсов; к - напряжение на выходе источника 9 опорного напряжения; л - напряжение на выходе интегратора 10.

Умножитель частоты работает следующим образом.

В исходном состоянии перед включением питающих напряжений конденсаторы всех трех интеграторов разряжены и напряжение на их выходах равно нулю. После включения питающих напряжений при поступлении импульса (фиг. За) на входную шину 8 блок- 7 управления формирует последовательность управляющих импульсов (фиг.Зб, обеспечивающих запись выходного напряжения интегратора 1 в блок 3 вы35 борки-хранения и последующий разряд конденсатора интегратора 1 до нулевого уровня.

Величина напряжения U (фиг.Зг) на выходе интегратора 1 в момент при

хода импульса на входную шину 8 определяется величиной напряжения U( (фиг.Зд) на выходе интегратора и периодом Т следования импульсов

30

45

и.

Ц°..т R.Ci

UoTi

(1)

50

55

где t, постоянная времени первого

интегратора.

Из (1) следует, что при заданной величине U напряжение U на выходе первого интегратора, а следовательно и напряжение на выходе блока 3 выборки-хранения пропорциональны периоду следования импульсов на входной шине 8. Напряжение на выходе блока 3 выборки-хранения сравнивается с напряжением U2 на выходе второго интегратора 2.

рез последовательно соединенные и встречно включенные стабилитроны 21 и 22 соединена с общей шиной.

На фиг.3 изображены временные диаграммы работы устройства: Л-- напряжение на входной шине 8; - напряжение на первом выходе блока 7

f управления; о - напряжение на втором

ряжение на выходе первого интегратора 1; Q - напряжение на входах первого и второго интеграторов; е. - напряжение на выходе блока 3 выбор- ки-хранения; ,- напряжение на выходе второго интегратора 2; i-- напряжение на выходе компаратора 4; к- - напряжение на выходе формирователя 5 импульсов; к - напряжение на выходе источника 9 опорного напряжения; л - напряжение на выходе интегратора 10.

Умножитель частоты работает следующим образом.

В исходном состоянии перед включением питающих напряжений конденсаторы всех трех интеграторов разряжены и напряжение на их выходах равно нулю. После включения питающих напряжений при поступлении импульса (фиг. За) на входную шину 8 блок- 7 управления формирует последовательность управляющих импульсов (фиг.Зб,, обеспечивающих запись выходного напряжения интегратора 1 в блок 3 выборки-хранения и последующий разряд конденсатора интегратора 1 до нулевого уровня.

Величина напряжения U (фиг.Зг) на выходе интегратора 1 в момент прихода импульса на входную шину 8 определяется величиной напряжения U( (фиг.Зд) на выходе интегратора и периодом Т следования импульсов

и.

Ц°..т R.Ci

UoTi

(1)

50

55

где t, постоянная времени первого

интегратора.

Из (1) следует, что при заданной величине U напряжение U на выходе первого интегратора, а следовательно, и напряжение на выходе блока 3 выборки-хранения пропорциональны периоду следования импульсов на входной шине 8. Напряжение на выходе блока 3 выборки-хранения сравнивается с напряжением U2 на выходе второго интегратора 2.

Напряжение U на выходе второго интегратора определяется напряжением и на его входе и периодом Т импульсов, формируемых на выходе формирователя 5

и, и„

Т, (2)

и.

Я, С,

1-

г

где L - постоянная времени второго

интегратора.

Импульс на выходе формирователя 5 формируется при срабатьшании компаратора 4, что происходит при равенстве напряжений на его входах U U , Из (1) и (2) следует

IГ.

-Т,

пульсов на выходной шине 6 в N раз больше, чем частота импульсов на входной шине 8 устройства. Коэффициент умножителя N, как видно из (3), не зависит от величины напряжения на входах интеграторов 1 и 2 и определяется только отношением их постоянных интегрирования Си t .

При увеличении частоты импульсов на входной шине 8 напряжение Uj. на выходе первого интегратора 1 в момент прихода очередного импульса уменьшается, а следовательно, уменьшается и напряжение на выходе блока 3 выборки-хранения. До тех пор, пока напряжение на выходе блока 3 выборки-хранения больше (по абсолютной величине), чем напряжение на выходе

20 ряжений на входе и выходе элементов на уровне обеспечивает высокую точность их работы в условиях помех и наводок,

Блок 11 опорного напряжения и

т.е. период Т выходных импульсов умножителя пропорционален периоду Т входных импульсов и отношению постоянных времени Cz. S соответственно

второго и первого интеграторов. Таким OR i / , L - « , диоды 14 и 15 обеспечивают максимальобразом, при i,,L, - N частота им- -. ..

ныи диапазон изменения напряжения Uo

на входе интеграторов 1 и 2. При этом минимальньш уровень определяется делителем 13, который задает ве- 30 личину напряжения на выходе первого интегратора при низшей частоте импульсов на входной шине. Кроме того, диод 18 и стабилитроны 21 и 22 позволяют исключить влияние пульса1р1й 35 напряжения питания на точность работы умножителя и повысить быстродействие цепи с третьим интегратором, поскольку его выходное напряжение независимо от знака изменяет величину 40 напряжения Ue на входах интеграторов 1 и 2.

Предлагаемый умножитель частоты импульсов обладает высоким быстродействием, так как частота выходных источника 9 опорного напряжения, нап- 45 импульсов определяется только вре- ряжение на выходе третьего интегра- менным интервалом (периодом Xj) межтора 10 отрицательно. ду двумя предшествующими импульсами Когда напряжение на выходе блока 3 на сигнальном входе и не зависит от выборки-хранения становится меньше постоянной времени третьего интег- опорного, определяемого источником 9, 50 ратора, который обеспечивает повы- напряжение на выходе третьего интег- шение точности и расширение диапазо- ратора начинает изменяться и становится положительным, что приводит к увеличению входного напряжения Up интеграторов 1 и 2.55

В стационарном режиме по мере увеличения частоты входных импульсов на выходе третьего интегратора устанавливается напряжение, при котором

на рабочих частот.

Формула изобретения

1. Умножитель частоты следования импульсов, содержащий первый и второй интеграторы, источник опорного напряжения и блок выборки-хранения.

,

входное напряжение U, интеграторов 1 и 2 увеличивается настолько, что обеспечивается минимальное напряжение

g Uv на выходе блока 3 выборки-хранения на уровне, определяемом источником 9 опорного напряжения.

При заданной точности которая определяется минимально допустимым

10 уровнем Up и и, зто позволяет в

100-1000 раз расширить диапазон рабочих частот умножителя, так как блоки предлагаемого устройства работают при достаточно высоких уров15 нях входных и выходных сигналов, что уменьшает влияние токов утечки, наводок и помех, а также временной и температурной нестабильности других элементов. Поддержание рабочих нап20 ряжений на входе и выходе элементов на уровне обеспечивает высокую точность их работы в условиях помех и наводок,

Блок 11 опорного напряжения и

OR i / , L - «Предлагаемый умножитель частоты импульсов обладает высоким быстродействием, так как частота выходных импульсов определяется только вре- менным интервалом (периодом Xj) между двумя предшествующими импульсами на сигнальном входе и не зависит от постоянной времени третьего интег- ратора, который обеспечивает повы- шение точности и расширение диапазо-

на рабочих частот.

Формула изобретения

1. Умножитель частоты следования импульсов, содержащий первый и второй интеграторы, источник опорного напряжения и блок выборки-хранения.

вход которого подключен к выходу первого интегратора, а выход - к пepвo fy входу компаратора, выход которого соединен с входом формирователя импульсов, выход которого соединен с выходной шиной и тактовым входом второго интегратора, причем входная шина соединена с входом блока управления, первый выход которого соединен с тактовым входом первого интегра- тора, а второй - с управляющим входом блока выборки-хранения, о т л и- ч а ю щ и и с Я тем, что, с целью расширения рабочего диапазона частот при сохранении точности, в него введен третий интегратор и блок опорного напряжения, вход которого соединен с выходом третьего интегратора, а выход -с входами первого и второго интеграторов, причем первый вход тре- тьего интегратора соединен с выходом блока выборки-гхранения, а второй - с выходом источника опорного напряжения, причем второй вход компаратора соединен с выходом второго интеграто ра.

.1020

15

25

2,Умножитель по п.1, отличающийся тем, что блок опорного напряжения содержит источник опорногр напряжения, выход которого соединен через делитель напряжения с анодом первого диода, катод которого соединен с выходом блока опорного напряжения и катодом второго диода, анод которого соединен с входом блока опорного напряжения.

3.Умножитель по п.1, отличающийся тем, что блок опорного напряжения содержит источник опорного напряжения, выход которого через делитель соединен с анодом диода, катод которого соединен с выходом блока опорного напряжения и через последовательно соединенные первый

и второй резисторы с входом блока опорного напряжения, а точка соединения первого и второго резисторов через последовательно соединенные и встречно включенные первый и второй стабилитроны соединена с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкополосный умножитель частоты импульсов | 1988 |

|

SU1564709A1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1802395A1 |

| Преобразователь среднего значения напряжения | 1982 |

|

SU1114964A1 |

| Устройство для компенсации реактивной мощности нагрузки и симметрирования трехфазной сети | 1985 |

|

SU1261044A1 |

| Преобразователь напряжения в частоту | 1982 |

|

SU1022308A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2014 |

|

RU2554571C1 |

| ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 2000 |

|

RU2171011C1 |

| Электрометрический вольтметр | 1986 |

|

SU1413538A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР КВАДРАТУРНЫХ СИГНАЛОВ | 2014 |

|

RU2565362C1 |

| Частотно-фазовый детектор | 1987 |

|

SU1515359A1 |

Изобретение может быть использовано в цифровых частотомерах низ- них и средних частот с широким диапазоном изменения частоты входных импульсов, а также цифровых системах управления и регулирования. Цель изобретения - расширение диапазона рабочих частот при сохранении точности - достигается введением в умножитель частоты третьего интегратора 10 и блока 11 опорного напряжения. Кроме того, умножитель частоты содержит интеграторы 1 и 2, блок 3 выборки и хранения, компаратор 4, формирователь 5 импульсов, выходную шину 6, блок управления, входную шину 8, источник 9 опорного напряжения. Блок 11 содержит источник 12 опорного напряжения, который через делитель 13 напряжения соединен с диодами 14 и 15. Умножитель обладает высоким быстродействием, что обеспечивает повьштение точности и расширение диапазона рабочих частот. 2 з.п. ф-лы, 3 ил. ш (Л С СА GO 0ta.f

I

1f

tl.M iОХЧГ

7Sig 20

ери г. г.

Редактор Л.Пчолинская

Составитель Сазонов Техред И.Верес

Заказ 3591/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

Корректор В.Бутяга

| Умножитель частоты | 1982 |

|

SU1083330A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Новицкий П.В | |||

| и др | |||

| Цифровые приборы с частотными датчиками | |||

| - Л.: Энергия, 1970, с | |||

| ПОРШНЕВОЙ ДВИГАТЕЛЬ | 1916 |

|

SU282A1 |

Авторы

Даты

1987-08-15—Публикация

1985-10-28—Подача