1

Изобретение относится к импульсной технике и может нспользонаться для моделирования и контроля каналов связи

Цель изобретения - увеличение спектра генерируемых потоков.

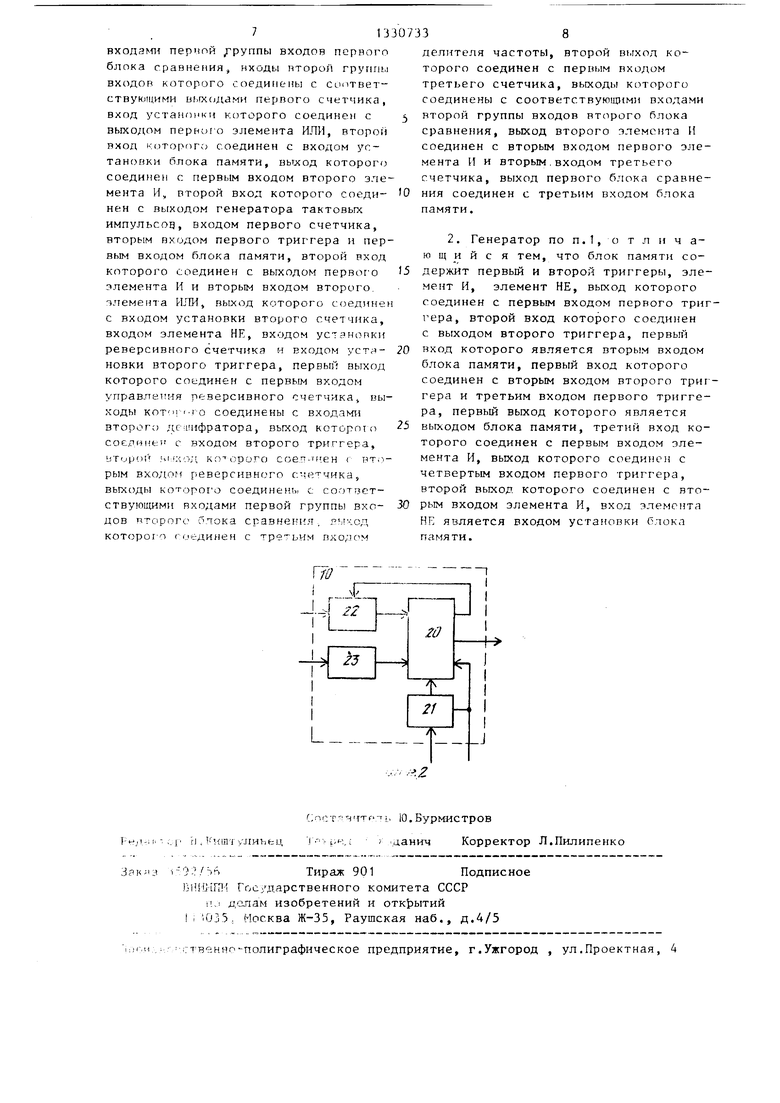

На фиг.1 представлена структурная схема генератора потока ошибок; на фиг.2 - схема примера реализации блока памяти.

Генератор потока ошибок (фиг.1) содержит генератор 1 тактовых импульсов, первьп 2, второй 3 и третий k счетчики, реверсивный счетчик 5, первый 6 и второй 7 блоки , пер-15 нения, выход которого соединен с Бый8и второй 9 дешифраторы, блок 10 третьим входом делителя 12 частоты, памяти, первый триггер 11, делитель 12 частоты, второй тригтер 13, первый 14 и второй 15 злеме)1ты И, первторой выход которого соединен с первым входом третьего счетчика 4, выходы которого соединены с соответ

16 и второй 17 элементы 1ШИ, эле-20 твую1цими входами второй группы входов

мент НЕ 18, шину 19 начальной уста- ИОВУЛ1, 13 11ход генерат ора 1 тактовых импульсов соединен с входом /телителя 12 частотьи Вь ходы второго счетчика 3 соединены с входги-ш пер- 2 1юго дс-шифрггтора 8, выход которого соед;тиап с первьм входом первого триггера 1 1 , выход которс т-о соединен с iiopBLiN; входом пбрвого лсмснга И 14.

второго блока 7 сравнения. Выход второго элемента И 15-соединен с вторым входом первого элемента И 14 и вторым входом третьего счетчика 4. Вых/эд первого блока 6 сравнения соединен с третьим входом блока 10 памяти.

Блок 10 памяти (фиг.2) содержит первы 20 и второй 21 триггеры, элемент И 22, элемент НЕ 23, выход котоВыход второго элемента И 15 соединен зо рого соединен с первым входом первопервым входом перяогп элемента ИЛИ

I о „

r;-iiro:i 19 япчальиой у

пьгм пчоцог- зторот -; э

V , ч Г M ;HT;I Н 1 пг г i IC, i т i

;:.-iT-o с: о единен с

. и пер- т мйнта ИЛИ 17.

;;, :, пг.пг.,) с BTQ -: ч.и - ГГ ты, г ер- . : . ;- .jb: ; ;с ;ик | 5 и вхо- 3 . ВЫХОД1: КОТОb -.,ii,OM рс; о :: /; л( Г О : дом второго счетчика рого coc;iniien.4 с соотвстстБующики iii ppofi rpyrriM входов первого блока 6 сравнения, входы второй группы BxojuH3 которого соодипень с соот- вс гстпую- уп .п цыходами первого счетчи- .:а 2. вход vcraHOBKH )рого соедп- iioii с ;зь х: .п.ом первого ИЛИ 16 второй вход которого соединен с вхопамяти, выход

установки блока которого соединен с первый входом ь rDpoi c :)лепента И 15, нтороС вход которого сеед11}1ек с выходом генерато- - 1 тактотп;1Х импульсов, входом пер- йоге счетчика 2, вторым входом первого тригтера 11 и первым входом блока

Генератор потока ошибок работает следую1 Д м образом.

Во втором счетчике 3 содержится длина безоишбочного интервала, т.е. число тактовых импульсов в данном безошибочном интервале (начинается с нуля), а в реверсивном счетчике 5 - число, показывающее сколько раз этот

10 памяти, второй вход которого соеди- интервал повторить (начинается иен с выходом первого элемента И 14 и с единицы). Счетчик 2 считает такто- ш.-орыь входом второго элемента ИЛИ 17, 11ыход которого соедипеи с гг-:одом ус- Гстполки счот -шкл 3, входом

вые импульсы, а счетчик 4 - моменты окончаний безошибочных интервалов. Как только количество тактовых импул

07332

элемента 18 НЕ, входом установки реверсивного счетчика 5 и входом установки второго триггера 13, первый

, выход которого соединен с первым входом управления реверсивного счетчика 5, выходы которого соединены с входами, второго дешифратора 9, выход которого соединен с входом второго триг10 гера 13, второй выход которого соединен с вторым входом реверсивного счетчика 5, выходы которого соединены с соответствующими входами первой группы входов второго блока 7 сравнения, выход которого соединен с третьим входом делителя 12 частоты,

второй выход которого соединен с первым входом третьего счетчика 4, выходы которого соединены с соответсвторого блока 7 сравнения. Выход второго элемента И 15-соединен с вторым входом первого элемента И 14 и вторым входом третьего счетчика 4. Вых/эд первого блока 6 сравнения соединен с третьим входом блока 10 памяти.

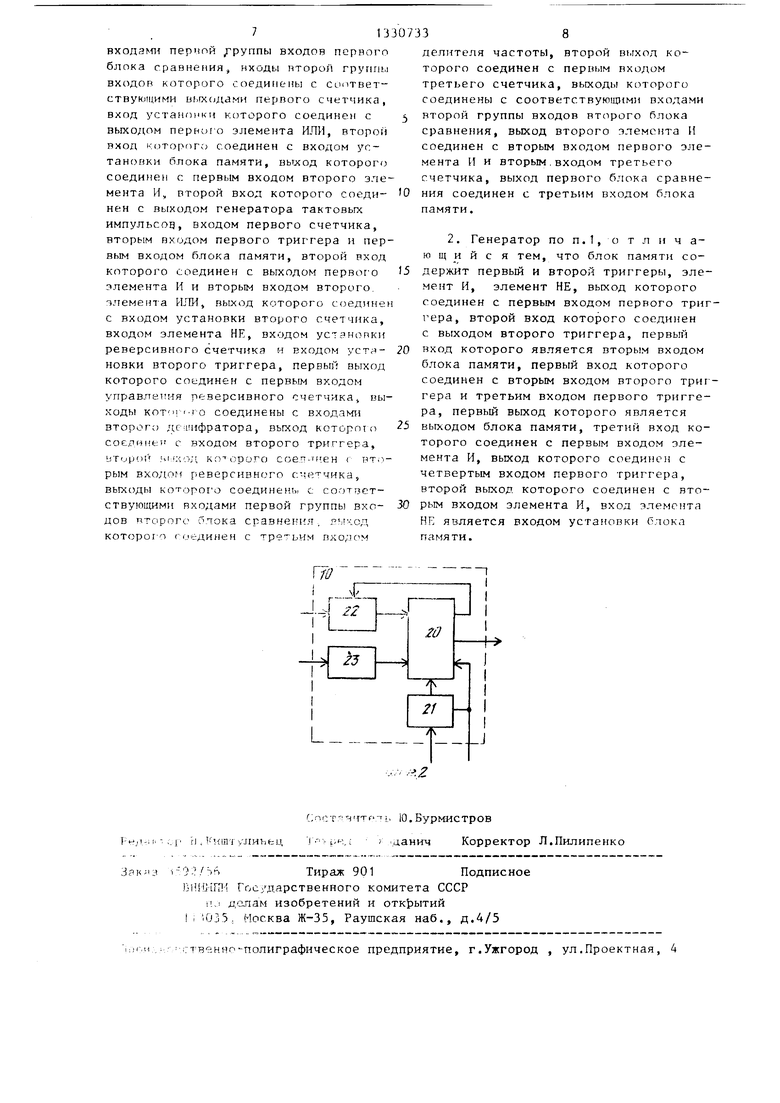

Блок 10 памяти (фиг.2) содержит первы 20 и второй 21 триггеры, элемент И 22, элемент НЕ 23, выход кото0

го триггера 20, второй вход которого соединен с выходом второго триггера 21, первый вход которого является вторым входом блока 10 памяти, первый рход которого соединен с вторым входом второго триггера и третьим Бходом первого триггера 20, первый выход которого является выходом блока 10 па -1яти, третий вход которого соединен с первым входом элемента И 22, в1)Гход которого соединен с четвертым входом первого триггера 20, второй выход которого соединен с вторым входом элемента И 22. Вход элемента НЕ 23 является входом уста- HOBK;I блока 10 памяти.

Генератор потока ошибок работает следую1 Д м образом.

Во втором счетчике 3 содержится длина безоишбочного интервала, т.е. число тактовых импульсов в данном безошибочном интервале (начинается с нуля), а в реверсивном счетчике 5 - число, показывающее сколько раз этот

интервал повторить (начинается с единицы). Счетчик 2 считает такто-

вые импульсы, а счетчик 4 - моменты окончаний безошибочных интервалов. Как только количество тактовых импульсов, сосчитанное счетчиком 2, становится равным длине безошибочного интервала, записанной в счетчик 3, блок 6 сравнения вьщает сигнап на блок 10 памяти, который разрешает прохождение тактового импульса через элемент И 15 на выход устройства и на вход счетчика 4, увеличивая его содержимое на

канчивается цикл работы ренерспвного счетчика 5 и цикл выдачи безошибочных интервалов, т.е. щткл работы устройства.

Рассмотрим работу устроистна более подробно. Перед началом работы на шину 19 начальной установки подается сигнал, который переводит тригтср 13, единицу, а также через элемент ИЛИ 16 ю делитель 12 частоты, счетчики 2 и 3, на сброс счетчика 2 в исходное (нуле- реверсивный счетчик 3 и блок 10 памя

вое) состояние. Если содержимое счетчика 4 не равно содержимому реверсивного счетчика 5, то длина безошибочного интервала, записанная в счетчик 3, не меняется и циклы работы счетчика 2 повторяются до тех пор, пока содержимое счетчика 4 не станет равным содержимому реверсивного счетчик 5. 3 этом случае блок 7 сравнения через делитель 12 частоты выдает сигнал, который увеличивает содержимое счетчика 3 на единицу (увеличивает на единицу длину безошибочного интервала), мчменяет содержимое реверсивного счетчика 5 на единицу и переводит счетчик 4 в исходное (нулевое ) состоя 1ие. Режим работы реверсивног о счетчика 5 задается состоянием триггера 13. В начале работы триггер 13 находится в исходном состоянии и выдает с выхода на вход управления реверсивного счетчика 5 сигнал прямого счета . Как только число, записанное на реверсивном счетчике 5, становитс равным п, дешифратор 9 вырабатывает сигнал, который переводит триггер 13 в рабочее состояние и последний начинает выдавать на вход управления реверсивного счетчика 5 со своего выхода сигнал обратного счета. Каждый цикл работы счетчика 4 заканчивается увеличением длины безошибочного интервала, записанного в счетчике 3, и когда она становится максимальной, т.е. равной 2п - 2, то дешифратор 8 вырабатывает сигна.п, который через триггер 11, элемент И 14 и элемент ИЛИ 17 переводит счетчик 3, триггер 13, делитель 12 частоты и реверсив ньй счетчик 5 в исходное состояние При этом в исходном состоянии в ш.-гг- чики 2-4 записывается нуль, а в реверсивный счетчик 5 - единица. Перевод в исходное гостояние триггера 13, делителя 12 частоты, счетчика 3, ре- версивиш о счетчика 5 осуществляется по импульсу, зaвepшaющe fy максималь- ньш безош1бочный интервал. Этим за

5

0

5 Q

0

0

5

ти в исходное состояние. В исходном состоянии числа, находяиц1еся в счетчиках 2, 3, одинаковы (оба нули), поэтому с выхода блока 6 сравнения на вход блока 10 памяти подается сигнал по которому с приходом первого тактового импульса блок 10 памяти устанавливается в рабочее состояние и пропускает тактовый импульса на через элемент И 15. Этот импульс через элемент ИЛИ 16 удерживает счетчик 2 в исходном состоянии и добавляс т единицу в счетчик 4, а так как счетчик 4 в исходном состоянии число, равное нулю, то записанное число становится равным единице и совпадает с числом, записанным в реверсивный счетчик 5. В результате этого блок 7 сравнения вьфабатывает сигнал, который устанавливает делитель 12 частоты в исходное-состояние, сигнал с выхода последнего поступает на сброс счетчика 4, устанавливая его в исходное состояние, а с первого выхода - на счетчик 3 и реверсивный счетчик 5, увеличивая их содержимое на единицу. На этом заканчивается первы Ш1КЛ работы счетчика 4. Наиболее короткие безошибочные интервалы в первом и втором циклах работы счетчика 4, определяющих быстродействие и надежность работы. Блрк 10 памяти устанавливаетея в рабочее состояние при поступлении тактовых импульсов и при наличии сигнала сравнения с блока 6 сравнения при условии, что в предьдущем такте блок 10 памяти находился в исходном состоянии или данный такт является первым в данном рабочем цикле. По второму тактовому импульсу в счетчик 2 записывается единица, что совпадает с содержимым счетчика 3, и поэтому блок 6 сравнения вырабатывает сигнал сравнения, который по третьему тактовому импульсу устанавливает блок 10 памяти в рабочее состояние, которое разрешает прохоящение через элемент И 15 такто:ич о импульса, сбрг см килцего счетчшс 2 и записыпающего п счетчик А единицу В это время н реверсннном счетчике 5 записано число два, поэтому блок 7 cpaiMieiiTiH не )зырабатывает сигнала cpaDne}f;i j. По четвертому импу-цьсу в счетчик 2 записывается единица и по сигналу с выхода блока 6 сравнения п пятому тактовому импульсу срабатывает блок 10 памяти, выдается сигнал на выход устройства, который сбрасывает счетчик 2, и в счетчике А устанавливает число два, которое совпадает с числом в реверсивном счетчике 5,иоэтом1 блок 7 сравнения вырабатывает сигнал, который по шестому тактовому импульсу переводит делитель 12 частот:; в рабочее состояние, а пос- переводит в исходное состояние счетчик 4, а содержимое счетчика 3 и рер,ирсив)ого счетчика 5 увеличивает па единицу. Так заканчи11ас тся второй и, работы счетчика 4.

К.альнейшая работа устройства ана ..огична работе его во втором цикле счетчика 4 до тех пор, пока в реверсивном счетчике 5 не будет записано ,равное и. После записи числа п р. реж рсипный счетчик 5 срабатьшает деиифр .то 9 и перевг.1Д11т триггер 3 в рапочес: состояние, пмсле чего в реиеГ СИ Пип- счетчике 5 после око)1ча- ния iva.-;vu;T o i;i-n jia счетч-ика 4 ие при- бапляеч ся ециница, а лпчитается. Так пр();,; . гжи1 - тся до после/u crii цикла (;че чика ( в j ainiOM цик.че работы уст- poi CTiia- , иаступчипии последнего цикта счот ч1иса 4 счетчик 3 насчитыфронту синхроимпульсов, поступаюпшх на первый вход блока 10 памяти. Инверсный выход триггера 20 через элемент И 22 соединен с своим информа5 ционным входом. Поэтому при любых сигналах на третьем входе блока 10 памяти по информационному входу невозможно установить триггер 20 в рабочее состояние в двух соседних так10 так. Однако такая необходимость появляется на границе двух циклов работы устройства. Это обеспечивает триггер 21, который по сигналу установки в конце цикла работы устройства уста15 навливается в рабочее состояние, и по входу установки в рабочее состояние (обычно R - или S- вход) удерживает триггер 20 на протяжении первого такта следующего цикла в рабочем сос20 тоянии. Элемент НЕ 23 обеспечивает согласова}ше сигналов установки триггера 20 в исходное состояние с полярностью пускового сигнала на входе устройства,

25 Предлагаемое устройство позволяет создавать модели потока ошибок, возникающего при наличии структуроподоб- ной помехи в каналах связи, обеспечивая при этом распределение безоши30 бочпых интервалов по закону Симпсона,

Формула изобретения

нает числи Zi

- .

, 11 о jj е р с и in ibii I счетчик

1. Генератор потока ошибок, содер- 35 жащй генератор тактовых импульсов, выход которого соединен с первым входом делителя частоты, первый счетчик, второй счетчик, выходы которого соединены с входами первого дешифратора, 40 выход которого соединен с первым входом первого триггера, выход которого соединен с первым входом первого элемента И, тзторой дешифратор, отличающийся тем, что, с целью 45 увеличения спектра генерируемых потоков, в него введены третий счетчик, реверсивный счетчик, первый и второй первый цикл работы устройства. Осталь- блоки сравнения, блок памяти, второй ньк1 его работы аи;1ло1 ичны за триггер, второй элемент И, выход ко- исклычением того, что каж/,ый последую-50 торого соединен с первым входом перво1)- , срабатывает дешифратор 8, срабатыгь К т делителт. 12 частоты, который после срабатывания блока 10 niK iiy c-KaeT через элемент И 15 и элемент 1 14 тактоиый импульс, ко- i-oj4--iii является импульсом сброса дд1Я счетчикот5 3 и 4, реверсивного счетчика 5, триггера 13. Так заканчивается

lUJui цикл начинается при рабочем состоянии б.иока 10 памяти.

Блок 10 памяти работает следующим образом.

Он сопертагг триггер 20 - типа D, а триггер 21 - типа IK, прп этом ipitrrep 20 срабатывает по переднему d l o iTy, а триггер 21 -по заднему

0733-6

фронту синхроимпульсов, поступаюпшх на первый вход блока 10 памяти. Инверсный выход триггера 20 через элемент И 22 соединен с своим информа5 ционным входом. Поэтому при любых сигналах на третьем входе блока 10 памяти по информационному входу невозможно установить триггер 20 в рабочее состояние в двух соседних так10 так. Однако такая необходимость появляется на границе двух циклов работы устройства. Это обеспечивает триггер 21, который по сигналу установки в конце цикла работы устройства уста15 навливается в рабочее состояние, и по входу установки в рабочее состояние (обычно R - или S- вход) удерживает триггер 20 на протяжении первого такта следующего цикла в рабочем сос20 тоянии. Элемент НЕ 23 обеспечивает согласова}ше сигналов установки триггера 20 в исходное состояние с полярностью пускового сигнала на входе устройства,

25 Предлагаемое устройство позволяет создавать модели потока ошибок, возникающего при наличии структуроподоб- ной помехи в каналах связи, обеспечивая при этом распределение безоши30 бочпых интервалов по закону Симпсона,

Формула изобретения

го элемента 1 ШИ, второй вход которого соединен с шиной начальной установки и первым вхгодом второго элемента ИЛИ, элемент НЕ, выход которого соединен с вторым входом делителя частоты,

первый выход которого соединен с,пер- вь1м входом реверсивного счетчика и входом второго счетчика, выходы которого соединены с соответствующими

713

входами парной / руппы входов первого блока сравнения, нходы пторой группы входов которого соединены с сиптвет- ствующими вьгх( первого счетчика, вход устанонкм которого соединен с выходом пергпл о элемента ИЛИ, второй вход которого соединен с входом установки блока памяти, выход которого соединен с первым входом второго элемента И, второй вход которого соеди- иен с выходом генератора тактовых импульсод, входом первого счетчика, вторым входом первого триггера и первым входом блока памяти, второй вход которого соединен с выходом первог о элемента И и вторым входом второго, элемента ИЛИ, выход которого соединен с входом установки второго счетчика, входом элемента НЕ, входом устэнопкп реверсивного счетчика и входом устя- новки второго триггера, первый выход которого соединен с первым входом управления реверсивного счетчика выходы кот 11 i-ro соединены с входами второго дса ифратора, выход которого соединен с входом второго триггера, ьтороГ ы.Счод Kn oporcj с ит.-:- рым вxoдo f реверсивного с гр., выходы которог о соединен)., с соответствующими входами первой группь вхо- дов второго блока сравнеьгил яыкод которого го€-динен с третьим входом

ишт улиььц

(; п Г; т I ч тт f т ь 10. Бу рмис тр ОБ

- Р« ,; ) данич Корректор Л.Пилипенко

i- }// iТираж 901Подписное

jH.lfLrn- Государственного комитета СССР

1, д(2лам изобретений и открытий h i035, Москва Ж-35, Раушская наб., д.4/5

;твен.но-полиграфическое предприятие, г.Ужгород , уд .Проектная, 4

38

делителя частоты, второй выход которого соединен с первым входом третьего счетчика, вьсходы которого соединены с соответствующими входами второй группы входов второго блока сравнения, выход второго элемента И соединен с вторым входом первого элемента И и вторым.входом третьего счетчика, выход первого блока сравнения соединен с третьим входом блока памяти.

2. Генератор по п.1, о т л и ч а- ю щ и и с я тем, что блок памяти содержит первый и второй триггеры, элемент И, элемент НЕ, выход которого соединен с первым входом первого триггера, второй вход которого соединен с выходом второго триггера, первый вход которого является вторым входом блока памяти, первый вход которого соединен с вторым входом второго триггера и третьим входом первого триггера, первый выход которого является выходом блока памяти, третий вход которого соединен с первым входом элемента И, выход которого соединен с четвертым входом первого триггера, второй выход, которого соединен с вторым входом элемента И, вход элемента НЕ является входом установки блока памяти.

...

-. -.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля и испытаний блоков памяти бортовых ЭВМ | 1984 |

|

SU1182526A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Генератор случайного импульсного процесса | 1982 |

|

SU1094032A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Анализатор случайных процессов | 1987 |

|

SU1474678A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| Авторское свидетельстао СССР ,№ 1077044, кл,Н 03 К 3/84, 1982 | |||

| Генератор тактовых импульсов | 1979 |

|

SU855963A2 |

Авторы

Даты

1987-08-15—Публикация

1986-03-03—Подача