1

Изобретение предназначено для статистического анализа случайных процессов и может быть использовано в системах обработки информации.

Целью изобретения является расширение функциональных возможностей за счет формирования признака стационарности случайного процесса.

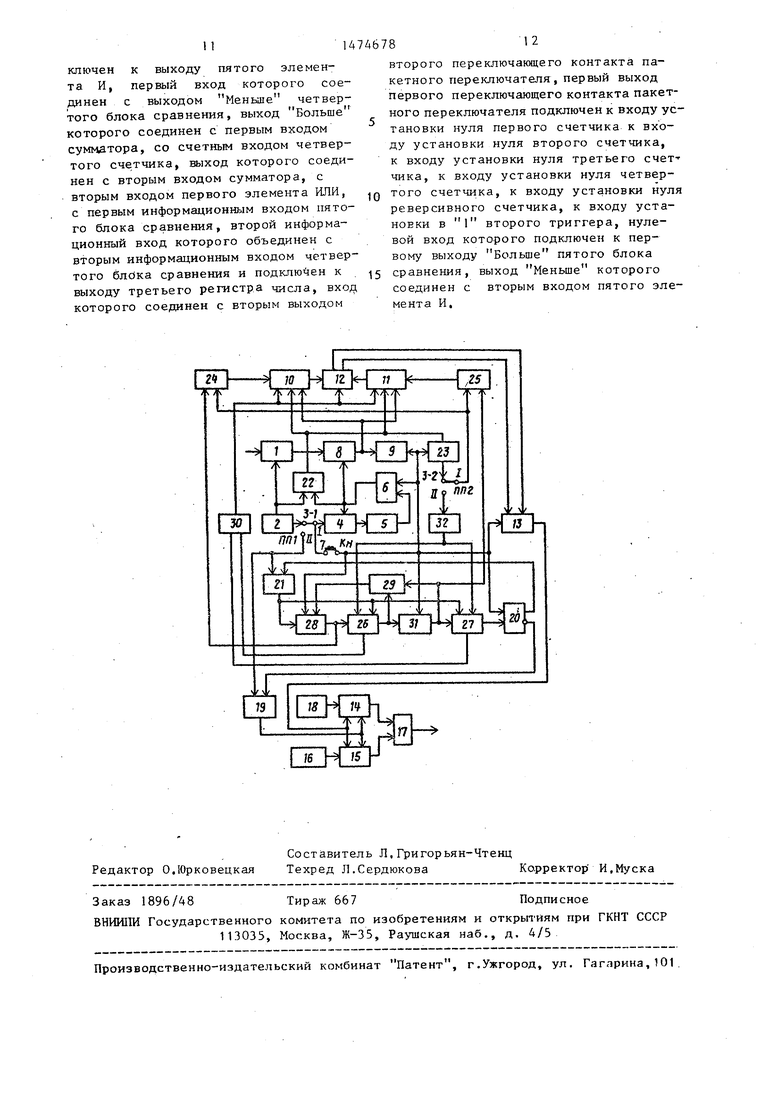

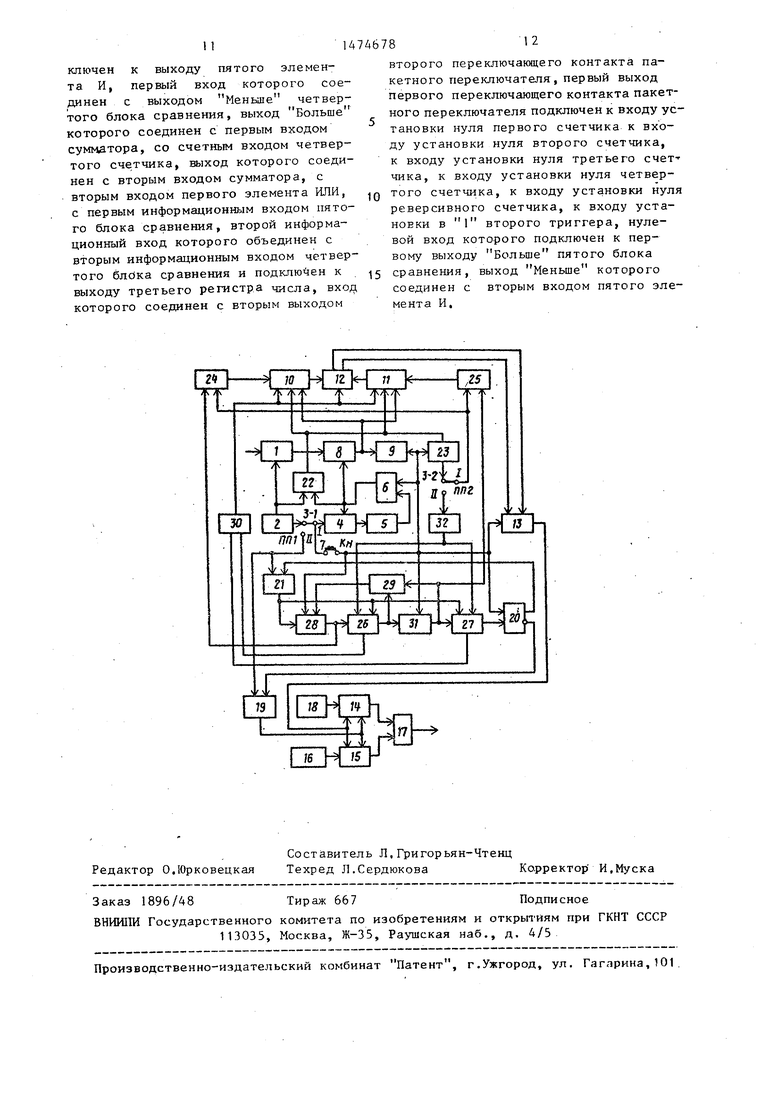

На чертеже представлена блок-схема анализатора,

Информационный вход аналого-цифрового преобразователя 1 является входом анализатора, а управляющий вход соединен с первым выходом генератора 2 тактовых импульсов, второй выход которого через первый переключающий контакт 3-1 пакетного переключателя 3 соединен с информационным входом первого временного селектора 4, выход которого через делитель 5

частоты соединен с нулевым входом первого триггера 6, единичный вход которого через кнопочный переключатель 7 объединен с информационным входом первого временного селектора 4, вход разрешения которого объединен с входом разрешения второго временного селектора 8 и подключен к единичному выходу первого триггера 6. Выход аналого-цифрового преобразовав теля 1 подключен к информационному входу второго временного селектора 8, выход которого соединен со счетным входом первого счетчика 9 и с информационными входами первого и второго блоков 10 и 11 памяти, выходы которых подключены соответственно к первому и второму информационным входам первого блока 12 сравнения, выходы Больше и Меньше которого

#Ь 1

4

оэ j

00

соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 13, выход которого соединен с первым информационным входом второго блока 14 сравнения, с первым информационным входом третьего блока 15 сравнения, второй информационный вход которого соединен с выходом первого регистра 16 числа, а выход подключен к первому входу первого элемента И 17, выход которого является выходом анализатора, а второй вход соединен с выходом второго блока 14 сравнения, второй информационный вход которого соединен с выходом второго регистра 8 числа, а управляющий вход объединен с управляющим входом третьего блока 15 сравнения и подключен к выходу второго элемента И 19, пер- вый вход которого соединен с нулевым выходом второго триггера 20, единич- ный выход которого подключен к первому входу третьего элемента И 21, второй вход которого объединен с вторым входом второго элемента И 19 и подключен к второму выходу первого переключающего контакта 3-1 пакетного переключателя 3, Первый выход генератора 2 тактовых импульсов соединен с первым входом четвертого элемента |И 22, второй вход которого подключен к единичному выходу первого триггера 6, а выход соединен соответственно с входами разрешения записи первого и второго блоков 10 и 11 памяти и со счетным входом второго счетчика 23, выход которого через второй переключающий контакт 3-2 пакетного переключателя 3 соединен соответственно с первым входом первого элемента ИЛИ 24 и с первым входом второго элемента ИЛИ 25р выход которого подключен к адресному входу второго блока 11 памяти, Выход третьего элемента И 2 соединен с входами разрешения сравнения четвертого блока 26 сравнения и пятого блока 27 сравнения и со счет

ным входом третьего счетчика 28, вход.

5

приема кода которого подключен к выходу сумматора 29, а выход соединен соответственно с первым информационным входом четвертого блока 26 сравнения и с вторым входом первого элемента ИЛИ 24, выход которого подключен к адресному входу первого блока 10 памяти, вход разрешения чтения которого объединен с входом

10

2025

д.

46784

разрешения чтения второго блока 11 памяти, с управляющим входом первого блока 12 сравнения и подключен к выходу пятого элемента И 30, первый вход которого соединен с первым входом четвертого блока 26 сравнения, второй выход которого соединен соответственно с первым входом сумматора 29 и со счетным входом четвертого счетчика 31, которого соединен с вторым входом сумматора 29, с вторым входом второго элемента ИЛИ 25 и с первым информационным входом пятого блока 27 сравнения, второй информационный вход которого соединен с вторым информационным входом четвертого блока 26 сравнения и подключен к выходу третьего регистра 32 числа, вход которого соединен с вторым выходом второго переключающего контакта 3-2 пакетного переключателя 3, Информационный вход первого временного селектора 4 через кнопочный переключатель 7 объединен с входами установки нуля первого счетчика 9, второго счетчика 23, третьего счетчика 28, четвертого счетчика 31 и реверсивного счетчика 13, а также с единичным входом второго триггера 20, нулевой вход которого подключен к первому выходу пятого блока 27 сравнения, второй выход которого соединен с вторым входом пятого элемента И 30, В положении I пакетного переключателя 3 анализатор измеряет среднее значение исследуемого случайного процесса и осуществляет накопление поступающих измерений в блоках 10 и 11 памяти.

Работа анализатора по измерению среднего значения заключается в следующем.

Напряжение реализации х (t) исследуемого случайного процесса X (t) поступает в аналого-цифровой преобразователь 1. В моменты выборок, задаваемых импульсами генератора 2 тактовых импульсов, напряжение реализации преобразуется в цифровой код. Этот код подводится к информационному входу временного селектора 8 и может проходить через него в счетчик 9 только тогда, когда на его вход разрешения подано разрешающее напряжение с триггера 6, что имеет место, если единичный выход триггера нахо30

35

40

45

50

55

5

дится в единичном состоянии. За N выборок (опросов) в счетчике 9 накапливается число, которое дает непосредственную оценку среднего значения исследуемого процесса,

Количество выборок N задаетсясхемой, состоящей из временного селектора 4, делителя 5 частоты, триггер 6, первого переключающего 3-1 пакетного переключателя 3, кнопочного переключателя 7. До начала измерений единичный выход триггера 6 может находиться в произвольном состоянии. После нажатия переключателя 7 первый импульс опроса с второго выхода генератора импульсов опроса через neprv вый переключающий контакт 3-1 пакетного переключателя 3 устанавливает единичный выход триггера 6 в единичное состояние, с этого момента на оба временных селектора 4 и 8 поступает разрешающее напряжение и, следовательно, создается Возможность передачи через временный селектор 8 цифрового кода с аналого-цифрового преобразователя 1 в счетчик 9,

Этот же импульс, появившийся при нажатии переключателя 7, устанавливает в нуль все счетчики 9, 13, 23, 28 и 31 анализатора и перебрасывает триггер 20 в единичное состояние. Таким образом, в этот момент открывается элемент И 21, а элемент И 19 закрывается для прохода импульсов, Пока единичный выход триггера 6 пребывает в единичном состоянии, импульсы опроса с второго выхода генератора 2 проходят через временной селектор 4 в делитель 5 частоты, который представляет собой пересчетную схему. После сдачи N импульсов на выходе делителя 5 возникает импульс, переводящий единичный выход триггера 6 в положение нуля, В результате снимается разрешающее напряжение с временных селекторов 4 и 8, и счет импульсов прекращается,

Накопление измеренных значений исследуемого случайного процесса в блоках 10 и 11 памяти проходит следующим образом.

На информационные входы обоих блоков 1Q и 11 подаются коды, которые проходят через временный селектор 8, Сигнал р-азрешения записи для блоков 10 и 1 1 формируется элементом И 22, который пропускает импульсы с первого выхода генератора 2 тактовых им746786

пульсов,когда единичный выход триггера 6 находится в единичном состоянии, Эти же импульсы, прошедшие через элемент И 22, подаются на вход счетчика 23, .Таким образом, в счетчике -23 формируется номер выбранного значения исследуемого случайного процесса. Этот номер используется для 10 адресации информации при записи ее з-первый и второй блоки 10 и 11 памяти. Код с выхода счетчика 23 через второй переключающий контакт 3-2 пакетного переключателя 3 подается .,. на входы элементов ИЛИ 24 и 25 и проходит через них без изменений на адресные входы блоков 10 и 11, потому что на другие входы элементов ИЛИ 24 и 25 в эти моменты поступают Q нулевые коды соответственно со счетчиков 28 и 31.

Цикл измерения среднего и запоминания результатов измерений исследуемого случайного процесса в блоках 5 10 и 11 памяти заканчивается с выработкой сигнала делителя 5 частоты, В конце этого цикла в счетчике 23 на. капливается число запомненных в бло-, ках 10 и 11 измерений. о В момент переключения пакетного переключателя 3 в положение II начинается цикл работы анализатора по проверке накопленных в блоках 10 и 11 памяти измерений исследуемого процесса на стационарность. В конце этого цикла на выходе анализатора появляется импульс, если исследуемый случайный процесс определен как стационарный,

0 Для формирования признака стационарности в предлагаемом анализаторе используется непараметрическая статистика, суть которой следующая.

По -реализации случайного, процес- 5 са X (t), содержащей N+1 измерений х (( 1 ) .N), вычисляется непараметрическая статистика

N-1N

С ZI 2Z С ,-j , ( I)

i 0 j; ( 1

5

0

где величина С-- вычисляются по формуле

;1 , если х. х; ; О, если .; (2) - 1, если х ( .

Исследуемый случайный процесс является стационарным, если найденная статистика -С удовлетворяет условию

,(3)

где величина Сн и Cg задают соответственно нижнюю и верхнюю границы допуска для статистики С, в пределах которого исследуемый случайный процесс является стационарным.

Работа анализатора по формированию признака стационарности заключа- етбя в следующем,

При переключении пакетного переключателя в положение II происходит перезапись содержимого счетчика 23 и регистр 32 числа, откуда оно подается на вторые информационные входы блоков 26 и 27 сравнения.

,-

Счетчик 28 используется для организации цикла по индексной переменной j , а счетчик 31 организует цикл по индексной переменной i, Сумматор 29 служит для записи полученного значения в счетчик 28, где оно используется в качестве начального значения индексной переменной j, На- вход счетчика 28 поступают импульсы, которые пропускает открытый элемент И 21. Значение счетчика 28 индексной переменной j подается на первый вход блока 26 сравнения и через элемент ИЛИ 24 попадает на адресный вход блока 10 памяти. Блок 26 сравнения сравнивает содержимое счетчика 28 с содержимым регистра 32 числа, Если содержимое счетчика 28 не больше со- держииого регистра 32 числа, то на первом выходе блока 26 сравнения появляется импульс, который проходит на первый вход элемента И 30, Если содержимое счетчика 28 больше содер- жимого регистра 32 числа, то на втором выходе блока 26 появляется им-: . пульс, который поступает на вход счетчика 31 и первый вход сумматора 29. Импульс на втором выходе блока 26 увеличивает содержимое счетчика 3 на единицу, разрешает сумматору 29 прибавить к изменившемуся значению счетчика 31 единицу и записать полученное значение в счетчик 28, Содер- жимое счетчика 31 подается на первый вход блока 27 сравнения„ на второй вход сумматора 29 и через первый вход элемента ИЛИ 25 попадает на адресный вход блока 11 памяти, Разреше ние на начало сравнения в блоках 26 и 27 сравнения производится импульсом, прошедшим через элемент И 21, Блок 27 сравнения производит сравне5

О

15

202530 40 Д5 1 ,-,. ссние содержимого счетчика 31 с содержимым регистра 32 числ-а. Если содержимое счетчика 31 не меньше содержи- мого регистра 32 числа, то на первом выходе блока 27 сравнения появляется импульс, который проходит на нулевой вход триггера 20 и переводит его единичный выход в нулевое состояние. Тем самым закрывается элемент И 21, и открывается элемент И 19 для пропускания импульсов с второго выхода генератора импульсов. Если содержимое счетчика 31 меньше содержимого регистра 32 числа, то на втором выходе блока 27 сравнения появляется импульс, который подается на второй вход элемента И 30, Импульсы с выхода элемента И 30 обеспечивают считывание значений исследуемого случайного процесса с блоков 10 и 11 памяти и сравнение этих значений в блоке

12.Последний производит сравнение поступивших значений х.- и х-. Если значение х, больше значения х,. то на первом выходе блока 12 появляется импульс, который проходит на суммирующий вход реверсивного счетчика

13.Если значение х меньше значения X;, то на втором выходе блока 12 появляется импульс, который проходит на вычитающий вход реверсивного счетчика 13, Таким образом, в реверсивном счётчике 13 подсчитывается статистика С, Содержимое реверсивного счетчика 13 подается на первые информационные входы блоков 14 и 15 сравнения, Когда подсчет статистики С заканчивается, то открывается эле- мет И 19, и первый импульс, прошедший через него, разрешает блокам 14

и 15 сравнения производить сравнение. На второй информационный вход блока 14 подается содержимое регистра 18 числа, в котором хранится нижняя граница допуска Сн статистики С, Блок 14 сравнения производит сравнение статистики С с нижней границей допуска Сч, Если значение величины Сн не больше значения статистики С, то на выходе блока 14 сравнения появляется импульс, В противном случае импульсы на выходе блока 14 не возникают. На второй информационный вход блока 15 сравнения подается содержимое регистра 16 числа, в котором хранится верхняя граница допуска С $ статистики С, Блок 15 сравнения производит сравнение статистики

С с верхней границей допуска Св. Если значение статистики С не больше значения величины См то на выходе блока 15 появляется импульс. В противном случае импульсы на выходе блока 15 не возникают. Выходы блоков 14 и 15 сравнения подключены к входах элемента И 17. Следовательно, когда выполняется неравенство ( 3) , то на выходе элемента И 17 появляется импульс, Этот импульс является признаком стационарности исследуемого случайного процесса,

Формула изобретения

Анапизатор случайных процессов, содержащий генератор тактовых импульсов, первый выход которого под- ключей к тактовому входу аналого- цифрового преобразователя, информационный вход которого является информационным входом анализатора, второй выход генератора тактовых им- пульсов через первый переключающий контакт пакетного переключателя соединен с информационным входом первого временного селектора ,и через

кнопочный переключатель подключен

к входу установки в 1 первого триггера, выход первого временного селектора через делитель частоты соединен с входом установки в О первого триггера, единичный выход которого подключен к входам разрешения первого и второго временных селекторов, информационный вход которого соединен с выходом аналого-цифрового преобразователя, выход второго времен 40 ного селектора подключен к С-входу первого счетчика, первый регистр числа, первый блок сравнения, первый элемент ИЛИ, отличающийся тем, что, с целью расширения функцио- нальных возможностей за счет формирования стационарности случайного процесса, анализатор содержит два блока памяти, пять элементов И, элемент ИЛИ, два регистра числа, три счетчи- ,.- ка, четыре блока сравнения, сумматор, реверсивный счетчик, при этом выход аналого-цифрового преобразователя подключен к информационным входам первого и второго блоков памяти, вы- „ ходы которых подключены соответственно к первому и второму информационным входам первого блока сравнения, выходы Больше и Меньше которого

jg

15

0 25

30

40 ,.- „

соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выход которого соединен соответственно с первым информационным входом второго блока сравне- ния, с первым информационным входом третьего блока сравнения, второй информационный вход которого соединен с выходом первого регистра числа, выход третьего блока сравнения подключен к первому входу первого элемента И, выход которого является выходом анализатора, второй вход первого элемента И соединен с выходом второго блока сравнения, второй информационный вход которого ;соединен с выходом второго регистра числа, а управляющий вход второго блока сравнения объединен с управляющим входом третьего блока сравнения и подключен к выходу второго элемента И, первый вход которого соединен с нулевым выходом второго триггера, единичный выход которого подключен к первому входу третьего элемента И, второй вход которого объединен с вторым входом второго элемента И и подключен к второму выходу первого переключающего контакта пакетного переключателя, первый вход генератора тактовых импульсов соединен с первым входом четвертого элемента И, второй вход которого подключен к единичному выходу первого триггера, выход четвертого элемента И соединен с входами разрешения записи первого и второго блоков памяти И, со счетным входом второго счетчика, выход которого через второй переключающий контакт пакетного переключателя соеди нен -с первым входом первого элемента ИЛИ, с первым входом второго блока памяти, выход третьего элемента И соединен с входами сравнения четвертого и пятого блоков сравнения и со счетным входом третьего счетчика, вход приема кода которого подключен к выходу сумматора, выход третьего счетчика соединен с первым информационнным входом четвертого блока сравнения, с вторым входом первого элемента ИЛИ, выход которого подключен к адресному входу первого блока памяти, вход разрешения чтения которого объединен с входом разрешения чтения второго блока памяти, с входом разрешения сравнения первого блока сравнения и под11

ключей к выходу пятого элемента И, первый вход которого соединен с выходом Меньше четвертого блока сравнения, выход Больше которого соединен с первым входом сумматора, со счетным входом четвер14

того счетчика, выход которого соединен с вторым входом сумматора, с вторым входом первого элемента ИЛИ, с первым информационным входом пятого блока сравнения, второй информационный вход которого объединен с вторым информационным входом четвертого сравнения и подключен к выходу третьего регистра числа, вход которого соединен с вторым выходом

467812

второго переключающего контакта пакетного переключателя, первый выход первого переключающего контакта пакетного переключателя подключен к входу установки нуля первого счетчика к входу установки нуля второго счетчика, к входу установки нуля третьего счет чика, к входу установки нуля четвертого счетчика, к входу установки нуля реверсивного счетчика, к входу установки в 1 второго триггера, нулевой вход которого подключен к первому выходу Больше пятого блока

сравнения, выход Меньше которого соединен с вторым входом пятого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

| Анализатор случайных процессов | 1983 |

|

SU1137480A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU877564A1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

Изобретение предназначено для статистического анализа случайных процессов и может быть использовано в системах обработки информации с возможностью формирования признака стационарности случайного процесса. Целью изобретения является расширение функциональных возможностей за счет формирования признака стационарности случайного процесса. Устройство содержит аналого-цифровой преобразователь, генератор импульсов опроса, пакетный переключатель, два временных селектора, делитель частоты, два триггера, кнопочный переключатель, четыре счетчика, два блока памяти, пять блоков сравнения, реверсивный счетчик, три регистра числа, пять элементов И, два элемента ИЛИ и сумматор. 1 ил.

| Мирский Г,Я, Радиоэлектронные измерения, - М.: Энергия, 1975, с.427 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-13—Подача