ственно, выход первого элемента ИЛИ соединен с первыми входами- первого и второго элементов И блокауправления, выход переполнения счетчика блока управления соединен со счетным входом счетчика управления частотой, выход второго элемента ИЛИ соединен с первым входом третьего элемента И блока управления, входом синхронизации блока формирования контрольных кодов и счетным входом счетчика адреса, информационный выход которого соединен с первыми информационными входами коммутатора данных и коммутатора эталонных кодов и входом индикации адреса блока индикации, информационный выход блока-формирования фиксированного кода соединен с вторь1М и третьим информационными входами коммутатора данных и вторым информационным входом коммутатора эталонных кодов, выход кокоторого соединен с входом индикации эталонных кодов блока индикации и первым информационным входом блока сравнения, в.ьгход блока сравнения соединен с входом ошибки блока индикации и вторым входом третьего элемента ИЛИ выход которого соединен с. нулевым входом триггера пуска, выход регистра данных соединен с входом индикации данных блока индикации и вторым информационным входом блока сравнения, первый выход дешифратора блока. управления соединен с первым входом первого элемента ИЛИ блока управления, с входом индикации режима блока- индикации и первым управляющим входом коммутатора данных, выход которого является информационным входом контролируемого блока памяти, второй вькод дешифратора блока управления соединен с первым входом второго элемента ИЛИ, с первым управляющим входом коммутатора эталонных кодов и вторым входом индикации режима блока индикации, третий выход дешифратора блока управления соединен с вторым входом первого элемента ИЛИ, с первым входом третьего элемента ШШ блока управления, с третьим входом индикации режима блока индикации, вторым управляющим входом коммутатора данных, четвертый выход дешифратора блока управления соединен с вторым входом второго элемента ИЛИ, с первым входом четвертого элемента ИЛИ блока управления и с четвертьм входом индикации режима блока ищ икацин, пятый выход дешифратора блока управления соединен с третьим входом первого элемента ИЛИ, с вторым входом третьего элемента ШШ блока управления, с третьим управлякяцим входом коммутатора данных и с пятым входом индикации режима блока индикации, шестой выход дешифратора блока управления соединен с третьим входом второго элемента ИЛИ, вторым входом четверто го элемента ШШ блока управления с шестым входом индикации режима блока индикации, выходы третьего и четвертого элементов ШШ и выход третьего элемента И блока управления соединены соответственно с входом разрешения формирования контрольных кодов блока формирования контрольных кодов с вторым управляющим входом коммутатора эталонных кодов и входом разрешения сравнения блока сравнения, выход первого и четвертого .элементов ШШ блока управления соединены соответственно с втоым входом первого элемента И и с ретьим входом третьего элемента ИЛИ блока управления, выход второго элеента ИЛИ блока управления соеинен с вторыми входами второго третьего элементов И блока упавления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Многоканальное устройство для программного управления | 1989 |

|

SU1695266A1 |

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1261014A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

СИСТЕМА ДЛЯ КОНТРОЛЯ И ИСПЫТАНИЙ БЛОКОВ ПАМЯТИ БОРТОВЫХ ЭВМ, содержащая счетчик адреса, регистр данных, блок сравнения и блок управления, причем блок управления содержит счетчик, три элемента ИЛИ, дешифра- .тор, первьй и второй элементы И, выход переполнения и информационные выходы счетчика адреса соединены соответственно со счетным входом счетчика блока управления и адресным входом контролируемого блока памяти, информационный вьрсод которого соединен с и:- формационным входом регистра данных, информационные выходы счетчика блока управления соединены с входами дешифратора блока управления, выход первого элемента И блока управления соединен с входом записи контролируемого блока памяти, выход второго элемента И блока управления соединен с входом считывания контролируемого блока памятии синхровходом регистра данных, отличающаяся тем, что, с целью повьшения достоверности контроля, в устройство введены блок задания режима, блок формирования контрольных кодов, делитель час.тоты, блок индикации, счетчик управления частотой, коммутатор данных и коммутатор эталонных кодов, триггер пуска, генератор импульсов, первый, второй и третий элементы ИЛИ, а в блок управления введены третий элемент И, четвертый элемент ИЛИ, причем выходы адреса, кода режима, кода частоты, первый и второй выходы синхронизации и выход пуска блока задания i режимов соединены соответственно-с информационными входами счетчика ад(Л реса, счетчика блока управления, счетчика управления частотой, первыми входами первого и второго элементов ИЛИ, единичным входом триггера пуска, выход которого соединен с входом индикации работы блока индикации и пусковым входом генератора импуль00 сов, первый, второй и третий выходы ISD ел разрешения записи блока задания режимов соединены соответственно с вхоND дом синхронизации счетчика адреса, с тактовым входом счетчика блока управления и тактовым входом счетчика управления частотой, выход переполнения которого соединен с первым входом третьего элемента ИЛИ и входом индикации Норма блока индикации, информационный выход счетчика управления частотой и выход генератора импульсов соединены соответственно с информационным и тактовым входами делителя частоты, первый и второй выходы которого соединены с вторыми входами первого и второго элементов ИЛИ соответ

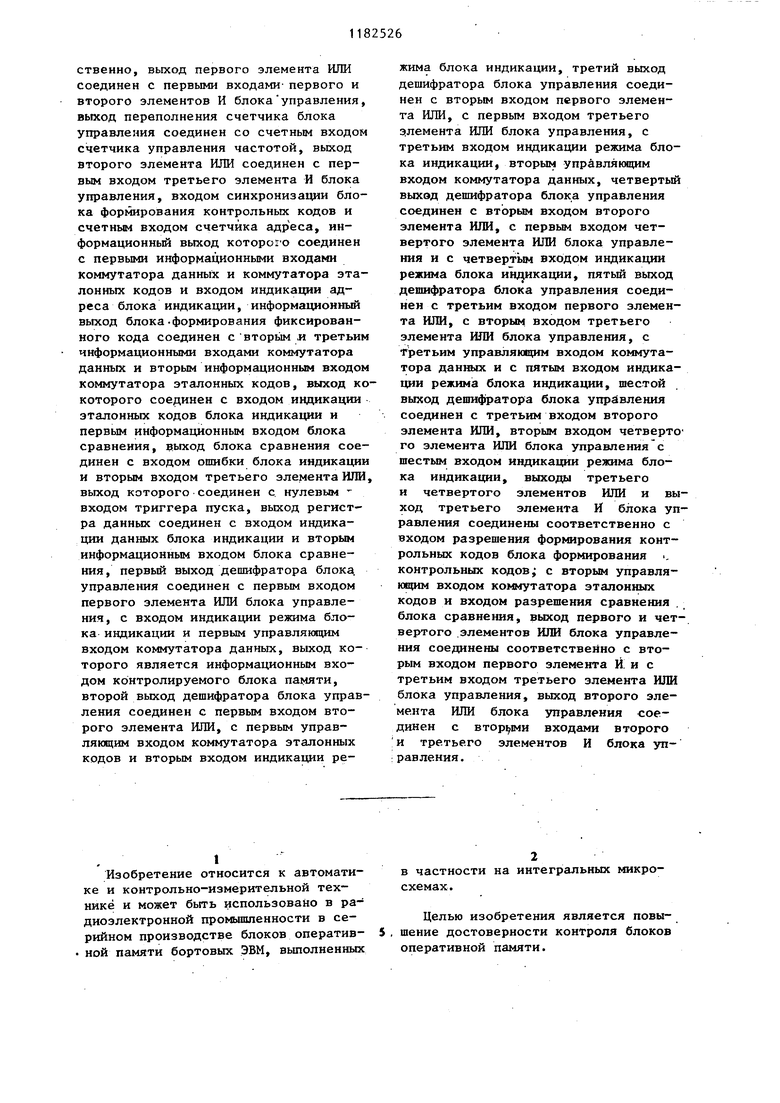

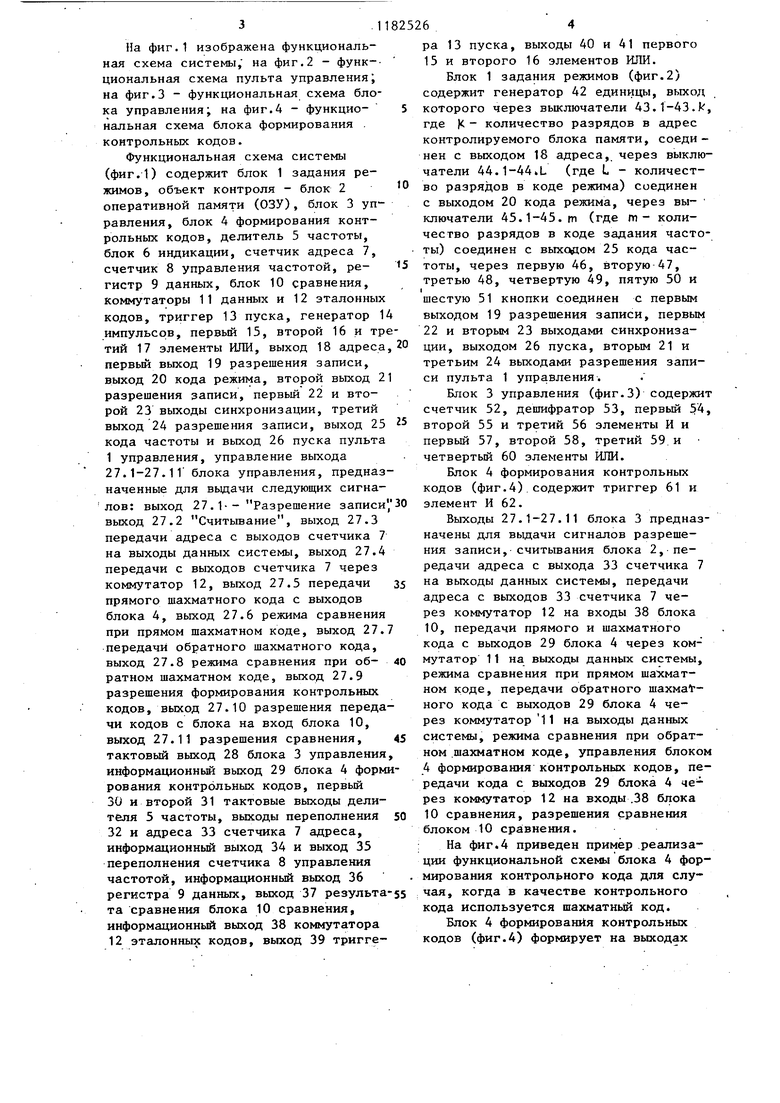

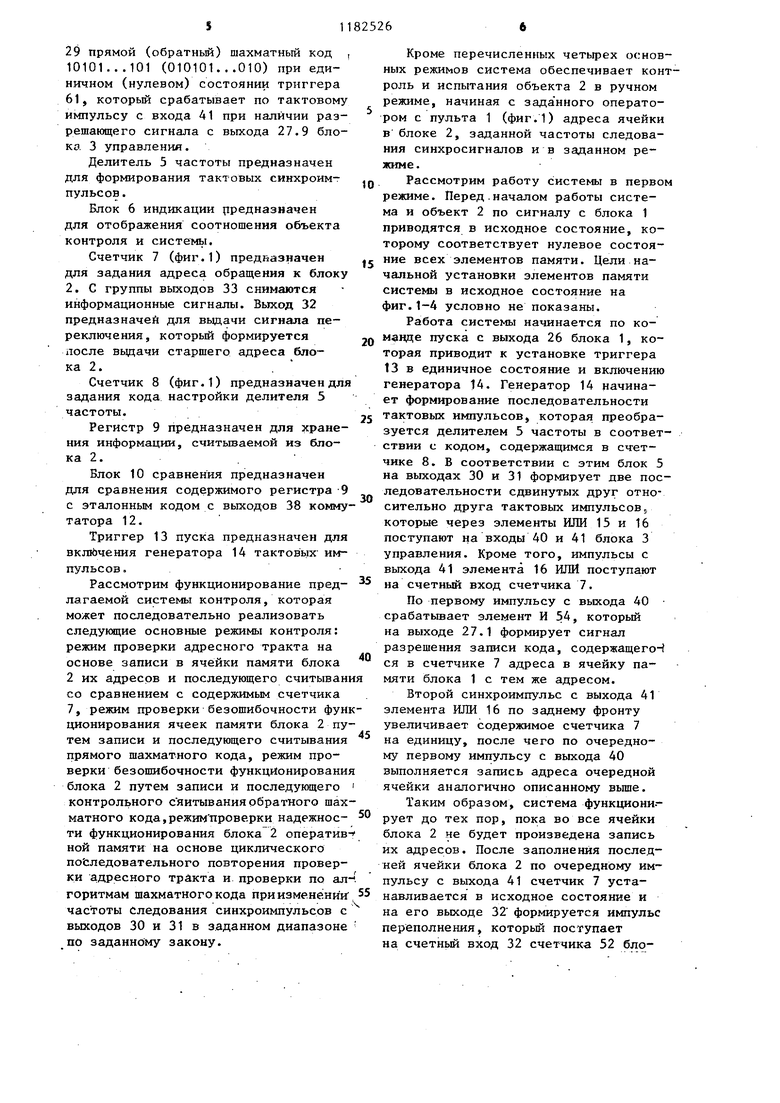

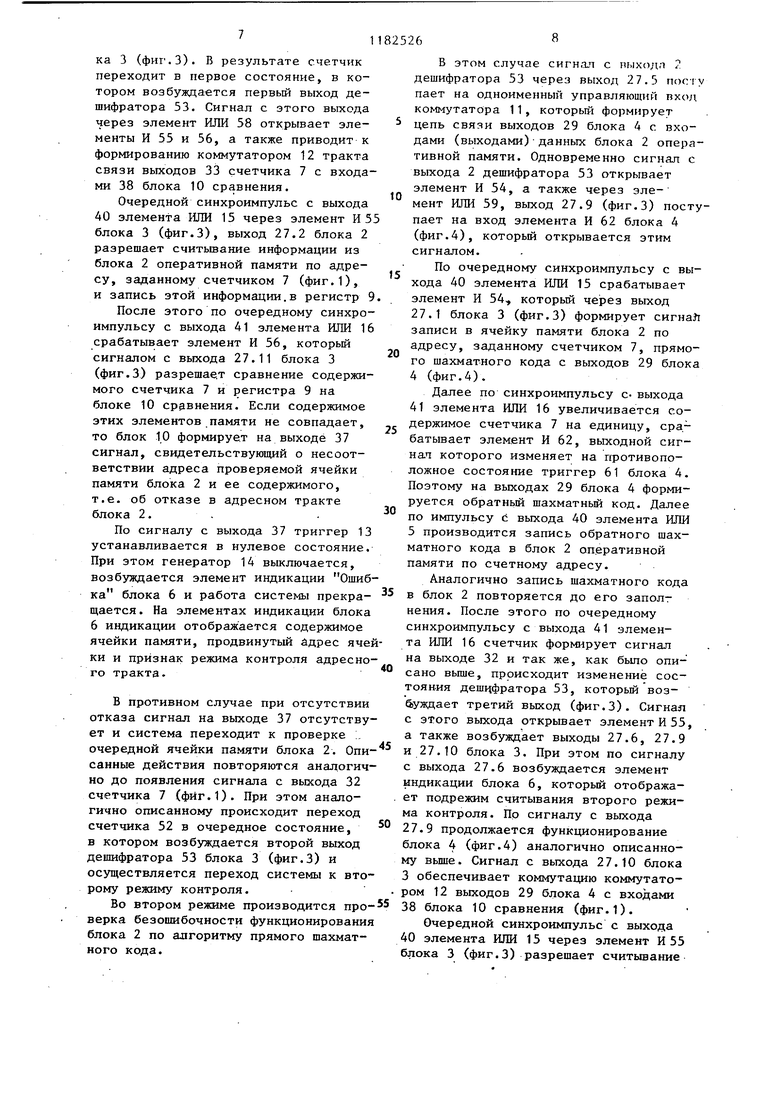

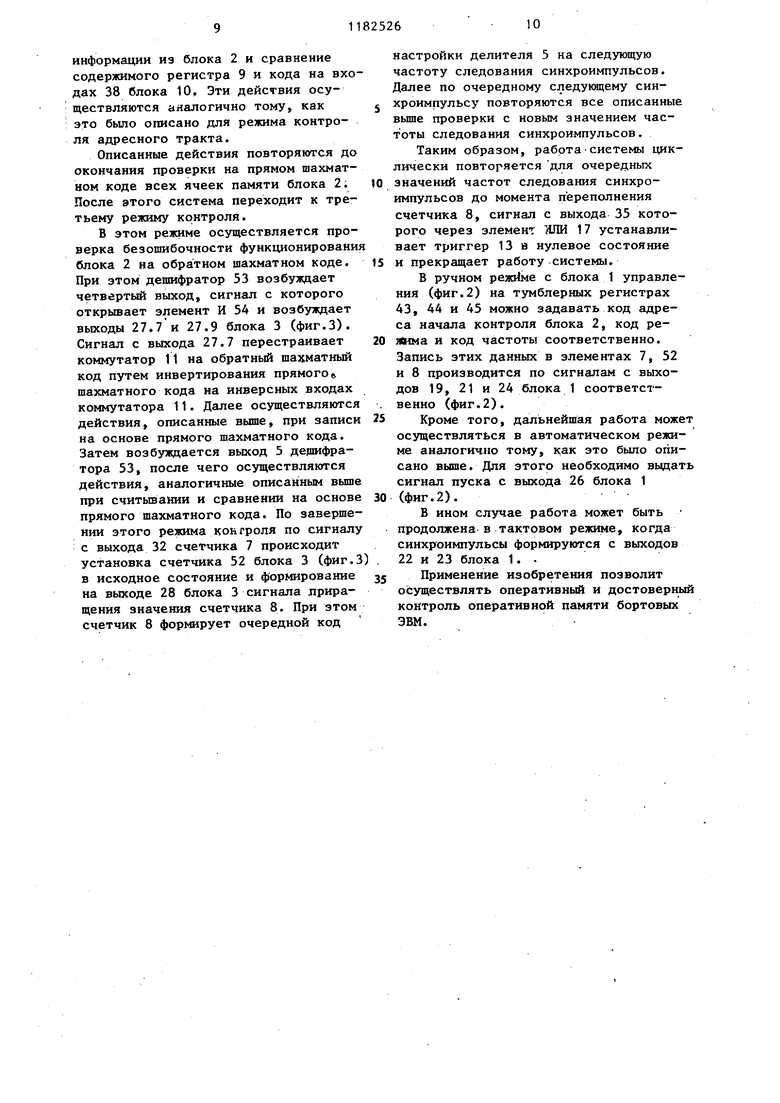

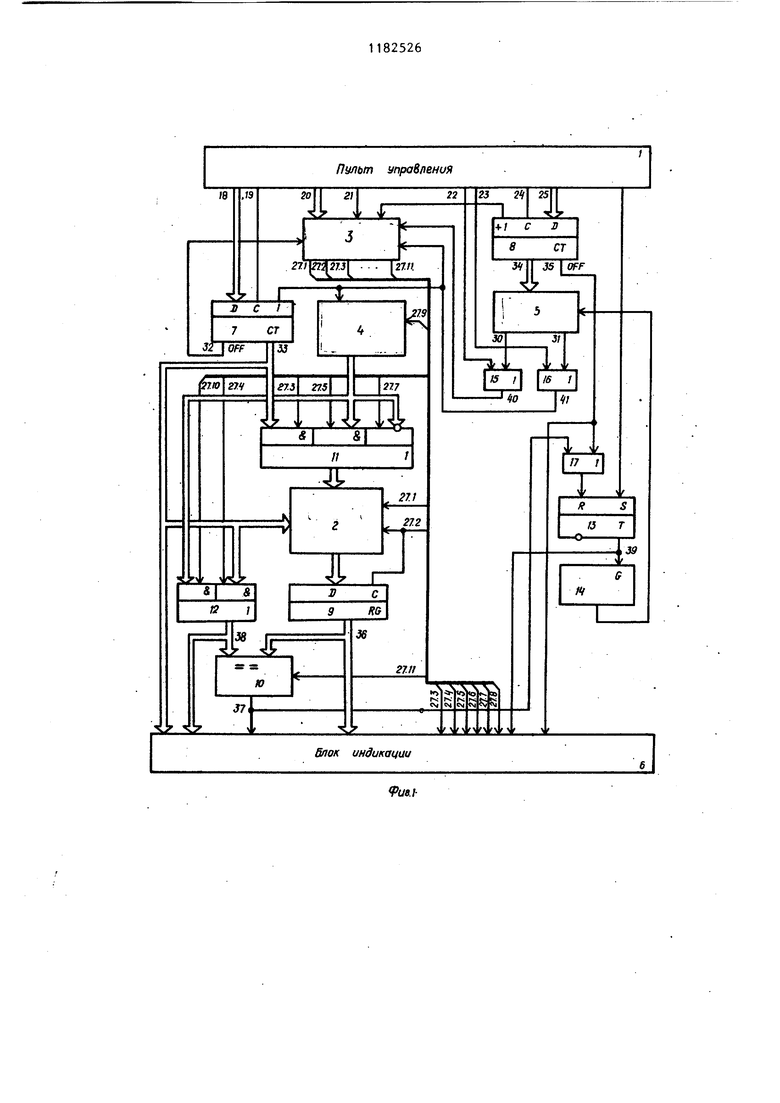

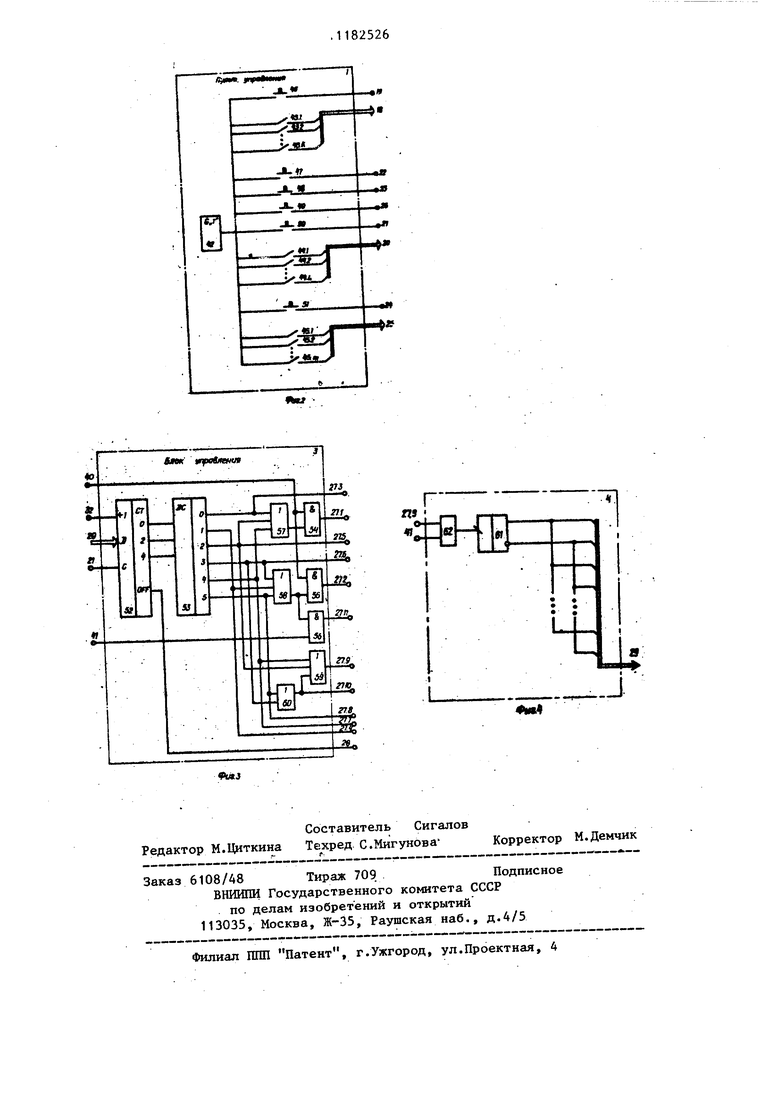

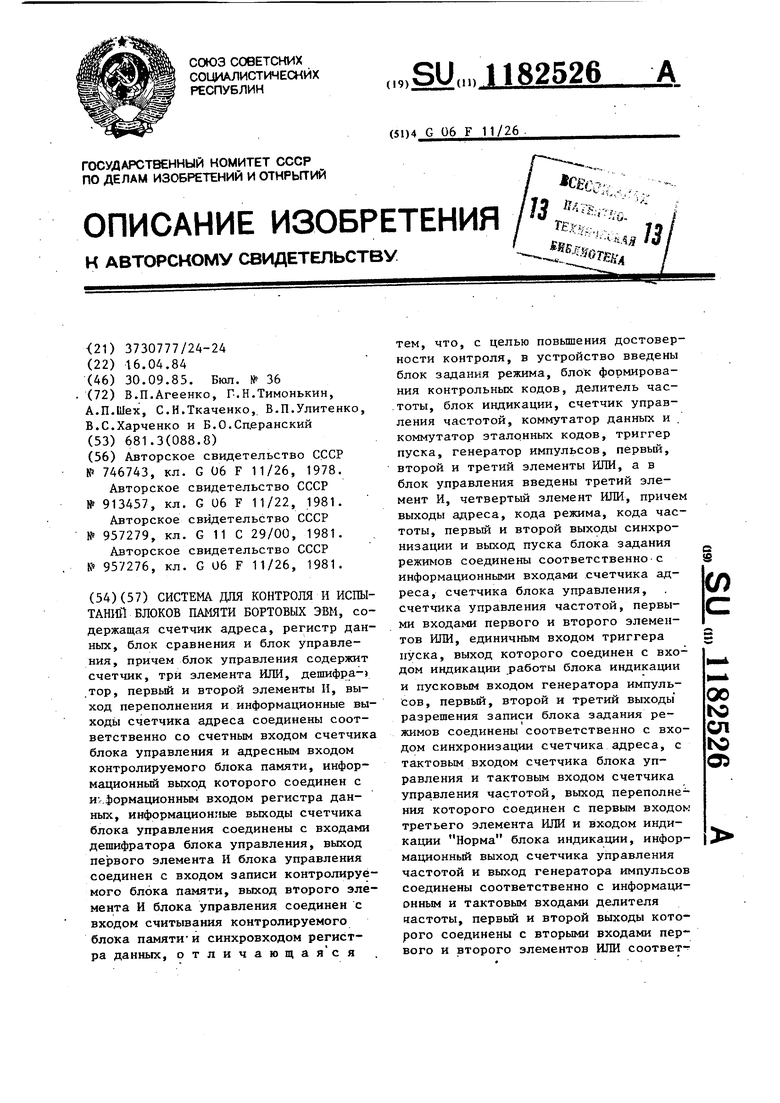

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано в радиоэлектронной промышленности в серийном производстве блоков оператив- 5, ной памяти бортовых ЭВМ, выполненных в частности на интегральных микросхемах. Целью изобретения является повышение достоверности контроля блоков оперативной памяти. На фиг.1 изображена функциональная схема системы, на фиг. 2 - функ-циональная схема пульта управления; на фиг.З - функциональная схема блока управления; на фиг.4 - функциональная схема блока формирования . контрольных кодов. Функциональная схема системы {фиг.1) содержит блок 1 задания режимов, объект контроля - блок 2 оперативной памяти (ОЗУ), блок 3 управления, блок А формирования контрольных кодов, делитель 5 частоты, блок 6 индикации, счетчик адреса 7, счетчик 8 управления частотой, регистр 9 данных, блок 10 сравнения, коммутаторы 11 данных и 12 эталонных кодов, триггер 13 пуска, генератор 1 импульсов, первый 15, второй 16 и тр тий 17 элементы ИЛИ, выход 18 адреса первый выход 19 разрешения записи, выход 20 кода режима, второй выход 2 разрешения записи, первый 22 и второй 23 выходы синхронизации, третий выход 24 разрешения записи, выход 25 кода частоты и выход 26 пуска пульта 1 управления, управление выхода 27.1-27.11 блока управления, предназ наченные для выдачи следующих сигна лов: выход 27.1-- Разрешение записи выход 27.2 Считывание, выход 27.3 передачи адреса с выходов счетчика 7 на выходы данных системы, выход 27.4 передачи с выходов счетчика 7 через коммутатор 12, выход 27.5 передачи прямого шахматного кода с выходов блока 4, выход 27.6 режима сравнения при прямом шахматном коде, выход 27. передачи обратного шахматного кода, выход 27.8 режима сравнения при обратном шахматном коде, выход 27.9 разрешения формирования контрольных кодов, выход 27.10 разрешения переда чи кодов с блока на вход блока 10, выход 27.11 разрешения сравнения, тактовый выход 28 блока 3 управления информационный выход 29 блока 4 форм рования контрольных кодов, первый 30 и второй 31 тактовые выходы делителя 5 частоты, выходы переполнения 32 и адреса 33 счетчика 7 адреса, информационный выход 34 и выход 35 переполнения счетчика 8 управления частотой, информационный выход 36 регистра 9 данных, выход 37 результа та сравнения блока 10 сравнения, информационный выход 38 коммутатора 12 эталонных кодов, выход 39 триггера 13 пуска, выходы 40 и 41 первого 15 и второго 16 элементов ИЛИ. Блок 1 задания режимов (фиг.2) содержит генератор 42 единицы, выход которого через выключатели 43.1-43.k, где К - количество разрядов в адрес контролируемого блока памяти, соединен с выходом 18 адреса, через выключатели 44. (где L - количество разрядов в коде режима) соединен с выходом 20 кода режима, через выключатели 45.1-45. m (где т- количество разрядов в коде задания частоты) соединен с выхсщом 25 кода частоты, через первую 46, вторую-47, третью 48, четвертую 49, пятую 50 и шестую 51 кнопки соединен с первым выходом 19 разрешения записи, первым 22 и вторым 23 выходами синхронизации, выходом 26 пуска, вторым 21 и третьим 24 выходами разрешения записи пульта 1 управления. Блок 3 управления (фиг.З) содержит счетчик 52, дешифратор 53, первый 54, второй 55 и третий 56 элементы И и первый 57, второй 58, третий 59. и четвертый 60 элементы ИЛИ. Блок 4 формирования контрольных кодов (фиг.4).содержит триггер 61 и элемент И 62. Выходы 27.1-27.11 блока 3 предназначены для выдачи сигналов разрешения записи,-считывания блока 2,-передачи адреса с выхода 33 счетчика 7 на выходы данных системы, передачи адреса с выходов 33 счетчика 7 через коммутатор 12 на входы 38 блока 10, передачи прямого и шахматного кода с выходов 29 блока 4 через коммутатор 11 на выходы данных системы, режима сравнения при прямом шахматном коде, передачи обратного шахматного кода с выходов 29 блока 4 через коммутатор 11 на выходы данных системы, режима сравнения при обратном .шахматном коде, управления блоком 4 формирования контрольных кодов, передачи кода с выходов 29 блока 4 че рез коммутатор 12 на входы .38 блока 10 сравнения, разрешения сравнения блоком 10 сравнения. На фиг.4 приведен пример реализации функциональной схемы блока 4 формирования контрольного кода для случая, когда в качестве контрольного кода используется шахматный код. Блок 4 формирования контрольных кодов (фиг.4) формирует на выходах 29 прямой (обратньй) шахматный код 10101,..101 (010101...010) при единичном (нулевом) состоянии триггера 61, который срабатывает по тактовому импульсу с входа 41 при наличии разрешающего сигнала с выхода 27.9 блока 3 управления. Делитель 5 частоты предназначен для формирования тактовых синхроимпульсов . Блок 6 индикации предназначен для отображения соотношения объекта контроля и системьк Счетчик 7 (фиг.1) предназначен для задания адреса обращения к блоку 2. С группы выходов 33 снимаются информационные сигналы. Выход 32 предназначей для выдачи сигнала переключения , который формируется после вьщачи старшего адреса блока 2. Счетчик 8 (фиг.1) предназначен дл задания кода настройки делителя 5 частоты. Регистр 9 предназначен для хранения информации, считьшаемой из блока 2. Блок 10 сравнения предназначен для сравнения содержимого регистра 9 с эталонным кодом с выходов 38 комму татора 12. Триггер 13 пуска предназначен для включения генератора 14 тактовых импульсов. Рассмотрим функционирование предлагаемой системы контроля, которая может последовательно реализовать следующие основные режимы контроля: режим проверки адресного тракта на основе записи в ячейки памяти блока 2 их адресов и последующего считыван со сравнением с содержимым счетчика 7, режим проверки безошибочности фун ционирования ячеек памяти блока 2 пу тем записи и последующего считывания прямого шахматного кода, режим проверки безошибочности функционировани блока 2 путем записи и последующего контрольного сяитывания обратного шах матного кода,режимпрове.рки надежноети функционирования блока 2 оператив ной памяти на основе циклического последовательного повторения проверки адресного трАкта и проверки по ал горитмам шахматного кода при изменении частоты Следования синхроимпульсов выходов 30 и 31 в заданном диапазон по заданному закону. Кроме перечисленных четырех основных режимов система обеспечивает контроль и испытания объекта 2 в ручном режиме, начиная с заданного оператором с пульта 1 (фиг.1) адреса ячейки вблоке 2, заданной частоты следования синхросигналов ив заданном режиме. Рассмотрим работу системы в первом режиме. Перед.началом работы система и объект 2 по сигналу с блока 1 приводятся в исходное состояние, которому соответствует нулевое состояние всех элементов памяти. Цели начальной установки элементов памяти системы в исходное состояние на фиг.1-4 условно не показаны. Работа системы начинается по пуска с выхода 26 блока 1, которая приводит к установке триггера 13 в единичное состояние и включению генератора 14. Генератор 14 начинает формирование последовательности тактовых импульсов, которая преобразуется делителем 5 частоты в соответствии с кодом, содержащимся в счетчике 8. В соответствии с этим блок 5 на выходах 30 и 31 формирует две последовательности сдвинутых друг относительно друга тактовых импульсов. которые через элементы ИЛИ 15 и 16 поступают на входы 40 и 41 блока 3 управления. Кроме того, импульсы с выхода 41 элемента 16 ИЛИ поступают на счетный вход счетчика 7. По первому импульсу с выхода 40 срабатьшает элемент И 54, который на выходе 27.1 формирует сигнал разрешения записи кода, coдepжaщeгo ся в счетчике 7 адреса в ячейку памяти блока 1 с тем же адресом. Второй синхроимпульс с выхода 41 элемента ИЛИ 16 по заднему фронту увеличивает содержимое счетчика 7 на единицу, после чего по очередному первому импульсу с выхода 40 выполняется запись адреса очередной ячейки аналогично описанному вьш1е. Таким образом, система функциони-рует до тех пор, пока во все ячейки блока 2 не будет произведена запись их адресов. После заполнения последней ячейки блока 2 по очередному импульсу с выхода 41 счетчик 7 устанавливается в исходное состояние и на его выходе 32 формируется импульс переполнения, которьш поступает на счетный вход 32 счетчика 52 блока 3 (фиг.З). В результате счетчик переходит в первое состояние, в котором возбуждается первый выход дешифратора 53. Сигнал с этого выхода через элемент ИЛИ 58 открывает элементы И 55 и 56, а также приводит к формированию коммутатором 12 тракта связи выходов 33 счетчика 7 с входами 38 блока 10 сравнения. Очередной синхроимпульс с выхода 40 элемента ИЛИ 15 через элемент И 55 блока 3 (фиг.З), выход 27.2 блока 2 разрешает считьшание информации из блока 2 оперативной памяти по адресу, заданному счетчиком 7 (фиг.1), и запись этой информации.в регистр 9 После этого по очередному синхроимпульсу с выхода 41 элемента ИЛИ 16 срабатывает элемент И 56, который сигналом с выхода 27.11 блока 3 (фиг.З) разрешает сравнение содержимого счетчика 7 и регистра 9 на блоке 10 сравнения. Если содержимое этих элементов памяти не совпадает, то блок 10 формирует на выходе 37 сигнал, свидетельствующий о несоответствии адреса проверяемой ячейки памяти блока 2 и ее содержимого, т.е. об отказе в адресном тракте блока 2. По сигналу с выхода 37 триггер 13 устанавливается в нулевое состояние. При этом генератор 14 выключается, возбуждается элемент индикации Ошиб ка блока 6 и работа системы прекращается. На элементах индикации блока 6 индикации отображается содержимое ячейки памяти, продвинутый йдрес яче ки и признак режима контроля адресно го тракта. В противном случае при отсутствии отказа сигнал на выходе 37 отсутству ет и система переходит к проверке очередной ячейки памяти блока 2. Опи санные действия повторяются аналогично до появления сигнала с выхода 32 счетчика 7 (фйг.1). При этом аналогично описанному происходит переход счетчика 52 в очередное состояние, в котором возбуждается второй выход дешифратора 53 блока 3 (фиг.З) и осуществляется переход системы к второму режиму контроля. Во втором режиме производится проверка безошибочности функционирования блока 2 по алгоритму прямого шахматного кода.

Очередной синхроимпульс с выхода 40 элемента ИЛИ 15 через элемент И 55 блока 3 (фиг.З) разрешает считывание В этом случае сигнал с пыход-т дешифратора 53 через выход 27.5 посчу пает на одноименный управляющий пх(д коммутатора 11, который формирует цепь связи выходов 29 блока 4 с входами (выходами) данных блока 2 оперативной памяти. Одновременно сигнал с выхода 2 дешифратора 53 открывает элемент И 54, а также через элемент ИЛИ 59, выход 27.9 (фиг.З) поступает на вход элемента И 62 блока 4 (фиг.4), который открывается этим сигналом. По очередному синхроимпульсу с выхода 40 элемента ИЛИ 15 срабатывает элемент И 54, который через выход 27.1 блока 3 (фиг.З) формирует сигнал записи в ячейку памяти блока 2 по адресу, заданному счетчиком 7, прямого шахматного кода с выходов 29 блока 4(фиг.4). Далее по синхроимпульсу с- выхода 41 элемента ИЛИ 16 увеличивается содержимое счетчика 7 на единицу, сра.батывает элемент И 62, выходной сигнап которого изменяет на противоположное состояние триггер 61 блока 4. Поэтому на выходах 29 блока 4 формируется обратный шахматньй код. Далее по импульсу с выхода 40 элемента ИЛИ 5производится запись обратного шахматного кода в блок 2 оперативной памяти по счетному адресу. Аналогично запись шахматного кода в блок 2 повторяется до его заполт нения. После этого по очередному синхроимпульсу с выхода 41 элемента ИЛИ 16 счетчик формирует сигнал на выходе 32 и так же, как было описано выше, происходит изменение состояния дешифратора 53, который возбуждает третий выход (фиг.З). Сигнал с этого выхода открывает элемент И 55, а также возбуждает выходы 27.6, 27.9 и 27.10 блока 3. При этом по сигналу с выхода 27.6 возбуждается элемент индикации блока 6, который отображает подрежим считывания второго режима контроля. По сигналу с выхода 27.9 продолжается функционирование блока 4 (фиг.4) аналогично описанному вьше. Сигнал с выхода 27.10 блока 3 обеспечивает коммутацию коммутатором 12 выходов 29 блока 4 с входами 38 блока 10 сравнения (фиг.1).

информации из блока 2 и сравнение содержимого регистра 9 и кода на входах 38 блока 10, Эти действия осуществляются аналогично тому, как это было отшсано для режима контроля адресного тракта.

Описанные действия повторяются до окончания проверки на прямом шахматном коде всех ячеек памяти блока 2; После этого система переходит к третьему режиму контроля.

В этом режиме осуществляется проверка безошибочности функционирования блока 2 на обратном шахматном коде. При этом дешифратор 53 возбуждает четвертый выход, сигнал с которого открывает элемент И 54 и возбуждает выходы 27.7 и 27.9 блока 3 (фиг.З). Сигнал с выхода 27.7 перестраивает коммутатор 11 на обратньй шахматный код путем инвертирования прямого шахматного кода на инверсных входах коммутатора 11. Далее осуществляются действия, описанные выше, при записи на основе прямого шахматного кода. Затем возбуждается выход 5 дершфратора 53, после чего осуществляются действия, аналогичные описанным вьш1е при считывании и сравнении на основе прямого шахматного кода. По завершении этого режима контроля по сигналу с выхода 32 счетчика 7 происходит установка счетчика 52 блока 3 (фиг.З в исходное состояние и формирование на выходе 28 блока 3 сигнала лркращения значения счетчика 8. При этом счетчик 8 формирует очередной код

настройки делителя 5 на следующую частоту следования синхроимпульсов. Далее по очередному следующему синхроимпульсу повторяются все описанные вьш1е проверки с новым значением частоты следования синхроимпульсов.

Таким образом, работасистемы циклически повторяется для очередных значений частот следования синхроимпульсов до момента переполнения счетчика 8, сигнал с выхода 35 которого через элемент ИЛИ 17 устанавливает триггер 13 в нулевое состояние и прекращает работу системы.

В ручном режиме с блока 1 управления (фиг.2) на тумблерных регистрах 43, 44 и 45 можно задавать код адреса начала контроля блока 2, код режима и код частоты соответственно. Запись этих данных в элементах 7, 52 и 8 производится по сигналам с выходов 19, 21 и 24 блока 1 соответственно (фиг.2).

Кроме того, дальнейшая работа може осуществляться в автоматическом режиме аналогично тому, как это было описано выше. Для этого необходимо выдат сигнал пуска с выхода 26 блока 1 (фиг.2).

В ином случае работа может быть продолжена в тактовом режиме, когда синхроимпульсы формируются с выходов 22 и 23 блока 1. .

Применение изобретения позволит осуществлять оперативный и достоверны контроль оперативной памяти бортовых ЭВМ.

| Запоминающее устройство с автономным контролем | 1978 |

|

SU746743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 913457, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957276A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-16—Подача