1

Пзобретенне относится к радиотех.пике и предназначено для использования в широкодиапазонных приемниках и анализаторах спектра с автоматическо перестройкой по частоте, осуществляемой с помощью элементов электронной перестройки, например вариканов, емкость которых зависит от величины приложенного к ним управляющего напряжения.

Цель изобретения - расширение фунциональных возможностей путем обеспечения возможности раздельного управления напр яжениями на двух выходах, благодаря чему достигается возможность лучшего сопряжения с цепями устройств, подключаемых к выходу.

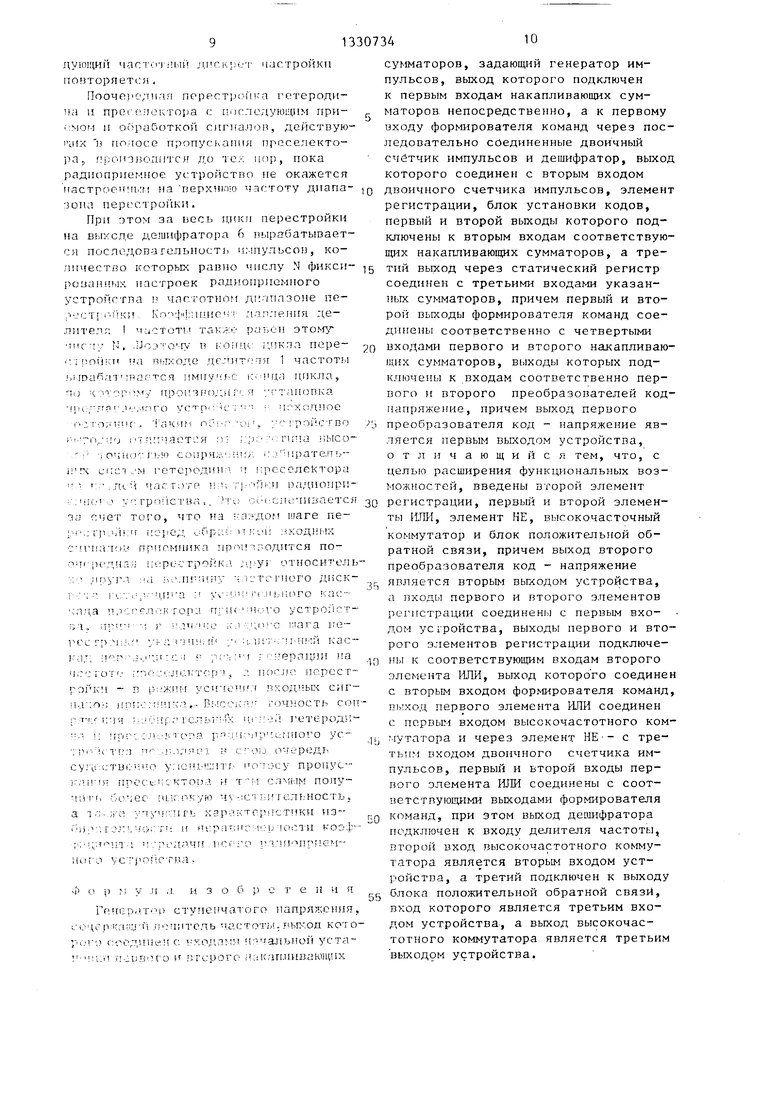

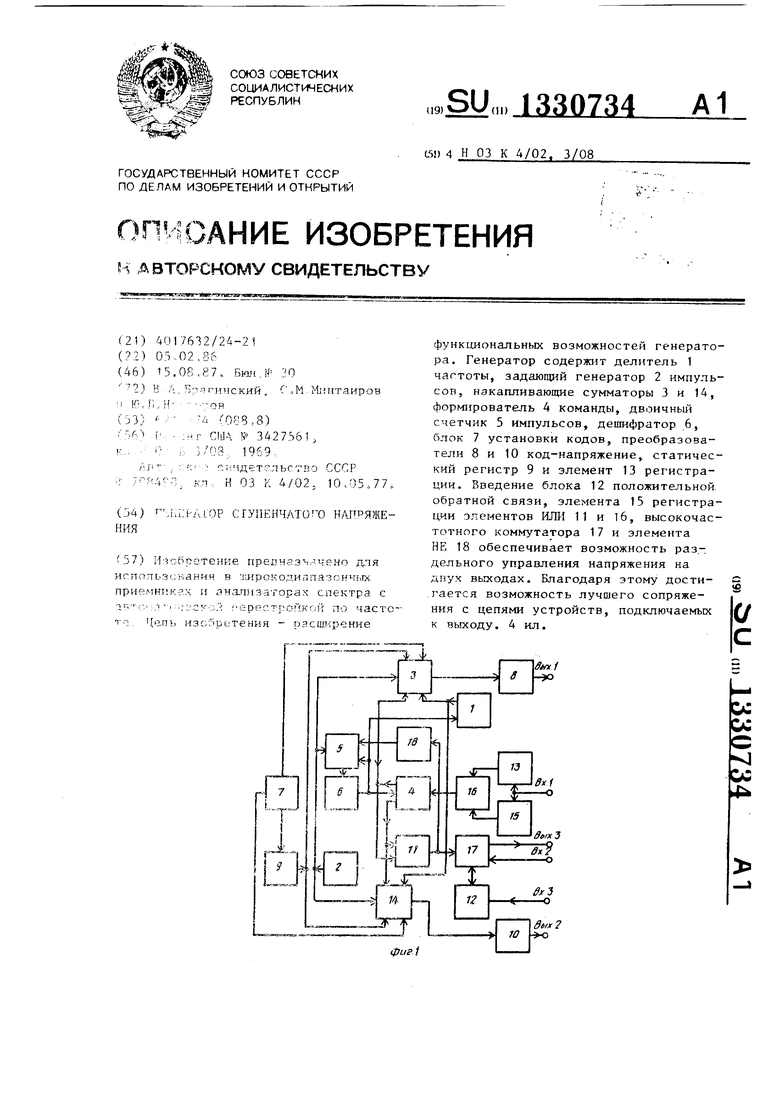

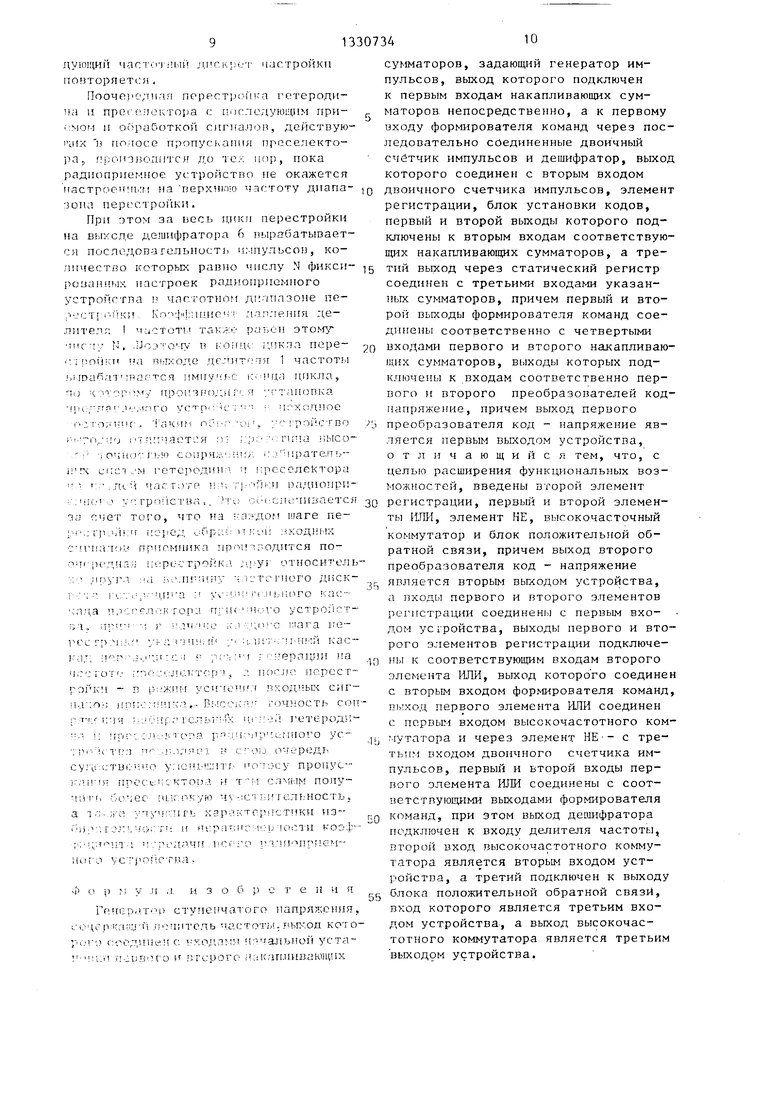

На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока установки кодов; на фиг.3 а,б - принципиальные схемы усилительного каскада преселектора и блока положительной обратной связи соответственно: на фиг.4 - временные диаграммы, поясняющие принцип работы устройства.

Устройство СФИГ.1) содержит делитель 1 частоты, задающий генератор

1

2 импульсов, первый на.капливающ1}й сумматор 3, формирователь 4 команд, двоичньш счетчик 5 импульсов, дешифратор 6, блок 7 установки кодов, первый преобразователь 8 код - напряжение, статический регистр 9, второй преобразователь 10 код - напряжение первьп 3Jicf.CHT 11 ИЛИ, блок 12 положительной обратной связи, первый 13 регистрации, второй накап ливашицп сумматор 14, второй элемент 15 регистрации, второй элеме1 Т 16 ИЛИ высокочастотный коммутатор 17 и элемент 18 НЕ. I

Выход задающего генератора 2 подключен к первым (тактируюиц1м) входам накапливаютцих ;умматоров 3 и 14 непосредственно, а к перво -г, входу формирователя 4 через последовательно соединенные двоичный счетчик 5 и дешифратор 6,выход которого связан с вторым входом (входом обнуления) двоичного счетчика 5 и входом делителя 1. Первый и второй выходы блока 7 под1спючены к вторым входам накапли

ваюищх сумматоров 3 и 14 соответствен-55 формирователя 4. Соединенные между но, а третий выход - к входу стати- собой вход счетного триггера и вход ческого регистра 9, выход которого установки нуля статического триггера соединен с третьими входами накапли- служат вторым входом формирователя 4, ваю1цих сумматоров 3 и 14. Первьш и первым входом которого является вход

30

35

40

,

503307342

второй выходы форьшрователя 4 связаны с четвертыми входами соответственно первого и второго накапливающих сумматоров 3 и 14, а также с соответствующими входами первого элемента 11 ИЛИ, выход которого соединен с первым управляющим входом коммутатора 17 и через элемент 18 НЕ - с тре 1Q тьим (управляющим) входом двоичного счетчика 5. Выход первого накапливающего сумматора 3 подключен к входу преобразователя 8, выход которого является первым выходом устройства.

15 Выход второго накапливающего сумматора 14 соединен с входом преобразователя 10, выход которого служит вто- рым выходом устройства. Соединенные между собой входы элементов 13 и 15

2Q регистрации являются первым и входом устройства, а выходы этих элементов связаны с соответствующими ВХОДАМИ второго элемента 16 ИЛИ, выход которого подключен к второму входу фор-и

25 мирователя 4. Выход делителя 1 соединен с входами начальной установки накапливающих сумматоров 3 и 14. Выход коммутатора 17 является третьим выходом устройства, второй вход - вторым входом устройства, а третий вход связан с выходом блока 12, вход которого служит третьим входом устройства.

Первьш и второй выходы устройства подключаются к управляющим входам перестройки гетеродина и преселектора радиоприемника соответственно. Третий выход устройства подключается к сигнальному входу усилительного каскада, используемого для целей автоматической перестройки и сопряжений избирательных цепей гетеродина и преселектора. Выход указанного усилительного каскада связан с третьим входом устройства. Первый вход устройства соединен с выходом смесителя, а второй вход - с выходом той части преселектора, которая предшествует указанному усилительному каскаду.

45

Формирователь 4 команд состоит из ститического и счетного триггеров, прямые выходы которых являются соответственно первым и вторым выходами

установки единицы стати itLKi.u гчи: гера.

Элементы ГЗ и 15 perHf,T)aii,riii -IK тоят из иослг-л вательно с оединь яшлх усилителя- i:; раничителя, полосоги:. ( ., фиш.тра, детектгфа ог ибакщей, трш - гера Шмид га, дифференцирующе;; ил ии и одностороннего усилителя- ограни чителн. Частоты настроек полосооых фильтр1Л ц элг;ментах 13 и 15 рег ист рации оппеделяются как f|, f f . оотпетственно, где f - зничени ; прог.ежуточной частоты приемного устройства; л - величина дискрета пег. -;стройки. Вхс1дами элемс-иток 13 и 15 регистрации являются 1 ХС Ц1Л соответствующих симме Г рн.:- л ь.х ; ( p vii телей oгpaничитeJ . :,, . :v.: .-- : выходы соответстг / ,; : . ::. г. усилителей .граги;- :

Блок 7 уиганол ки -.с; .в (ф1- г,2) 1УЖИТ .р: -|Н;:ова1-1Т 1 . ..ir /-п-П::/ .

: Г: ОД,ОН НаЧ-Л,:: Ь

кл н/): . , :::;: . i- ,: . -

код, rj IL ,:::с.|птя . Г Э ТИЧеС1 .i; , р;-- ::::

... . лч;н liCVNVB ;. .;:1 ;л ii;:rD,;;-ii i .Г- ..;. ;;- i .. - 9 ;: 20., че- ir.-; о чьгм ;;та 2 i у.- .ч. - ния (ча;т Ч i -- члпки), эль1.:.::.; ;:.: и 23 110р№1Г- --пания уро ней л,-- -i-i :) :i го пул-. .: jijpHHf-L -; .: сд - U- , ; . элемента 24 пода13 лени : др .изэгй( J;i;- менты 22 и 2 форлирс-пя , ,;. оi.-.F и логическ 1Г : Чуля и л :. - :;лии,

ПОДКЛЮ ТСЧЬ; к СС ТПетСТ :- -: и;Л;ОЛ1)

злементор v --- Пл ,-П . : г ч . л го элемент а 21 через л ;-; ;К : /ч .

СЛЮЧСГ 5 П) .i lCi . f l ч -; - . :

регис- рсв :: И 20, г также per icrpa 9. Выход -. остальных Tpei: элементов 21 управления через элементы 2А подключены к вторым тактирующим входа (входам сдвига) регистров 19 и 20 и регистра 9. Выходы разрядов регистров 19 и 20 образуют первый и второй информа 1ионные выходы блока 7, Тр;е тий (информационный) выхо,, Ojiorra , вклю -и. П..1.-.ОДЫ 2,

KOl Opl e j .;: ;:ifcl i ЛС Гг: ГСТЕУЮПИХ -,;; , ЛанТТ; . :п;. С,е ДК -ЧЮ7 - V

nH h -.-; .jt-i : тактируюин-а й FJ.. (: и с т : т ( -. е к о г о р е г и с р -i

Вл ,;; , 2 1Э..1С га-;тельной обрать-.;-- iri с - значен для перевода ;.: р1тельк ,г / н-гскада з преселекторе г. аль огч: ;1.:-мьг;;го устройства Е f r. i гем включения блока 1 г;-:; : ду оходоп к усш:итагтькогс

.каскада через вп сокочаг; i отнь.и комм- Т гор , Структура блока 12 определяе ;:я т:1пом и-люпьзуемого усилительного |:;- Скада преселек тора .

г1а фиг , За пре дг. г; nrit 1л одна из ьС Зможных npHHiyiniiaj7bHfc:x -- JieKTpHHec К)х схем усилитель.чого каскада пред L 1 : «ля1Г 1;(еги глыбой электронно-перестр иваетфи } резонансный ус1 аитель на тразисторе включен : 17: I хемь- с общей базой.

На фиг,Зб показана принципиальная блока 12, Включение- блока 12 входом и выходом указанного усилительного каскада обеспечивает тoJ yчeниe на его основе электронно- перестраиваемого генератора, собран- .:: по схеме е -1костной трехточки, . i ,тота г енерации при этом задается ;;1-зоь ансной частотой контура, (збра- , ; энного индуктивностью L и емкостью лсрсменная составляющая котс)рой опре- .;. емкостью парикапа V2 (фиг. За :М., котрсиные Bapi : ,;T:.i построения эле i. - HTOB 13 и 5 регистрации,, делителя : ч. С готы, блока 7 у,.-тановки кодов

блока 1 2 не яв7 -1:о1ся единственны о1, :1Яниг ;)ОУТл ОТ технических требова- :- :;i v испопьзуемол зпеме1 тной базы и /: ;г-- : г л ;.Д1-11;ГХ данных ;чг)гут быть н-;: .пЙН1- iiifbic г ути пс:Сгроения указан-- -гп- узлов,. Например, элементы 13 и 15 : :1 пстрацг. 1 1 мог ут бь ть выполнены в У:;... ;..1;1фро1зы ; изь еркте,1ей частоты вы- .го сигнала смесителя,

.- стройство работает следующим обГ: -. J О . г

.j начало;. рлоэть: F статические ,: лсгры 19 и 2G блока 7 заносятся к У1Ы начальной установки накапливаю- U;H:V сумматоров 3 и 14, а в регистр 9 - код приращения; Запись кодов в статические регистры 19 и 20 блока 7 и Е статический регистр 9 производит- ; .. последовательным вьодои указанных

л.ов со стороны с i арших разрядов ,-эс Т5етствующ1-гх регистров г Для этого ; информационном входе регистра с ::;ющью соответствующего элемента 21 устанавливается требуемый уровень мапрЯукения (логического нуля или ло- уу ческой единицы) после чего произ- ;. и-тся сдвиг информации из старших ;,-: рядов регистра в соседние младшие Г аряды с помощью элемента 21 нинр подключенного к тактирующему . --ДУ регистра через элемент 24 по- г. Бления дребезга,.

в начале каждого гцичла перестройки двоичный счетчик 5 и де:пггель 1 обнуляются, а в накапливающие сумматоры 3 и 14 из регистров 19 и 20 блока 7 через соотпетствуюац1е информационные 5 входы записываются коды начальной установки . Обнуление двоичного счетчика 5 производится по каждому выходному импульсу дешифратора 6.

Для записи кодов начальной установ- К1 в накагтливаюп ие сумматоры 3 и 14 и( пользуе ся параллельный способ передачи кодов из статических регистров 19 и 20 блока 7 в сумматоры 3 и 14. Запись кодов начальной установки в -5 сумматоры 3 и 14 производится импульсом, поступающим с вькода делителя 1 на начальные входы установки указан- HfcK сумматоров.

Запись кодов начальной установки 20 в накапливающие сумматор1 1 3 и 14 обеспечивает появление на выходе преобразователя 8 напряжения, при котором

гетеродин приемного устройства оказы 25

1330734 6

Таким образом, на интервале нремени

наетси

тоту Г,

10 напряжения,

настроенным на ег о нижнюю час- а на выходе преобразователя при KoiopoM преселекTO (см.фиг.4), в течение происходит заполнение счетчика 5 импульсами с генёраГора 2, производится прием и обработка входных сигналов приемного устройства на нижней частоте диапазона поиска.

После прохождения заданного числа импульсов генератора 2 на вход счетчика 5 на выходах разрядов этого сче чика формируется параллельный код, обеспечивающий срабатывание дешифратора 6, на выходе которого вырабатывается импульс (фиг.4ж). Под действием этого импульса двоичный счетчик 5 обнуляется, а счетный триггер формирователя 4 команд устанавливает ся в единичное состояние, что приводит к появлению разрешающих потенциалов на втором вькоде формирователя 4 команд и на выходе первого элемента 11 ИЛИ (фиг.4в и д соответственно а также запрещающего потенциала на вькоде элемента 18 НЕ (фиг.4е). При этом в первом накапливающем супмато- ре 3 под действием тактирующих импульсов, поступающих на его первый вход с выхода генератора 2, в каждом такте происходит cyMNmpoBanne кода, записанного в сумматоре 3, с кодом приращения, хранящимся в статическом регистре 9. Состояние счетного триггера формирователя 4 команд остается неизменным, что обеспечивае сохранение запрещающего потенциала на четвертом входе второго накапливающего сумматора 14 и препятствует изменению кода в сумматоре 14, а так же изменению выходного напряжения нреобразователя 10 и частоты настрой ки избирательных цепей преселектора ((|1иг.4б, диаграмма 2).

ГО15 niu eM4in a оказь ается па 1 пжню;о частоту сигнала ;тиа граммы 1

г

настрренны „Р(фиг.4б 2 соо глГ ТгтЕ енно) .

гатическпи и cqt-Tinin триггеры в Ориироватсле 4 устапа .ливаются в нуЛГ- ТлОС состояние, ГЦ ИВОДИТ к ПОЯВ , 1 1М НОрВОМ I: Г ТОРОН ВЫХОДаХ фор

MHT otia геля 4 i; nep ioi o элемента 11 ИЛИ заг1пе1ЦЛ1 гц 1х потенциалов (фиг.4в, г п д соответственно), а на выходе элемента 18 ill-; единичного потенциала (.4е), разрешающего поступления и - пульсов с зада 01:1его генератора 2 (фи.4а) на уход двоичног о c4CT4iiKa 5. Иаппчпе aanpeiuaiui ero потенн,иа. 1а ia В1,;ходе элемента 1 1 ГПИ, поступаюш.его на первый (управляющий) нход ком утатора 17, лызыпает подключение входа усилительного каскада в проселек гчпре к выходу предшествую- атей части н.реселектора. Поступление :, n pc:ina}oi:tnx потенциалов с первого и -.-,рого пькодоп формирователя 4 на Чч1ТВР|1тые входы соответственно первого 3 и второго 14 накашн1вашщих сумматоров 3 и 14 предотвращает изменение кода сумматоров, а следовательно, и изменение выходных напряжений преобразователей 8 и 10. При згом частоты настроек преселектора и гетерод П1а остаются неизменными.

-5

0

5

0

0

5

с

0

5

TO (см.фиг.4), в течение происходит заполнение счетчика 5 импульсами с генёраГора 2, производится прием и обработка входных сигналов приемного устройства на нижней частоте диапазона поиска.

После прохождения заданного числа импульсов генератора 2 на вход счетчика 5 на выходах разрядов этого счетчика формируется параллельный код, обеспечивающий срабатывание дешифратора 6, на выходе которого вырабатывается импульс (фиг.4ж). Под действием этого импульса двоичный счетчик 5 обнуляется, а счетный триггер формирователя 4 команд устанавливается в единичное состояние, что приводит к появлению разрешающих потенциалов на втором вькоде формирователя 4 команд и на выходе первого элемента 11 ИЛИ (фиг.4в и д соответственно), а также запрещающего потенциала на вькоде элемента 18 НЕ (фиг.4е). При этом в первом накапливающем супмато- ре 3 под действием тактирующих импульсов, поступающих на его первый вход с выхода генератора 2, в каждом такте происходит cyMNmpoBanne кода, записанного в сумматоре 3, с кодом приращения, хранящимся в статическом регистре 9. Состояние счетного триггера формирователя 4 команд остается неизменным, что обеспечивает сохранение запрещающего потенциала на четвертом входе второго накапливающего сумматора 14 и препятствует изменению кода в сумматоре 14, а также изменению выходного напряжения нреобразователя 10 и частоты настройки избирательных цепей преселектора ((|1иг.4б, диаграмма 2).

Появление разрешающего потенциала на первом входе высокочастотного коммутатора 17 обеспечивает подключение входа соответствующего усилительного каскада в преселекторе через коммутатор 17 к выходу блока 12, соединенного входом с выходом указанного усилительного каскада. При этом усилительный каскад переводится в режим генерации на частоте преселектора. Последовательное нарастание кода.в каждом такте приводит к ступенчатому изменению напряжения на выходе преобразователя 8, что вызывает CTyneH iaToe нарастание частоты гетеродина приемного устройства ( фиг.4б, диаграмма 1)

и сигнала разноатной частоты, выделяемого на выходе смесителя радиоприемного устройства и поступающего на вхо ды элементов 13 и 15 регистрации. Поскольку частоты настроек полосовых фильтров в элементах 13 и 15 регистра ции равны, соответственно f f , Ь , то выходной сигнал смесителя, выходя из полосы пропускания фильтра в элементе 13, попадает в полосу пропускания фильтра в элементе 15 (фиг.1а). Выходной импульс элемента 15 через второй элемент 16 ИЛИ поступает на второй вход формирователя 4 и вызывает установку статического триггера в формирователе 4 в нулевое состояние, а счетного триггера - в единичное. При этом на четвертом входе первого накапливающего сумматора 3 устанавливается запрещающий потенциал, а на четвертом входе второго накапливающего сумматора 14- разрешающий (фиг.4в иг) Нарастание кода первого накапливающего сумматора 3 приостанавливается, и увеличение выходного напряжения преобразователя 8 прекра1цается, что приводит к остановке перестройки гетеродина радиоприемного устройства (фиг,4б, диаграмма 1). В то же время под действием тактирующих импульсов, поступающих на первый вход второго накапливающего сумматора 14, в каждом такте происходит суммирование кода сумматора 14 с кодом приращения, хранящимся в регистре 9. Последовательное нарастание кода в каждом такте вызывает ступенчатое увеличение выходного напряжения преобразователя 10, что приводит,к ступенчатому нарастанию частоты настройки всех избирательных цепей пресе- лектора, в который входит используемый усилительньм каскад (фиг.46, диаграмма 2). Поскольку на выходе первого элемента 11 ИЛИ сохраняется напряжение логической единицы (фиг.4д), то используемьй усилительный каскад пре- селектора остается охваченным положительной обратной связью с помощью блока 12 через коммутатор 17 и про.должает работать в режиме генератора на частоте настройки преселектора. Ступенчатое нарастание частоты выходного сигнала усилительного каскада, работающего в режиме генерации вызывает ступенчатое уменьшение часто П ы выходного сигнала смесителя. Таким образом, указанный сигнал, переходя из полосы пропускания фильтра в элементе 15 в полосу пропускания фильтра в элементе 13 вызывает формирование импульса на выходе элемента 13 (фиг.4и). Поступление этого импульса через второй элемент 16 1ШН на второй вход формирователя 4 приводит к установке счетного триггера в формирователе 4 в нулевое состояние (фиг.4в). Состояние статического триггера в формирователе 4 при этом не меняется (фиг.4г). На выходе первого элемента 11 ИЛИ устанавливается нулевой (запрещающр;й) потенциал, а на выходе элемента 18 FiE - единичный (разрешающий) (фиг.4д и е соответственно).

0

5

0

5

0

5

0

5

Появление запрещающего потенциала на первом управляющем входе коммутатора 17 вызывает отключение выхода блока 12 от входа усилительного каскада преселектора и перевод этого каскада в его основной режим работы- режим усиления входных сигна.пов радиоприемного устройства в полосе пропускания преселектора. Таким образом, как гетеродин, так и преселектор радиоприемного устройства оказываются перестроенными на величину дискрета перестройки по Сравнению с предшествующим шагом, при этом разность частот насгроек гетеродина и преселектора равны промеждуточной частоте f . Действие разрешающего потенциала на четвертом входе двоичного счетчика 5 обеспечивает накопление в счетчике 5 тактирующих импульсов, В течение времени накопления в счетчике 5 импульсов генератора 2 производится прием входных сигналов радиоприемного устройства на данном частотном дискрете настройки. Поступление на счетный вход двоичного счетчика 5 заданного количества импульсов приводит к появлению на выходе дешифратора 6 импульса (фиг,4ж). Под дейс- трием этого импульса двоичньп1 счетчик 5 обнуляется, статический триггер формирователя 4 команд устанавливается в единичное состояние, а используемый усилительный каскад преселектора переводится в режим генерации сигнала на частоте настройки избирательных цепей преселектора. После этого процесс последовательной перестройки гетеродина и преселектора радиоприемного устройства на еле9

МС1 ПС- Г

1

дующи) qacTO j iniU ;u ci pL-T аастронки повторяется.

1ооче1 С ;п1пл nepecT)jofii:a г е те род lia и npcco- ieiiTOiJa с пислсдукидим при- .:;мог.1 и обработкой слгиал зи, действую I uix и поносе пропускания прсселекто- ра, произ}5одптся до тех пор, пока радиоприемное устройство пе окажется иастроенмып яа верхнюю частоту диапазона пер(н л-ройки.

При этом за весь цию перестройки а выксде де иифратора 6 вырабатывается последовагельиость импульсов, ко

личество которых равно числу N фнкси- g тий выход через статический регистр

роааниых настроек радиоприемпого устройстпа i частотном Д1: 1пазоне пе- vjcT i iiKH Кп чЬфипцсч ллрления де- лител;; мастоть такяо p. jbCTi TiTc-iy N. JJoD O -ry в конце ;;пкла пере- /rpoiiKu а иьгеоде де, ит- -ТЯ I частот 1 1)1 юиб;п гвиатся имиу ьс ,:) к: тор у iipomt fi;;n: 1( I jf: ..inro устр

Г ст олlinГ , ( акпм пГ:-г - 7(.: i j мл;:чаотоя п;

- i04H(:K-i bw conp i;;v: сг:с 1. М 1 стсродии:1 ;: . та и час тотр л-и ; -:чкяо громс гва :. та счет того, что на : ус,: гр:.1И1:ч г;о11ед оОри- смгпалоу

очс leruia;

ца цикла, п апопка

ПГ ХС Д Ое 4)1 . У ГроЙСТВО

гуу : : типа иысо- i: :Ум ратеп - ирсселеКтора |-т:П :и па/ иопри- ; С1, 1:сп(.: 1изается а/ - дог шаге пе11 1:1 Й ЧХОД1П Х

приемника ирпи- .г-одится по а фестройка лууг относитель ла -sv-jii iHiiy ч i::Tcnioro диск- .;|.И1 а ; v4 i i милюго F ;ac- ycTpoiicT- :i;n: c i:iara гге;.1 1 Г-:- М 1-1Й Кас I уерал.и.и на I iioiyjjo- персет жпм усиченил ,НЬЕ-С сиг- иг

ППИ

carta п,т:;: е,пг:к гора

. npii-i .у лч iiij ;г.

сс Г). yi-;: i j И ; ука, ; j jyi : с г ; U y

ч. : ГОТ ; ; n( - :;i::J CKTCpa ,

ройкч - п 15;- ЖПГ1 усчченил

ia;;o: ; и рис липка,- Dbicci-:,; гоч юсть соп;- гг-1:г i;tfq :; :iL4If.r rCJlbi i-ik iU i:-3i 1 етерОДИ- -Т и ЛОГЧ с Ji:jI-TOr a р 1 :у П;: и;ГИ1ОГО

: P(V(-ТР;) Т . L I Т п гередь cy; i;:cTur.- ;iio у: ic н 1-1 :1П I - lUTTC cy пропус-- 1::;мггя riPcctucKTona и получи ь боЧеС ilLira KyR-) ЧУ r;C i 1И ГеЛ1;НОСТЬ.

а 1.-;. упуч -Л1гь хар I ijy:; roj:L4o;: ти 1 (t;pa

. LVf in -1 - I ОЛЯЛП 1 С

iii. устройства

IKTOp iCTHKVI ИЗ-- П1СМ ;ичО;:1И КООФ- i о iv i l l nrVlGM

vP (

3 о 0

i) Г у л .1. li 3 о о р о т е и и я Гс чер.гг / Г стулеичатого напряжения, р: сапа м л мпп ель чг .стоть. Т1ькод кото- ро1 л (осдинен с у-хола:-; 4:i -faj ibHO i уста- гь ивого if лтсрого иакаггливаюгцих

10

сумматоров, задающий генератор импульсов, выход которого подключен к первым входам накапливающих сум- NjaTopoB непосредственно, а к первому входу формирователя команд через последовательно сйединенные двоичный счётчик импульсов и дешифратор, выход которого соединен с вторым входом двоичного счетчика импульсов, элемент регистрации, блок установки кодов, первый и второй выходы которого подключены к вторым входам соответствующих накапливающих сумматоров, а тре

соединен с третьими входами указанных сумматоров, причем первый и второй выходы формирователя команд сое- д1И1ены соответственно с четвертыми 0 входами первого и второго накапливающих сумматоров, выходы которых подключены к входам соответственно первого и второго преобразователей код- иaпpяжe}п e, причем выход первого j преобразователя код - напряжение является первым выходом устройства, отличающийся тем, что, с целью расширения функциональных воз- молашстей, введены второй элемент 30 регистрации, первый и второй элементы ИЛИ, элемент НЕ, высокочасточный KObtMYTaTOp и блок положительной обратной связи, причем выход второго преобразователя код - напряжение -j,r, является вторым вьгходом устройства, а входы первого и второго элементов регистрации соединены с первым входом устройства, выходы первого и второго элементов регистрации подключено РЛ)1 к соответствующим входам второго элемента 1-ШИ, выход которо го соединен с вторым входом формирователя команд, выход первого элемента ИЛИ соединен с первым входом высокочастотного ком- ;.гутатора и через элемент НЕ - с третьим входом двоичного счетчика импульсов, первый и второй входы первого элемента ИЛИ соединены с соответствующими выходами формирователя команд, при этом выход дешифратора подключен к входу делителя частоты, второй вход высокочастотного коммутатора является вторым входом устройства, а третий подключен к выходу блока положительной обратной связи, вход которого является третьим входом устройства, а выход высокочастотного коммутатора является третьим выходом устройства.

it

ГС

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор ступенчатого напряжения | 1979 |

|

SU938378A1 |

| Функциональный генератор напряжения | 1976 |

|

SU734746A2 |

| Функциональный генератор напряжения | 1976 |

|

SU610129A1 |

| Генератор ступенчатого напряжения | 1977 |

|

SU708498A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Устройство для определения характеристической функции | 1986 |

|

SU1327134A2 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Функциональный преобразователь параболического напряжения ступенчатой формы | 1973 |

|

SU437110A1 |

| Устройство фиксации импульсов | 1986 |

|

SU1394408A1 |

И:чо игпользс приемН1 К Ueni. ЧГИТ1СКИИ , -л () :нг СШ4 № 3427561, - J / о 3 1969:-. : Г:7;ЧДеТ.ЛЬС7ЕО СССР , кл, Н 03 К 4/02. 10,05Л7. ьРАЮР СТУПЕНЧАТОГО НЛПРЯЖЕоретение прелназьлчено для н,анин в тлрокодиапазоннЕ.к -,х Н анаанзаторах спектра с .. Слсг- ол Г ерестройкг; -: по часто- мэс Зретения - расширение функциональных возможностей генератора. Генератор содержит делитель 1 частоты, задс1ющий генератор 2 импульсов, накапливающие сумматоры 3 и 14, формирователь 4 команды, двоичньш счетчик 5 импульсов, дешифратор 6, блок 7 установки кодов, преобразователи 8 и 10 код-напряжение статический регистр 9 и элемент 13 регистрации. Введение блока 12 положительной обратной связи, элемента 15 регистрации элементов ИЛИ 11 и 1б, высокочастотного коммутатора 17 и элемента НЕ 18 обеспечивает возможность раздельного управления напряжения на двух выходах. Благодаря этому достигается возможность лучшего сопряжения с цепями устройств, подключаемых к выходу. 4 ил. S (J

Г

lit.l flT/

i-r

ifj

But.I

Btitj

BHX.i

ffrof i/ettnt/fnf f

ffOn/fJtJffPf

/Tif/rrOHUjr

виЖС jffil/fUmfMi

Uynp

y/ipoAunmttf MmpJHitffM/e

UcM

ffp)fffMUf

etteuffMU

i

В/ген f2

ffMro3

//

iiii.|..J4-i4-|4J

II

mm.

i-n:;n;.;. :;i 1. ;::т тста СССР

i -;;-: 1 . il;., :i O i ixf JbiTJ-lff

. , : . : i:-:c; ; чао.

M.JVL,..,-C Г) 11 1рнятпе 5 Г.Ужгород., ул .Проектная ,

,C - ириои

IvojjpeKTop Л.Бескид Подписное

Авторы

Даты

1987-08-15—Публикация

1986-02-05—Подача