БОЙ li БТОУЮЙ ВХОДПЬПС ШИН 56 и 57 ОДновременмо преобразуются в коды на выходных шинах 62, 63; по втором режиме н р;од преобразуют . и разность частот сигналов на тинах 56, 57; D третьем режиме осуществляется одновременное 1 реобра-. в код скоростей изменения частот, а в четвертом режиме - суммы п разности скоростей изменения частот. В калшом режиме преобразования начальный сброс осуществляется сигналом на тине 61 Сброс, обнулякжщм реверсивные счетчики 20 и 21 и триггеры

1

Изобретение отиосится к импульсной гехнике и может Си.п ь иснользова- 1О п системах связи вычислительньгх; машин с объектами тфавления, в системах стаб1-шизации частоты и скорое ти изме)1ения частоты для обработки сигналов от частотнь(х датчиков.

Цель изобретения - расширение функциональных возможностей преоб- разоп;1,теля за счет догюл ительного преобраяования в код и разнос- ТГ1 частот и и рлзности скоростей их изменения.

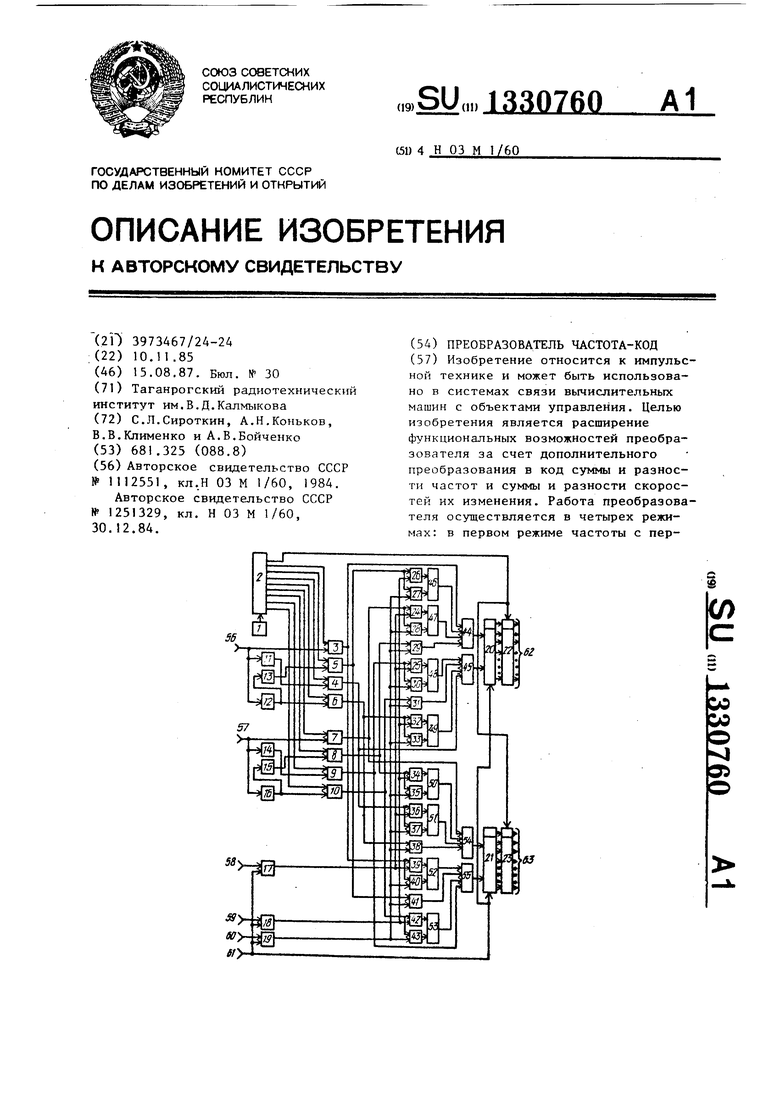

I;i чертеже представлена структур- нап э.чектрическал ск.емг преобразова-- теля ,

1и еооразо1 ате.1ть --.jCTcrra код со-- держит генератор тактовь х импульСОВ распред,ел ггель

импульсов, синхронизаторы 3-)О , пинии 11-16 задержки, триггеры 17-19 ре/етчма, реверсивные- счетчики 20 и 21 имнульсов, коммутаторы 22 и 23, элементы И 2А-чЗ, элементы ИГО 44-55, входные шины 56 и 57, шины 58-60 режима (соответственно шинь Су1-1ма и разность частот , Скорость изменени.я частот и Сумма и разность скоростей изменения частот), шину 61 Сорос и выходные шины 62 и 63.

Раснределитель 2 импульсов формирует во време 1и периодические импульсные последовательности для обеспечения работы синхронизаторов 3-10 и кo «-ryтaтopoв 22 и 23. РаспределУ1тель 2 может быть реализо17, 18 и 9 режима и имеи, длительное i, большую времени задержки в линиях задержки 11,12,13,1ч,15 и 16. , коды частот формируются на pcP.epcV BHbix счетчиках 20 и 21 и поступают на выходные шины через ком- мутач оры 22 и 23. Уиранление формируемыми 1 еператором 1 тактовых им- пу.пьсоп и распределителем 2 имлуль- сов чапг отными носледователь)1остями осуществляется с помошью синхронизаторов 3-10, триггеров 17,18 и 19, двенадцати элементов ИЛИ А4-55 и двадцати элементов И 24-43. 1 ил.

Ь

10

15

30

36

ран но известным схе- .ам. Синхронизаторы 3-10 осуп1,есч-вля 1)г В);сменную привязку в. iiMiiyjii-coH к такто- ВЫ1--1 и могут быть реали з ианы по известным схемам.

Работа нре.длаглем1,)го преобразователя осуществляв. | и и ii.n,:pex режимах. В первом режим;- чистоты с пер- ной 1- второй входных uiMii 56 и 57 од- иоБременно преобразунп ;: т коды на выходных шинах 62 и 63; ш. IJTOPOM 11ржиме осуществляете и n;i-.;i.iin ieMeiu oe преобразование и к- )п, у, и разности 4,ic-iOT, пхк:т упгпогц /- на 1зходные 1уинь и 57; н TII(- L 4(j i e ieHHoe npeoni-i ;) );;.стей изменении -.,-- на Г ходные шины 5Ь и режиме - одновреме 1Н(:- ние в код суммы и разит тп скоростей изменения часто, посгунаюгпих на вход.ные шины 56 и 57.

В каждом режиме преоГ Г Ггзования нача.чьньй сброс осу1цеств.г1яется следующим образом. шину 61 Сброс нодается сигнал, у( анавливающий в Hyj ieBoe положение счетчики 20 и 21 и григгеры 17 - 19 ре,«има. При этом длиJ eлr.iocть сигн;1:;а сброса должна быть ьо.пыуе суммарно грем.ени задержки в линиях 12 и i J задержки или в пиниях 15 и 16 зацержки япя их гихпиой очистки,

В первом режиме работа преобразователя начинается нри отсутствии игна.гюв yпpaвлeн sя на рлии.ах 58, 59

.1 :ч-ж1 ме - од- liin- в код ско- , .If; (VI уНаЮ11Ц- Х

; ) чет)ертом 11 : еобразова

3

и 60 и при окончании сигнала сброса на шине 61. При этом первая частота входной шины 56 через синхронизатор 3 и элемент ИЛИ 4А поступает на суммирующий вход первого реверсивного счетчика 20 и через первую линию 11 задержки, синхронизатор 4 и элемент ИЛИ 45 - на его вычитающий вход. Одновременно вторая частота с входной шины 57 через синхронизатор 7 и элемент ИЛИ 54 поступает на суммирующи вход второго реверсивного счетчика 21 и через четвертую лин1-по 14 задержки, синхронизатор 9 и элемент ИЛИ 55 - на его вычитающий вход. В данном режиме все элементы И закрыты, так как триггеры 17, 18 и 19 режима находятся в нулевом состоянии. Таким образом, счетчик 20 непрерывно отслеживает в коде значение первой частоты, а счетчик 21 непрерывно отслеживает в коде значение второй частоты. Считывание кода со счетчика 20 на выходную шину 62 осуществляется через коммутатор 22, а со счетчика 21 на выходную шину 63 - через коммутатор 23 при поступлении на коммутаторы управляющего сигнала с девятого выхода распределителя 2. Во втором режиме после окончания сигнала сб.роса на шину 5 режима Сумма и разность частот подается сигнал, устанавливающий триггер 17 режима в единичное состояние. При этом от- крываются элементы И 24,25,36 и 39. Остальные элементы И закрыты. В данном режиме на счетные входы счетчиков 20 и 21 поступают те же сигналы что и в первом режиме, и добавляются следующие. Первая частота с входной шины 56 через синхронизатор 3, элемент И 39, элементы ИЛИ 52 и 55 поступает на вычитающий вход счетчика 21 и через линию 11 задержки, синхронизатор 4, элемент И 36, элементы ИЛИ 51 и 54 - на его суммирующий вход. Вторая частота с входной шины 57 через синхронизатор 7, элемент И 24, элементы ИЛИ 47 и 44 поступает на суммирующий вход счетчик 20 и через линию 14 задержки, синхронизатор 9, элемент И 25, элементы ИЛИ 48 и 45 - на его вычитающий вход. Таким образом, счетчик 20 не- прерьгано отслеживает в коде значени суммы частот, а счетчик 21 непрерыв

0

5

0

5

0

но отслеживает значение разности частот. Считывание кода со счетчиков

20и 21 осуществляется с помощью коммутаторов 22 и 23 так же, как и в первом режиме.

В третьем режиме после окончания сигнала сброса на шину 59 режима Скорость изменения частот подается сигнал, устанавливающий триггер 18 режима в единичное состояние. При этом открываются элементы И 26, 32, 34 и 42, а остальные элементы И закрыты. В данном режиме на счетные входы счетчиков 20 и 21 поступают те же сигналы, что и в первом режиме, и добавляются следующие. Первая частота с входной шины 56 через линию 12 задержки, синхронизатор 6, элемент И 32 и элементы ИЛИ 49 и 45 поступает на вычитающий вход счетчика 20 и через линии 12 и 13 задержки, синхронизатор 5, элемент И 26 и элементы ИЛИ 46 и 44 - на его суммирующий вход. Вторая частота с входной шины 57 через линию 16 задержки, синхронизатор 10, элемент И 42 и элементы ИЛИ 53 и 55 поступает на вычитающий вход счетчика 21 и через линии 16 и 15 задержки, синхронизатор 8, элемент И 34 и элементы ИЛИ 50 и 54 - на его суммирующий вход. Таким образом, счетчик 20 непрерывно отслеживает в коде значение скорости изменения первой частоты, а счетчик

21непрерывно отслеживает в коде значение скорости изменения второй частоты. Считывание кодов со счетчиков 20 и 21 осуществляется с помощью коммутаторов 22 и 23 так же, как в первом и втором режимах.

В четвертом режиме после окончания сигнала сброса на шину 60 режима Сумма и разность скоростей измене- 5 ния частот подается сигнал, устанавливающими триггер I9 режима в единичное состояние, при этом открываются элементы И 27 - 31,33,35,37,38, 40,41 и 43, а остальные элементы И закрыты. В данном режиме на счетные входы счетчиков 20 и 21 поступают те же сигналы, что и первом режиме, и добавляются следующие. Первая частота с входной щины 56 через синхронизатор 3, элемент И 40, элементы ИЛИ 52 и 35 поступает на вычитающий вход счетчика 21, эта же частота через линию 11 задержки, синхрониза- -тор .4, элемент И 37, элементы ИЛИ 51

5

0

0

5

и 54 поступает на его суммирующий вход, эта же частота через линию 12 задержки, синхронизатор 6, элемент И 33, элементы ИЛИ 49 и 45 поступает на вычитающий вход счетчика 20 и после синхронизатора 6 через элемент И 38 и элемент ИЛИ 54 - на суммирующий вход счетчика 21. Эта же частота через линии 12 и 13 задержки, синхронизатор 5, элемент И 27, элементы ИЛИ 46 и 44 поступает на суммирующий вход счетчика 20 и после синхронизатора 5, элемента И 41 и элемента ИЛИ 55 поступает на вычитающий вход счетчика 21, Вторая частота с входной шины 57 через синхронизатор 7, элемент И 28, элементы ИЛИ 47 и 44 поступает на суммирующий вход счетчика 20. Эта же частота через линию 14 задержки, синхронизатор 10, элемент И 30 и элементы ИЛИ 48 и 45 поступает на вычитающий вход счетчика 20. Эта же частота через линию 16 задержки, синхронизатор 10, элемент И 31 и элемент ИЛИ 45 поступает на вычитающий вход счетчика 20 и после синхрГонизатора 10, элемента И 43, элементов ИЛИ 53 и 55 - на вычитающий вход счетчика 21. Эта частота через линии 16 и 15 задержки, синхронизатор 8, элемент И 29, элемент ИЛИ 44 поступает на суммирующий вход счетчика 20 и после синхронизатора 8, элемента И 35, элементов ИЛИ 50 и 54 - на суммирующий вход счетчика 21. Таким образом, счетчик 20 непрерывно отслеживает в коде сумму скоростей изменения частот, а счетчик 21 - одновременно разность скоростей изменения частот. Считывание кодов со счетчиков 20 и 21 осуществляется с помощью коммутаторов 22 и 23 так же, как в первом втором и в третьем режимах.

В описываемом режиме преобразование в код суммы скоростей изменения частот осуществляется на первом реверсивном счетчике 20 за счет того, что он независимо вырабатывает значение скорости изменения первой частоты совместно с независимой выработкой значения скорости изменения второй частоты, так как на его суммирующий и вычитающий входы параллельно поступают импульсные последовательности, соответствующие значениям скоростей изменения первой и

второй частот. Таким образом, на счетчике 20 осуществляется сложение скоростей изменения входных частот, Одновременно с этим в этом же режиме преобразование в код разности скоростей изменения частот осуществляется на втором реверсивном счетчике 21 за счет того, что он независимо

вьфабатывает значение скорости изменения второй частоты совместно с независимой выработкой значения скорости изменения первой частоты со знаком минус, так как соответствующие

импульсные последовательности второй частоты поступают на суммирующий вход счетчика 21, а первой частоты - на .его вычитающий вход и, наоборот, соответствующие импульсные последовательности второй частоты поступают на вычитающий вход счетчика 21, а первой частоты - на его суммирующий вход, поэтому на счетчике 21 непрерывно отслеживается значение разности скоростей изменения частот.

Для того, чтобы синхронизаторы 3-10 не вносили существенных временных сдвигов и не влияли на точность преобразования, частота генератора 1 должна выбираться не менее чем в 9 раз больще (по числу выходов распределителя) максимальных значений входных частот.

Таким образом, в предлагаемом

преобразователе расщирены функцио- . нальные возможности за счет введения режимов одновременного преобразования в код суммы и разности частот и преобразования в код суммы и разности

скоростей изменения частот с выработкой знаков разностей, причем все режимы преобразования осуществляются непрерывно, что дает возможность устранить временную привязку моментов

преобразования.

Кроме того, в предлагаемом преобразователе за счет того, что выходной код реверсивных счетчиков дополнительный модифицированный, есть возможиость выявления переполнений счетчиков и определения знака разности частот и знака разности скоростей изменения частот, что можно использовать, например, в системах

стабилизации частоты или стабилизации скорости изменения частоты.

Формула изобретения Преобразователь частота - код,

содержащий генератор тактовых импульсов, выход которого соединен с входом ряспределителя импульсов, первые четыре выхода которого соответственно соединены с первыми входами первого, второго, третьего и четвертого синхронизаторов, а пятый выход соединен с управляющим входом первого коммутатора, выходы которого являются соответствующими первыми выходными шинами, а информационные Входы соответственно соединены с выходами первого реверсивного счетчика импульсов, вход сброса которого является шиной Сброс, а суммирующий и вычитающий входы соответственно соединены с выходами первого и второго элементов ИЛИ, первьЕе входы которых соответственно подключены к выходам первог о и второго синхронизаторов, второй вход второго из которых соединен с выходом первой линии задержки, вход которой объединен с вторым выходом первого син- хроир1затора и входом второй линии задержки и является первой входной шиной, а выход второй линии задержки соединен с входом третьей линш задержки, и первый и второй элементы И, входы которых объединены и ис дклншены к выходу первогю тригтс)а режима, первый вход которого явлчется первой шиной режима, о т J и ч а ю щ и и с я тем, что, с целью расширения функциональных возможно ,; той иреобразователя за счет донолиичр.чьного преобразования в ко/1, суммы и разности частот и и р;1чи;)сти скоростей их изменения, в нет ;j )1 едены четвертая, пятая и шестая .пинии за.цержки, пятый, шестой седьмо и восьмой синхронизаторы, второй и третий триггеры режима, реверсивный счетчик импульсов, десят элементов ИЛИ, восемнадцать элементов И и второй коммутатор, выходы которого являются соответствующи ш вторыми выходными шинами, управляющий вход соединен с пятым выходом распределения импульсов, а информа- п, вход1 1 соединены с соответ- .) выходами второго реверсив- HOI-0 сче-. -чика импульсов, вход сброса которого объединен с первыми входами второго и третьего триггеров режима и вторым входом первого триггера режима и является шиной Сброс а суммирующий и вычитающий входы со- ответствегпго соединены с выходами

0

5

0

0

ь

0

f,

5

одиннадцатого и двенадцатого элементов ИЛИ, первые входы которых соответственно подключены к выходам седьмого и девятого элементов ИЛИ, вторые входы - к выходам восьмого и девятого элементов ИЛИ, а третьи входы - к выходам пятнадцатого и восемнадцатого элементов И, первые входы которых объединены с первыми входами четвертого, пятого, шестого, седьмого, восьмого, десятого, двенадцатого, четырнадцатого, семнадцатого и двадцатого элементов И и подключены к выходу третьего . триггера режима, при этом первые входы третьего, девятого, одиннадцатого и девятнадцатого эле- ментов И объединены и подключены к выходу второго трип-ера режима, вторые, третьи и четвертые вход), первого и второго элe eнтoв IL IH соответственно соединены с выхидлми третьего и шестого элемоитогн 1ПИ, четвертого и пятог о элементов МЛН и шестого и восьмого элементов И, вторые входы которых соответственно объединены с вторыми входами одиннадцатого и девятнадцатого :ги;ментои И и соответственно подключеиь; к Н.1Х )Дай шестого и восьмого гинхр.мизатрр: :-. четвертые входы одиннллп.11 i о i аиенад- цатого элементов И.ПИ. coornoTcvi- it iU объединены с вторыми нход г-п - и второго элемеь:то« Г и . ооч ветственко noaKnFJ4eut,: i: яых,),д.);.1 г что го и седьм 5Го синхрошма i оров , н; ;:1лы j третьего элемента И. И , .ги соединены с выходами . четвертого элементов И, нторые входд которых объединены с л i П,:- 1x0,1.4 восемнадцатого элемеН)1 II и иодк иоче- ны к выходу третьего сянчрони - oT(, входы четвертого и пятого э.чементов ШШ соответст)1енио соеди ЧЧ ы г .;- дами первого и пятог о : Д1 менгиа И и выходами второго и седьмого элементов И, входы шестог гт sjs . --.i гп-,э il:lii соответственно соединены о 1ял -д.-гш девятого и десятого эл1;м1;пов И, вторые входы которых объе,)неиы с вторым вх(,дом пятнадп,.1того элемент. И и подключены к пыход ч -ты, рг ci . i синхронизатора, входы :е; ,Т:,моги и .е- ся гого элемен /ов JUfli гтяснио соединены с вьгхид.и-Hi од:-;|-Ч1,ди, о; i и двенадцатого элементг.р v с т.гчо- дами девятнадцатого и др.1Д11, элементов И, перные вхпд},. - ,ii:.; Tii,.9 133076010

того и шестнадцатого элементов Иго синхронизаторов, второй вход шесобъединены и подключены к выходу пер-того синхронизатора соединен с вывого триггера режима, выходы тринад-ходом пятой линии задержки, вход коцатого и четырнадцатого элементов И 5 торой объединен с вторым входом

соответственно соединены с входамивосьмого синхронизатора и подключен

восьмого элемента ИЛИ, а вторые вхо-к выходу шестой линии задержки, втоды объединены и подключены к выходуРой вход седьмого синхронизатора

второго синхронизатора, входы девя-соединен с выходом четвертой линии

того элемента ИЛИ соответственноЮ задержки, вход которой объединен с

соединены с выходами шестнадцатоговходом шестой линии задержки и втои семнадцатого элементов И, вторыерым входом пятого синхронизатора и

входы которых объединены и подключе-является второй входной шиной, втррые

ны к выходу первого синхронизатора,входы второго и третьего триггеров

причем вторые входы третьего и чет- 5 режима являются соответственно втовертого синхронизаторов соответствен-рой и третьей шинами режима, а втоно соединены с выходами третьей ирые входы первого, второго, одиннадвторой линий задержки, шестой,цатого и девятнадцатого элементов И

седьмой, восьмой и девятый выходысоответственно объединены с вторыми,

распределителя импульсов соединены20 входами пятого, седьмого , две.соответственно с первыми входаминадцатого и двадцатого элемен пятого, шестого, седьмого и восьмо-тов И..

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

| Преобразователь частоты импульсов в код | 1984 |

|

SU1251329A1 |

| Преобразователь частоты в код | 1987 |

|

SU1418906A2 |

| Преобразователь частоты в код | 1985 |

|

SU1305857A1 |

| Преобразователь частоты в код | 1984 |

|

SU1179545A1 |

| Преобразователь частоты в код | 1987 |

|

SU1411975A1 |

| Преобразователь частота-код | 1987 |

|

SU1410276A1 |

| Преобразователь частоты импульсов в код | 1983 |

|

SU1156259A1 |

| Устройство для измерения средней длительности временных интервалов | 1987 |

|

SU1506433A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ СИГНАЛОВ С ЛИНЕЙНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2099719C1 |

Изобретение относится к импульсной технике и может быть использовано в системах связи вычислительных машин с объектами управления. Целью изобретения является расширение функциональных возможностей преобразователя за счет дополнительного преобразования в код суммы и разности частот и суммы и разности скоростей их изменения. Работа преобразователя осуществляется в четырех режимах: в первом режиме частоты с персл 00 : 9)

| Преобразователь частоты в код | 1983 |

|

SU1112551A1 |

| Преобразователь частоты импульсов в код | 1984 |

|

SU1251329A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-15—Публикация

1985-11-10—Подача