Предлагаемое изобретение относится к области цифровой радиоизмерительной техники и может быть использовано для измерения начального значения несущей частоты и скорости ее изменения внутри импульса с линейной частотной модуляцией в режиме обработки одиночных или редко повторяющихся сигналов.

Известно устройство, являющееся аналогом, и описанное в книге Павленко Ю.Ф. Шпаньон П.А. Измерение параметров частотно-модулированных колебаний. М. Радио и связь, 1986, с. 95-101, рис. 2.30, которое содержит генератор модулирующего напряжения, первый выход которого через делитель частоты соединен с входом X осциллографа, второй выход генератора модулирующего напряжения подключен к одному из входов ЧМ генератора, выход которого подключен к смесителю, другой вход которого соединен с выходом поискового генератора, а выход смесителя соединен через фильтр нижних частот с входом Y осциллографа, другой выход ЧМ генератора соединен с первым входом электронно-счетного частотомера, второй вход которого соединен с выходом поискового генератора.

Данное устройство позволяет измерять центральную частоту частотно-модулированного сигнала, однако его недостатком является требование достаточно длительного времени измерения, что при конечной длительности ЛЧМ-сигнала не всегда может быть достижимо.

Известно устройство, являющееся аналогом и описанное в книге Лихарев В. А. Цифровые методы и устройства в радиолокации. М. Советское радио, 1973, с. 108, рис. 2.12 и с. 100, рис. 2.8 и которое состоит из квантизатора на два уровня, соединенного по входу с шиной входных сигналов, а его выход через формирователь соединен с входом цифровой линии задержки и соединен с суммирующим входом реверсивного счетчика, выход цифровой линии задержки подключен к вычитающему входу реверсивного счетчика, а синхронизирующий вход соединен с выходом блока управления и синхронизации, выходы реверсивного счетчика подключены через сравнивающее устройство к выходным шинам.

Данное устройство позволяет оценить текущее значение частоты заполнения сигнала с внутриимпульсной частотной модуляцией (ЛЧМ-сигнала), однако его недостатком является низкая точность измерения.

Известно устройство, являющееся прототипом и описанное в авторском свидетельстве СССР N 1449924, кл. G 01 R 23/00, Б.И. N 1 от 07.01.89 г. и содержащее входной формирователь, выход которого соединен со счетными входами первого и второго счетных каналов, содержащих последовательно соединенные селектор, счетчик и буферный регистр, селектирующие входы обоих каналов подключены к соответствующим выходам формирователя времени счета, содержащего последовательно соединенные опорный генератор, декадный делитель частоты и формирователь стробов, выходы которого являются соответственно первым и вторым выходами формирователя времени счета, одновибратор переписи кода, вход которого подключен к второму выходу формирователя времени счета, а выход соединен с управляющим входом буферного регистра второго канала, одновибратор импульса сброса, выход которого соединен с обнуляющим входом счетчика второго канала, блок вычитания, выход которого соединен с индикатором, а также имеются второй одновибратор переписи кода, второй одновибратор импульса сброса, триггер, два коммутатора, причем вход второго одновибратора переписи кода соединен с первым выходом формирователя времени счета, а выход подключен к входу второго одновибратора импульса сброса, к R-входу триггера и к управляющему входу буферного регистра первого счетного канала, выход второго одновибратора импульса сброса подключен к обнуляющему входу счетчика первого счетного канала, выход первого одновибратора переписи кода соединен с входом первого одновибратора импульса сброса и с S-входом триггера, прямой выход триггера соединен с управляющим входом первого коммутатора, первый информационный вход которого соединен с прямым выходом первого буферного регистра, а второй с инверсным выходом второго буферного регистра, инверсный выход триггера соединен с управляющим входом второго коммутатора, первый информационный вход которого соединен с прямым выходом второго буферного регистра, второй информационный вход с инверсным выходом первого буферного регистра, выходы коммутаторов подключены соответственно к первому и второму выходам блока вычитания.

Однако данное устройство обладает тем недостатком, что имеет низкую точность измерения частоты несущего колебания fx ЛЧМ-сигнала независимо от того канала, в котором производится это измерение.

Перед изобретателем стояла задача создания измерителя параметров сигналов с линейной частотной модуляцией, позволяющего повысить точность измерения начального значения несущей частоты fx ЛЧМ-сигнала с одновременным сохранением точности измерения изменения частоты внутри импульса (скорости изменения частоты внутри импульса μx).

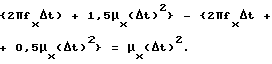

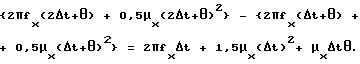

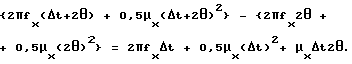

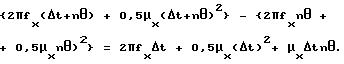

Технический результат изобретения заключается в том, что повышается точность измерения начального значения несущей частоты ЛЧМ-сигнала с одновременным измерением величины скорости ее линейного изменения и определения знака этого изменения. В рассмотренных аналогах и в прототипе можно, помимо измерения скорости изменения частоты, измерить несущую частоту с некоторой точностью, определяемой выражением

2πfxΔt + 0,5μx(Δt)2,

где Δt временной интервал, определяемый блоками его формирования.

Видно, что частота fx измеряется с погрешностью 0,5μx(Δt)2 зависящей как от величины μx так и величины Δt. Устранение этой погрешности измерения fx с одновременным сохранением точности и знака измерения μx и является техническим результатом предлагаемого устройства.

Технический результат достигается тем, что в устройство, содержащее блок формирования, информационный вход которого соединен с шиной входных сигналов, два реверсивных счетчика и блок вычитания, введен блок управления и синхронизации, первый выход которого соединен с управляющим входом блока формирования, блок ждущего мультивибратора, а также две последовательно соединенные цифровые линии задержки, входы и выходы которых соединены с суммирующими и вычитающими входами соответствующих реверсивных счетчиков, вход первой цифровой линии задержки соединен с выходом блока формирования, выход второй цифровой линии задержки соединен с входом элемента И, второй вход которой соединен с синхронизирующими входами цифровых линий задержки и с вторым синхронизирующим выходом блока управления и синхронизации, выходы реверсивных счетчиков соединены с соответствующими входами блока вычитания, выходы которого соединены с первыми входами первой группы введенных N элементов И, вторые входы которых объединены и соединены с выходом блока ждущего мультивибратора, информационный вход которого соединен с выходом элемента И, а управляющий выход соединен с третьим выходом блока управления и синхронизации, также введены вторая группа N элементов И, блок вычитания, блок суммирования, блок масштабирования и цифровой интегратор, состоящий из многоразрядного сумматора и блока многоразрядной цифровой линии задержки, причем первые входы введенной второй группы N элементов И соединены с выходами второго реверсивного счетчика, их вторые входы объединены и подключены к выходу блока ждущего мультивибратора, а их выходы соединены с первыми входами введенного блока вычитания, выходы которого являются первыми выходами устройства, вторые входы введенного блока вычитания соединены с выходами введенного блока суммирования, первые входы которого соединены с выходами цифрового интегратора, вторые входы введенного блока суммирования соединены с выходами первой группы N элементов И, которые также соединены с соответствующими входами блока масштабирования, выходы которого соединены с вторыми выходами устройства и с входами цифрового интегратора, к которым подключены первые входы многоразрядного сумматора, выходы которого соединены с входами блока многоразрядной цифровой линии задержки, синхронизирующий вход которой соединен с вторым выходом блока управления и синхронизации, четвертый выход которого соединен с входами установки нуля цифровых линий задержки, реверсивных счетчиков и блока многоразрядной цифровой линии задержки, выход блока многоразрядной цифровой линии задержки соединен с выходными шинами цифрового интегратора и с вторыми входами многоразрядного сумматора.

Достижение положительного эффекта покажем следующим образом. Если использовать устройство, описанное в авт.св. N 1449924, на его выходе образуется код, пропорциональный алгебраической величине μxΔt Код, находящийся к моменту времени 2Δt во втором счетчике, будет пропорционален величине 2πfxΔt + 0,5μx(Δt)2, а следовательно, непосредственное его считывание даст величину кода несущей частоты с ошибкой. Кроме того, сдвиг во времени измерительного интервала сопровождается возрастанием этой ошибки. Введенные дополнительные узлы в выбранный прототип обеспечивает измерение fx без этих систематических ошибок, чем и достигается положительный эффект, а именно повышается точность измерения величины начального значения несущей частоты импульса fx с линейно изменяющейся частотой модуляции внутри него с сохранением этой точности в течение всего интервала измерения и с сохранением точности изменения величины и знака скорости линейного изменения частоты μx (см. также книгу Павленко Ю.Ф. Шпаньон П.А. "Измерение параметров частотно-модулированных колебаний". М. Радио и связь, 1986, с. 65 72).

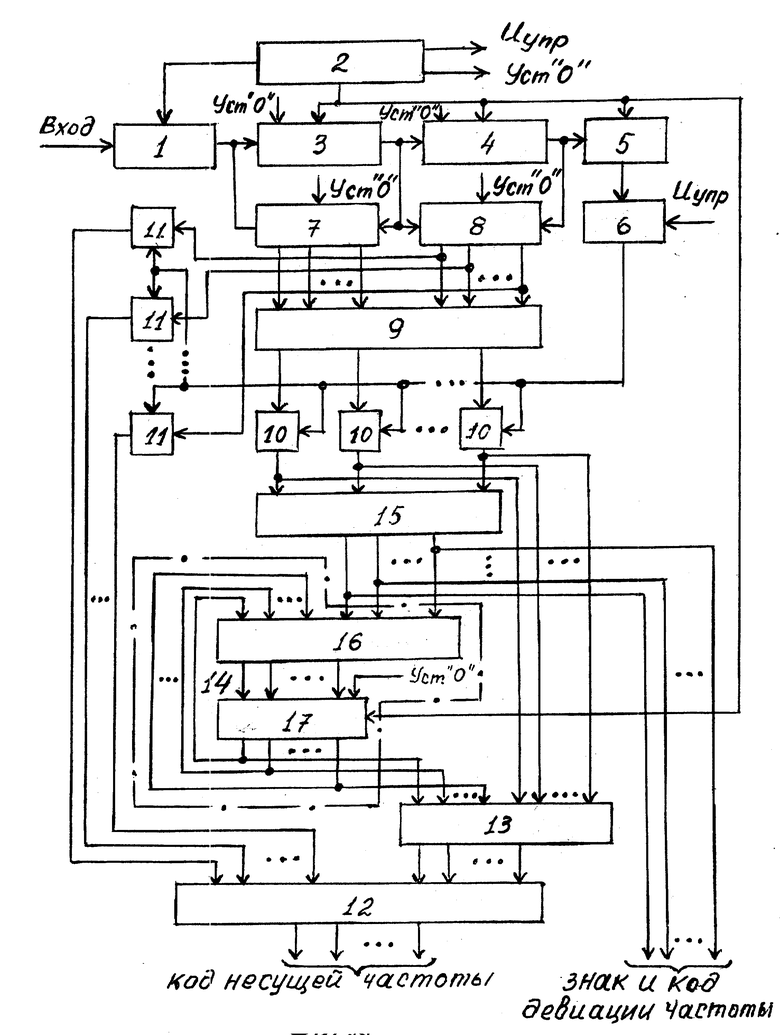

На чертеже изображена структурная схема измерителя параметров сигнала с линейной частотной модуляцией.

Представленный на чертеже измеритель параметров сигнала с линейной частотной модуляцией содержит блок формирования 1, информационный вход которого соединен с шиной входных сигналов, управляющий вход соединен с первым выходом блока управления и синхронизации 2, а его выход соединен через две последовательно соединенные цифровые линии задержки 3 и 4 с первым входом элемента И 5, второй вход которой соединен с синхронизирующим вторым выходом блока управления и синхронизации 2 и с синхронизирующими входами двух цифровых линий задержки 3 и 4, а выход элемента И 5 соединен с входом блока ждущего мультивибратора 6, управляющий вход которого соединен с третьим выходом блока управления и синхронизации 2, входы и выходы цифровых линий задержки 3 и 4 подключены соответственно к суммирующим и вычитающим входам первого 7 и второго 8 реверсивных счетчиков, которые соединены по входам установки нуля с четвертым выходом блока управления и синхронизации 2, к которому также подключены по входам установки нуля первая 3 и вторая 4 цифровые линии задержки, выходы реверсивных счетчиков 7 и 8 соединены с соответствующими входами блока вычитания 9, выходы которого соединены с первыми входами N элементов И 10, вторые входы которых объединены и соединены с выходом блока ждущего мультивибратора 6, первые входы N элементов И 11 соединены с выходами второго реверсивного счетчика 8, их вторые входы объединены и подключены к выходу блока ждущего мультивибратора 6, а их выходы соединены с первыми входами блока вычитания 12, выходы которого являются первыми выходами устройства, вторые входы блока вычитания 12 соединены с выходами блока суммирования 13, первые входы которого соединены с выходами цифрового интегратора 14, вторые входы блока суммирования 13 соединены с выходами N элементов И 10, которые также соединены с соответствующими входами блока масштабирования 15, выходы которого соединены с вторыми выходами устройства и с входами цифрового интегратора 14, к которым подключены первые входы многоразрядного сумматора 16, выходы которого соединены с входами блока многоразрядной цифровой линии задержки 17, синхронизирующий вход которой соединен с вторым выходом блока управления и синхронизации 2, четвертый выход которого соединен с входом установки нуля блока многоразрядной цифровой линии задержки 17, выход которой соединен с выходными шинами цифрового интегратора 14 и с вторыми входами многоразрядного сумматора 16.

Работает устройство следующим образом. Положим, что к моменту времени t 0 все цифровые узлы установлены в нулевое состояние по сигналу с четвертого выхода блока 2, т.е. во всех цифровых линиях задержки (ЦЛЗ) записаны нули, а реверсивные счетчики обнулены.

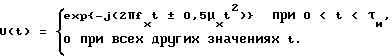

Пусть в момент времени t 0 на вход устройства поступает ЛЧМ-сигнал с неизвестной центральной частотой fx, расположенный в диапазоне fмин fмакс, и неизвестной скоростью ее изменения μx за время длительности сигнала τи и который может быть записан в виде

Отметим, что независимо от знака при величине 0,5μxt2 работа устройства не изменяется. Необходимо будет только учитывать этот знак при проведении соответствующих выкладок. В дальнейшем будем полагать, что знак положителен.

Этот сигнал по выходной шине поступает на вход блока формирования 1, на выходе которого появляются сигналы в виде последовательности нулей и единиц. Положим, что единицам соответствуют положительные значения действительной части экспоненты, а нулям отрицательные. При этом в блоке 1 происходит формирование сигналов, моменты появления которых во времени на выходе блока 1 синхронизированы с моментами времени синхроимпульсов, поступающими из блока 2 на управляющие входы цифровой линии задержки 3 с частотой, выбираемой из условия выполнения теоремы Котельникова, т.е. с частотой не менее 2fмакс. При этом согласовывается асинхронный режим поступления входных импульсов с синхронным режимом работы цифровых узлов таким образом, чтобы на каждые полпериода несущей частоты входного ЛЧМ-сигнала вырабатывался один импульс, который записывается одновременно по сигналу синхроимпульса из блока 2 в ЦЛЗ 3 и N-разрядный реверсивный счетчик 7 (РС 7). Максимальное время задержки в ЦЛЗ 3 и 4 Δt ≅ 0,5τи Поступающие на вход ЦЛЗ 3 сигналы продвигаются вдоль нее под действием синхроимпульсов, поступающих с выхода блока 2.

Одновременно эти же сигналы поступают на суммирующий вход РС 7, который начинает производить подсчет количества периодов входного колебания. В каждый текущий дискретный момент времени t = nθ где n 0,1,2. θ = Δt/2N 0≅ t≅ Δt, в РС 7 будет находиться код, пропорциональный целому числу периодов высокочастотного заполнения. В момент времени t Dt на выходе ЦЛЗ 3 будет находиться сигнал, задержанный на время Dt и который поступает на вторую ЦЛЗ 4, на вычитающий вход РС 7 и суммирующий вход N-разрядного реверсивного счетчика 8 (РС 8). Также как у ЦЛЗ 3, у ЦЛЗ 4 время задержки равно Dt, на ее суммирующий вход поступают с той же тактовой частотой синхронизирующие импульсы с выхода блока 2, которые сдвигают сигнальные импульсы вдоль этой ЦЛЗ 4. В моменты времени Dt ≅ t ≅ 2Δt на выходах РС 8 будет находиться код, пропорциональный числу периодов высокочастотного заполнения и который будет равен коду, который находился в РС 7 в моменты времени 0 ≅ t ≅ Δt.

Одновременно в РС 7 будет находиться код, равный разности частот сигналов на его входах, то есть код, пропорциональный величине

и величина которого нарастает с ростом времени t, что не позволяет точно измерить несущую частоту fx на интервале времени Δt. Очевидно, что максимальное значение кода, которое может быть записано в РС 7, будет зависеть от значений величины fмакс и τи и будет определять требования к его разрядности.

В момент времени t 2Δt сигнальный импульс достигнет конца ЦЛЗ 4 и поступает на вычитающий вход РС 8 и на вход элемента И 5. В этот момент времени на выходах РС 8 появляется код, пропорциональный разности частот сигналов на его входах, то есть код, пропорциональный величине

Одновременно в РС 7 будет находиться код, равный разности частот сигналов на его входах, то есть код, пропорциональный величине

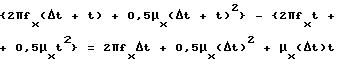

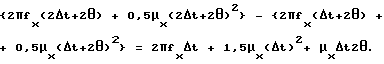

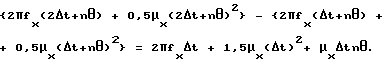

Полученные значения с выходов РС 7 и 8 в виде параллельных цифровых кодов поступают на входы блока вычитания 9. На выходах этого блока образуется код, величина которого пропорциональна разности кодов чисел, поступивших с выходов РС 7 и 8 и которая будет равна

Одновременно в момент времени t 2Δt сигнальный импульс совпадает с импульсом с выхода блока 2 на входах элемента И 5 и на его выходе появляется сигнал, который поступает на вход блока ждущего мультивибратора 6, на выходе которого появляется разрешающий сигнал с задержкой на Δτ, величина которой больше или равна времени переходных процессов в блоке вычитания 9 и которая определяется сигналом с третьего выхода блока управления и синхронизации 2. Этот сигнал поступает на соединенные вместе входы N элементов И 10, на вторых входах которых находится результат вычисления кода разности с выходов блока вычитания 9 и который появляется на выходах элементов И 10.

Одновременно код на выходе РС 7 будет находиться на первых входах N элементов И 11, на вторых входах которых находится разрешающий сигнал с выхода блока ждущего мультивибратора 6.

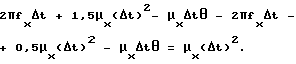

Этот код в виде величины, равной

2πfxΔt + 0,5μx(Δt)2,

поступит на первые входы блока вычитания 12.

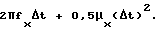

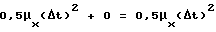

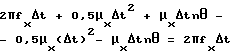

Одновременно код с выходов N элементов И 10, равный величине μx(Δt)2, поступает на входы блока масштабирования 15, на выходе которого появляется код, пропорциональный величине μxΔt и который поступает на вторые выходы устройства. Величина и знак кода, соответствующего μxΔt определяет величину и знак девиации частоты ЛЧМ-сигнала.

Одновременно код μx(Δt)2 с выходов N элементов И 10 поступает на вторые входы блока суммирования 13, который по этим входам имеет весовой коэффициент, равный 0,5.

Одновременно код, пропорциональный μxΔt, с выхода блока масштабирования 15 поступает на входы цифрового интегратора 14, к которым подключены первые входы с коэффициентом θ многоразрядного сумматора 16, на других входах которого с коэффициентом, равным единице, находится в этот момент времени код, равный нулю, а следовательно, код, соответствующий mxDtθ, записывается в блок многоразрядной цифровой линии задержки 17.

Одновременно на выходах многоразрядной цифровой линии задержки 17 будет код, соответствующий нулю и который, помимо поступления на вторые входы с коэффициентом, равным единице, многоразрядного сумматора 16, поступает также на первые входы блока суммирования 13, на выходе которого появится код, пропорциональный величине

и который поступает на вычитающий вход блока вычитания 12.

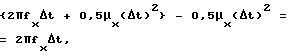

При этом на выходе блока вычитания 12 будет находиться код, соответствующий величине

что соответствует начальной несущей частоте ЛЧМ-сигнала.

В следующий дискретный момент времени t=2Δt+θ на выходе РС 8 будет находиться код, соответствующий величине

Этот код через N элементов И 11 поступает на первые входы блока вычитания 12.

Одновременно на выходе РС 7 будет код, соответствующий величине

Коды с выходов РС 7 и РС 8 одновременно поступают на блок вычитания 9, на выходах которого появляется код, соответствующий величине

Этот код через N элементов И 10 поступает на блок масштабирования 15, на выходе которого появляется код, пропорциональный величине μxΔt и который поступает на вторые входы устройства. Этот же код μxΔt поступает на входы цифрового интегратора 14, к которым подключены первые входы с коэффициентом θ многоразрядного сумматора 16. На других входах многоразрядного сумматора 16 будет находиться код mxDtθ который в этот момент времени появится на выходе блока многоразрядной цифровой линии задержки 17. Следовательно код, который будет равен сумме кодов на входах многоразрядного сумматора 16

μxΔtθ+μxΔtθ=μxΔt2θ,,

будет записан в блок цифровой многоразрядной линии задержки 17.

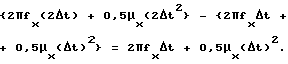

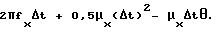

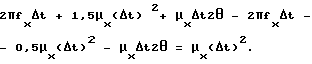

Одновременно код μx(Δt)2 с выходов N элементов И 10 поступает на вторые входы блока суммирования 13 с коэффициентом 0,5, на его первые входы с выхода блока 17 поступает код, пропорциональный величине  а следовательно, на выходах блока суммирования 13 будет код, пропорциональный величине

а следовательно, на выходах блока суммирования 13 будет код, пропорциональный величине

0,5μx(Δt)2 + μxΔtθ.

Этот код поступает на вторые вычитающие входы блока вычитания 12, на других входах которого с выходов N элементов И 11 будет код, пропорциональный величине

Следовательно, на выходе блока вычитания 12 будет код, пропорциональный величине

и который поступает на первые выходы устройства.

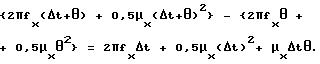

Таким образом в дискретный момент времени t = 2Δt + θ так же как и в дискретный момент времени t = 2Δt на первых выходах устройства будет код, соответствующий несущей частоте и пропорциональный величине 2πfxΔt а на вторых выходах будет код, соответствующий знаку и величине девиации частоты и пропорциональный величине μxΔt

В следующий дискретный момент времени t = 2Δt + 2θ на выходе РС 8 будет находиться код, соответствующий величине

Этот код через N элементов И 11 поступает на первые входы блока вычитания 12. Одновременно на выходе РС 7 будет код, соответствующий величине

Коды с выходов РС 7 и РС 8 одновременно поступают на блок вычитания 9, на выходах которого появляется код, соответствующий величине

Этот код через N элементов И 10 поступает на блок масштабирования 15, на выходе которого появляется код, пропорциональный величине μxΔt и который поступает на вторые выходы устройства. Этот же код μxΔt поступает на входы цифрового интегратора 14, к которым подключены первые входы с коэффициентом θ многоразрядного сумматора 16, на других входах которого находится код mxDt2θ который в этот момент времени появится на выходе блока многоразрядной цифровой линии задержки 17.

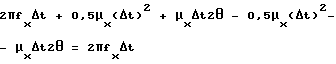

Следовательно, код, который будет равен сумме кодов, находящихся на входах многоразрядного сумматора 16 в виде

μxΔt2θ + μxΔtθ = μxΔt3θ,

будет записан в блок 17.

Одновременно код  с выходов N элементов И 10 поступает на вторые входы блока суммирования 13 с коэффициентом 0,5, на его первые входы с выхода блока 17 поступает код, пропорциональный величине μxΔt2θ а следовательно, на выходах блока суммирования 13 будет код, пропорциональный величине

с выходов N элементов И 10 поступает на вторые входы блока суммирования 13 с коэффициентом 0,5, на его первые входы с выхода блока 17 поступает код, пропорциональный величине μxΔt2θ а следовательно, на выходах блока суммирования 13 будет код, пропорциональный величине

0,5μx(Δt)2 + μxΔt2θ.

Этот код поступает на вторые вычитающие входы блока вычитания 12, на других входах которого с выходов N элементов И 11 будет код, пропорциональный величине

2πfxΔt + 0,5μx(Δt)2 + μxΔt2θ

Следовательно, на выходе блока вычитания 12 будет код, пропорциональный величине

и который поступит на первые выходы устройства.

Таким образом, в дискретный момент времени t - 2Δt + 2θ так же как и в предыдущие дискретные моменты времени, на первых выходах устройства будет код, пропорциональный 2πfxΔt а на его вторых выходах код, пропорциональный величине μxΔt

В произвольный дискретный момент времени t = 2Δt + nθ где 2Δt < t <τи на выходе РС 8 будет находиться код, соответствующий величине

и этот код через N элементов И 11 поступает на первые входы схемы вычитания 12.

Одновременно на выходе РС 7 будет код, соответствующий величине

Коды с выходов РС 7 и РС 8 одновременно поступают на блок вычитания 9, на выходах которого появляется код, соответствующий величине

Этот код через N элементов И 10 поступает на блок масштабирования 15, на выходе которого появляется код, пропорциональный величине μxΔt и который поступает на вторые выходы устройства.

Этот же код μxΔt поступает на входы цифрового интегратора 14, к которым подключены первые входы с масштабирующим коэффициентом θ многоразрядного сумматора 16, на других входах которого находится код  который в этот момент времени появится на выходе многоразрядной цифровой линии задержки 17.

который в этот момент времени появится на выходе многоразрядной цифровой линии задержки 17.

Следовательно, код, который будет равен сумме кодов, находящихся на входах многоразрядного сумматора 16 в виде

μxΔtnθ + μxΔtθ = μxΔt(n+1)θ, будет записан в блок 17.

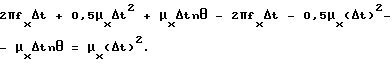

Одновременно код μx(Δt)2 с выходов N элементов И 10 поступает на вторые входы блока суммирования 13 с коэффициентом 0,5, на его первые входы с выхода блока 17 поступает код, пропорциональный величине μxΔtnθ.

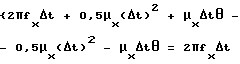

Следовательно, на выходах блока суммирования 13 будет код, пропорциональный величине

0,5μx(Δt)2 + μxΔtnθ.

Этот код поступает на вторые вычитающие входы блока вычитания 12, на других входах которого с выходов элементов И 11 будет код, пропорциональный величине

2πfxΔt + 0,5μx(Δt)2 + μxΔtnθ

Следовательно, на выходе блока вычитания 12 будет код, пропорциональный величине

и который поступит на первые выходы устройства.

Таким образом, в каждый дискретный момент времени t = 2Δt + nθ так же как и в любые другие моменты времени, на первых выходах устройства будет код, пропорциональный 2πfxΔt а на его вторых выходах код, пропорциональный величине μxΔt

В момент времени t = τи закончится разрешающий сигнал, поступающий с выхода блока ждущего мультивибратора 6, что приведет к тому, что все элементы И 10 и И 11 закроются и на их выходах будут коды, соответствующие нулю. Одновременно сигнал установки нуля с четвертого выхода блока управления и синхронизации 2 установит в нулевое состояние ЦЛЗ 3 и 4, РС 7 и РС 8, а также блок многоразрядной цифровой линии задержки 17. После интервала времени, определяемого временем восстановления блока ждущего мультивибратора 6, устройство измерения параметров сигналов с линейной частотной модуляцией готово к работе.

Отметим, что вторые выходы устройства могут быть подключены к выходу элемента И 10, однако в этом случае при изменении величины Δt (то есть времени задержки в ЦЛЗ 3 и 4) величины кодов несущей частоты и девиации изменяются непропорционально, что затрудняет в некоторых случаях процесс измерения.

Технико-экономическая эффективность предлагаемого устройства может быть оценена следующим образом. Поскольку приборы и устройства, аналогично заявленному, нашей промышленностью не выпускаются, то целесообразно сравнение производить с прототипом. В том случае, если использовать для измерения несущей частоты fx в прототипе полученное значение кода, то точность измерения зависит от времени анализа Δt и от величины μx Даже если эти величины малы относительно длительности импульса τи и несущей частоты fx соответственно, тем не менее точность измерения fx в прототипе прямо пропорциональна отношению μx/fx

В предлагаемом устройстве за счет введения дополнительных узлов в процессе измерения независимо от величин Δt и μx одновременно производится точное измерение несущей частоты fx и без потери точности величины μx

Таким образом, данное устройство позволяет измерить величину начального значения несущей частоты fx с заданной точностью, определяемой величиной Δt и не зависящей от значения величины μx а также измерять величину и знак девиации частоты μx без потери точности, что свидетельствует о высокой технико-экономической эффективности предлагаемого устройства.

Изобретение относится к области цифровой радиоизмерительной техники и предназначено для обработки одиночных или редко повторяющихся импульсов с линейной частотной модуляцией путем измерения его несущей частоты и параметра девиации. Для достижения технических результатов в устройство, содержащее блок формирования, два реверсивных счетчика и блок вычитания, введены блок управления и синхронизации, блок ждущего мультивибратора, две цифровые линии задержки, 2N+1 элементов И, введен блок вычитания, блок суммирования, блок масштабирования и цифровой интегратор, состоящий из многоразрядного сумматора и многоразрядной цифровой линии задержки. 1 ил.

Измеритель параметров сигналов с линейной частотной модуляцией, содержащий блок формирования, информационный вход которого соединен с шиной входных сигналов, два реверсивных счетчика и блок вычитания, отличающийся тем, что в него введен блок управления и синхронизации, первый выход которого соединен с управляющим входом блока формирования, блок ждущего мультивибратора, а также две последовательно соединенных цифровые линии задержки, входы и выходы которых соединены с суммирующими и вычитающими входами соответствующих реверсивных счетчиков, вход первой цифровой линии задержки соединен с выходом блока формирования, выход второй цифровой линии задержки с входом элемента И, второй вход которого соединен с синхронизирующими входами цифровых линий задержки и с вторым синхронизирующим выходом блока управления и синхронизации, выходы реверсивных счетчиков соединены с соответствующими входами блока вычитания, выходы которого соединены с первыми входами первой группы введенных N элементов И, вторые входы которых объединены и соединены с выходом блока ждущего мультивибратора, информационный вход которого соединен с выходом элемента И, а управляющий выход с третьим выходом блока управления и синхронизации, также введены вторая группа N элементов И, блок вычитания, блок суммирования, блок масштабирования и цифровой интегратор, состоящий из многоразрядного сумматора и блока многоразрядной цифровой линии задержки, причем первые входы введенной второй группы N элементов И соединены с выходами второго реверсивного счетчика, их вторые входы объединены и подключены к выходу блока ждущего мультивибратора, а их выходы соединены с первыми входами введенного блока вычитания, выходы которого являются первыми выходами измерителя, вторые входы введенного блока вычитания соединены с выходами введенного блока суммирования, первые входы которого соединены с выходами цифрового интегратора, вторые входы с выходами первой группы N элементов И, которые также соединены с соответствующими входами блока масштабирования, выходы которого соединены с вторыми выходами измерителя и с входами цифрового интегратора, к которым подключены первые входы многоразрядного сумматора, выходы которого соединены с входами блока многоразрядной цифровой линии задержки, синхронизирующий вход которой соединен с вторым выходом блока управления и синхронизации, четвертый выход которого соединен с входами установки нуля цифровых линий задержки, реверсивных счетчиков и блока многоразрядной цифровой линии задержки, выход блока многоразрядной цифровой линии задержки соединен с выходными шинами цифрового интегратора и с вторыми входами многоразрядного сумматора.

| SU, авторское свидетельство, 1449924, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1997-12-20—Публикация

1993-01-11—Подача