Изобретение относится к электроэнергетике, преимущественно к защите синхронных электродвигателей.

Цель изобретения - расширение функциональных возможностей, повышение эффективности и точности устройства.

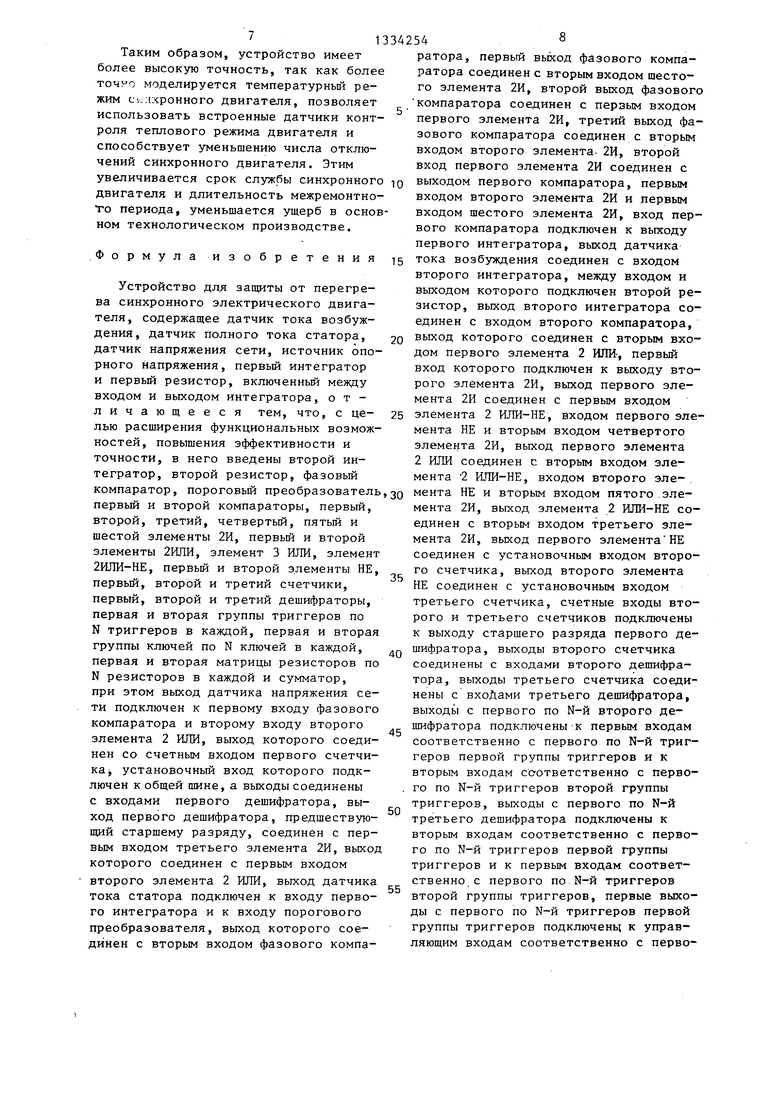

На чертеже приведена принципиальная схема устройства.

Устройство для защиты от перегрева синхронного электрического двигателя содержит датчик 1 напряжения сети, подключенный к первому входу фазового компаратора 2 и второму входу второго элемента 3 ИЛИ 35 вьтход которого соединен со счетньм входом первого счетчика 4, Установочньш вход счетчика 4 подключен к общей шине. Выходы первого счетчика 4 соединены с входами первого дешифратора 5, выход первого дешифратора 5, предшест-i вующий самому старшему разряду, соединен с первым входом третьего элемента 2И 6, выход которого соединен с первым входом элемента 3 ИЛИ 3„ Выход датчика 7 тока статора подключен к входу первого интегратора 8, охваченного с помощью первого резистора 9 обратной отрицательной связью, а также к входу порогового преобразователя 10, выход которого .соединен с вторым входом фазового компаратора 2 Первый выход фазового компаратора 2 соединен с вторым входом шестого элемента 2И 11, второй выход фазового компаратора соединен с первым входом первого элемента 2И 12, третий - с вторым входом второго элемента 2И 13,

Второй вход первого элемента 2И

12 соединен с в ыходом пбгрвого компаратора 14, первым входом второго элемента 2И 13, первым входом шестого элемента 2И 1 К Вход первого компаратора 14 соединен с выходом первого интегратора 8, Выход датчика 15 тока возбуждения соединен с входом второго интегратора 16, охваченного с помощью второго резистора 17 обратной отрицательной связью. Выход второго интегратора 16 соединен с входом второго компаратора 18, выход которого соединен с вторым входом первого элемента

2ИЛИ 19, первьй вход которого соединен с выходом второго элемента 2И 13„ Выход первого элемента 2И 12 соединен с первым входом элемента 2 ИЛИ-НЕ 20 и. входом первого элемента НЕ 21, Выход первого элемента 2 ИЛИ 19 соединен с вторым входом элемента 2 ИЛИ-НЕ

0

5

0

5

0

5

0

5

0

5

20, входом второго элемента НЕ 22 и вторым входом элемента 2И 23. Вьйсод элемента 2ИЯИ-НЕ 20 соединен с вторым входом третьего элемента 2И 6. Выход первого элемента НЕ 21 соединен с установочным входом второго счетчика 24, а выход второго элемента НЕ 22 соединен с установочньш входом третьего счетчика 25. Счетные входы счетчиков 24 и 25 подключены к старшему выкоду первого дешифратора 5, Выходы второго счетчика 24 соединены с входами второго дешифратора 26. Выходы третьего счетчика 25 соединены с входами третьего дешифратора 27. Первый выход второго дешифратора 26 соединен с первым входом первого триггера

28первой группы, второй выход этого дешифратора соединен с первым входом второго триггера этой группы, третий выход - с первым входом третьего триггера и т.д. Кроме того, первьй выход второго дешифратора 26 соединен с вторым входом первого триггера 29 второй группы, второй выход второго дешифратора- 26 соединен с ВТОРЫМ входом второго триггера 29 второй группы, третий выход второго дешифратора 26 соединен с вторым входом третьего триггера 29 второй группы и т,д. Аналогично первьй выход третьего дешиф ратора 27 соединен с первым входом первого триггера 29 второй группы и вторым входом первого триггера 28 первой группы, второй выход третьего дешифратора 27 соединен с первым входом второго триггера 29 второй группы и вторым входом второго триггера

29первой группы и т.д. Количество триггеров в каждой группе одинаково,

Первьй (прямой) выход первого триггера 28 первой группы соединен с управляющим входом первого,ключа

30первой группы, первьй выход второго триггера 28 первой группы соединен с управляющим входом второго ключа

30 первой группы и т,д«

Управляющие входы ключей 31 второй группы присоединены соответственно к вторым (инверсным) выходам триггеров 29 второй группы. Все входы ключей обеих групп соединены и подключены к источнику 32 опорного напряжения. Выход канздого из ключей присоединен к соответствующему резистору 33 первой или второй 34 матриц резисторов, Выходы матриц резисторов подключены . к входу суммирующего устройства 35,

3133А25А

Прямые выходы последних триггеров обеих групп соединены соответственно с первыми входами элементов 2И 36 и 23, второй вход четвертого элемента 2И 36 соединен с выходом первого элемента 2И 12.

Выходы элементов 2И 36, 23 и 11 соединены соответственно с nepabiMj вторым и третьим входами элемента 3 ю ИЛИ 37. Выходной сигнал элемента 3 ИЛИ 37 подается на исполнительный механизм, работающий на сигнализацию или отключение.

Вьпсодной сигнал сумматора 35 пода- 15 активный). Интеграторы 8 и 16 на ос- ется в схему полупроводникового воз- новании информации датчиков 15 и 7 будителя синхронного двигателя в ка- тока возбуждения и тока статора не-, честве добавки к напряжению, опреде- прерывно моделируют температурный ре- ляющего уставку тока возбуждения. жим соответствующей части синхронного Датчики тока статора и тока возбужде- jg двигателя.

ния имеют аналоговьй вькод. Интегра- При превышении температуры статора тор выполнен на базе операционного над допустимой на выходе компаратора усилителя и конденсатора. Компараторы 14 устанавливается уровень логической выполнены на базе операционных усили- единицы. При превышении температуры

версным выходам триггеров, т.е. в исходном состоянии ключи 31 являются замкнутыми. К входу сумматора 35 через замкнутые ключи 31 и резисторы 34 подключен источник 32 опорного напряжения. Этому исходному состоянию соответствует на выходе сумматора 35 напряжение, которое в качестве добавки поступает к задатчику тока возбуждения синхронного двигателя. Фазовый компаратор 2 непрерьшно определяет характер режима нагрузки синхронного двигателя (емкостной, индуктивный.

телей, на неинвертирующий вход которых поступает сигнал от интегратора, а инвертирующий вход подключен к выводу подвижного контакта переменного резистора. Один из вьюодов неподвижных контактов переменного резистора подключен к земляной шине, а другой к шине опорного напряжения. Регулировкой переменного резистора устанавливается уставка порога срабатывания компаратора.

Датчик напряжения имеет логический выход. В качестве датчика напряжения используется пороговьй преобразователь синус - меандр.

Устройство работает следующим образом.

В исходном состоянии на прямых выходах всех триггеров установлен уровень логического нуля. Все счетчики находятся в нулевом состоянии. Нулевому состоянию счетчиков 24 и 25 соответствует на всех выходах дешифраторов 26 и 27 уровень логической единицы. Нулевому состоянию счетчика 4 соответствует на всех выходах дешифратора 5 уровень логического нуля, т.е. код дешифратора 5 является инверсным относительно кода дешифраторов 26 и 27. Поскольку управляющие входы ключей 30 первой группы подключены к прямым входам триггеров, то в исходном состоянии ключи 30 являются разомкнутыми. Управляющие входы ключей 31 второй группы подключены к инактивный). Интеграторы 8 и 16 на ос- новании информации датчиков 15 и 7 тока возбуждения и тока статора не-, прерывно моделируют температурный ре- жим соответствующей части синхронного двигателя.

версным выходам триггеров, т.е. в исходном состоянии ключи 31 являются замкнутыми. К входу сумматора 35 через замкнутые ключи 31 и резисторы 34 подключен источник 32 опорного напряжения. Этому исходному состоянию соответствует на выходе сумматора 35 напряжение, которое в качестве добавки поступает к задатчику тока возбуждения синхронного двигателя. Фазовый компаратор 2 непрерьшно определяет характер режима нагрузки синхронного двигателя (емкостной, индуктивный.

5

0

5

0

5

0

5

ротора над допустимой на выходе компаратора 18 также устанавливаетс я уровень логической единицы. Так как сигнал компаратора 14 поступает на второй вход элемента 2 И 12, на первый вход которого поступает сигнал от второго выхода фазового компаратора 2 (этот сигнал равен логической единице при индуктивном характере нагрузки), то на выходе элемента 2 И 12 устанавливается уровень логической единицы только в одном случае. Этот случай соответствует превьш1ению температуры статора при индуктивной нагрузке, т.е. в этом случае тепловой режим двигателя можно нормализовать путем увеличения тока возбуждения, Аналогично когда превышение температуры статора происходит при емкостном режиме, то уровень логической единицы устанавливается на выходе элемента 2И 13. Ток возбуждения двигателя следует уменьшить не только при появлении сигнала логической единицы на выходе элемента 2И 13, но и в случае превьшения температуры в обмотке ротора.

Превышению температуры в обмотке ротора соответствует сигнал на выходе компаратора 18. Так как выход компаратора 18 подключен к второму входу элемента 2 ИЛИ 19, первьй вход которого подключен к выходу элемента 2И 13, то появление логической единицы на выходе элемента 2 ИЛИ 19 соответствует случаю, когда тепловой режим двигателя можно нормализовать путем уменьшения тока возбуждения.

Когда превышение температуры происходит при активном характере нагрузки, на выходе элемента 2И 11, следовательно на выходе элемента 3 ИЛИ 37 устанавливается уровень логической единицы, которьш поступает непо- - средственно на исполнительньш механизм. Когда тепловой режим двигателя не требует коррекции тока возбужде- , НИЛ, на выходах элементов 2И 12 и 2 ИЛИ 19 устанавливается уровень логического нуля, следовательно на выходе элемента 2 ИЛИ-НЕ 20 и на втором входе элемента 2 И 6. - уровень логической единицы. Так как .на всех выходах дешифратора 5 установлен уровень логического нуля, то на выходе элемента 2 И 6 и на первом входе элемента 3 ИЛИ 3 также будет уровень нуля, Поэтому элемент 3 ИЛИ 3 пропускает импульсы с выхода датчика 1 на счетньш вход счетчика 4„ Состояние счетчика 4 и дешифратора 5 изменяется с частотой входных импульсов. При появлении

на выходе дешифратора 5, соединенного с первым входом элемента 2И 6, логической единицы устанавливается уровень логической единицы и на первом входе элемента 3 РИГИ 3. Этим прекращается поступление импульсов на вход счетчика 4, при этом счетчик 4 и дешифратор 5 хранят записанньш в них код.

Если произойдет нарушение теплоЪо- го режима, требующее коррекции тока возбуждения, на выходе элемента 2 ИЛИ-НЕ 20 установится уровень нуля, Следовательно, на выходе элемента 2И 6 также установится уровень нуля и счетчику 4 разрешится дальнейший счет импульсов. Первьй входной импульс изменит состояние счетчика 4 и дешифратора 5, При этом на выходе дешифратора 5, подключенном к счетным входам счетчиков24 и 25, появится импульс. Этот импульс сменит состояние только одного из счетчиков .24 или 25, При

этом, если на выходе элемента 2И 12 установлен уровень логической единицы (т.е. требуется увеличить ток возбуждения) , то на выходе элемента НЕ 21 и на установочном входе второго счетчика 24 установится уровень логического нуля, т.е. счет импульсов будет разрешен счетчику 24„ Этот счетчик будет изменять свое состояние с частотой следования импульсов от первого дешифратора 5, Первое состояние счетчик 24 изменит в момент нарушения теплов.ого режима, второе и все последующие - с вьщержкой, определяемой коэффициентом счета счетчика 4. После счета счетчиком 24 первого импульса

на первом выходе дешифратора 26 установится уровень логического нуля и первьш триггер 28 первой группы изменит, свое состояние. На его выходе появится уровень логической единицы,

который замкнет первьй ключ 30 первой группы и на выходе сумматора 35 напряжение возрастет и вызовет увеличение тока возбуждения. Если через- выдержку времени тепловой режим не нор1 ализуется последует переключение второго триггера 28 и дополнительная добавка напряжения и т,д. Если все . добавки будут использованы и тепловой режим не нормализуется, то на выходе

элемента 2И 36, следовательно, на выходе элемента 3 ШШ 37 установится уровень логической единицы, который поступит на исполнительньш механизм.

0

0

Если наступит нарушение теплового режима, требующее уменьшения тока возбуждения, то элемент НЕ 22, проин- вертировав сигнал с выхода элемента - 2 ИЛИ 19, разрешит счет импульсов счетчику 25. В результате этого будут переключаться триггеры 29, Поскольку ключи 31 подключены управляющими входами к инверсным выходам триггеров 29, то они будут размыкаться и вькод- ное напряжение сумматора будет yrvjeHb- шаться. Когда переключится последний триггер 29 второй группы, а тепловой режим не нормализуется, то -на выходе элемента 3 ИЛИ 37 установится уровень логической е,циницы, который поступит на исполнительньм механизм.

Возможен случай, когда по условию теплового режима, происходила добавка к выходному напряжению сумматора 35., но переключение всех триггеров 28 не потребовалось. Если после этого произойдет новое нарушение теплового режима, требующее уже уменьшения выходного напряжения сумматора 35, то сразу переключатся первые триггеры обеих групп и произойдет уменьшение напряжения на две ступени. Триггеры первой группы будут переходить в ис-. ходное состояние.

5

0

5

Таким образом, устройство имеет более высокую точность, так как более точуо моделируется температурньо режим €i..ixpoHHoro двигателя, позволяет использовать встроенные датчики контроля теплового режима двигателя и способствует уменьшению числа отключений синхронного двигателя. Этим

увеличивается срок службы синхронного выходом первого компаратора, первым двигателя и длительность межремонтно- То периода, уменьшается ущерб в основном технологическом производстве.

Формула изобретения 15

Устройство для защиты от перегрева синхронного электрического двигателя, содержащее датчик тока возбуждения, датчик полного тока статора, 20 датчик напряжения сети, источник опорного напряжения, первьй интегратор и первьй резистор, включенньй между входом и выходом интегратора, отличающееся тем, что, с це- 25 лью расширения функциональных возможностей, повышения эффективности и точности, в него введены второй интегратор, второй резистор, фазовый

входом второго элемента 2И и первым входом шестого элемента 2И, вход пер вого компаратора подключен к выходу первого интегратора, выход датчика тока возбуждения соединен с входом второго интегратора, между входом и выходом которого подключен второй ре зистор, выход второго интегратора со единен с входом второго компаратора, выход которого соединен с вторым вхо дом первого элемента 2 ИЛИ-, первый вход которого подключен к выходу вто рого элемента 2И, выход первого элемента 2И соединен с первым входом элемента 2 ИЛИ-НЕ, входом первого эл мента НЕ и вторым входом четвертого элемента 2И, выход первого элемента 2 ИЛИ соединен с вторым входом элемента 2 ИЛИ-НЕ, входом второго элекомпаратор, пороговьй преобразователь,зо мента НЕ и вторым входом пятого .эле- первьй и второй компараторы, первый, второй, третий, четвертьй, пятьй и

мента 2И, выход элемента 2 ИЛИ-НЕ соединен с вторым входом третьего элемента 2И, выход первого элемента НЕ соединен с установочным входом второго счетчика, выход второго элемента НЕ соединен с установочным входом третьего счетчика, счетные входы вто рого и третьего счетчиков подключены к выходу старшего разряда первого дешифратора, выходы второго счетчика соединены с входами второго дешифратора, выходы третьего счетчика соеди нены с входами третьего дешифратора, выходь с первого по N-й второго дешифратора подключены-к первым входам соответственно с первого по N-й триг геров первой группы триггеров и к вторым входам соответственно с перво го по N-й триггеров второй группы триггеров, выходы с первого по N-й третьего дешифратора подключены к вторым входам соответственно с перво го по N-й триггеров первой группы триггеров и к первым входам соответственно с первого по N-й триггеров второй группы триггеров, первые выхо ды с первого по N-й триггеров первой группы триггеров подключены к управляющим входам соответственно с перво

шестой элементы 2И, первьй и второй элементы 2ИЛИ, элемент 3 ИЛИ, элемент 2ИЛИ-НЕ, первьй и второй элементы НЕ, первьй, второй и третий счетчики, первый, второй и третий дешифраторы, первая и вторая группы триггеров по N триггеров в каждой, первая и вторая группы ключей по N ключей в каждой, первая и вторая матрицы резисторов по N резисторов в каждой и сумматор, при этом выход датчика напряжения сети подключен к первому входу фазового компаратора и второму входу второго элемента 2 ИЛИ, выход которого соединен со счетным входом первого счетчика установочный вход которого подключен к общей шине, а выходы соединены с входами первого дешифратора, выход первого дешифратора, предшествующий старшему разряду, соединен с первым входом третьего элемента 2И, выход которого соединен с первым входом второго элемента 2 ИЛИ, выход датчика тока статора подключен к входу первого интегратора и к входу порогового преобразователя, выход которого соединен с вторым входом фазового компа2548

ратора, первый вькод фазового компаратора соединен с вторым входом шестого элемента 2И, второй выход фазового компаратора соединен с первым входом первого элемента 2И, третий выход фазового компаратора соединен с вторым входом второго элемента. 2И, второй вход первого элемента 2И соединен с

выходом первого компаратора, первым

входом второго элемента 2И и первым входом шестого элемента 2И, вход первого компаратора подключен к выходу первого интегратора, выход датчика тока возбуждения соединен с входом второго интегратора, между входом и выходом которого подключен второй резистор, выход второго интегратора соединен с входом второго компаратора, выход которого соединен с вторым входом первого элемента 2 ИЛИ-, первый вход которого подключен к выходу второго элемента 2И, выход первого элемента 2И соединен с первым входом элемента 2 ИЛИ-НЕ, входом первого элемента НЕ и вторым входом четвертого элемента 2И, выход первого элемента 2 ИЛИ соединен с вторым входом элемента 2 ИЛИ-НЕ, входом второго элео мента НЕ и вторым входом пятого .эле-

5

0

5

0

5

мента 2И, выход элемента 2 ИЛИ-НЕ соединен с вторым входом третьего элемента 2И, выход первого элемента НЕ соединен с установочным входом второго счетчика, выход второго элемента НЕ соединен с установочным входом третьего счетчика, счетные входы второго и третьего счетчиков подключены к выходу старшего разряда первого дешифратора, выходы второго счетчика соединены с входами второго дешифратора, выходы третьего счетчика соединены с входами третьего дешифратора, выходь с первого по N-й второго дешифратора подключены-к первым входам соответственно с первого по N-й триггеров первой группы триггеров и к вторым входам соответственно с первого по N-й триггеров второй группы триггеров, выходы с первого по N-й третьего дешифратора подключены к вторым входам соответственно с первого по N-й триггеров первой группы триггеров и к первым входам соответственно с первого по N-й триггеров второй группы триггеров, первые выходы с первого по N-й триггеров первой группы триггеров подключены к управляющим входам соответственно с первого по N-и ключей первой группы ключей, вторые выходы с первого по N-й триггеров второй группы триггеров подключены к управляющим входам соответственно с первого по N-Й ключей второй группы ключей неуправляющие входы всех ключей объединейы и подключены к источнику опорного напряжения, выходы с первого по N-й ключей первой группы ключей подключены к входам соответственно с первого по N-й резисторов первой матрицы резис- торс в, выходы с первого по N-й ключей второй группы ключей подключены к входам соответственно с первого по

Редактор М.Бандура

Составитель Ю.Постников

Техред М.Дидык . Корректор В.Бутяга

Заказ 3972/51Тираж 617Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г« Ужгород, ул. Проектная, 4

N-й резисторов второй матрицы резисторов, выходы первой и второй матриц резисторов объединены и подключены к входу сумматора, первый вход четвертого элемента 2И подключен к первому выходу N-ro триггера первой группы триггеров, первый вход пятого элемента 2И подключен к первому выходу N-го триггера второй группы триггеров, первьш вход элемента 3 ИЛИ подключен к выходу четвертого элемента 2И,. второй вход элемента 3 ИЛИ соединен с выходом пятого элемента 2И, а третий вход элемента 3 ИЛИ подключен к выходу шестого элемента 2И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Электромагнитный интегрирующий толщиномер | 1986 |

|

SU1427165A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Селектор импульсов по длительности | 1989 |

|

SU1667235A2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ОБЪЕКТОВ | 1992 |

|

RU2065569C1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Устройство для автоматического контроля сопротивления изоляции электрических цепей | 1989 |

|

SU1647472A1 |

Изобретение относится к электроэнергетике, преимущественно к защите синхронных электродвигателей. Цель изобретения - расширение функциональных возможностей, повьшение эффектив-, ности и ТОЧНОСТИ . Цель достигается введением в устройство второго интегратора 16, фазового компаратора 2, порогового преобразователя 10, первого 5, второго 26, третьего 27 дешифраторов. Превышению температуры в обмотке ротора соответствует сигнал выхода компаратора 2. Так как выход компаратора 18 подключен к второму входу элемента 2 ИЛИ 19, первый вход которого подключен к выходу элемента 2И 13,то появление логической единицы на выходе элемента 2 ИЛИ 19 соответствует случаю, когда тепловой ре-г жим двигателя можно нормализовать путем уменьшения тока возбуждения. 1 ил. СЛ

| Вантруб О.Ш | |||

| и др | |||

| Схема управления синхронным двигателем с подчиненной структурой регулирования | |||

| - Электричество, 1975, № 4, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Устройство для защиты от перегрева синхронной электрической машины | 1980 |

|

SU928507A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-08-30—Публикация

1986-03-13—Подача