1133

Изобретение относится к электро- texHHKe и может быть использовано во вторичных источниках питания для уп равления генераторами, работающими на переменную нагрузку.

Цель изобретения - повьшшние надежности и КПД,

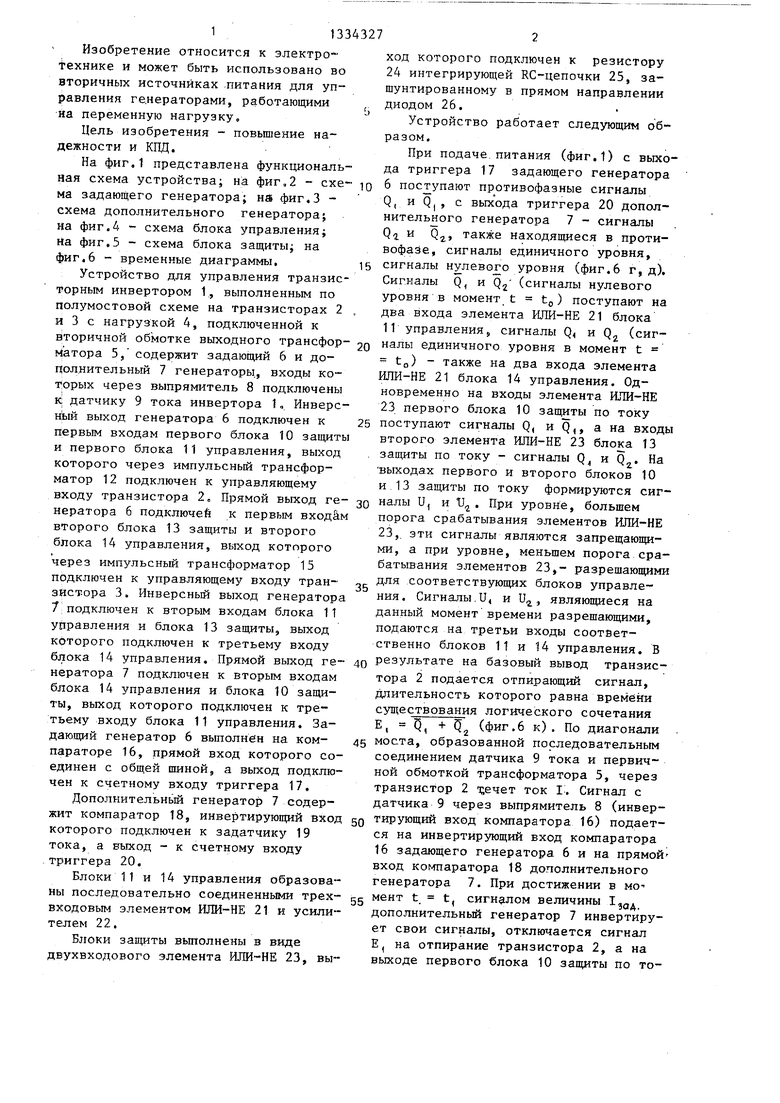

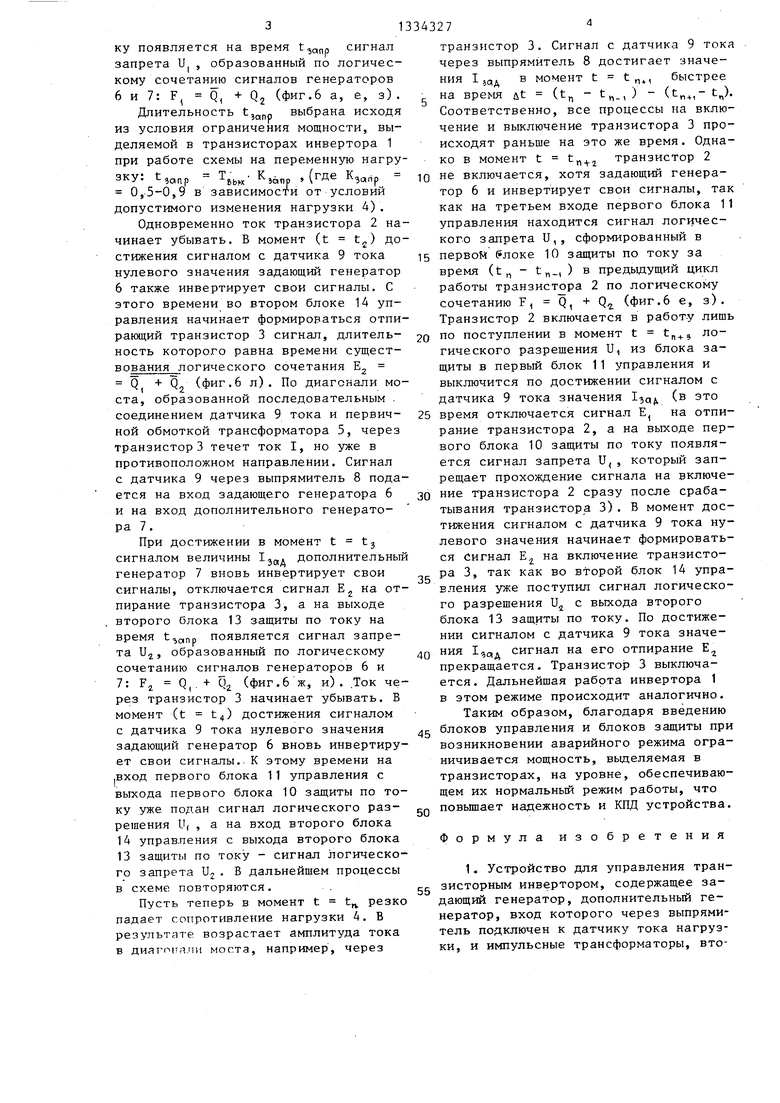

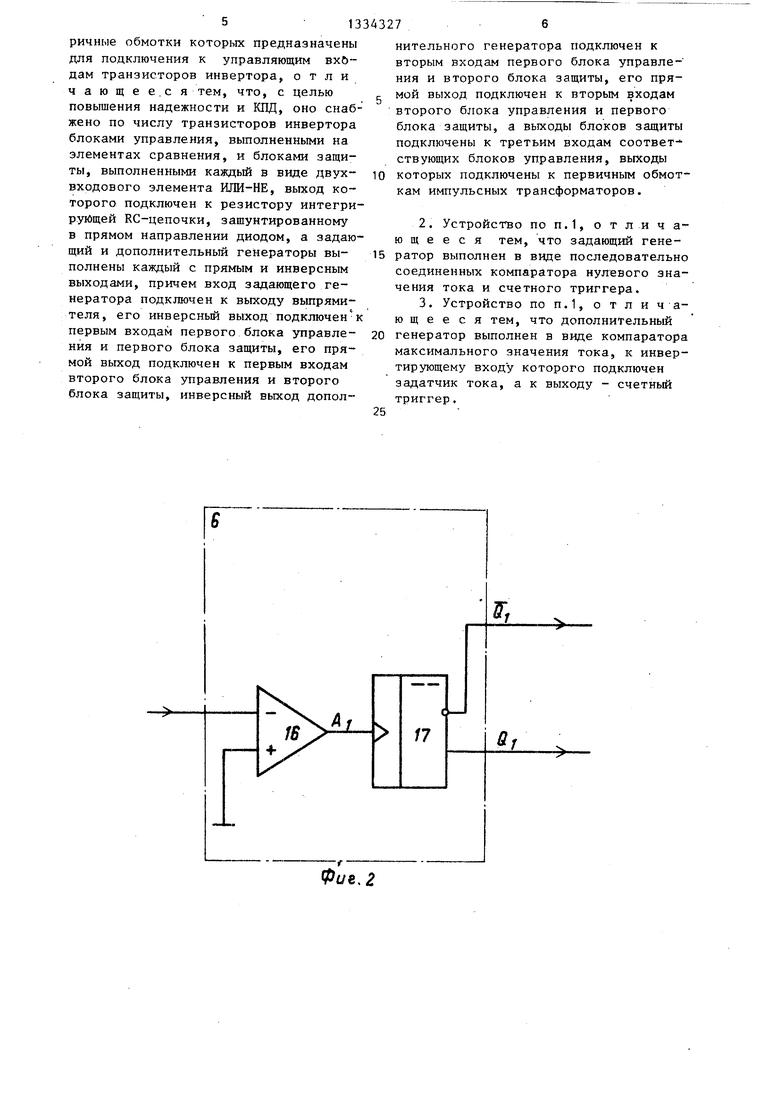

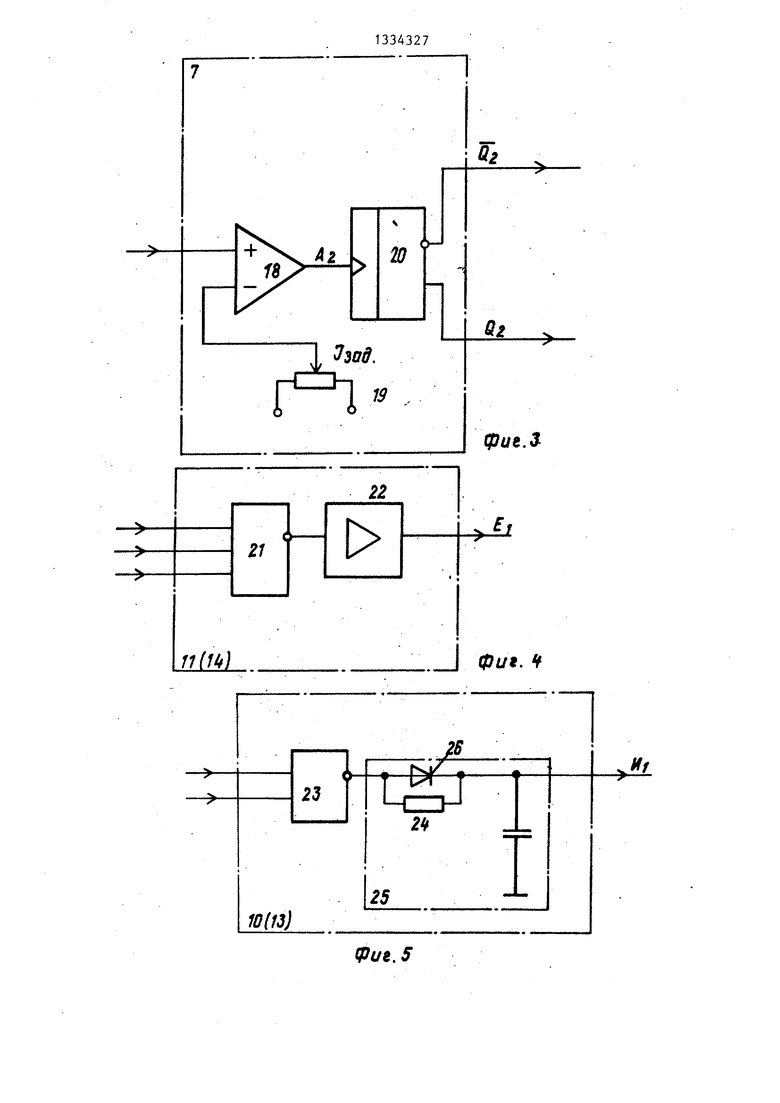

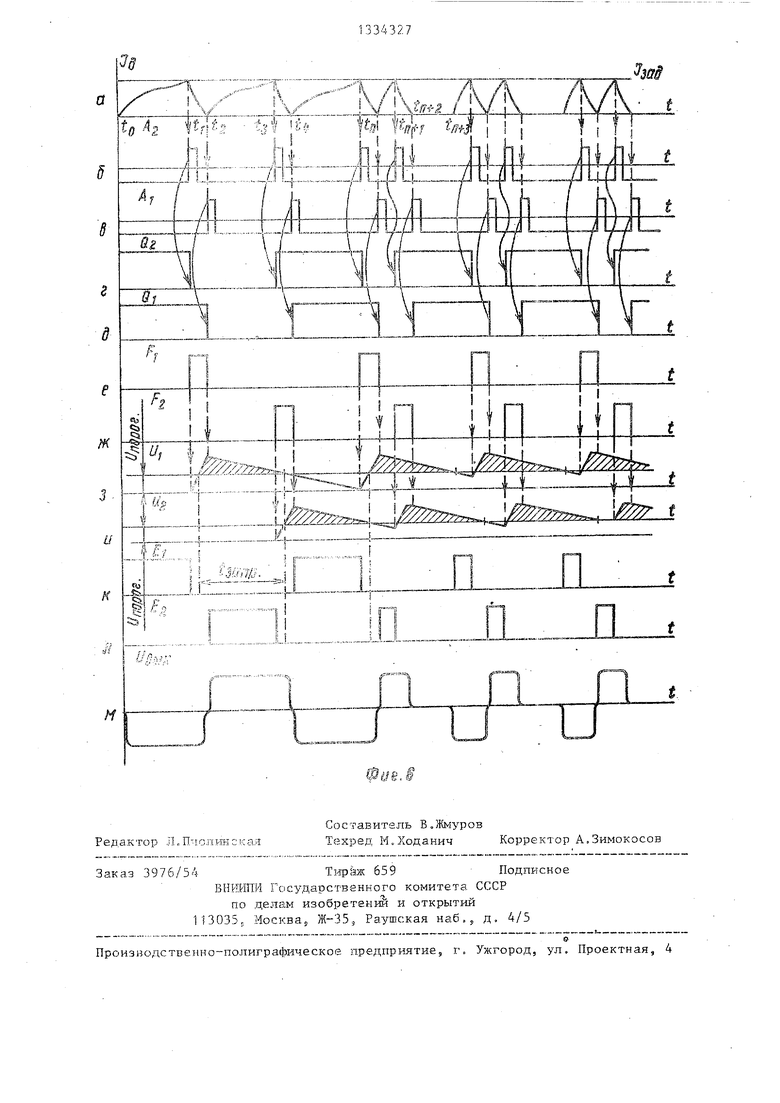

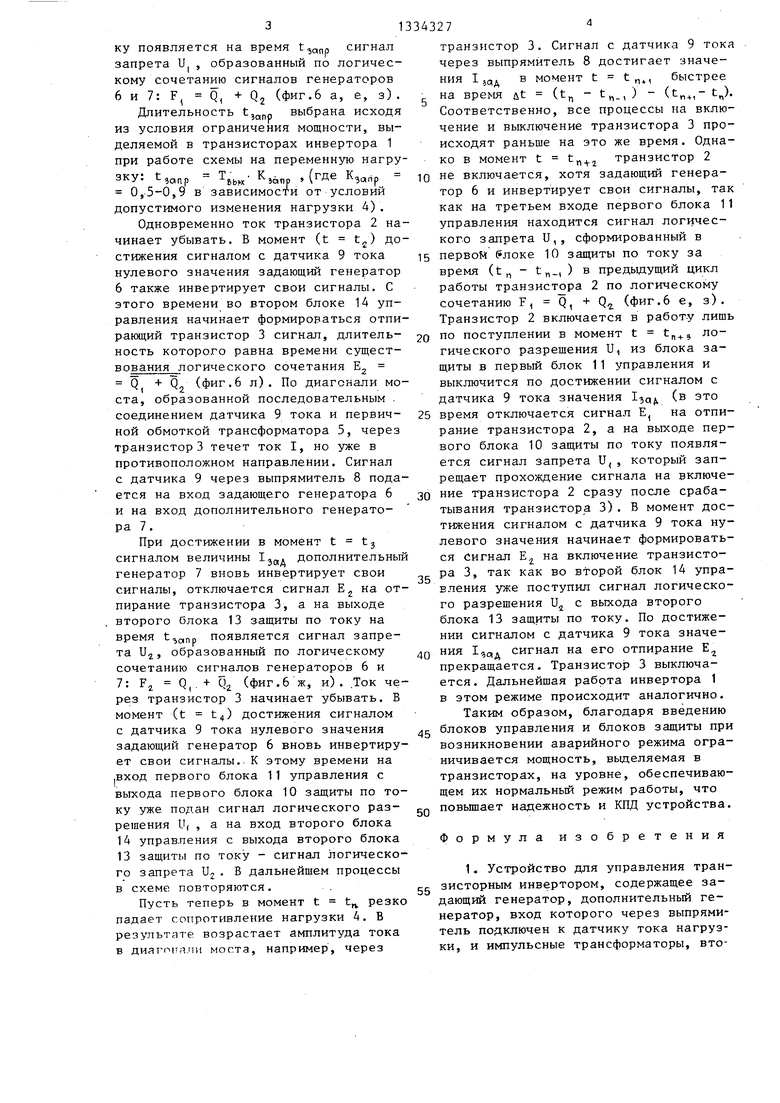

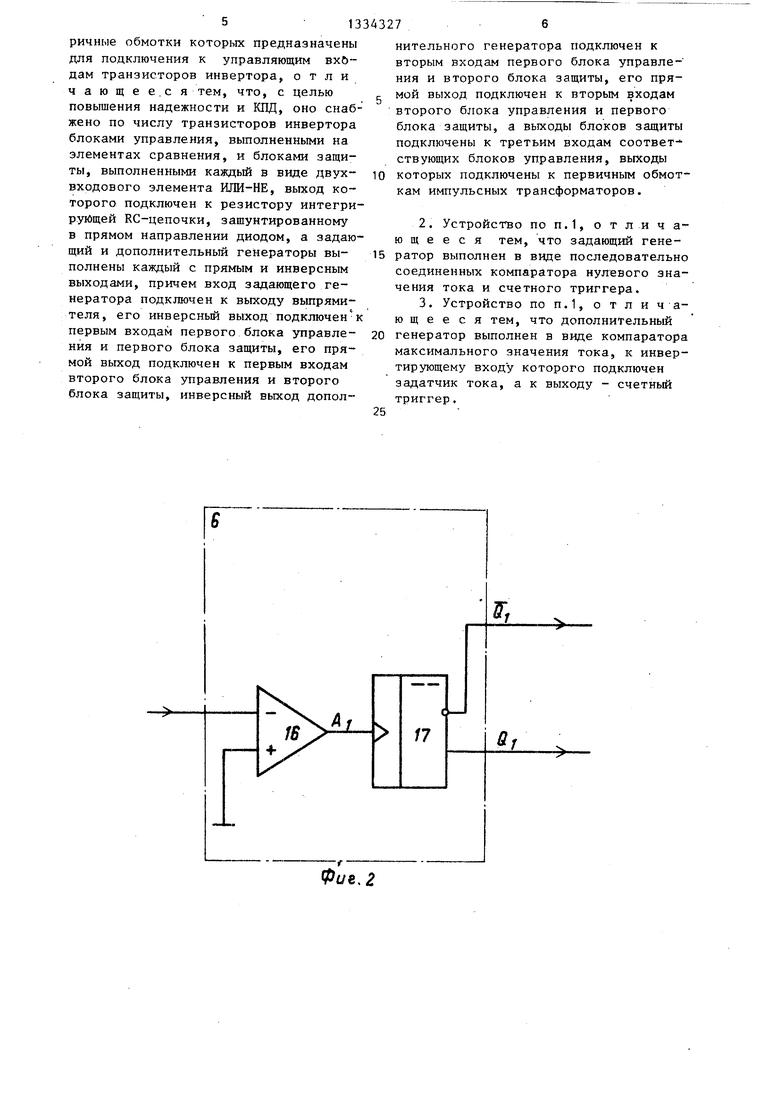

На фиг,1 представлена функциональная схема устройства; на фиг,2 - схе- ма задающего генератора; на фиг.З - схема дополнительного генератора; На фиг.4 - схема блока управления; на фиг.5 - схема блока защитьц на фиг,6 - временные диаграммы,

Устройство для управления транзисторным инвертором 1, выполненным по полумостовой схеме на транзисторах 2 и 3 с нагрузкой 4, подключенной к Вторичной обмотке выходного трансформатора 5, содержит задающий 6 и дополнительный 7 генераторы., входы которых через выпрямитель 8 подключены к; датчику 9 тока инвертора 1 „ Инверсный выход генератора 6 подключен к первым входам первого блока 10 защиты и первого блока 11 управления, выход которого через импульсньй трансформатор 12 подключен к управляющему входу транзистора 2, Прямой выход ге- нератора б подключей к первым вход&м второго блока 13 защиты и второго блока 14 управления, выход которого

через импульсньй трансформатор 15 подключен к управляющему входу тран- зйстора 3. Инверсный выход генератора / подключен к вторым входам блока 11 управления и блока 13 защиты, выход которого подключен к третьему входу блока 14 управления. Прямой выход ге- нератора 7 подключен к вторым входам блока 14 управления и блока 10 защиты, выход которого подключен к третьему входу блока 11 управления. Задающий генератор 6 выполнен на ком- параторе 16, прямой вход которого соединен с общей шиной, а выход подключен к счетному входу триггера 17.

Дополнительньй генератор 7 содержит компаратор 18, инвертирующий вход которого подключен к задатчику 19 тока, а ныход - к счетному входу триггера 20,

Блоки 11 и 14 управления образованы последовательно соединенными трех- входовым элементом ИЛИ-НЕ 21 и усилителем 22,

Блоки защиты вьшолнены в виде двухвходового элемента ИЛИ-НЕ 23, вы0

Q 5

25 зо

gg до 45

50

gg

ход которого подключен к резистору 24 интегрирующей КС-цепочки 25, за- шунтированному в прямом направлении диодом 26,

Устройство работает следующим образом.

При подаче питания (фиг,1) с выхода триггера 17 задающего генератора 6 поступают противофазные сигналы Q, и QI, с выхода триггера 20 дополнительного генератора 7 - сигналы Qa и Qa также находящиеся в проти- вофазе, сигналы единичного уровня, сигналы нулевого уровня (фиг,6 г, д), Сигналы Q, и (сигналы нулевого уровня в момент t t) поступают на два входа элемента ИЛИ-НЕ 21 блока 11 управления, сигналы р4 и Q, (сигналы единичного уровня в момент t tj,) - также на два входа элемента ИЛИ-НЕ 21 блока 14 управления. Одновременно на входы элемента ИЛИ-НЕ 23 первого блока 10 защиты по току поступают сигналы Q, и Q,, а на входы второго элемента ИЛИ-НЕ 23 блока 13 защиты по току - сигналы Q и Q, На выходах первого и второго блоков 10 и 13 защиты по току формируются сигналы и, и и, При уровне, большем порога срабатывания элементов ШШ-НЕ 23, эти сигналы являются запрещающими, а при уровне, меньшем порога срабатывания элементов 23,- разрешающими для соответствующих блоков управления. Сигналы.и, и и, являющиеся на данный момент времени разрешающими, подаются на третьи входы соответственно блоков 11 и 14 управления. В результате на базовый вывод транзистора 2 подается отпирающий сигнал, длительность которого равна времени существования логического сочетания Е, Q, + 2 (фиг.6 к). По диагонали моста, образованной последовательным соединением датчика 9 тока и первичной обмоткой трансформатора 5, через транзистор 2 ток i:. Сигнал с датчика 9 через выпрямитель 8 (инвертирующий вход компаратора 16) подается на инвертирующий вход компаратора 16 задающего генератора 6 и на прямой вход компаратора 18 дополнительного генератора 7. При достижении в мо мент t t, сигналом величины . дополнительный генератор 7 инвертирует свои сигналы, отключается сигнал Е, на отпирание транзистора 2, а на выходе первого блока 10 защиты по току появляется на время сигнал запрета U|, образованный по логическому сочетанию сигналов генераторов 6 и 7: F Q, + Qj (фиг.6 а, е, з).

Длительность выбрана исходя из условия ограничения мощности, выделяемой в транзисторах инвертора 1 при работе схемы на переменную нагрузку: t,c,np , К, , (где 0,.5-0,9 в зависимости от условий допустимого изменения нагрузки 4).

Одновременно ток транзистора 2 начинает убывать. В момент (t t) достижения сигналом с датчика 9 тока нулевого значения задающий генератор 6 также инвертирует свои сигналы. С этого времени во втором блоке 14 управления начинает формироваться отпирающий транзистор 3 сигнал, длительность которого равна времени сущест- вования логического сочетания Е QI + Qj (фиг.6 л). По диагонали моста, образованной последовательным . соединением датчика 9 тока и первичной обмоткой трансформатора 5, через транзистор 3 течет ток I, но уже в противоположном направлении. Сигнал с датчика 9 через выпрямитель 8 подается на вход задающего генератора 6 и на вход дополнительного генератора 7 .

При достижении в момент t tj сигналом величины Хзад дополнительный генератор 7 вновь инвертирует свои сигналы, отключается сигнал Е на отпирание транзистора 3, а на выходе второго блока 13 защиты по току на время появляется сигнал запрета Uj, образованный по логическому сочетанию сигналов генераторов 6 и 7: FJ Q,-+ 2 (фиг. 6 ж, и). .Ток через транзистор 3 начинает убывать. В момент (t t) достижения сигналом с датчика 9 тока нулевого значения задающий генератор 6 вновь инвертирует свои сигналы.. К этому времени на ,вход первого блока 11 управления с выхода первого блока 10 защиты по току уже подан сигнал логического разрешения и, , а на вход второго блока 14 управления с выхода второго блока 13 защиты по току - сигнал логического запрета Uj. В дальнейшем процессы в схеме повторяются.

Пусть теперь в момент t t резко падает сопротивление нагрузки 4. В результате возрастает амплитуда тока в диагонали моста, например, через

334327

транзистор 3. Сигнал с датчика 9 тока через выпрямитель 8 достигает значения 1501Д в момент t tru, быстрее на время at (t - t,) - (й„,-t). Соответственно, все процессы на включение и выключение транзистора 3 происходят раньше на это же время. Однако в момент t t

n-vi

транзистор 2

не включается, хотя задающим генератор 6 и инвертирует свои сигналы, так как на третьем входе первого блока 11 управления находится сигнал логического залрета U,, сформированный в

первом локе 10 защиты по току за время (t - tn, ) в предыдущий цикл работы транзистора 2 по логическому сочетанию Г, Q, + Q (фиг.6 е, з). Транзистор 2 включается в работу лишь

по поступлении в момент t t,, логического разрешения U, из блока защиты в первый блок 11 управления и выключится по достижении сигналом с датчика 9 тока значения (в это

время отключается сигнал Е на отпирание транзистора 2, а на выходе первого блока 10 защиты по току появляется сигнал запрета U,, который запрещает прохождение сигнала на включение транзистора 2 сразу после срабатывания транзистора 3). В момент достижения сигналом с датчика 9 тока нулевого значения начинает формироваться сигнал EJ, на включение транзистора 3, так как во второй блок 14 управления уже поступил сигнал логического разрешения } с выхода второго блока 13 защиты по току. По достижении сигналом с датчика 9 тока значеНИН сигнал на его отпирание Е,, прекращается. Транзистор 3 выключается. Дальнейшая работа инвертора 1 в этом режиме происходит аналогично. Таким образом, благодаря введению

блоков управления и блоков защиты при возникновении аварийного режима ограничивается мощность, вьщеляемая в транзисторах, на уровне, обеспечивающем их нормальный режим работы, что повьшает надежность и КПД устройства.

Формула изобретения

1, Устройство для управления транзисторным инвертором, содержащее задающий генератор, дополнительный генератор, вход которого через выпрямитель подключен к датчику тока нагрузки, и импульсные трансформаторы, вто

5 13 ричные обмотки которых предназначены для подключения к управляющим вхб- дам транзисторов инвертора, о т л и ч а ю щ е е.с я тем, что, с целью повышения надежности и КПД, оно снабжено по числу транзисторов инвертора блоками управления, выполненными на элементах сравнения, и блоками защиты, выполненными каждый в виде двух- вхсдового элемента ИЛИ-НЕ, выход которого подключен к резистору интегрирующей RC-цепочки, зашунтированному в прямом направлении диодом, а задающий и дополнительный генераторы выполнены каждый с прямым и инверсным выходами, причем вход задающего генератора подключен к выходу выпрямителя, его инверсный выход подключен к первым входам первого блока управления и первого блока защиты, его прямой выход подключен к первым входам второго блока управления и второго блока защиты, инверсный выход допол

7

6

нительного генератора подключен к вторым входам первого блока управле- ния и второго блока защиты, его прямой выход подключен к вторым входам второго блока управления и первого блока защиты, а выходы блоков защиты подключены к третьим входам соответ- ствующих блоков управления, выходы которых подключены к первичным обмоткам импульсных трансформаторов.

2. Устройство по П.1, отличающееся тем, что задающий гене

ратор выполнен в виде последовательно соединенных компаратора нулевого значения тока и счетного триггера.

3. Устройство по П.1, отличающееся тем, что дополнительный генератор выполнен в виде компаратора максимального значения тока, к инвертирующему входу которого подключен задатчик тока, а к выходу - счетный триггер.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный источник постоянного напряжения | 1985 |

|

SU1309012A1 |

| Преобразователь напряжения с защитой от перегрузок | 1988 |

|

SU1585884A1 |

| ИМПУЛЬСНО-МОДУЛИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012989C1 |

| Преобразователь напряжения с защитой от перегрузки | 1990 |

|

SU1713047A2 |

| Преобразователь постоянного напряжения в постоянное | 1988 |

|

SU1605302A1 |

| Система электропитания | 1989 |

|

SU1603499A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ ЭЛЕКТРОПРИВОД С НЕУПРАВЛЯЕМЫМ ЗВЕНОМ ПОСТОЯННОГО ТОКА | 1993 |

|

RU2067352C1 |

| Импульсный стабилизатор постоянного напряжения с программным управлением | 1987 |

|

SU1458865A1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Устройство для управления транзисторами двухтактного преобразователя | 1986 |

|

SU1334310A1 |

Изобретение относится к электротехнике и может быть использовано во вторичных источниках питания для управления генераторами, работающими на переменную нагрузку. Целью изобретения является повышение надежности и КПД. Поставленная цель достигается благодаря введению блоков управления 11 и 14 и блоков защиты 10 и 13. При возникновении аварийного режима ограничивается мощность, вьщеляемая в транзисторах 2 и 3, на- уровне, обеспечивающем их нормальный режим работы. 2 з.п, ф-лы, 6 ил. (Л с bo САЭ 4 00 1чЭ фиг. 7

Фие,2

-

18

Az

зад.

r

21

ri jiff

и

фие,3

22

1

фи1,

23

Л.

fff

2ft

10(13)

25

(pue.S

Реда.ктор Л.Пчолинскал Заказ 3976/54

Составитель В.Жмуров

Техред М.Ходанич Корректор А.Зимокосов

659Подписное

ВИШНИ Государственного комитета СССР

по делам изобретешда и открытий 113035,: Москваг Ж-ЗЗ, Раушская наб, д., 4/5

.- о

Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

| Транзисторный инвертор | 1974 |

|

SU521642A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Транзисторный инвертор | 1979 |

|

SU788313A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-08-30—Публикация

1986-04-22—Подача