реализации блока коммутации; на фиг. 3 эпюры, поясняющие работу преобразователя с защитой от перегрузки.

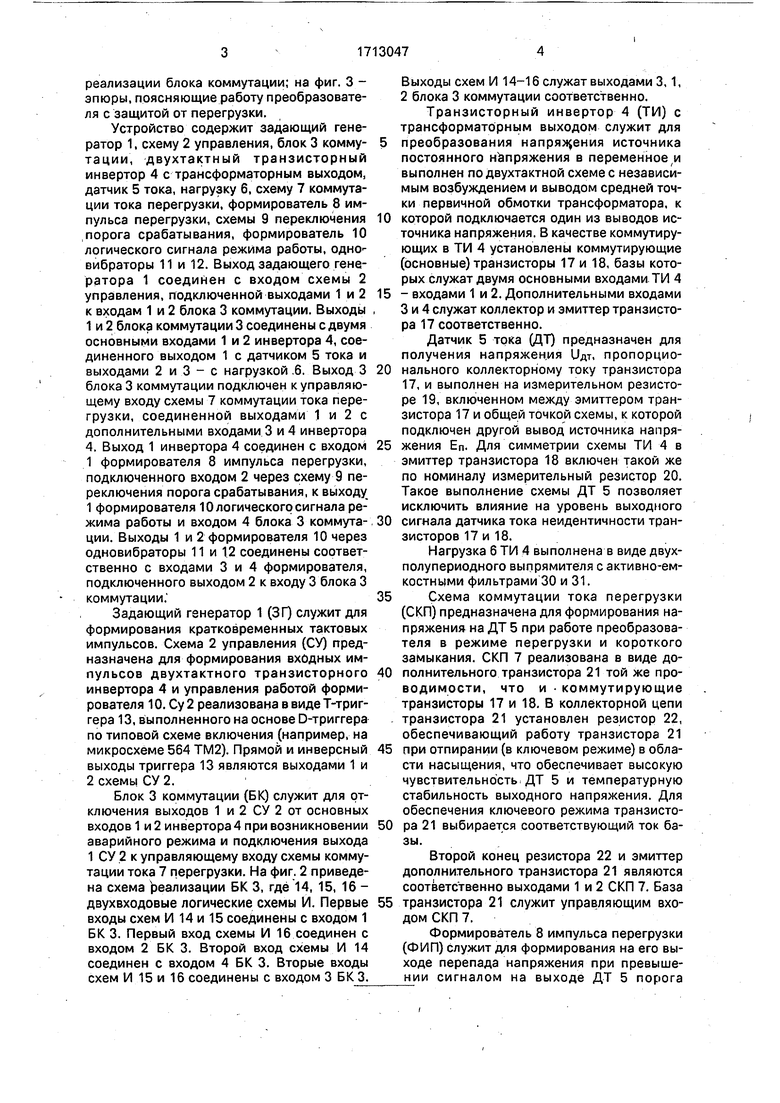

Устройство содержит задающий генератор 1, схему 2 управления, блок 3 коммутации, двухтактный транзисторный инвертор 4 с трансформаторным выходом, датчик 5 тока, нагрузку 6, схему 7 коммутации тока перегрузки, формирователь 8 импульса перегрузки, схемы 9 переключения порога срабатывания, формирователь 10 логического сигнала режима работы, одновибраторы 11 и 12. Выход задающего генератора 1 соединен с входом схемы 2 управления, подключенной выходами 1 и 2 к входам 1 и 2 блока 3 коммутации. Выходы 1 и 2 блока коммутации 3 соединены с двумя основными входами 1 и 2 инвертора 4, соединенного выходом 1 с датчиком 5 тока и выходами 2 и 3 - с нагрузкой .6. Выход 3 блока 3 коммутации подключен к управляющему входу схемы 7 коммутации тока перегрузки, соединенной выходами 1 и 2 с дополнительными входами 3 и 4 инвертора 4. Выход 1 инвертора 4 соединен с входом 1 формирователя 8 импульса перегрузки, подключенного входом 2 через схему 9 переключения порога срабатывания, к выходу

1формирователя 10 логического сигнала режима работы и входом 4 блока 3 коммутации. Выходы 1 и 2 формирователя 10 через одновибраторы 11 и 12 соединены соответственно с входами 3 и 4 формирователя, подключенного выходом 2 к входу 3 блока 3 коммутации.

Задающий генератор 1 (ЗГ) служит для формирования кратковременных тактовых импульсов. Схема 2 управления (СУ) предназначена для формирования входных импульсов двухтактного транзисторного инвертора 4 и управления работой формирователя 10. Су 2 реализована в виде Т-триггера 13, в;ыполненного на основе D-триггера по типовой схеме включения (например, на микросхеме 564 ТМ2). Прямой и инверсный выходы триггера 13 являются выходами 1 и

2схемы СУ 2.

Блок 3 коммутации (БК) служит для отключения выходов 1 и 2 СУ 2 от основных входов 1 и 2 инвертора 4 при возникновении аварийного режима и подключения выхода 1 СУ 2 к управляющему входу схемы коммутации тока 7 перегрузки. На фиг. 2 приведена схема эеализации БК 3, где 14, 15, 16 двухвходовые логические схемы И. Первые входы схем И 14 и 15 соединены с входом 1 Б К 3. Первый вход схемы И 16 соединен с входом 2 БК 3. Второй вход схемы И 14 соединен с входом 4 БК 3. Вторые входы схем И 15 и 16 соединены с входом 3 БК 3.

Выходы схем И 14-16 служат выходами 3,1,

2блока 3 коммутации соответственно.

Транзисторный инвертор 4 (ТИ) с трансформаторным выходом служит для

преобразования напря 1 ения источника постоянного напряжения в переменное,и выполнен по Двухтактной схеме с независимым возбуждением и выводом средней точки первичной обмотки трансформатора, к

0 которой подключается один из выводов источника напряжения. В качестве коммутирующих в ТИ 4 установлены коммутирующие (основные) транзисторы 17 и 18, базы которых служат двумя основными входами ТИ 4

5 - входами 1 и 2. Дополнительными входами

3и 4 служат коллектор и эмиттер транзистора 17 соответственно.

Датчик 5 тока (ДТ) предназначен для получения напряжения UAT, пропорционального коллекторному току транзистора 17, и выполнен на измерительном резисторе 19, включенном между эмиттером транзистора 17 и общей точкой схемы, к которой подключен другой вывод источника напряжения ЕП. Для симметрии схемы ТИ 4 в эмиттер транзистора 18 включен такой же по номиналу измерительный резистор 20. Такое выполнение схемы ДТ 5 позволяет исключить влияние на уровень выходного

0 сигнала датчика тока неидентичности транзисторов 17 и 18.

Нагрузка 6 ТИ 4 выполнена в виде двухполупериодного выпрямителя с активно-емкостными фильтрами 30 и 31.

5 Схема коммутации тока перегрузки (СКП) предназначена для формирования напряжения на ДТ 5 при работе преобразователя в режиме перегрузки и короткого замыкания. СКП 7 реализована в виде дополнительного транзистора 21 той же проводимости, что и - коммутирующие транзисторы 17 и 18. В коллекторной цепи транзистора 21 установлен резистор 22, обеспечивающий работу транзистора 21

5 при отпирании (в ключевом режиме) в области насыщения, что обеспечивает высокую чувствительность ДТ 5 и температурную стабильность выходного напряжения. Для обеспечения ключевого режима транзистора 21 выбирается соответствующий ток базы.

Второй конец резистора 22 и эмиттер дополнительного транзистора 21 являются соответственно выходами 1 и 2 СКП 7. База

5 транзистора 21 служит управляющим входом СКП 7.

Формирователь 8 импульса перегрузки (ФИП) служит для формирования на его выходе перепада напряжения при превышении сигналом на выходе ДТ 5 порога

срабатывания формирователя. ФИП 8 может быть выполнен по схеме компаратора, например, на микросхеме типа 521САЗ, имеющей два сигнальных входа 1 и 2.

Алгоритм работы ФИП 8 описывается уравнением

{о

при Ux.i Uexa ;

U8

О при UBX.I ивх.2.

где Us - выходной сигнал ФИП 8;

1, О - уровни сигналов;

UBX.I, UBX.2 - уровни сигналов на соответствующих входах ФИП 8.

Схема 9 переключения порога срабатывания (СПП) предназначена для изменений порога срабатывания ФИП 8 при переходе преобразователя из рабочего (Uni) в аварийный режим работы (Un2) и обратно. Необходимость в изменении порога объясняется тем, что ДТ 5 запитывается в рабочем режи-, ма коллекторным током, протекающим через полуобмотку трансформатора ТИ 4 и транзистор 17, а в аварийном режиме коллекторным током транзистора 21, протекающим через ту же полуобмотку трансформатора и дополнительный резистор 22. Позтому току перегрузки при аварийном режиме (после переключения ДТ 5 с транзистора 17 на 21) соответствует напряжение идт в К-раз меньшее, чем уровень Удт в рабочем режиме. Этим объясняется необходимость соответствующего уменьшения порогового уровня в аварийном режиме (с Uni на Un2).

Схема реализации СПП 9 приведена на фиг. 1, где 23-25 -делитель опорного напряжения ЕОП на резисторах, 26 - транзисторный ключ. Резисторы 23-25 соединены последовательно и подключены к источнику опорного напряжения ЕОП. Точка соединения резисторов 23 и 24 служит выходом СПП

9. Ключ подсоединен параллельно резистору 25. База ключа 26 является управляющим входом СПП 9. Ключ 26 служит для шунтирования резистора 25 при подаче на вход уровня 1 и изменения тем самым

козффициента деления опорного напряжения.

Формирователь 10 логического сигнала режима работы (ФЛС) предназначен для

формирования на его выходах 2 и 1 логических сигналов 1 в зависимости от режима работы преобразователя (рабочий, аварийный) и сигналов на управляющих входах 3 и 4. При этом длительность логического сигнала 1 определяется длительностями аварийного (рабочего) режима и импульсс) на выходе одновибратора 12 (11), поступающего на соответствующий управляющий вход ФЛС.

Работа ФЛС 10 описывается следующим алгоритмом.

В рабочем режиме напряжение на выходе 1 ФЛС 10 равно

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения с защитой от перегрузок | 1989 |

|

SU1713051A1 |

| Преобразователь напряжения с защитой от перегрузок | 1988 |

|

SU1585884A1 |

| Регулируемый конвертор | 1986 |

|

SU1365290A1 |

| Регулируемый преобразователь постоянного напряжения | 1986 |

|

SU1336175A1 |

| Устройство управления сварочным источником питания | 1990 |

|

SU1745455A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Способ преобразования временного сдвига между двумя сигналами и устройство для его осуществления | 1989 |

|

SU1723560A1 |

| Фотодатчик | 1989 |

|

SU1640548A1 |

| Блок управления печатающими молоточками в печатающем устройстве | 1986 |

|

SU1344629A1 |

| Регулятор температуры | 1980 |

|

SU883880A1 |

Изобретение относится к преобразовательной технике. Цель изобретения - повышение надежности защиты. Устройствосодержит задающий генератор, блок управления, блок коммутации, двухта.ктный транзисторный инвертор с трансформаторным выходом, датчик тока, нагрузку, блок комму-, тации тока перегрузки, формирователь импульса перегрузки, блок переключения порога срабатывания, формирователь логического сигнала режима работы, два одно- вибратора. За счет принудительного удержания инвертора одновибраторами в течение фиксированного интервала вроме- ни в соответствующем переключенном состоянии после моментов перехода его в аварийный и рабочий режимы повышается надежность защиты преобразователя от перегрузок. 3 ил.-сЁИзобретение относится к преобразовательной технике и может быть использовано в системах электропитания различных электронных устройств..Известен преобразователь напряжения с защитой от перегрузки, содержащий двухтактный транзисторный инвертор с трансформаторным выходом, нагруженным на выпрямитель с фильтром и датчиками тока в змиттерных цепях транзисторов инвертора, и схему защиты от перегрузки, содержащую коммутатор тока перегрузки, формирователь импульса перегрузки, схему переключения порога срабатывания и формирователь логического сигнала режима работы с двумя входами, прямым и инверсным выходами.Недостатком устройства является снь:- жение надежности защиты при работе преобразователя на выпрямитель с фильтром с активно-емкостной нагрузкой.Цель изобретения - повышение надежности защиты при работе преобразователя на выпрямитель с фильтром с активно-емкостной нагрузкой.Поставленная цель достигается тем. что в преобразователь напряжения с защитой от перегрузок введены два одновибратора, а формирователь логического сигнала режима работы снабжен входами принудительной установки формирователя в аварийный и рабочий режимы. Причем прямой выход формирователя логического сигнала режима работы подключен через один одновиб- ратор к входу принудительной установки формирователя в аварийный режим, а инверсный выход соединен с входом принуди- тельной установки формирователя в рабочий режим через другой одновибратор.На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - схемаСОgVJ>&ю

.0 при Lb О В момент перехода преобразователя в рабочий режим; о в интервале tp t tn независимо от Us на этом интервале ; о в области tii t tA при Us О на соответствующих интервалах времени О-Ти гдеtii -длительность импульса одновибратора 11 на входе 3 ФЛС 10;35 tp, tA - моменты возникновения рабочего или аварийного режима, соответственно.

при Us 1 в момент tA перехода преобразователя в аварийный режим; У в интервале tA t ti2 независимо от Us на этом интервале ; Ч в области ti2 t tp при Us 1 на соответствующих интервалах времени O-tn

где ti2 - длительность импульса одновибратора 12 на входе 4 ФЛС 10.

ФЛС 10 реализован на D-триггере 27 40 (например, микросхеме типа 564ТМ2). Вход 2 ФЛС 10 соединен через одновибратор 28 и схему НЕ 29 с С-входом D-триггера 27. Входы 3 и 4 ФЛС 10 являются соответственно входами принудительной установки фор- 45 мирователя 10 в рабочий и аварийный режимы и соединены с R и S-входами триггера 27 (фиг. 1).

Одновибратор 28 служит для устранения влияния на точность формирования логического сигнала режима работы коммутационного выброса коллекторного тока в момент насыщения трансформатора ТИ 4. Для этого длительность импульса Ти одновибратора 28 выбирается 0,7 Т, так В аварийном режиме напряжение нв выходе 1 ФЛС 10 равно

как длительность коммутационного выброса не превышает 0,3 Т, где Т - период повторения тактовых импульсов ЗГ1. Одновибратор 28 может быть реализован на микросхеме типа 155АГ1. При срабатывании одновибратора 28 на его выходе формируется уровень 1.

Логическая схема НЕ 29 инвертирует выходной сигнал одновибратора 28. Поэтому при поступлении на вход схемы НЕ 29 импульсов длительностью Ти с периодом повторения Т, на выходе схемы НЕ 29 фор-мируются сигналы U29 с логическим уров нем 1, длительностью г 2Т- Ги , .

d при О t tn ;

U29

l при tn t 2 т - tn 2 т- Ти .

гдеt -текущее время, отсчитываемое в пределах каждого периода коммутации инвертора относительно соответствующего момента коммутации;

tn - момент времени формирования заднего фронта импульса на выходе одновибратора 28, отсчитываемый в пределах каждого периода коммутации инвертора относительно соответствующего момента коммутации с задержкой, равной Ти , т.е. ги

Ти .

D-триггер 27 предназначен для формирования логического уровня сигнала 1 на. выходах 1 и 2 ФЛС 10 при следующих временных соотношениях импульсов, поданных на D и С-входы

1 , Тпри t tM-2T, b при о t Ти.

При этом согласно логике работы Dтриггера, 1 формируется на его прямом выходе в момент t 1и Ти прихода импульса на С-вход.

Для выхода 2 (ввиду инверсности выходов 2 и 1 это же условие определяет формирование О на выходе 1)

на D-входе

о при О t tM ;

и

1и t Т,

на С-входе

., ГУ при t Ти-2Т; и

, О при О t Хи.

Одновибратор 11 предназначен для блокирования ФЛС 10 по входу 3 в течение длительности импульса tii, т.еГ. для удержания ФЛС 10 в состоянии О на выходе 1 на время tii с момента tp начала рабочего режима. Поэтому вход 3 является входом принудительной установки формирователя 10 в

рабочий режим.

Одновибратор 12 предназначен для блокирования ФЛС 10 по входу 4 в течение длительности импульса ti2, т.е. для удержания ФЛС 10 в состоянии 1 на выходе 1 на

время ti2 с момента tA начала аварийного режима. Вход 4 является входом принудительной установки формирователя 10 в аварийный режим.

Одновибраторы 11 и 12 могут быть реализованы на микросхеме типа 155АГ1, причем выбирают tii «ti2 tn, где tn длительность установления амплитуды напряжения Uc3i на выходе РзоСз1-фильтра нагрузки 6 при переходных процессах,

возникающих при изменении режима работы преобразователя в моменты tp и tA (tn пропорционально постоянной времени ВзоСз1 фильтра с активно-емкостной нагрузкой R30 и Csi).

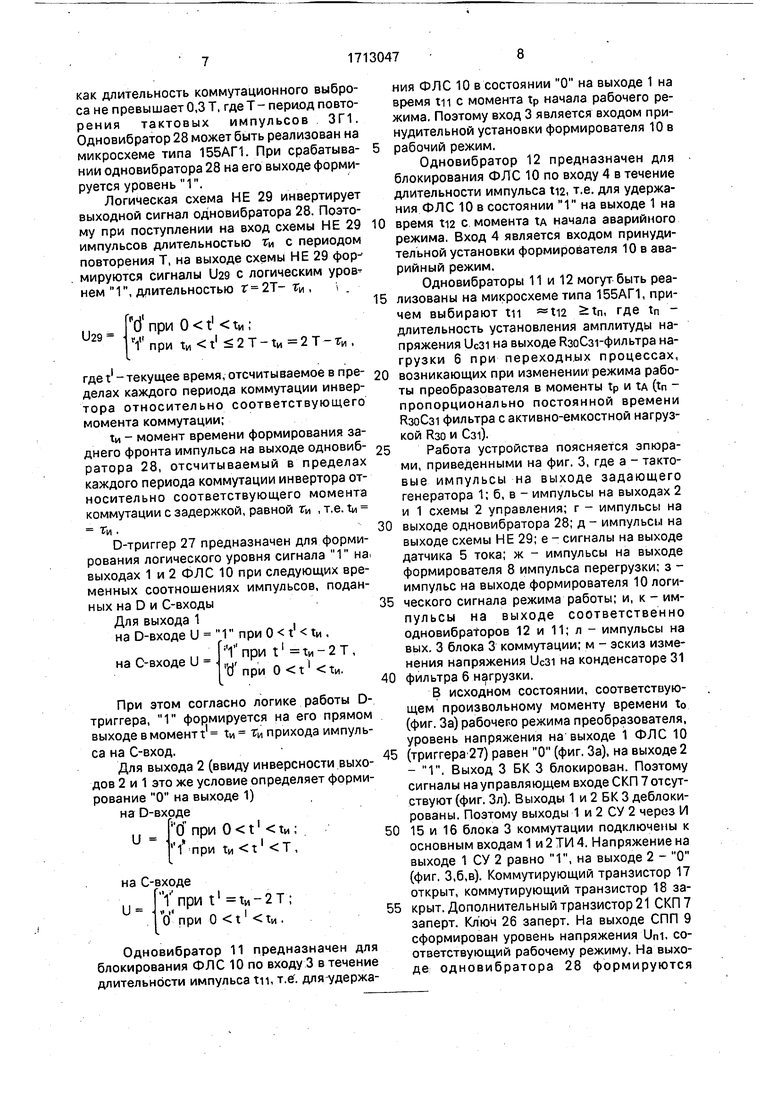

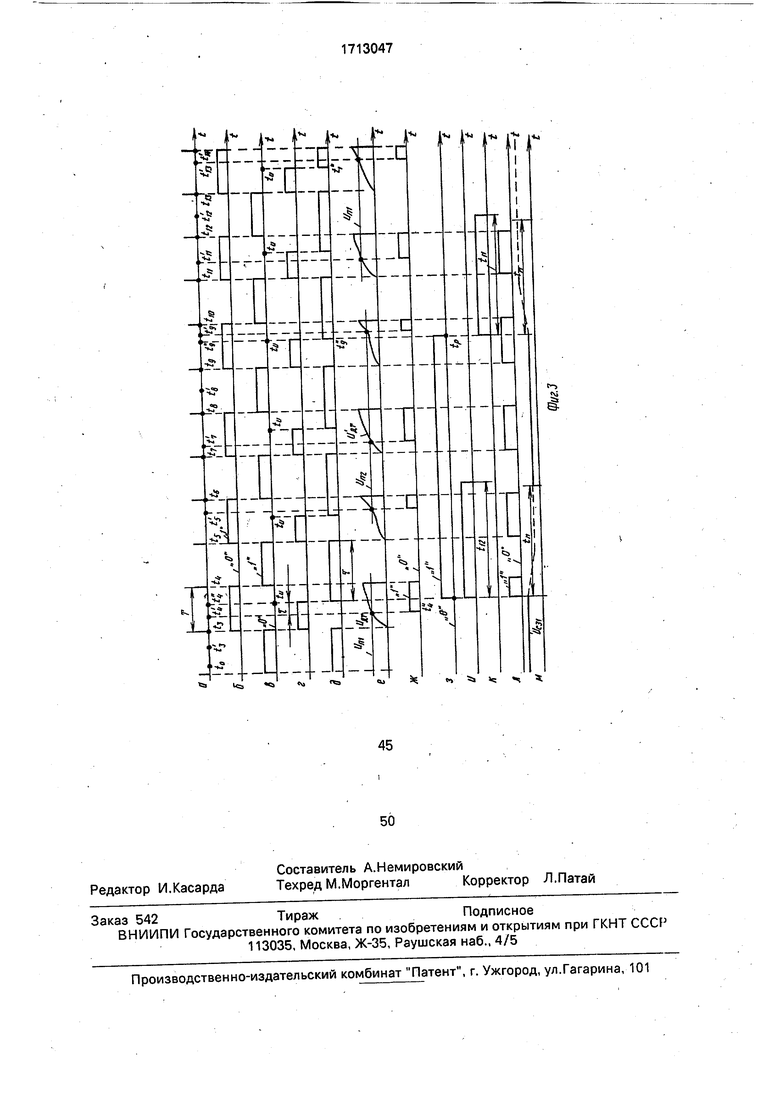

Работа устройства поясняется эпюрами, приведенными на фиг. 3, где а - тактовые импульсы на выходе задающего генератора 1; б, в - импульсы на выходах 2 и 1 схемы 2 управления; г - импульсы на

выходе одновибратора 28; д - импульсы на выходе схемы НЕ 29; е - сигналы на выходе датчика 5 тока; ж - импульсы на выходе формирователя 8 импульса перегрузки; з импульс на выходе формирователя 10 логического сигнала режима работы; и, к - импульсы на выходе соответственно одновибраТоров 12 и 11; л - импульсы на вых. 3 блока 3 коммутации; м - эскиз изменения напряжения Uc3i на конденсаторе 31

фильтра 6 нагрузки.

В исходном состоянии, соответствующем произвольному моменту времени to (фиг. За) рабочего режима преобразователя, уровень напряжения на выходе 1 ФЛС 10

(триггера 27) равен О (фиг. За), на выходе 2 - 1. Выход 3 БК 3 блокирован. Поэтому сигналы науправляюд1ем входе СКП 7отС;утствуют (фиг. 3л). Выходы 1 и 2 БК 3 деблокированы. Поэтому выходы 1 и 2 СУ 2 через И

15 и 16 блока 3 коммутации подключены к основным входам 1 и 2 ТИ 4. Напряжение на выходе 1 СУ 2 равно 1, на выходе 2 - О (фиг. 3,6,в). Коммутирующий транзистор 17 открыт, коммутирующий транзистор 18 закрыт. Дополнительный транзистор 21 СКП 7 заперт. Ключ 26 заперт. На выходе СПП 9 сформирован уровень напряжения Uni, соответствующий рабочему режиму. На выходе одновибратора 28 формируются

импульсы Ги. Напряжение на выходе одновибраторов 11 и 12 равно нулю (фиг. 3 и,к). Уровень напряжения на выходе СПП 9 (Uni) выбирается равным напряжению DAT на резисторе 19 датчика 5 тока, формируемому в момент t 1и Ти при предельно допустимом значении тока в нагрузке б инвертора 4 (предельно допустимая перегрузка). Так, например, если при предельно допустимой перегрузке коллекторный ток транзистора 17 равен 200 мА, Ri9 3,0 м, уровень Uni 0,6 В. Так как режим рабочий, напряжение Uni на ДТ5 в соответствующем интервале времени О - tn ниже уровня Uni. Предположим при этом, что в одном из периодов коммутации ТИ 4 в рабочем режиме в момент ti Ли Ги на выходе схемы НЕ 29 формируется импульс 1 длительностью Ги 2Т - 1и (на фиг. 3 не показан), поступающий на С-вход триггера 27. При сравнении Удт с уровнем Uni в соответствующий момент их равенства ta, находящийся согласно алгоритму работы ФИП 8 в рабочем режиме вне интервала времени ti, на выходе компаратора ФИП 8 формируется импульс 1, поступающий на D-вход триггера 27. Указанные соотношения уровней напряжений UAT и Uni полностью аналогичны приведенным для рабочего режима на фиг. Зе во временном интервале ti3-ti4 (фиг. За). Причем моменту ti соответствует (фиг. Зд) момент ti временного интервала т 2T-tи 2Т - Ги . Моменту ta соответствует момент tis равенства идт Uni (фиг. Зе).

Так как t2 , ti tn Ги , т.е. сигнал на D-вход триггера 27 поступает позже импульса на С-входе, D-триггер, согласно алгоритму его работы остается в прежнем состоянии. Информации) в триггер 27 не записывается. Напряжение на выходе 1 ФЛС 10 (триггера 27) равно О. Поэтому преобразователь остается в рабочем режиме. При зтом амплитуда переменного .напряжения UH на выходе 2 (3) полуобмоток трансформатора ТИ 4 незначительно превышает амплитуду постоянного (выпрямленного) напряжения на конденсаторе 31 Uc3i на величину падения напряжения на открытых диодах выпрямителя 6 нагрузки: UH Uc3i. Величина нагрузочного сопротивления 30 определяет амплитуду напряжения иДт на выходе ДТ 5.

Предположим, что в некоторый момент 1з (t2 ta t3) происходит перегрузка ТИ 4 по току, превышающая предельно допустимую величину- начало аварийного режима. Вследствие этого напряжение идт (фиг. Зе) превышает пороговый уровень Uni в момент t4 tи. На выходе ФИП 8 в момент ts t4 tA

формируется импульс 1 (фиг. Зж). Так как при этом на D-вхбд триггера 27 поступает раньше, чем появится уровень 1 на С-входе, на выходе 1 ФЛС 10 формируется 1 (фиг. Зз). На выходе 2 при t tA ФЛС 10 устанавливается уровень О. Появление 1 на В.4 БК 3 деблокирует выход 3 БК 3, появление О на входе 3 БКЗ блокирует БК

3по выходам 1 и 2. Кроме того, появление 0 1 на управляющем входе СПП 9 открывает

ключ 26, который шунтирует резистор 25. Напряжение на выходе СПП 9 уменьшается до уровня Un2, соответствующего аварийному режиму (Un2 Uni).

5 Деблокирование выхода 3 БК 3 приводит к тому, что на его выходе 3 и соединенном cv ним управляющем входе СКП 7 начинают формироваться импульсы, определяемые логическими уровнями сигналов

0 на входе 1 БКЗ (фиг. 3л). При появлении 1 на управляющем входе транзистора 21 (интервалы времени ts-te, ty-te), он открывается и на выходе ДТ 5 формируются импульсы напряжения, амплитуда которых идт в первый момент ts после переключения оказывается меньше порогового уровня Un2 (фиг. Зе) на соответствующем интервале О-Ти. Это объясняется тем, что при переключении ТИ

4на дополнительный транзистор 21с токо0 ограничительным резистором 22 амплитуда

напряжения UH на выходе трансформатора ТИ 4 оказывается ниже установившегося на конденсаторе 31 постоянного напряжения Uc3i, соответствующего предшествующей

5 работе ТИ 4 в рабочем режиме при t tA. Поэтому на врем$г длительности переходных процессов tn в RC-фильтре нагрузки 6 диоды выпрямителя подзакрываются. их прямое сопротивление возрастает и напря0 жение- идт на резисторе 19 уменьшается несмотря на токовую перегрузку преобразователя Возникает режим, близкий к холостому ходу работы ТИ 4. При формировании 1 на выходе 1 ФЛС 10 в

5 момент tV (фиг. За) запускается одновибратор 12 (фиг. Зи), длительность импульса которого ti2 превышает tn (фиг.Зм).

Поэтому, несмотря , что идт Un2 в сбответствующих интервалах времени 00 tn области t4 t tn - соотношение амплитуд напряжений, характерное для неаварийного (рабочего) режима триггер 27 в течение времени ti2 принудительно удерживается по S-входу (вход 4 ФЛС 10) в со5. стоянии 1.

После окончания импульса ti2 при продолжающейся перегрузке ФЛС 10 остается в состоянии 1 на вь1ходе 1, так как к моменту времени (фиг. За) переходные процессы в RC-фильтре нагрузки 6 заканчиваются. Поэтому напряжение UcSi фильтра успевает уменьшиться до уровня ниже амплитуды UH на величину прямого падения напряжения на диодах выпрямителя, которые открываются и тем самым подключают аварийную нагрузку к инвертору 4, При этом напряжение DAT возрастает и становится пропорциональным току перегрузки. В дальнейшем при продолжающемся аварийной режиме, при равенстве напряжений UBX.I на входе 1 и Un2 на входе 2 компаратора ФИП 8 формируются импульсы (фиг. Зж), возникающие в () соответствующего интервала времени (ty-te). При этом моменты t появления передних фронтов соответствующих импульсов на D-входе триггера 27 находятся внутри временного интервала 0-1и: О t Ти, т.е. соотношение времени поступления импульсов на,входы 1 и 2 ФЛС 10 остается таким же, как при возникновении аварийного режима при t 14. Поэтому на выходе 1 ФЛС 10 сохраняется уровень 1.

Предположим, что аварийный режим оканчивается в момент времени те (фиг. За). Снижение перегрузки ниже предельно допустимой приводит к уменьшению напряжения на выходе ДТ 5 (интервал tg-tio). Сигнал на входе 1 ФИП 8 становится меньше уровня Un2 (фиг. Зе). Поэтому момент tg равенства входных напряжений при возникновении на ДТ 5 коммутационного выброса тока оказывается вне интервала О-Хи (tn tg Tj. На выходе ФИП 8 в момент tg tp tg формируется импульс 1 (фиг. Зж), поступающий на D-вход триггера 27.

Так как tg tn, т.е. сигнал на D-вход поступает позже импульса на С-входе (фиг. Зд), D-триггер 27 согласно алгоритму его работы меняет состояние и на выходе 1 ФЛС 10 устанавливается уровень О, на выходе 2 - 1 (фиг. Зз). Единичный перепад на выходе 2 ФЛС 10 запускает одновибратор 11 с длительностью импульса tii, который через вход 3 ФЛС 10 поступает на R-вход триггера 27 (фиг. Зж).

Происходит переход из аварийного режима работы преобразователя в рабочий режим. Появление О на входе 4 БК 3 блокирует выход 3 БК 3, на котором устанавливается уровень О. Дополнительный транзистор 21 СКП 7 запирается. Кроме того, запирается ключ 26. На выходе СПП 9 устанавливается уровень Uni. Появление 1 на входе 3 деблокирует БКЗ по выходам 1 и 2. Поэтому с выходов 1 и 2 СУ 2 импульсы поступают через И 15 и 16 на основные входы 1 и 2 ТИ 4. К выходным полуобмоткам (выходы 2 и 3) ТИ 4 прикладывается напряжение, амплитуда которого UH в течение

времени tn переходных процессов на RCфильтре нагрузки б оказывается больше, чем установившееся в предшествующем аварийном режиме постоянное напряжение на конденсаторе 31. В результате этого в течение интервала длительности переходных процессов tn происходит дополнительный подзаряд конденсатора 31, что приводит к увеличению амплитуды Удт на датчике 5 тока по сравнению с уровнем Удт в установившемся рабочем режиме (на фиг. Зе условно показана только область tii-ti2). Амплитуда Удт в интервале ti;i-ti2 в пределах длительности O-tn (фиг; Зг) оказывается больше Uni. При сравнении идт с Uni (фиг, Зе) в момент tn tn формируется импульс на выходе компаратора ФИП 8 (фиг. Зж), поступающий на D-вход триггера 27. Так как til Ти, то по аналогии с ранее рассмотренным случаем () на выходе D-триггера (выход 1 ФЛС 10) должна произойти ложная установка 1 - признак перехода в аварийный режим (ложная - так как фактически в рабочем, установившемся режиме перегрузки нет), Однако ложный переход преобразователя в аварийный режим не происходит, так как в интерврле tn переходных процессов ФЛС 10 удерживается по входу 3 принудительной установки в рабочий режим (вход 3 триггера 27) в состоянии О импульсом одновибратора 11 длительностью tii (фиг. Зк). После окончания переходных процессов в рабочем режиме (фиг. 3м) при t ti2 дополнительная перегрузка, обусловленная дозарядом конденсатора 31, снижается до нуля. Поэтому напряжение UAT в интервале ti3-ti4,B пределах длительности O-tn, определяемое установившейся нагрузкой, становится меньше Uni. При сравнении идт с Uni (фиг. Зе) в момент tis формируется импульс на выходе компаратора ФИП 8 (фиг. Зж), поступающий на D-вход триггера 27. Так как tis tn, то по аналогии с ранее рассмотренным случаем (tg tn) преобразователь остается в рабочем режиме при снятой блокировке ФЛС 10 по входу . 3. В дальнейшем при возникновении перегрузок указанные циклы работы повторяются.

Таким образом, предлагаемое устройство по сравнению с известным позволяет обеспечить надежность защиты преобразователя, нагруженного на выпрямитель с фильтром с активно-емкостной нагрузкой. При этом имеется возможность регулировки в широком диапазоне уровня .предельно допустимого тока перегрузки, при превышении которого срабатывает защита преобразователя, возвращающая его в рабочий режим после уменьшения перегрузки.

Формула изобретения

Преобразователь напряжения с защитой от перегрузки по авт. св. № 1585884, о тличающийся тем, что, с целью повышения надежности защиты при работе преобразователя на выпрямитель с фильтром с активно-емкостной нагрузкой, в него введены два одновибратора, а формирователь логического сигнала режима работы снабжен

Вх4 8х.5

входами принудительной установки формирователя в аварийный и рабочий режимы, причем прямой выход формирователя логического сигнала режима работы подключен через один одновибратор к входу принудительной установки формирователя в аварийный режим, а инверсный выход соединен с входом приУ|удительной установки формирователя в рабочий режим через другой одновибратор.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-02-15—Публикация

1990-02-02—Подача